Цифровое устройство оценки дальности

Иллюстрации

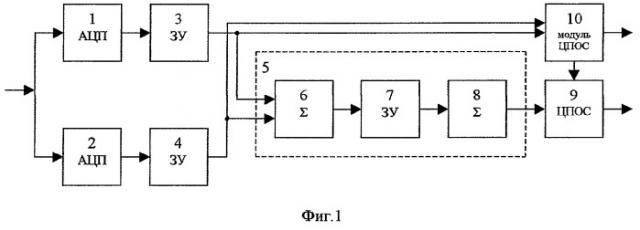

Показать всеЦифровое устройство оценки дальности относится к цифровой вычислительной технике и может быть использовано в радиолокационных системах (РЛС) в устройствах измерения радиальных скорости и дальности цели. Технический результат - упрощение схемы, уменьшение объема аппаратурной реализации, сложности и стоимости устройства при сохранении высокого качества работы РЛС. Устройство содержит первый и второй аналого-цифровые преобразователи, входы которых объединены и являются входом устройства, а выходы соединены соответственно с входами первого и второго запоминающих устройств, цифровой процессор обработки сигналов (ЦПОС), модуль цифровых процессоров обработки сигналов для грубой оценки дальности (модуль ЦПОС), формирователь циклического сигнала, содержащий последовательно соединенные первый сумматор, третье запоминающее устройство и второй сумматор. Выход первого запоминающего устройства соединен с первыми входами первого сумматора формирователя циклического сигнала и модуля ЦПОС, а выход второго запоминающего устройства соединен с их вторыми входами. Выход второго сумматора формирователя циклического сигнала соединен с первым входом цифрового процессора обработки сигналов, ко второму входу которого подключен первый выход модуля ЦПОС, второй выход которого и выход цифрового процессора обработки сигналов являются, соответственно, первым и вторым выходами устройства. 5 ил.

Реферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в радиолокационных системах (РЛС) в устройствах измерения радиальных скорости и дальности цели.

В качестве устройств, выходная информация которых используется в РЛС для измерения радиальных скорости и дальности цели, широко применяются специализированные многопроцессорные вычислительные комплексы (СМВК) многоканальной цифровой обработки сигналов, содержащие большое количество цифровых процессоров обработки сигналов (ЦПОС). ЦПОС предназначены для выполнения быстрых преобразований Фурье (БПФ) или Хартли (БПХ), вычисления функций спектральной плотности, вычисления функций быстрой цифровой свертки и их анализа на превышение заданных порогов. Современные СМВК, как правило, состоят из модулей на основе ЦПОС (ADSP, Motorola, TMS), выпускаемых в различных форматах (PCI, VME, PMC) и исполнениях (коммерческое, индустриальное, военное), отличаются один от другого, в основном, составом аппаратуры в зависимости от предназначения и технических характеристик (ТХ) РЛС.

Наиболее близким по технической сущности к изобретению (прототипом) является устройство цифровой обработки сигналов, содержащее амплитудно-цифровой преобразователь, вход которого является входом устройства и подключается к выходу полосового фильтра суммарного канала приемника РЛС, а выход соединен с запоминающим устройством, к выходу которого подключен СМВК, выход которого является выходом устройства, при этом СМВК состоит из модуля ЦПОС для грубой оценки дальности и модулей ЦПОС для точной оценки дальности, причем общее число М ЦПОС оценивается отношением

где ΔТ - интервал времени тактов зондирования;

Δt - время счета БПФ (БПХ) числа отсчетов, равного N.

В данном устройстве производится: формирование массива m-разрядных чисел длиной L (разрядность m определяется типом используемого АЦП, величина L определяется интервалами оцифрения и строба радиолокационного приемника); разбиение этого массива на М перекрывающихся массивов длиной N (N - число отсчетов зондирующего сигнала, М=L/(N-P), где Р - число отсчетов в интервале перекрытия; вычисление спектра каждого из перекрывающихся массивов и его обработка (определение величины и номера отсчета - максимума, сравнение его с порогом). В случае обнаружения отраженного сигнала измеряется радиальная скорость и производится грубая оценка радиальной дальности цели (при половинном перекрытии P=N/2, если зондирующий сигнал гармонический). В случае обнаружения и получения точной оценки радиальной дальности цели производятся вычисления быстрой свертки каждого массива с массивом скорректированной опорной функции, представляющей собой числовой эквивалент зондирующего (опорного) сигнала с поправкой на доплеровскую частоту (определение величины и номера отсчета-максимума, сравнение его с порогом). Для зондирующих сигналов типа ЛЧМ, ФКМ перекрытие соответствует Р=1. Таким образом, устройство формирует признак обнаружения цели при превышении порогов величинами максимумов и обеспечивает соответственно заданию величины Р оценки дальности цели [Л.Рабинер, Б.Гоулд, «Теория и применение цифровой обработки сигналов». М. «Мир», 1978. Стр.803, рис.13.9].

Причина, препятствующая достижению указанного ниже технического результата при использовании известного устройства цифровой обработки сигналов, заключается в следующем.

Одно из свойств циклической свертки состоит в том, что при N отсчетах входного сигнала и опорного сигнала, среди N отсчетов выходного сигнала лишь один соответствует линейной свертке, т.е. лишь один отсчет выхода является «правильным», а все остальные - «неправильные». Для того чтобы получить все отсчеты сигнала линейной свертки с помощью циклической свертки, число отсчетов входного сигнала необходимо расширить, т.е. удвоить, увеличив при этом число опорной функции до той же величины путем добавления нулевых по значению отсчетов. Следовательно, для определения точной дальности (соответствующей интервалу оцифрения) необходимо выполнить циклическую свертку с числом отсчетов, равным 2N. Прямое вычисление свертки длиной 2N приводит к ухудшению отношения сигнал/шума на 3 дБ, увеличению времени вычисления в 2 раза, к неопределенности в выборе порога. Для большинства РЛС, функционирующих в реальном масштабе времени, такие потери неприемлемы, поэтому на практике и реализуется метод параллельного вычисления N сверток длиной N. Необходимость вычисления большого количества функций цифровой линейной свертки в ограниченные интервалы времени приводит к необходимости распределения их вычислений на параллельных вычислительных структурах - многопроцессорных комплексах, что усложняет и удорожает цифровые устройства оценки дальности в РЛС.

Задачей изобретения является упрощение схемы, уменьшение объема аппаратурной реализации, сложности и стоимости цифрового устройства оценки дальности при сохранении высокого качества работы РЛС.

Указанный технический результат достигается тем, что в известное устройство цифровой обработки сигналов, содержащее первый аналого-цифровой преобразователь, вход которого является входом устройства, а выход соединен с входом первого запоминающего устройства, модуль цифровых процессоров обработки сигналов для грубой оценки дальности (модуль ЦПОС), цифровой процессор обработки сигналов, согласно полезной модели введены второй аналого-цифровой преобразователь, второе запоминающее устройство, формирователь циклического сигнала, содержащий последовательно соединенные первый сумматор, третье запоминающее устройство и второй сумматор, при этом вход второго аналого-цифрового преобразователя соединен с входом первого аналого-цифрового преобразователя, а выход - с входом второго запоминающего устройства, выход первого запоминающего устройства соединен с первыми входами первого сумматора формирователя циклического сигнала и модуля ЦПОС, а выход второго запоминающего устройства соединен со вторыми входами первого сумматора формирователя циклического сигнала и модуля ЦПОС, выход второго сумматора формирователя циклического сигнала соединен с первым входом цифрового процессора обработки сигналов, ко второму входу которого подключен первый выход модуля ЦПОС, второй выход которого и выход цифрового процессора обработки сигналов являются, соответственно, первым и вторым выходами устройства.

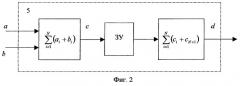

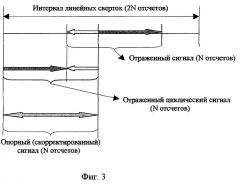

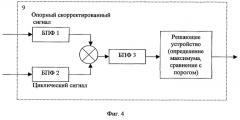

Изобретение поясняется чертежами, на которых представлены: фиг.1 - структурная схема цифрового устройства оценки дальности; фиг.2 - математическая модель формирователя циклического сигнала; фиг.3 - графическая модель формирователя циклического сигнала; фиг.4 - блок-схема алгоритма вычисления быстрой циклической свертки и ее обработка; фиг.5 - графическая иллюстрация вычислений, выполняемых модулем ЦПОС грубой оценки дальности.

Цифровое устройство оценки дальности (фиг.1) содержит первый 1 и второй 2 аналого-цифровые преобразователи (АЛЛ), первое 3 и второе 4 запоминающие устройства (ЗУ), формирователь циклического сигнала (ФЦС) 5, содержащий последовательно соединенные первый сумматор 6, третье ЗУ 7 и второй сумматор 8; цифровой процессор обработки сигналов (ЦПОС) 9 и модуль цифровых процессоров обработки сигналов для грубой оценки дальности (модуль ЦПОС) 10. Входы первого 1 и второго 2 АЦП объединены и, являясь входом устройства, подключаются к выходу полосового фильтра суммарного канала приемника РЛС, а их выходы соединены с входами соответственно первого 3 и второго 4 ЗУ. Выход первого ЗУ 3 соединен с первыми входами первого сумматора 6 ФЦС 5 и модуля ЦПОС 10, а выход второго ЗУ 4 соединен со вторыми входами первого сумматора 6 ФЦС 5 и модуля ЦПОС 10. Выход второго сумматора 8 ФЦС 5 соединен с первым входом ЦПОС 9, ко второму входу которого подключен первый выход модуля ЦПОС 10. Его второй выход и выход ЦПОС 9 являются, соответственно, первым и вторым выходами цифрового устройства оценки дальности, к которым подключаются потребители информации.

Элементы и блоки устройства являются типовыми, выполнены и функционируют по известным правилам. Например, в качестве АЦП могут быть использованы АЦП типа AD6645; в качестве ЦПОС 9 может быть использован ЦПОС типа ADSP-TS101, а в качестве модуля ЦПОС 10 использован ЦПОС формата PCI типа 4× ADSP-TS101 Tiger SHARC фирмы Analog Devices [см., например, www.rtsoft.ru/dsp]. ФЦС 5 может быть выполнен на ПЛИС типа EP1S10 фирмы ALTERA [см., например, www.Altera.com].

Цифровое устройство оценки дальности работает следующим образом (фиг.1). С частотой тактов зондирования на входы первого 1 и второго 2 АЦП поступает сигнал с выхода полосового фильтра суммарного канала приемника РЛС, содержащий отраженный от цели полезный сигнал, шумы и помехи, ограниченный во времени управляемым временным стробом приемника. Последовательности цифровых отсчетов, получаемые с выходов АЦП, запоминаются соответственно в первом 3 и втором 4 ЗУ. Эти отсчеты являются когерентными выборками, суммирование которых согласно известным правилам статистики позволяет получить одну выборку с повышенной на 3 дБ величиной отношения сигнал/шум. В случае немодулированного зондирующего сигнала за время каждого такта зондирования запомненные на предшествующем такте зондирования числовые выборки обрабатываются модулем ЦПОС 10, а в случае модулированного сигнала - обрабатываются последовательно ФЦС 5 и ЦПОС 9.

Если зондирующий сигнал не модулирован (гармонический), то когерентные выборки из ЗУ 3 и 4 длиной L поступают в модуль ЦПОС 10, где по известным правилам (фиг.5) суммируются и из полученной последовательности формируются последовательности чисел длиной, равной количеству отсчетов зондирующего сигнала N. Каждый полученный массив подвергается БПФ или БПХ с последующим вычислением функции спектральной плотности Фурье. Определяются значения величины и координаты порогового превышения каждой функции спектральной плотности, по которым определяются признак наличия отраженного от цели сигнала в стробе, доплеровское смещение по частоте и положение двух последовательностей, содержащих отсчеты отраженного сигнала - интервал линейных сверток. Эта информация является выходной данного блока модуля ЦПОС 10 и с его второго выхода (первого выхода устройства) поступает к потребителям информации.

Если зондирующий сигнал модулирован (линейная частотная модуляция или фазово-кодовая модуляция), то когерентные выборки а и b длиной 2N отсчетов с выходов соответственно первого 3 и второго 4 ЗУ поступают в ФЦС 5 (фиг.2). В первом сумматоре 6 они суммируются по формуле причем в результате сложения двух когерентных последовательностей повышается отношение сигнал/шум на 3 дБ. Получаемые значения в количестве, равном удвоенному числу отсчетов сигнала, записывают в третье ЗУ 7. Эта последовательность с разбивается пополам (фиг.3) и полученные последовательности чисел длиной, равной количеству отсчетов зондирующего сигнала N, поступают во второй сумматор 8, в котором выполняется поэлементное сложение первой и второй половин, записанных в третьем ЗУ 7, по формуле и, таким образом, обеспечивается формирование циклического сигнала с числом отсчетов, равным числу отсчетов скорректированного опорного сигнала, и понижение отношения сигнал/шум на 3 дБ. Полученная последовательность d поступает на вход ЦПОС 9, в котором по известным правилам осуществляются вычисления быстрой циклической свертки и ее обработка (фиг.4). Например, вычисление быстрой циклической свертки может производиться по формуле

Z=БПФ(БПФ(Х)·БПФ(Y)),

где Х - циклический сигнал;

У - опорный сигнал со скорректированным на величину доплеровского смещения частотным спектром;

БПФ - быстрое преобразование Фурье.

В ЦПОС 9 реализуется алгоритм быстрой цифровой свертки циклического и скорректированного опорного сигналов с помощью быстрых алгоритмов Фурье или Хартли. Определяются значения величин и координат порогового превышения значений свертки с точностью до отсчета (интервала оцифрения), являющихся выходной информацией ЦПОС 9, которая с его выхода (второго выхода устройства) поступает к потребителям информации.

Осуществление изобретения обеспечивает существенное упрощение структурной схемы цифрового устройства оценки дальности, уменьшение сложности и объема аппаратурной реализации, а также стоимости устройства при сохранении высокого качества работы РЛС. Использование быстрого преобразования Хартли для выполнения циклической свертки не требует устройств формирования квадратурных каналов, способствует получению более простой формы программного кода, что также упрощает устройство в целом.

Устройство цифровой обработки сигналов, характеризующееся тем, что оно содержит первый аналого-цифровой преобразователь, выход которого соединен с входом первого запоминающего устройства, второй аналого-цифровой преобразователь, выход которого соединен с входом второго запоминающего устройства, цифровой процессор обработки сигналов, модуль цифровых процессоров обработки сигналов для грубой оценки дальности (модуль ЦПОС), формирователь циклического сигнала, содержащий последовательно соединенные первый сумматор, третье запоминающее устройство и второй сумматор, при этом входы первого и второго аналого-цифровых преобразователей объединены и являются входом устройства, выход первого запоминающего устройства соединен с первыми входами первого сумматора формирователя циклического сигнала и модуля ЦПОС, а выход второго запоминающего устройства соединен со вторыми входами первого сумматора формирователя циклического сигнала и модуля ЦПОС, выход второго сумматора формирователя циклического сигнала соединен с первым входом цифрового процессора обработки сигналов, ко второму входу которого подключен первый выход модуля ЦПОС, второй выход которого и выход цифрового процессора обработки сигналов являются соответственно первым и вторым выходами устройства.