Устройство для ввода изображения в эвм

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в системах технического зрения для ввода информации в ЭВМ. Техническом результатом является повышение скорости ввода изображения в ЭВМ. Указанный результат достигается за счет того, что в устройство для ввода изображения в ЭВМ, содержащее АЦП, блок управления, введены усилитель, регистр приема-передачи. Ввод видеоинформации в ЭВМ осуществляется последовательно чтением каждого байта, записанного в регистр приема-передачи. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в системах технического зрения для ввода информации в ЭВМ.

Известно устройство для ввода изображения в ЭВМ (авт.свид. №1432494 СССР, кл. G 06 F 3/00, 1988 г., Бюл. №39), содержащее регистр сдвига, блок управления, счетчик бит, регистр приема, счетчик адреса, формирователь импульсов, блок буферной памяти, блок канальных приемопередатчиков, блок связи с ЭВМ.

Недостатком этого устройства является невысокое быстродействие, т.к. для ввода изображения в ЭВМ необходимо передавать устройству адрес каждого вводимого элемента изображения.

Наиболее близким к предлагаемому является устройство для ввода изображения в ЭВМ (пат. РФ №2166790, кл. 7 G 06 F 3/00, 2000 г., Бюл. №13), содержащее блок управления, регистр приема, блок буферной памяти, счетчик адреса, блок связи с ЭВМ, АЦП, первый и второй блоки канальных передатчиков.

Недостатком этого устройства является низкая скорость ввода изображения в ЭВМ.

Технической задачей устройства является повышение скорости ввода изображения в ЭВМ.

Техническая задача решается тем, что в устройство для ввода изображения в ЭВМ, содержащее АЦП, блок управления, введены усилитель, регистр приема-передачи, причем информационный выход телекамеры подключен к входу усилителя, выход которого соединен с первым входом АЦП, чей второй вход соединен с первым выходом блока управления и с управляющим входом регистра приема-передачи, входы данных которого подключены к выходам АЦП, а информационные выходы соединены с первой группой входов блока управления и являются группой выходов устройства для подключения к младшим восьмимультиплексированным линиям AD [0...7] шины PCI, второй и третий выходы блока управления, первый, второй и третий входы второй группы входов блока управления и третья группа входов блока управления составляют шину управляющих сигналов и подключены соответственно к управляющим линиям шины PCI, а именно к TRDY, DEVSEL, CLK, FRAME, IRDY и С/ВЕ [0...3], четвертая группа входов блока управления составляет адресную шину устройства и соединена с мультиплексированными линиями AD [8...11] шины PCI.

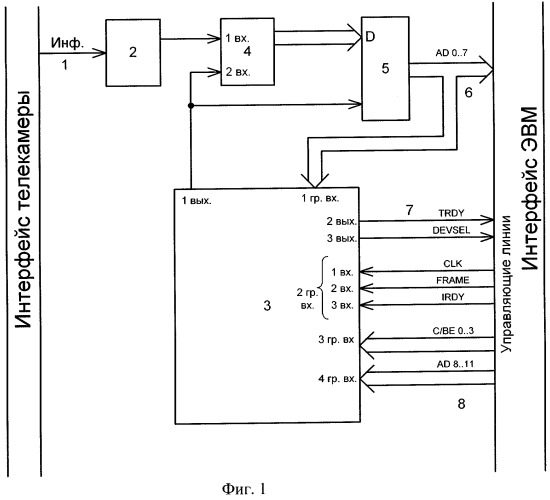

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема устройства для ввода изображения в ЭВМ, а на фиг.2 представлена схема блока управления.

Устройство для ввода изображения в ЭВМ содержит информационный вход 1, усилитель 2, блок управления 3 (БУ), АЦП 4, регистр приема-передачи 5, шину адреса и данных 6, шину управляющих сигналов 7, адресную шину 8, причем информационный выход 1 телекамеры подключен к входу усилителя 2, выход которого соединен с первым входом АЦП 4, чей второй вход соединен с первым выходом блока управления 3 и с управляющим входом регистра приема-передачи 5, входы данных которого подключены к выходам АЦП 4, а информационные выходы соединены с первой группой входов блока управления 3 и являются группой выходов 6 устройства для подключения к младшим восьми мультиплексированным линиям AD [0...7] шины PCI, второй и третий выходы блока управления 3, первый, второй и третий входы второй группы входов блока управления 3 и третья группа входов блока управления 3 составляют шину управляющих сигналов 7 и подключены соответственно к управляющим линиям шины PCI, а именно к TRDY, DEVSEL, CLK, FRAME, IRDY и С/ВЕ [0...3], четвертая группа входов блока управления 3 составляет адресную шину 8 устройства и соединена с мультиплексированными линиями AD [8...11] шины PCI.

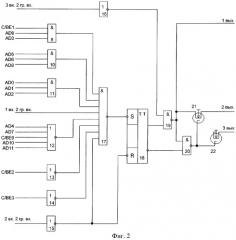

Блок управления 3 предназначен для управления приемом или передачей одного байта телевизионного изображения в ЭВМ. Блок управления (БУ) содержит первый 9, второй 10 и третий 11 элементы И, элемент ИЛИ-НЕ 12, первый 13, второй 14, третий 15 и четвертый 16 элементы НЕ, первый 17, второй 19 и третий 20 элементы И-НЕ, триггер 18, первый 21 и второй 22 транзисторы, причем вход первого элемента НЕ 16 является третьим входом второй группы входов БУ 3, третий вход элемента ИЛИ-НЕ 12, первый вход первого элемента И 9, вход первого элемента НЕ 13, вход второго элемента НЕ 14 соединены соответственно с управляющими линиями С/ВЕ [0...3] шины PCI и являются третьей группой входов БУ 3, третий вход второго элемента И 10, второй вход первого элемента И 9, четвертый и пятый входы элемента ИЛИ-НЕ 12 соединены соответственно с мультиплексированными линиями AD [8...11] шины PCI и являются четвертой группой входов БУ 3, первый, второй и третий входы третьего элемента И 11, третий вход первого элемента И 9, первый вход элемента ИЛИ-НЕ 12, первый и второй входы второго элемента И 10, второй вход элемента ИЛИ-НЕ 12 соединены соответственно с мультиплексированными линиями AD [0...7] шины PCI и являются первой группой входов БУ 3, четвертый вход первого элемента И-НЕ 17 является первым входом второй группы входов БУ 3, вход третьего элемента НЕ 15 является вторым входом второй группы входов БУ 3, выходы первого 9, второго 10 и третьего 11 элементов И, выход элемента ИЛИ-НЕ 12, выходы первого 13, второго 14 и третьего 15 элементов НЕ подключены соответственно к первому, второму, третьему, пятому, шестому, седьмому и восьмому входам первого элемента И-НЕ 17, выход третьего элемента НЕ 15 подключен также к входу сброса триггера 18, вход установки которого соединен с выходом первого элемента И-НЕ 17, прямой выход триггера 18 подключен ко второму входу второго элемента И-НЕ 19, первый вход которого связан с выходом четвертого элемента НЕ 16, выход второго элемента И-НЕ 19 соединен с истоком первого транзистора 21, первым входом третьего элемента И-НЕ 20 и является первым выходом БУ 3, инверсный выход триггера 18 подключен ко второму входу третьего элемента И-НЕ 20, выход которого связан с затворами первого 21 и второго 22 транзисторов, подложка первого 21, исток и подложка второго 22 транзисторов подключены к нулевому потенциалу, стоки первого 21 и второго 22 транзисторов являются соответственно вторым и третьим выходами БУ 3.

АЦП 4 представляет собой восьмиразрядный аналого-цифровой преобразователь и предназначен для преобразования аналогового видеосигнала, поступающего с усилителя 2, в цифровой двоичный восьмиразрядный код. На первый вход АЦП 4 поступает аналоговый видеосигнал, усиленный усилителем 2. Второй вход АЦП 4 является управляющим, при появлении импульса на этом входе происходит обновление данных на выходе АЦП.

Регистр приема-передачи 5 предназначен для приема поступающего от АЦП 4 восьмиразрядного кода и последующей передачи информации в канал ЭВМ.

Устройство работает следующим образом.

Информационный сигнал 1 от телекамеры поступает на вход усилителя 2, который обеспечивает амплитуду сигнала, необходимую для нормальной работы АЦП 4. АЦП 4 при наличии положительного импульса на своем втором входе преобразовывает этот сигнал в параллельный восьмиразрядный двоичный код и передает в регистр приема-передачи 5.

Для чтения байта данных изображения ЭВМ активизирует инверсный сигнал FRAME и на мультиплексированные линии AD [0...11] выставляет адрес устройства 036Fh (в двоичном виде 0011 0110 1111, старшие разряды слева), а на линии С/ВЕ [0...3] команду чтения порта ввода/вывода (в двоичном виде 0010). На первый вход второй группы входов БУ 3 поступают импульсы CLK с частотой до 66 МГц. Появление на входах БУ 3 адреса устройства, команды чтения и положительного импульса CLK вызывает появление логического 0 на выходе первого элемента И-НЕ 17 и затем установку триггера 18 в единичное состояние. Логический 0 на инверсном выходе триггера 18 вызывает появление логической 1 на выходе третьего элемента И-НЕ 20, которая поступает на затворы первого 21 и второго 22 транзисторов и открывает их. В этом случае на стоке второго транзистора 22 и соответственно на линии DEVSEL будет низкий уровень, что означает наличие устройства по адресу 036Fh.

При получении низкого уровня на линии DEVSEL ЭВМ указывает на свою готовность к обмену данными инверсным сигналом IRDY. Появление низкого уровня сигнала IRDY на третьем входе второй группы входов БУ 3 вызовет появление логической единицы на первом входе второго элемента И-НЕ 19. Логический 0 с выхода второго элемента И-НЕ 19 поступает на исток первого транзистора 21, вызывая появление логического 0 на стоке этого транзистора (транзистор открыт) и линии TRDY ЭВМ, указывая на готовность устройства к обмену. Кроме этого, логический 0 с выхода второго элемента И-НЕ 19 поступает на управляющий вход регистра приема-передачи 5, разрешая выдачу данных на шину адреса и данных 6 устройства и соответственно на мультиплексированные линии AD[0...7] шины PCI. Далее ЭВМ выставляет высокий уровень на линиях FRAME и IRDY, вследствие чего на управляющий вход регистра приема-передачи 5 поступает логическая 1, которая запрещает выдачу данных и обновляет данные на выходе АЦП 4. Кроме того, логический 0 на выходе третьего элемента НЕ 15 сбрасывает триггер 18 в 0, что вызывает появление логического 0 на выходе третьего элемента И-НЕ 20 и на затворах первого 21 и второго 22 транзисторов. Первый 21 и второй 22 транзисторы закрываются, что обеспечивает отсутствие сигнала на втором и третьем выходах БУ 3 (высокоимпедансное состояние). Для чтения следующего байта изображения процесс повторяется.

Таким образом, с введением в устройство усилителя и регистра приема-передачи повышается скорость ввода изображения в ЭВМ.

1. Устройство для ввода изображения в ЭВМ, содержащее АЦП, блок управления, отличающееся тем, что в устройство введены усилитель, регистр приема-передачи, причем информационный выход телекамеры подключен ко входу усилителя, выход которого соединен с первым входом АЦП, чей второй вход соединен с первым выходом блока управления и с управляющим входом регистра приема-передачи, входы данных которого подключены к выходам АЦП, а информационные выходы соединены с первой группой входов блока управления и являются группой выходов устройства для подключения к младшим восьми мультиплексированным линиям AD[0...7] шины PCI, второй и третий выходы блока управления, первый, второй и третий входы второй группы входов блока управления и третья группа входов блока управления составляют шину управляющих сигналов и подключены соответственно к управляющим линиям шины PCI, а именно к TRDY, DEVSEL, CLK, FRAME, IRDY и С/ВЕ[0...3], четвертая группа входов блока управления составляет адресную шину устройства и соединена с мультиплексированными линиями AD[8...11] шины PCI.

2. Устройство по п.1, отличающееся тем, что блок управления (БУ) содержит первый, второй и третий элементы И, элемент ИЛИ-НЕ, первый, второй, третий и четвертый элементы НЕ, первый, второй и третий элементы И-НЕ, триггер, первый и второй транзисторы, причем вход первого элемента НЕ является третьим входом второй группы входов БУ, третий вход элемента ИЛИ-НЕ, первый вход первого элемента И, вход первого элемента НЕ, вход второго элемента НЕ соединены соответственно с управляющими линиями С/ВЕ[0...3] шины PCI и являются третьей группой входов БУ, третий вход второго элемента И, второй вход первого элемента И, четвертый и пятый входы элемента ИЛИ-НЕ соединены соответственно с мультиплексированными линиями AD[8...11] шины PCI и являются четвертой группой входов БУ, первый, второй и третий входы третьего элемента И, третий вход первого элемента И, первый вход элемента ИЛИ-НЕ, первый и второй входы второго элемента И, второй вход элемента ИЛИ-НЕ соединены соответственно с мультиплексированными линиями AD[0...7] шины PCI и являются первой группой входов БУ, четвертый вход первого элемента И-НЕ является первым входом второй группы входов БУ, вход третьего элемента НЕ является вторым входом второй группы входов БУ, выходы первого, второго и третьего элементов И, выход элемента ИЛИ-НЕ, выходы первого, второго и третьего элементов НЕ подключены соответственно к первому, второму, третьему, пятому, шестому, седьмому и восьмому входам первого элемента И-НЕ, выход третьего элемента НЕ подключен также ко входу сброса триггера, вход установки которого соединен с выходом первого элемента И-НЕ, прямой выход триггера подключен ко второму входу второго элемента И-НЕ, первый вход которого связан с выходом четвертого элемента НЕ, выход второго элемента И-НЕ соединен с истоком первого транзистора, первым входом третьего элемента И-НЕ и является первым выходом БУ, инверсный выход триггера подключен ко второму входу третьего элемента И-НЕ, выход которого связан с затворами первого и второго транзисторов, подложка первого, исток и подложка второго транзисторов подключены к нулевому потенциалу, стоки первого и второго транзисторов являются соответственно вторым и третьим выходами БУ.