Устройство мониторинга безопасности автоматизированных систем

Иллюстрации

Показать всеИзобретение относится к электросвязи и может быть использовано в автоматизированных технических средствах защиты информации для мониторинга безопасности автоматизированных систем и оперативной идентификации применяемого в цифровых системах связи и, в частности, в сети передачи данных типа «Internet» семейства коммуникационных протоколов TCP/IP. Техническим результатом является повышение достоверности определения факта атаки на автоматизированную систему. Устройство содержит делитель частоты, приемный блок памяти, вычитающий счетчик, опорные блоки памяти, блоки дешифрации, счетчики, элементы И, блоки приема адреса, блоки сравнения, дешифраторы, регистр, блок индикации. 2 ил.

Реферат

Изобретение относится к электросвязи и может быть использовано в автоматизированных технических средствах защиты информации с целью мониторинга1 (1Толкование используемых терминов приведено в Приложении 1) безопасности автоматизированных систем2 (АС) и оперативной идентификации применяемого в цифровых системах связи и, в частности, в сети передачи данных (СПД) типа "Internet" семейства коммуникационных протоколов TCP/IP (Transmission Control Protocol/Internet Protocol), описанных в книге Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.: ил.

Заявленное техническое решение расширяет арсенал средств данного назначения.

Известно устройство мониторинга безопасности АС по патенту РФ №2115952 «Устройство поиска информации», класс G 06 F 17/40, заявленному 13.02.96. В указанном изобретении описано устройство поиска информации, содержащее делитель частоты, блок памяти, вычитающий счетчик, коммутатор, первый, второй, третий и четвертый блоки селекции, регистр стратегии поиска, формирователь временных интервалов и блок индикации.

Данное устройство имеет недостаток - узкая область применения, а именно только для анализа протоколов. Устройство реализует поиск информационных блоков в массиве посредством структурного метода распознавания без учета возможного наличия большого числа повторяющихся типов блоков данных, то есть без учета правил установления и ведения сеанса связи, что ограничивает область применения прототипа в сетях передачи данных типа "Internet" в условиях несанкционированного воздействия (атак3).

Известна система мониторинга безопасности АС по патенту РФ №2179738 «Способ обнаружения удаленных атак в компьютерной сети», класс G 06 F 12/14, заявленному 24.04.2000. Известный способ включает следующую последовательность действий. Наблюдение за графиком адресованных абоненту пакетов данных, включающее постоянно возобновляемый подсчет числа пакетов, выполняемый в пределах серии пакетов, поступающих подряд друг за другом через промежутки времени не более заданного, при этом проверку поступающих пакетов данных на соответствие заданным правилам выполняют каждый раз, когда размер очередной наблюдаемой серии достигает критического числа пакетов.

Недостатком данного способа является узкая область применения, что обусловлено его предназначением в основном для защиты от подмены одного из участников соединения. В аналоге применяют ограниченную совокупность признакового пространства - не учитывают наличия большого числа типов возможных пакетов и не все их допустимые последовательности, что приводит к снижению доступности АС за счет пропуска атаки - «шторма4» ложных запросов на установление соединения (см. Медведовский И.Д. и др. Атака на Internet. - М.: ДМК, 1999. - 336 с.: ил. на стр.120-128) и ограничивает область его применения.

Наиболее близким по своей технической сущности к заявленному является устройство мониторинга безопасности АС по патенту РФ №2219577 «Устройство поиска информации», класс G 06 F 17/40, заявленному 24.04.02. В указанном изобретении описано устройство, содержащее делитель частоты, первый и второй блоки памяти, вычитающий счетчик, первый, второй, третий и четвертый блоки дешифрации, первый, второй и третий элементы «И», первый, второй, третий и четвертый счетчики, первый, второй, третий и четвертый блоки приема адреса, первый и второй блоки сравнения, первый и второй дешифраторы и блок индикации.

Вход делителя частоты является тактовым входом устройства. Информационный вход первого блока памяти является информационным входом пакетов устройства. Тактовый вход первого блока памяти подключен к выходу делителя частоты и тактовому входу вычитающего счетчика, информационный вход числа пакетов которого является информационным входом числа пакетов устройства. Информационный выход первого блока памяти подключен к информационным входам второго блока памяти, второго блока дешифрации, четвертого блока дешифрации, второго блока приема адреса, четвертого блока приема адреса и второго дешифратора. Информационный выход второго блока памяти подключен к информационным входам первого и третьего блоков дешифрации, первого дешифратора и первым информационным входам первого и третьего блоков приема адреса. Тактовые входы второго блока памяти, первого блока дешифрации, второго блока дешифрации, первого счетчика, третьего блока дешифрации, четвертого блока дешифрации, второго счетчика, третьего и четвертого счетчиков объединены и подключены к тактовому выходу делителя частоты. Управляющий выход первого блока дешифрации подключен к первому управляющему входу первого элемента «И», второй управляющий вход которого подключен к выходу второго блока дешифрации. Выход первого элемента «И» подключен к управляющему входу первого счетчика, выход которого подключен к управляющему входу третьего блока дешифрации и управляющему входу четвертого блока дешифрации. Выход четвертого блока дешифрации подключен ко второму управляющему входу второго элемента «И», первый управляющий вход которого подключен к выходу третьего блока дешифрации. Выход второго элемента «И» подключен к управляющему входу второго счетчика, выход которого подключен к второму информационному входу первого блока приема адреса и первому информационному входу второго блока приема адреса. Первый и второй информационные входы первого блока сравнения подключены к выходам соответственно первого и второго блоков приема адреса. Выход первого блока сравнения подключен к управляющему входу третьего счетчика, информационный выход которого подключен к второму информационному входу третьего блока приема адреса и первому информационному входу четвертого блока приема адреса. Первый и второй информационные входы второго блока сравнения подключены к информационным выходам соответственно третьего и четвертого блоков приема адреса. Выход второго блока сравнения подключен к управляющему входу четвертого счетчика, управляющий выход которого подключен к управляющим входам первого и второго дешифраторов. Первый и второй управляющие входы третьего элемента «И» подключены к выходам соответственно первого и второго дешифраторов. Выход третьего элемента «И» подключен к управляющим входам блока индикации и вычитающего счетчика, управляющий выход которого подключен к управляющему входу первого блока памяти и является управляющим выходом устройства. Второй управляющий выход вычитающего счетчика подключен к управляющему входу второго блока памяти.

По сравнению с аналогами устройство может быть использовано в более широкой области, когда не только определяется тип протокола, производится проверка поступающих пакетов данных на соответствие заданным правилам очередности их поступления, но и учитываются правила установления и ведения сеанса связи, что необходимо для повышения устойчивости функционирования автоматизированных систем в условиях несанкционированного воздействия (атак).

Недостатком данного устройства является относительно низкая достоверность5 определения факта атаки на АС, а именно атака не распознается при «шторме» запросов на установление соединения с чередованием портов получателя пакетов сообщений. Это определяется тем, что сравниваются лишь два пакета сообщений - последующий и предыдущий, что является недостаточным для достоверного определения факта атаки на АС.

Целью заявленного технического решения является разработка устройства мониторинга безопасности АС, обеспечивающего повышение достоверности определения факта атаки на АС системами мониторинга безопасности АС при распознавании «шторма» ложных запросов на создание соединения за счет учета правил установления и ведения сеанса связи путем увеличения количества запоминаемых пакетов сообщений, что необходимо для обеспечения устойчивого функционирования АС, заключающегося в предоставлении сервисных возможностей санкционированным абонентам.

Поставленная цель достигается тем, что в известное устройство, содержащее делитель частоты, вход которого является тактовым входом устройства, приемный блок памяти, информационный вход которого является информационным входом пакетов устройства, тактовый вход приемного блока памяти подключен к выходу делителя частоты и тактовому входу вычитающего счетчика, информационный вход числа пакетов которого является информационным входом числа пакетов устройства, информационный выход приемного блока памяти подключен к информационным входам первого опорного блока памяти, второго и четвертого блоков дешифрации, второго и четвертого блоков приема адреса и второго дешифратора, тактовые входы первого опорного блока памяти, первого, второго, третьего и четвертого блоков дешифрации, первого, второго, третьего и четвертого счетчиков объединены и подключены к тактовому выходу делителя частоты, управляющий выход первого блока дешифрации подключен к первому управляющему входу первого элемента «И», второй управляющий вход которого подключен к выходу второго блока дешифрации, а выход первого элемента «И» подключен к управляющему входу первого счетчика, выход которого подключен к управляющему входу третьего блока дешифрации и управляющему входу четвертого блока дешифрации, выход которого подключен ко второму управляющему входу второго элемента «И», первый управляющий вход которого подключен к выходу третьего блока дешифрации, а выход второго элемента «И» подключен к управляющему входу второго счетчика, выход которого подключен к второму информационному входу первого блока приема адреса и первому информационному входу второго блока приема адреса, первый и второй информационные входы первого блока сравнения подключены к выходам соответственно первого и второго блоков приема адреса, а выход первого блока сравнения подключен к управляющему входу третьего счетчика, информационный выход которого подключен к второму информационному входу третьего блока приема адреса и первому информационному входу четвертого блока приема адреса, первый и второй информационные входы второго блока сравнения подключены к информационным выходам соответственно третьего и четвертого блоков приема адреса, а выход второго блока сравнения подключен к управляющему входу четвертого счетчика, управляющий выход которого подключен к управляющим входам первого и второго дешифраторов, первый и второй управляющие входы третьего элемента «И» подключены к выходам соответственно первого и второго дешифраторов, а выход третьего элемента «И» подключен к управляющим входам блока индикации и вычитающего счетчика, первый управляющий выход которого подключен к управляющему входу приемного блока памяти и является управляющим выходом устройства, дополнительно введены пятый счетчик, N опорных блоков памяти, где N≥2, и регистр, причем тактовые входы опорных блоков памяти объединены и подключены к тактовому выходу делителя частоты, информационный выход i-го опорного блока памяти, где i=1, 2, ..., N, подключен к информационному входу i+1 опорного блока памяти и j-му информационному входу регистра, информационный выход регистра подключен к информационным входам первого и третьего блока дешифрации, первого дешифратора и к первым информационным входам первого и третьего блоков приема адреса, управляющий вход i-го, где i=1, 2, ..., N, опорного блока памяти подключен к j-му управляющему выходу пятого счетчика, управляющий вход пятого счетчика подключен к второму управляющему выходу вычитающего счетчика, информационный выход N-го опорного блока памяти подключен к N-му информационному входу регистра.

Благодаря новой совокупности существенных признаков в заявленном устройстве обеспечивается повышение достоверности систем мониторинга безопасности АС при распознавании «шторма» ложных запросов на создание соединения за счет учета правил установления и ведения сеанса связи путем увеличения количества запоминаемых пакетов сообщений, что необходимо для обеспечения устойчивого функционирования автоматизированных систем в условиях несанкционированного воздействия (атак).

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

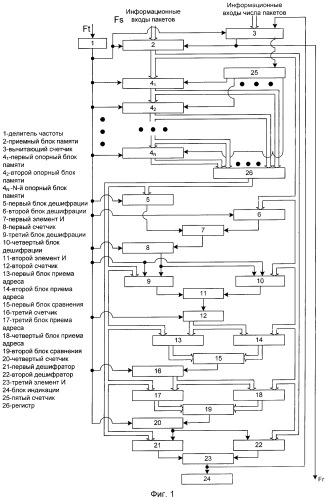

Заявленное устройство поясняется чертежами, на которых показаны:

фиг.1 - общая схема устройства;

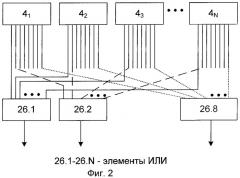

фиг.2 - схема регистра.

Устройство мониторинга безопасности автоматизированных систем, показанное на фиг.1, содержит делитель частоты 1, вычитающий счетчик 3, приемный блок памяти 2, первый 41, второй 42, i-й 4N, где i=1, 2, ..., N опорные блоки памяти, первый 5, второй 6, третий 9 и четвертый 10 блоки дешифрации, первый 7, второй 11 и третий 23 элементы «И», первый 8, второй 12, третий 16, четвертый 20 и пятый 25 счетчики, первый 13, второй 14, третий 17 и четвертый 18 блоки приема адреса, первый 15 и второй 19 блоки сравнения, первый 21 и второй 22 дешифраторы, блок индикации 24 и регистр 26.

Вход делителя частоты 1 является тактовым входом устройства. Информационный вход входного блока памяти 2 является информационным входом пакетов устройства. Тактовый вход входного блока памяти 2 подключен к выходу делителя частоты 1 и тактовому входу вычитающего счетчика 3, информационный вход числа пакетов которого является информационным входом числа пакетов устройства. Информационный выход входного блока памяти 2 подключен к информационным входам первого опорного блока памяти 41, второго блока дешифрации 6, четвертого блока дешифрации 10, второго дешифратора 22 и вторым информационным входам второго блока приема адреса 14 и четвертого блока приема адреса 18. Тактовые входы первого опорного блока памяти 41, второго опорного блока памяти 42, i-го, где i=1, 2, ..., N опорного блока памяти 4N, первого блока дешифрации 5, второго блока дешифрации 6, первого счетчика 8, третьего блока дешифрации 9, четвертого блока дешифрации 10, второго 12, третьего 16 и четвертого 20 счетчиков объединены и подключены к тактовому выходу делителя частоты 1. Управляющий выход первого блока дешифрации 5 подключен к первому управляющему входу первого элемента «И» 7, второй управляющий вход которого подключен к выходу второго блока дешифрации 6. Выход первого элемента «И» 7 подключен к управляющему входу первого счетчика 8, выход которого подключен к управляющему входу третьего блока дешифрации 9 и управляющему входу четвертого блока дешифрации 10. Выход четвертого блока дешифрации 10 подключен ко второму управляющему входу второго элемента «И» 11, первый управляющий вход которого подключен к выходу третьего блока дешифрации 9. Выход второго элемента «И» 11 подключен к управляющему входу второго счетчика 12, выход которого подключен к второму информационному входу первого блока приема адреса 13 и первому информационному входу второго блока приема адреса 14. Первый и второй информационные входы первого блока сравнения 15 подключены к выходам соответственно первого 13 и второго 14 блоков приема адреса. Выход первого блока сравнения 15 подключен к управляющему входу третьего счетчика 16, информационный выход которого подключен к второму информационному входу третьего блока приема адреса 17 и первому информационному входу четвертого блока приема адреса 18. Первый и второй информационные входы второго блока сравнения 19 подключены к информационным выходам соответственно третьего 17 и четвертого 18 блоков приема адреса. Выход второго блока сравнения 19 подключен к управляющему входу четвертого счетчика 20, управляющий выход которого подключен к управляющим входам первого 21 и второго 22 дешифраторов. Первый и второй управляющие входы третьего элемента «И» 23 подключены к выходам соответственно первого 21 и второго 22 дешифраторов. Выход третьего элемента «И» 23 подключен к управляющим входам блока индикации 24 и вычитающего счетчика 3, первый управляющий выход которого подключен к управляющему входу приемного блока памяти 2 и является управляющим выходом устройства. Информационный выход первого опорного блока памяти 41 подключен к информационному входу i-го, где i=1, 2, ..., N опорного блока памяти 4N и j-му, где j=1, 2, 3, ... N информационному входу регистра 26, информационный выход регистра 26 подключен к информационным входам первого блока дешифрации 5, третьего блока дешифрации 9, первого дешифратора 21, и первым информационным входам первого 13 и третьего 17 блоков приема адреса. Управляющий вход первого опорного блока памяти 41 подключен к первому управляющему выходу пятого счетчика 25. Управляющий вход i-го, где i=1, 2, ..., N опорного блока памяти 4N подключен к j-му управляющему выходу пятого счетчика 25, а информационный выход i-го опорного блока памяти 4N подключен к информационному входу (i+1)-го блока памяти и к j-му информационному входу регистра 26. Управляющий вход пятого счетчика 25 подключен ко второму управляющему выходу вычитающего счетчика 3. Информационный вход N-го опорного блока памяти 4N подключен к j-му информационному входу регистра 26 и является информационным выходом N-го опорного блока памяти, а управляющий вход i-го блока памяти 4N подключен к j-му управляющему выходу пятого счетчика 25.

Разрядность шины «Информационные входы пакетов» определяется разрядностью анализируемых данных, и т.к. устройство обрабатывает байты, она является восьмиразрядной. Разрядность шины «Информационные входы числа пакетов» определяется объемом оперативного запоминающего устройства (ОЗУ) блоков памяти, и т.к. емкость ОЗУ составляет 4096=212, она является двенадцатиразрядной. Информационные связи между блоками памяти и регистром 26, вторым 6 блоком дешифрации, четвертым 10 блоком дешифрации, вторым 14 блоком приема адреса, четвертым 18 блоком приема адреса и вторым 22 дешифратором являются восьмиразрядными, т.к. служат для передачи байтов и физически представляют собой шину из восьми проводников. Информационные связи между регистром 26, первым 5 блоком дешифрации, третьим 9 блоком дешифрации, первым 13 блоком приема адреса, третьим 17 блоком приема адреса, первым 21 дешифратором являются восьмиразрядными, т.к. служат для передачи байтов и физически представляют собой шину из восьми проводников. Управляющие связи между вторым 12 счетчиком, первым 13 блоком приема адреса и вторым 14 блоком приема адреса являются восьмиразрядными. Информационные связи между первым 13, вторым 14 блоками приема адреса и первым 15 блоком сравнения являются шестидесятичетырехразрядными. Управляющие связи между третьим 16 счетчиком, третьим 17 блоком приема адреса и четвертым 18 блоком приема адреса являются четырехразрядными. Информационные связи между третьим 17, четвертым 18 блоками приема адреса и вторым 19 блоком сравнения являются тридцатидвухразрядными. Восьмиразрядные информационные и управляющие связи представляют собой восемь параллельных проводников. Шестидесятичетырехразрядные информационные связи представляют собой шестьдесят четыре параллельных проводника. Четырехразрядные управляющие связи представляют собой четыре параллельных проводника. Тридцатидвухразрядные информационные связи представляют собой тридцать два параллельных проводника.

Делитель частоты 1 служит для деления тактовой частоты Ft на 8 с целью обеспечения побайтного анализа сигнальной цифровой последовательности Fs. Схема делителя частоты 1 известна (см., например, патент РФ N2115952, класс G 06 F 17/40), полностью совпадает по количеству входов и выходов, а также по функциональному назначению и может быть выполнена по схеме, изображенной на рис.1.66 Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып.1111) и, в частности, на К155ИЕ5.

Приемный блок памяти 2, первый 41, второй 42 и i-й 4N опорные блоки памяти предназначены для хранения и последующего считывания с них байтов данных пакетов. Схемы приемного блока памяти 2, первого 41, второго 42, i-го 4N опорных блоков памяти аналогичны, известны (см., например, фиг.2 патент РФ N2115952, класс G 06 F 17/40) и полностью совпадают по количеству входов и выходов, а также по функциональному назначению.

Вычитающий счетчик 3 предназначен для определения количества байтов пакета, включая байт, который анализируется в текущий момент времени, находящихся в приемном блоке памяти 2, управления функционированием приемного 2 блока памяти и пятого счетчика 25 и формирования управляющего сигнала (логическая "1") Fr разрешения трансляции сигнальной цифровой последовательности Fs, поступающего на демодулирующее устройство (канальный контроллер). Информация N о количестве байт, содержащихся в пакете, поступившем в приемный блок памяти 2, записывается в вычитающий счетчик 3 в параллельном виде по его второму - тринадцатому входам в момент поступления последнего байта пакета в приемный блок памяти 2. Уменьшение показания счетчика на единицу происходит при каждом поступлении на его первый вход управляющего сигнала с выхода делителя частоты 1. Обнуление показания счетчика происходит при поступлении управляющего сигнала на четырнадцатый вход вычитающего счетчика. При значении вычитающего счетчика 3, равном 0, на его первом выходе формируется управляющий сигнал, а при значении вычитающего счетчика 3, равном 1, на его втором выходе формируется управляющий сигнал. Он может быть выполнен по схеме, изображенной на рис.1.73 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып.1111).) и, в частности, на К155ИЕ17.

Первый 5 и второй 6 блоки дешифрации идентичны и предназначены для определения в сигнальной цифровой последовательности Fs, поступающей с приемного блока памяти 2 и первого опорного блока памяти 41 типа протокола сетевого уровня. В данном случае для протокола IP и формата кадра Ethernet 802.3/LLC это значение в десятичном исчислении равно шести (Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.: ил.). Вариант построения первого 5 и второго 6 блоков дешифрации известен (см. фиг.2 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Первый 8 счетчик предназначен для отсчета 9 байт для обнаружения 24-го байта пакета и выработки управляющего сигнала разрешения записи этого байта в третий 9 и четвертый 10 блоки дешифрации. Вариант построения такого блока известен (см. фиг.6 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Третий 9 и четвертый 10 блоки дешифрации идентичны и предназначены для определения в 24-ом байте от начала кадра числового значения «шесть» (06) в десятичном виде, идентифицирующем протокол транспортного уровня (Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.: ил.). Вариант построения третьего 9 и четвертого 10 блоков дешифрации известен (см. фиг.3 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Второй 12 счетчик предназначен для отсчета двух байтов до первого байта поля адреса отправителя в заголовке IP-пакета и выработки управляющих сигналов разрешения записи следующих восьми байтов (27-й - 34-й байты) пакета в первый 13 и второй 14 блок приема адреса. Вариант построения такого блока известен (см. фиг.7 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Первый 13 и второй 14 блоки приема адреса идентичны и предназначены для хранения адресов отправителя и получателя IP-дейтаграмм. Вариант построения такого блока известен (см. фиг.4 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Третий 16 счетчик предназначен для отсчета четырех байтов и выработки управляющих сигналов в третий 17 и четвертый 18 блоки приема адреса. Вариант построения такого блока известен (см. фиг.8 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Третий 17 и четвертый 18 блоки приема адреса предназначены для хранения номеров портов отправителя и получателя TCP-пакетов. Вариант построения такого блока известен (см. фиг.5 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Четвертый 20 счетчик предназначен для отсчета десяти байтов и выдачи управляющих сигналов разрешения записи в первый 21 и второй 22 дешифраторы 48-го байта от начала кадра. Вариант построения такого блока известен (см. фиг.9 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

В качестве первого 7, второго 11 и третьего 23 элементов И может быть использована одна из известных микросхем серии 555, например К555ЛИ2 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. стр.40, рис.1.23).

Первый 21 и второй 22 дешифраторы предназначены для выделения из 48-го байта от начала кадра контрольного бита синхронизации номеров в очереди SYN. Вариант построения такого блока известен (см. фиг.10 патент РФ №2219577, класс G 06 F 17/40) и полностью совпадает по количеству входов и выходов, а также по функциональному назначению.

Первый 15 блок сравнения, сравнивающий два шестидесятичетырехразрядных слова и второй 19 блок сравнения, сравнивающий два тридцатидвухразрядных слова, могут быть реализованы на микросхемах К555СП1. Схемы наращивания компараторов для сравнения двух N-разрядных слов известны и описаны в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып.1111) на стр. 183-184, 187, рис.1.135.

Блок индикации 24 предназначен для визуального отображения принятого решения о повторяющемся пакете протокола TCP/IP. Схемы индикаторов известны и описаны, например, в книге Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1989, стр.197, рис.7.1.

Пятый счетчик 25 служит для подачи сигнала разрешения считывания на первый 41, второй 42, i-й опорные блоки памяти 4N, где i=1, 2, ..., N. Схема счетчика известна и описана, см., например Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: Массовая радиобиблиотека. Вып.1145 на стр.92, рис.1.66., причем разрядность счетчика может наращиваться, схема наращивания разрядности известна и описана (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: Массовая радиобиблиотека. Вып.1145 на стр.91). В частности, такая схема может быть реализована на микросхеме К155ИЕ5.

Регистр 26 предназначен для объединения по операции ИЛИ первого-восьмого проводников информационных выходов первого 41, второго 42, i-го 4N опорных блоков памяти и подачи байтов пакетов на информационные входы первого блока дешифрации 5, третьего блока дешифрации 9, первого дешифратора 21, и первые информационные входы первого 13 и третьего 17 блоков приема адреса. Регистр 26 представляет собой восемь N-входовых элементов ИЛИ. Вариант построения регистра 25 показан на фиг.2. Регистр 26 содержит первый 26.1, второй 26.2, третий 26.3, четвертый 26.4, пятый 26.5, шестой 26.6, седьмой 26.7, восьмой 26.8 элементы ИЛИ. Первые входы первого 26.1, второго 26.2, третьего 26.3, четвертого 26.4, пятого 26.5, шестого 26.6, седьмого 26.7, восьмого 26.8 элементов ИЛИ являются первым входом регистра 26 и подключены к первому-восьмому проводникам информационного выхода первого опорного 41 блока памяти. Вторые входы первого 26.1, второго 26.2, третьего 26.3, четвертого 26.4, пятого 26.5, шестого 26.6, седьмого 26.7, восьмого 26.8 элементов ИЛИ являются вторым входом регистра 26 и подключены к первому-восьмому проводникам информационного выхода второго опорного 42 блока памяти, j-ые входы первого 26.1, второго 26.2, третьего 26.3, четвертого 26.4, пятого 26.5, шестого 26.6, седьмого 26.7, восьмого 26.8 элементов ИЛИ являются j-ым входом регистра 26 и подключены к первому-восьмому проводникам информационного выхода i-го 4N опорного блока памяти. Выход первого 26.1 элемента ИЛИ является первым выходом регистра 26. Выход второго 26.2 элемента ИЛИ является вторым выходом регистра 26. Выход третьего 26.3 элемента ИЛИ является третьим выходом регистра 26. Выход четвертого 26.4 элемента ИЛИ является четвертым выходом регистра 26. Выход пятого 26.5 элемента ИЛИ является пятым выходом регистра 26. Выход шестого 26.6 элемента ИЛИ является шестым выходом регистра 26. Выход седьмого 26.7 элемента ИЛИ является седьмым выходом регистра 26. Выход восьмого 26.8 элемента ИЛИ является восьмым выходом регистра 26. Схемы элементов ИЛИ известны и описаны, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: (Массовая радиобиблиотека. Вып.1145) на стр.48, рис.1.23з. В частности, такая схема может быть реализована на микросхеме К155ЛЛ1.

Устройство работает следующим образом. Делитель частоты 1 обеспечивает побайтный анализ входной цифровой последовательности. При получении с первого выхода реверсивного счетчика 3 разрешения на запись (логическая "1") производится заполнение ячеек ОЗУ приемного 2 блока памяти байтами пакета, поступившими с демодулирующего устройства (канального контроллера). После того, как записаны все байты очередного пакета анализируемого протокола, в вычитающий счетчик 3 заносится общее количество записанных в ОЗУ байтов, после чего на его первом выходе формируется разрешение на побайтное считывание информации (логический "0"). В это время в ОЗУ первого 41, второго 42 и i-го 4N, где i=1, 2, ..., N опорных блоков памяти, записаны предыдущие пакеты (или в начальном состоянии - нули).

С выходов приемного блока памяти 2 и первого 41, второго 42 и i-го, где i=1, 2, ..., N, опорных блоков памяти байты пакетов последовательно поступают на информационные входы первого 5, второго 6, третьего 9, четвертого 10 блоков дешифрации, первого 21, второго 22 дешифраторов, первого 13, второго 14, третьего 17 и четвертого 18 блоков приема адреса. Регистр 26 обеспечивает объединение по операции ИЛИ первой-восьмой информационных шин первого 41, второго 42 и i-го 4N, i=1, 2 ..., N опорных блоков памяти. Первый 5 и второй 6 блоки дешифрации определяют в сигнальной цифровой последовательности Fs числового значения «шесть» (06) в десятичном виде, соответствующее наличию в пакете протокола IP. Необходимо отметить, что в данной заявке рассматривается формат кадра Ethernet 802.3/LLC. В случае других типов кадра, например для Ethernet DIX (Ethernet II), длина этого поля составила бы 2 байта и его значение было бы равно в десятичном виде числу «восемь» (0800) (Кульгин М. Технологии корпоративных сетей. Энциклопедия. - СПб.: Издательство «Питер», 1999. - 704 с.: ил.). В первом 7 элементе И эти значения сравниваются для выработки управляющего сигнала на первый 8 счетчик, который отсчитывает 9 байт для обнаружения 24-го байта пакета и вырабатывает управляющий сигнал разрешения записи этого байта в третий 9 блок дешифрации и в четвертый 10 блок дешифрации. Третий 9 и четвертый 10 блоки дешифрации предназначены для определения в этом байте числового значения «шесть» (06) в десятичном виде. В этом случае используемым протоколом является TCP. Во втором 11 элементе И эти значения сравниваются для выработки разрешающего сигнала на второй 12 счетчик, который отсчитывает два байта до первого байта поля адреса отправителя в заголовке IP-пакета и вырабатывает управляющие сигналы разрешения записи следующих восьми байтов сигнальных цифровых последовательностей (27-й-34-й байты пакета) в регистры первого 13 блока приема адреса и в второго 14 блока приема адреса.

В результате в первый 13 и второй 14 блоки приема адреса записываются адреса отправителя и получателя IP-дейтаграмм. В первом 15 блоке сравнения эти адреса сравниваются, и в случае их совпадения вырабатывается управляющий сигнал, поступающий на третий 16 счетчик, который отсчитывает четыре байта и вырабатывает управляющие сигналы для записи в регистры третьего 17 блока приема адреса и в регистры четвертого 18 блока приема адреса 35-го, 36-го, 37-го и 38-го байтов пакета, в которых находятся номера портов отправителя и получателя пакета. В случае их совпадения второй 19 блок сравнения вырабатывает управляющий сигнал, поступающий на четвертый 20 счетчик, предназначенный для выдачи управляющих сигналов разрешения записи в первый 21 и второй 22 дешифраторы 48-го байта от начала кадра. Эти дешифраторы предназначены для выделения из 48-го байта от начала кадра контрольного бита синхронизации номеров в очереди SYN. В случае наличия этого бита в обоих пакетах третий 23 элемент И вырабатывает управляющий сигнал, поступающий на блок индикации 24 и обнуляющий показания вычитающего счетчика 3.

После принятия как положительного, так и отрицательного решения о наличии повторяющихся запросов на создание логического соединения происходит обнуление вычитающего счетчика 3 и устройство поиска информации готово к ведению анализа вновь поступающей входной цифровой последовательности.

Таким образом, из рассмотренного принципа действия устройства видно, что устройство обеспечивает возможность анализа протоколов, определения использования протокола TCP, получения решения о наличии неоднократно повторяющихся запросов на создание сколь угодно большого количества логических каналов связи путем сравнения поступающих блоков данных, что необходимо для обеспечения устойчивого функционирования автоматизированных систем в условиях несанкционированного воздействия (атак). Этим достигается сформулированная цель - повышение достоверности заявленного устройства, которое позволяет не только определить тип протокола (как в прототипе), но и учитывать правила установления и ведения сеанса связи. Обнаружение несанкционированного воздействия (атаки) происходит на втором цикле с вероятностью, близкой к единице.

Перечень используемых терминов

1. Мониторинг - регулярное отслеживание событий, происходящих в процессе обмена информацией, с регистрацией и анализом предопределенных значимых или подозрительных событий. [Конеев И.Р., Беляев А.В. Информационная безопасность предприятия. - СПб.: БХВ-Петербург, 2003. - 752 с.: ил. на стр.30].

2. Автоматизированная система (AC) - система, состоящая из персонала и комплекса средств автоматизации его деятельности, реализующая информационную технологию выполнения установленных функций [Информационная безопасность и защита информации. Сборник терминов и определений. Государственная техническая комиссия России, 2001 г.].

3. Атака - практическая реализация угрозы или попытка ее реализации с использованием той или иной уязвимости [Конеев И.Р., Беляев А.В. Информационная безопасность предприятия. - СПб.: БХВ-Петербург, 2003. - 752 с.: ил. на стр.30].

4. Шторм - передача на объект атаки как можно большего числа ложных TCP-запросов на создание соединения от имени любого хоста. [Медведовский И.Д. и др. Атака на Internet. - М.: ДМК, 1999. - 336 с.: ил. на стр.121].

5. Достоверность - степень объективного соответствия результатов диагностирования (контроля) действительному техническому состоянию объекта [Кузнецов В.Е., Лихачев А.М., Паращук И.Б., Присяжнюк С.П. Телекоммуникации. Толковый словарь основных терминов и сокращений. Под редакцией А.М.Лихачева, С.П.Присяжнюка. - Спб.: Издательство МО РФ, 2001.].

Устройство поиска информации, содержащее делитель частоты, вход которого является тактовым входом устройства, приемный блок памяти, информационный вход которого является инфо