Способ сжатия и восстановления цифровых данных и устройство его осуществления

Иллюстрации

Показать всеИзобретение относится к области регистрации цифровой информации, может использоваться для увеличения объема записи на DVD или CD. Техническим результатом является повышение степени сжатия при записи и восстановления цифровых данных вместе с избыточной информацией. Технический результат достигается тем, что способ формирует плавающий коэффициент сжатия от 2 до 255 при записи путем сравнения значений кодов потока по величине, подсчета числа равных по величине и следующих друг за другом кодов, формирование двоичного кода этого числа и введение его в поток за первым кодом своей последовательности с исключением из нее подсчитанных кодов, при восстановлении производится определение в потоке кода числа равных кодов, дешифрирование его и формирование числа сигналов выдачи первого кода, равного числу изъятых кодов при сжатии. 2 н.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области регистрации цифровой информации, может использоваться для увеличения объема записи цифровых данных на DVD или CD.

За прототип принят способ сжатия цифровых данных MPEG-2 [1, с.22] как стандарт сжатия для записи изображения на дисках DVD. Алгоритм MPEG выполняет поточное сжатие видео: анализирует динамику изменения между кадрами и устраняет избыточные данные. Способ сжатия MPEG-2 [1, с.22-25] определяет последовательное создание трех типов кадров: ключевого Intra кадра, выполняющего роль опорного кадра, следующего через 10-15 кадров, Р-кадра, предсказуемые кадры, содержат разность текущего изображения с предыдущим I-кадром или Р-кадром с учетом смещений отдельных фрагментов, В-кадры - кадры двунаправленной интерполяции, содержат ссылки на предыдущие или последующие I- или Р-кадры. Сжатие начинается с создания ключевого I-кадра, который для кодирования разбивается на блоки 8×8 пикселов, над каждым блоком производится дискретно-косинусное преобразование Фурье с последующим квантованием полученных коэффициентов. Дискретно-косинусное преобразование приводит к концентрации сигнала в низкочастотной части спектра, который после квантования эффективно сжимается с использованием кодирования переменной длины. Чем грубее квантование, тем сильнее сжатие сигнала, но тем больше вносится визуальных искажений. Затем следует обработка Р-кадров с использованием предсказания вперед по предшествующим исходным или предсказуемым кадрам. Р-кадр разбивается на макроблоки 16×16 пикселов. Каждому макроблоку ставится в соответствие похожий участок изображения из опорного I-кадра, сдвинутый на вектор перемещения. Допустимая степень сжатия Р-кадров превышает степень сжатия I-кадров в 3 раза. В-кадры с сылкой на I- или Р-кадры выполняют интерполяцию с учетом смещения фрагментов, с В-кадрами наиболее глубокое сжатие данных. В результате видеопоток представляется группами кадров, например ...I-B-B-P-В-B-P-B-B-P-B-B-I... При воспроизведении видеопотока декодер MPEG аппаратного проигрывателя выполняет обратное декодирование цифрового видеосигнала. Стандарт MPEG-2 поддерживает скорость потока от 3 до 15 Мбит/с, допускает разрешение до 720×576 /поток 6 Мбайт/с [2, c.542] и достигает степень сжатия 10:1. При воспроизведении сжатой информации (с видеодиска) декодер MPEG аппаратного проигрывателя выполняет обратное преобразование (декодирование) цифрового видеосигнала. При декодировании внутрикадровой компрессии используется обратное дискретно-косинусное преобразование Фурье. Недостатками способа-прототипа являются: способ предназначен для сжатия видеоданных; для повышения степени сжатия необходимо грубое квантование, вызывающее большее искажение при восстановлении изображения; в кадрах, насыщенных деталями и высокой динамикой, заметны на глаз дефекты - дробление, размытость изображения [1, c.25], сложность процесса сжатия - его многоступенчатость; исключение избыточной информации снижает художественность кадров.

Прототипом устройства принято устройство, реализующее способ сжатия MPEG-2 [2, с.543], представляющее кодер, включающий последовательно соединенные дискретно-косинусный преобразователь, устройство квантования и временной кодер. Недостатком прототипа является многоступенчатость процесса сжатия.

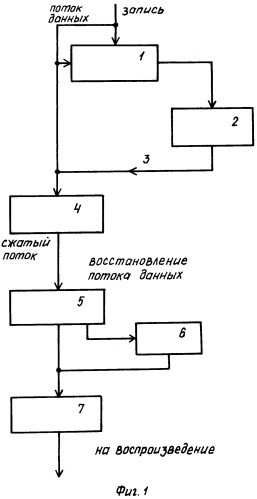

Цель изобретения - увеличение степени сжатия без удаления избыточной информации и восстановление всех данных при воспроизведении. Техническим результатом является повышение степени сжатия при записи и восстановление всех цифровых данных вместе с избыточной информацией. Технический результат достигается применением плавающего коэффициента сжатия и простотой способа, способ пригоден для сжатия любой цифровой информации: видео, звуковой. Степень сжатия на разных участках потока разная, диапазон изменения коэффициента сжатия от 2 до 255 (фиг.1). В темпе потока кодов производится подсчет числа последовательно следующих и равных по величине кодов, формируется двоичный код этого числа, который вводится в поток цифровых данных следом за первым кодом последовательности равных кодов. Максимальная длина последовательности равных кодов допускается до 255, т.е. код 11111111. Заявляемый способ сжатия и восстановления цифровых данных включает последовательно выполняемые операции по схеме фиг.1 при записи:

1. сравнение значений кодов потока по величине для определения кодов, равных по величине и следующих друг за другом;

2. подсчет числа кодов, равных по величине, начиная со второго кода в последовательности, и формирование двоичного кода этого числа;

3. введение кода числа в поток вслед за первым кодом своей последовательности;

4. регистрация сжатого потока данных на носитель;

при восстановлении потока цифровых данных:

5. определение в сжатом потоке кода числа равных по величине кодов;

6. дешифрация кода числа равных кодов и формирование числа сигналов выдачи первого кода соответственно количеству изъятых кодов при сжатии;

7. определение первого кода последовательности и выдача его соответственно числу изъятых кодов при сжатии.

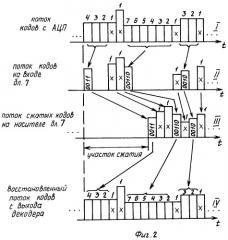

Диаграммы процесса сжатия потока данных и восстановление его для воспроизведения - на фиг.2. Число равных по величине кодов, следующих друг за другом, будет меняться, будет изменяться и коэффициент сжатия. Чем больше равных по величине кодов подряд, тем и выше степень сжатия.

Степень сжатия соответствует:

где: n-I - число равных кодов по величине, следующих друг за другом, кроме первого,

I - первый код последовательности, он всегда один.

В связи с тем, что видеосигналы кодируются 8-разрядным кодом, максимальный код числа равных кодов принимается 11111111, т.е. 255.

Сущность заявляемого способа в том, что в способе сжатия и восстановления цифровых данных, осуществляющем поточное сжатие и регистрацию сжатого потока на носитель, производится при записи сравнение значений кодов потока по величине, подсчет числа равных по величине и следующих друг за другом кодов, начиная со второго кода в последовательности, формирование двоичного кода этого числа и введение этого кода в поток за первым кодом в своей последовательности с исключением из нее подсчитанных кодов, при восстановлении производится определение в сжатом потоке кода числа равных кодов, дешифрирование его и формирование числа сигналов выдачи первого кода, равного числу изъятых кодов при сжатии.

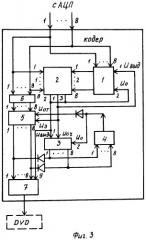

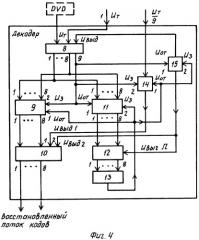

Код числа равных по величине кодов при восстановлении потока должен себя обнаруживать. Для этого он принимается 9-разрядным кодом: восемь разрядов являются информативными, а импульс девятого разряда используется в качестве служебного сигнала для опознания его при декодировании. Устройством реализации способа является кодек, содержащий кодер и декодер, выполняющие единую задачу сжатия и восстановления цифровой информации. Функциональная схема кодера - на фиг.3, декодера - на фиг.4.

Сущность изобретения устройства в том, что в кодеке, содержащем кодер и декодер, кодер выполнен из последовательно соединенных регистра, схемы сравнения, счетчика импульсов, дешифратора и блока ключей, блока элементов задержек и блока регистрации, декодер выполнен из последовательно соединенных первого регистра, первого блока ключей и второго регистра, последовательно соединенных второго блока ключей, вычитающего счетчика импульсов и дешифратора, и двух ключей.

Кодер включает (фиг.3) последовательно соединенные регистр 1, схему 2 сравнения (компаратор), счетчик 3 импульсов, дешифратор 4 и блок 5 ключей, блок 6 элементов задержек и блок 7 регистрации.

Декодер включает (фиг.4) последовательно соединенные первый регистр 8, первый блок 9 ключей и второй регистр 10, последовательно соединенные второй блок 11 ключей, вычитающий счетчик 12 импульсов и дешифратор 13, а также первый 14 и второй 15 ключи.

На вход кодера (фиг.3) поступают цифровые коды с АЦП в параллельном виде. Быстродействующие АЦП, выдающие коды видеосигналов в параллельном виде с дискретизацией 13,75 МГц и 27 МГц, приведены в патентах №2214693 (заявка №2001126388/09), №2232481 (заявка №2003108848/09). Код поступает параллельно на 1-8 входы регистра 1, на первые входы 1-8 схемы 2 сравнения и на входы блока 6 элементов задержек. Исходное состояние ключей в блоке 5 открытое. Код, поступающий в блок 6 элементов задержек, задерживается на длительность 18 нс (время срабатывания схемы 2 сравнения) и поступает через открытые ключи блока 5 на 1-8 входы блока 7 регистрации, при этом на входе 9 сигнала нет. При следовании кодов, не равных по величине, сравниваемых в блоке 2, ключи блока 5 остаются открытыми, и коды идут прямо на входы блока 7 регистрации. Схема 2 сравнения производит сравнение по величине каждого текущего и последующего кодов для выявления их равенства или неравенства. В качестве схемы 2 сравнения применяются две микросхемы 530СП1 с временем срабатывания 18 нс [3, с.279]. Схема 2 при неравенстве кодов А>В выдает сигнал на выходе 2 (в микросхеме это выход 5 [3, с.272, рис.2.190]), при равенстве кодов А=В выдает сигнал с выхода 1 (в микросхеме выход 6), при А<В выдает сигнал с выхода 3 (в микросхеме выход 7). В случае равенства кодов А=В сигнал с выхода 1 блока 2 закрывает ключи в блоке 5, поступает счетным сигналом на счетный вход счетчика 3 и на первый управляющим вход регистра 1 как сигнал Uвыд. Счетчик 3 импульсов производит счет импульсов, пока в потоке идут коды, равные по величине. В случае неравенства кодов (А>В или А<В) со схемы 2 сравнения следует сигнал с выхода 2 или 3, которые объединены, и сигналы их используются в качестве управляющих. При равенстве кодов счетчик 3 импульсов (микросхемы К531ИЕ17П с временем срабатывания 12 нс [3, c.156]) производит счет числа равных по величине кодов. Счетчик 3 8-разрядный, максимальный в нем код 11111111. При сравнении в схеме 2 неравных кодов по величине появляется сигнал с выхода 2 или 3. Этот сигнал выдает сформированный счетчиком 3 код на входы 1-8 блока 7 регистрации и импульс на вход 9 его, определяющий признак кода со счетчика 3, открывает Uот ключи в блоке 5 и обнуляет регистр 1 (вход 2). Прошедший на вход блока 7 регистрации код перед первым импульсом в счетчик 3 импульсов является первым кодом (диаграмма II на фиг.2) в последовательности равных кодов. Следующие за первым кодом коды 2, 3, 4..., равные по величине, подсчитываются счетчиком 3 до появления сигнала со схемы 2 о неравенстве кодов. Подсчитываемые счетчиком 3 коды на вход блока 7 не поступают, а исключаются из потока, т.е. за их счет и идет сжатие потока. За первым кодом последовательности равных кодов следует код со счетчика 3 импульсов на 1-8 входы блока 7 регистрации и сигнал на 9 вход блока 7. При следовании подряд равных кодов более 255 дешифратор 4 при коде 11111111 выдает сигнал, который открывает ключи в блоке 5, обнуляет регистр 1 и выдает код из счетчика 3 на 1-8 входы и импульс на 9-й вход блока 7. На входе блока 7 регистрации поток кодов имеет вид диаграммы II фиг.2. Блок 7 производит регистрацию этого потока на твердотельный носитель [2, с.326, 328], в который поток записывается байт за байтом, например в носители USB Flash Drive, x Dlicture Card, и принимает вид диаграммы III на фиг.2. С этого носителя сжатый поток может переписываться на любой диск (CD или DVD). Кодер может включаться в состав системного блока компьютера и иметь свой выход. Пропускная способность кодера определяется временем срабатывания схемы 2 сравнения 18 нс плюс время срабатывания счетчика 3 импульсов 12 нс, в сумме 30 нс, что обеспечивает максимально возможную скорость потока при параллельном следовании кодов 30 Мбайт/с. Для восстановления сжатой информации коды в последовательном виде поступают на информационный вход декодера (фиг.4) в первый регистр 8. При поступлении 8-разрядного кода заполняются 1-8 разряды регистра 8, которые выдаются сигналом Uвыд на входы блока 9 и 11 ключей. Исходное состояние ключей в блоке 9 открытое, в блоке 11 закрытое. Код через открытые ключи в блоке 9 поступает в регистр 10. Исходное состояние ключа 14 открытое, ключа 15 закрытое. С регистра 10 код выдается сигналом Uвыд1 с ключа 14, который и обнуляет регистр при выдаче. Пока приходят коды восьми разрядов в регистр 8, процесс повторяется. С приходом в регистр 8 кода из девяти разрядов, т.е. числа равных кодов, сигнал с 9-го разряда регистра 8 закрывает ключи в блоке 9, открывает ключи в блоке 11, закрывает ключ 14 и открывает ключ 15. Код числа равных кодов через открытые ключи блока 11 поступает в вычитающий счетчик 12 импульсов. Сигналы с ключа 15 поступают на счетный вход вычитающего счетчика 12 (микросхема 100ИЕ137 с временем срабатывания 10,5 нс [3, с.428], процесс вычитания в [4, c.210]) и одновременно поступает как сигнал выдачи Uвыд2 в регистр 10. Сигнал Uвыд2 выдает последний поступивший код в регистр 10, но при выдаче не обнуляет регистр 10. Поэтому пока идет работа счетчика 12 на вычитание (до появления в нем кода 00000000), с регистра 10 выдается один и тот же код, он представляет коды, изъятые при сжатии данных. С выхода декодера идет восстановленный поток данных, представленный на диаграмме IV фиг.2. Дешифратор 13 при поступлении в него кода 00000000 выдает сигнал, который закрывает блок 11 ключей, открывает блок 9 ключей, закрывает ключ 15, открывает ключ 14. Далее процессы повторяются. Пропускная способность декодера ограничивается временем срабатывания счетчика 12 10,5 нс плюс время срабатывания дешифратора 18 нс, максимально возможная скорость потока допускается 30 Мбайт/с. Декодер может включаться в состав аппаратуры, в которой уже есть кодер, но может и отдельно, например в видеопроигрыватель на его входе и в системный блок компьютера для просмотра видео с DVD, на котором информация записана через заявляемый здесь кодер.

Работа кодека.

Для сжатия цифровых данных коды с АЦП в параллельном виде поступают в кодере на входы регистра 1, первые входы схемы 2 сравнения и на входы блока 6 элементов задержек. При следовании кодов, не равных по величине, они через открытые ключи блока 5 проходят на регистрацию в блок 7 регистрации на твердотельный носитель. При следовании в потоке кодов, равных по величине, первый код этой последовательности проходит через открытые ключи блока 5 на регистрацию в блок 7, а начиная со второго кода, равные коды подсчитываются счетчиком 3 импульсов. Формируется в счетчике 3 двоичный код по числу равных кодов, который вместо изъятых одинаковых кодов регистрируется вслед за первым кодом в этой последовательности в блоке 7. При появлении в потоке другого кода, отличного по величине, процесс повторяется. Поток кодов, поступающий на вход блока 7 регистрации, представлен диаграммой II на фиг.2. Поток кодов на твердотельном носителе блока 7 представлен на диаграмме III фиг.2 и является сформированным сжатым потоком цифровых данных. Для восстановления сжатой информации в полный поток коды с блока 7 выдаются в последовательном виде на вход декодера, в котором они поступают на информационный вход регистра 8. При отсутствии сигнала на 9-м разряде регистра 8 код уже в параллельном виде поступает на входы блоков ключей 9 и 11. В исходном состоянии ключи блока 9 открыты, ключи блока 11 закрыты. Поэтому код поступает через ключи блока 9 в регистр 10, а с него выдается сигналом Uвыд1 на воспроизведение, а регистр 10 обнуляется, при наличии сигнала на 9-м разряде регистра 8 закрываются ключи в блоке 9, закрывается ключ 14, открываются ключи в блоке 11 и открывается ключ 15. Код числа равных кодов поступает в вычитающий счетчик 12 импульсов, на счетный вход которого поступают импульсы вычитания с ключа 15. С ключа 15 сигналы Uвыд2 выдают из регистра 10 содержащийся в нем код, без обнуления регистра подряд число раз, соответствующее числу изъятых кодов при сжатии. После полного вычитания в счетчике 12 дешифратор 13 по коду 00000000 выдает сигнал, который закрывает блок 11 ключей, открывает ключи в блоке 9, закрывает ключ 15 и открывает ключ 14. Далее процессы повторяются. Восстановленный первоначальный поток кодов соответствует диаграмме IV на фиг.2. Общая пропускная способность кодека составляет до 30 Мбайт/с. Предполагаемая степень сжатия потока в среднем достигает 30-60:1. Заявляемый способ пригоден для сжатия любой цифровой информации: видео, звуковой, измерительной. Устройство, реализующее способ, - кодек может использоваться в составе системного блока компьютера для записи сжатой информации на диски и воспроизведения такой же информации с них, в цифровых видеопроигрывателях и в цифровой измерительной аппаратуре, производящей непрерывное и круглосуточные измерения.

Использованные источники

1. C.H.Липатов. Я люблю создавать и копировать видеодиски. М., 2004, с.22-25, прототип.

2. В.И.Мураховский. Устройство компьютера. М., 2003, с.542, 543, 326, 328, прототип.

3. Цифровые интегральные микросхемы, справочник, Минск, 1991, с.156, 272, рис.2,190, с.279, с.428.

4. В.И.Тутевич. Телемеханика. М., 1985, с.210.

1. Способ сжатия и восстановления цифровых данных, осуществляющий поточное сжатие и регистрацию сжатого потока на носитель, отличающийся тем, что при записи производится последовательное сравнение величин кодов потока, подсчет числа равных по величине и следующих друг за другом кодов, начиная со второго кода в последовательности, формирование двоичного кода этого числа и введение его в поток вслед за первым кодом в своей последовательности с исключением из нее подсчитанных кодов, при воспроизведении - определение в сжатом потоке кода числа равных кодов, дешифрирование его, формирование числа сигналов выдачи первого кода равным числу изъятых кодов при сжатии.

2. Устройство осуществления способа - кодек, включающий кодер и декодер, отличающееся тем, что кодер содержит последовательно соединенные регистр, схему сравнения, счетчик импульсов, дешифратор и блок ключей, блок элементов задержек и блок регистрации, входы которого подключены к выходам блока ключей, входы регистра, первые входы схемы сравнения и входы блока элементов задержек поразрядно объединены и являются информационными 1-8 входами кодера, первый выход схемы сравнения подключен к счетному входу счетчика импульсов, к первому управляющему входу регистра и к второму управляющему входу блока ключей, второй и третий выходы схемы сравнения объединены и подключены к второму управляющему входу регистра, к первому управляющему входу счетчика импульсов, к первому входу блока ключей, выходы счетчика импульсов подключены к входам дешифратора и через диоды к 1-8 входам блока регистрации, девятым входом которого является второй выход схемы сравнения, а выход дешифратора подключен к второму управляющему входу счетчика импульсов и через диод подключен к первому управляющему входу блока ключей, декодер содержит последовательно соединенные первый регистр, информационный вход которого является входом декодера, первый блок ключей и второй регистр, 1-8 выходы которого являются выходами декодера, последовательно соединенные второй блок ключей, входы которого подключены к 1-8 выходам первого регистра, вычитающий счетчик импульсов и дешифратор, выход которого подключен к первому управляющему входу первого блока ключей и второму управляющему входу второго блока ключей, первый управляющий вход которого и второй управляющим вход первого блока ключей объединены и подключены к девятому выходу первого регистра, включает первый и второй ключи, сигнальные входы которых и управляющий вход первого регистра объединены и являются вторым управляющим входом декодера, первым управляющим входом которого является тактовый вход первого регистра, выход первого ключа подключен к первому управляющему входу второго регистра, выход второго ключа подключен к второму управляющему входу второго регистра и к счетному входу вычитающего счетчика импульсов, первый управляющий вход первого ключа и второй управляющий вход второго ключа объединены и подключены к выходу дешифратора, второй управляющий вход первого ключа и первый управляющий вход второго ключа подключены к девятому выходу первого регистра.