Электронная схема с контроллером и способ управления энергией

Иллюстрации

Показать всеИзобретение относится к электронным схемам, управляемым доступной энергией. Технический результат заключается в оптимизации использования доступной энергии, а значит, в оптимизации скорости вычисления с максимальным использованием энергии. Для этого средство управления электронной схемы управляет контроллером в зависимости от задачи процессора, связанных задач и энергии, доступной для контроллера. 2 н. и 11 з.п. ф-лы, 4 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к электронным схемам с контроллером и, в частности, к способу управления контроллером в таких электронных схемах.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Из-за все более распространяющегося использования безналичных платежей, передачи электронных данных по сетям общего пользования и обмена номерами кредитных карт по сетям общего пользования, существует все возрастающая необходимость в криптографических алгоритмах, которые могли бы позволить воплощать электронные подписи, задачи авторизации или шифрования. Известные криптографические алгоритмы включают в себя алгоритмы асимметричного шифрования, такие как алгоритм RSA, либо способы, основанные на эллиптических кривых, либо способы симметричного шифрования, такие как способы шифрования в соответствии со стандартами DES (стандарт кодирования данных - Data Encryption Standard) или AES (улучшенный стандарт шифрования - Advanced Encryption Standard).

Чтобы проводить вычисления, предписанные криптографическими алгоритмами, с приемлемой скоростью в повседневной жизни, применяются специально разработанные криптографические контроллеры. Такие криптографические контроллеры используются, например, в картах с микропроцессором, таких как SIM-карты или карты с образцами подписей, для осуществления платежа с помощью мобильного телефона, для банковских сделок из дома или для юридически обязательных электронных подписей. Альтернативно, криптографические контроллеры используются в компьютерах или серверах как микросхемы безопасности, чтобы проводить авторизацию или выполнять задачи шифрования, заключающиеся в безопасной передаче номеров кредитных карт, передаче электронной почты и безопасных безналичных платежах через Интернет.

К криптографическим контроллерам предъявляются требования, чтобы те отвечали высоким ожиданиям пользователей и могли утвердить себя на рынке. Чтобы гарантировать алгоритмическую безопасность к атакам извне, криптографические контроллеры должны обеспечивать значительную вычислительную мощность. Причина заключается в том, что безопасность криптографических алгоритмов, таких как известный алгоритм RSA, в общем случае решающим образом зависит от длины в битах используемого ключа, и, следовательно, криптографические контроллеры, выполняющие соответствующие криптографические алгоритмы, должны быть способны оперировать с числами максимально возможной длины. В алгоритмах RSA преимущественно используется длина ключа в 1024 бита или до 2048 бит, тогда как современные процессоры общего назначения, для сравнения, работают с 8-битными, 32-битными или, максимально, 64-битными числами.

Кроме того, криптографические контроллеры должны иметь высокую вычислительную мощность, чтобы проводить вычисления, требуемые для соответствующего криптографического алгоритма, за подходящий промежуток времени. Например, для любого пользователя было бы слишком ждать несколько минут для проверки авторизации или проведения платежа. Чтобы обеспечить высокие вычислительные мощности, известные криптографические контроллеры параллельно обрабатывают многие из проводимых вычислительных операций, чтобы увеличить скорость вычислений.

При использовании криптографических контроллеров в пластиковых картах с микропроцессором, таких как SIM-карты (модуль идентификации абонента - Subscriber Identity Module) или карты с образцами подписей, появляется дополнительная проблема, идущая от требования выпускать эти продукты с низкой стоимостью как массовые. Несмотря даже на то, что они должны за минимально возможный период времени выполнять алгоритмы, требующие значительных вычислительных операций, электронная схема не должна быть очень сложной и, следовательно, дорогой.

При разработке криптографических контроллеров появляется еще одна проблема, идущая от сосуществования множества общих криптографических алгоритмов. В случае кредитной карты, например, на рынке будет преимущественно находиться криптографический контроллер, который способен воплощать большинство стандартных криптографических алгоритмов и который, в результате, имеет широкую эксплуатационную надежность и высокую степень дружественности к пользователю. Такой "многофункциональный" криптографический контроллер, например, освобождает пользователя от необходимости носить с собой несколько карт с микропроцессором, каждая из которых предназначена для конкретного применения или конкретной криптографической процедуры. Однако в связи с многоцелевым применением такой многофункциональный криптографический контроллер должен быть способен выполнять множество вычислительных операций, используемых многими криптографическими алгоритмами, что ведет к увеличению сложности или уменьшению скорости электронной схемы.

Возможная конструкция криптографического контроллера, который имеет, с одной стороны, значительную многофункциональность и, с другой стороны, высокую скорость обработки, состоит из сочетания центрального процессора и одного или нескольких сопроцессоров, работающих параллельно, как, например, в современных ПК или в современных графических картах, и подключенных друг к другу через систему шин. Эти сопроцессоры выполняют сложные вычислительные задачи, связанные с конкретными криптографическими алгоритмами или конкретными вычислительными операциями, такими как умножение по модулю или арифметическое умножение.

Дополнительная проблема, с которой должны столкнуться криптографические контроллеры, заключается в том, что ограничена энергия. Терминалы для несущих контакты карт с микропроцессором обеспечивают ток с максимальной величиной всего несколько мА, тогда как в бесконтактных применениях и мобильных телефонах, таких как SIM-карта в мобильном телефоне, ток может быть ограничен до величины меньше 10 мА. Следовательно, скорость вычислений сопроцессоров ограничена величиной доступной энергии. Тактовая частота, с которой тактируются ЦП и криптопроцессоры, ограничена величиной доступной энергии, так как при воплощении микропроцессорного контроллера по КМОП-технологии потребление тока зависит от тактовой частоты или от частоты переключений МОП-транзисторов.

Проблемы, связанные с тем, что в обычных криптографических контроллерах используется низкая энергия, а в бесконтактных и мобильных вариантах даже меняющиеся или уменьшающиеся величины используемой энергии, с которыми сталкиваются в обычных криптографических контроллерах, состоят только в том, что такие контроллеры конструируются для использования определенного источника минимальной энергии. Весь криптографический контроллер, то есть ЦП и криптопроцессоры, тактируется фиксированными тактовыми частотами, так что энергия, требующаяся для набора тактовых частот, соответствует этой минимальной энергии. Вследствие этого работа схемы возможна только в том случае, если энергии достаточно, то есть она равна или больше минимальной энергии. Благодаря фиксированному тактированию сопроцессоров энергия, требующаяся для работы криптографического контроллера, не зависит от задачи криптографического контроллера, так что для сложных криптографических RSA-применений требуется столько же энергии, как и для менее сложных вычислений, основанных на эллиптических кривых. В случае, когда доступная энергия превышает энергию, требуемую для работы криптографического контроллера, дополнительная энергия теряется и остается неиспользованной.

Для производителей карт с микропроцессором и микросхем безопасности крайне важны криптографические контроллеры с улучшенным использованием энергии, поскольку, с одной стороны, может быть увеличена скорость вычислений, а тем самым время ожидания у терминала и дружественность к пользователю, а с другой стороны, при той же скорости вычислений могут быть уменьшены сложность схемы, а значит, и стоимость контроллера, что является преимуществом, особенно в массовом производстве.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩЕСТВА ИЗОБРЕТЕНИЯ

Задачей настоящего изобретения является создание электронной схемы с контроллером и способа управления электронной схемой таким образом, чтобы увеличить вычислительную мощность при той же самой доступной энергии.

Поставленная задача решается путем создания электронной схемы, заявленной в п.1 формулы изобретения, и способом, заявленным в п.14 формулы изобретения.

Электронная схема согласно изобретению содержит контроллер для обработки задачи процессора, а также средство определения энергии, доступной для контроллера, и средство управления контроллером в зависимости от энергии, доступной для контроллера, или в зависимости от нее.

Способ управления электронной схемой согласно изобретению, содержащей контроллер для обработки задачи процессора, заключается в определении энергии, доступной для контроллера, а также управление контроллером в функции от энергии, доступной для контроллера.

Настоящее изобретение основано на определении энергии, доступной для контроллера, например, криптографического контроллера, путем оптимизации времени вычислений при работе за счет того, что найденная энергия распределяется оптимальным образом для решающих сопроцессоров, то есть для тех, которые требуются в первую очередь для текущего задания процессора, или на другие периферийные устройства, или ЦП контроллера. Даже несмотря на то, что к электронной схеме добавлено средство нахождения энергии или эргометр, что увеличивает сложность электронной схемы, может быть достигнуто улучшение вычислительной мощности при неизменной сложности схемы, с одной стороны, и снижение сложности схемы при постоянной вычислительной мощности, с другой стороны, путем оптимального использования энергии.

В соответствии с одним вариантом выполнения изобретения управление контроллером осуществляется в функции от энергии, доступной для контроллера, причем тактовая частота контроллера, с которой контроллер работает, увеличивается, если в наличии больше энергии, и уменьшается, если в наличии меньше энергии. Иными словами, тактовая частота контроллера отслеживается в соответствии с энергией, определенной как доступная, чтобы достичь оптимального использования доступной энергии. Это является преимуществом, в частности, при использовании электронной схемы в карте с микропроцессором, предназначенной для использования в бесконтактных терминалах, поскольку в этом случае доступная энергия зависит от расстояния между картой с микропроцессором и бесконтактным терминалом, а следовательно, подвергается сильным изменениям. В случае карты с микропроцессором время ожидания на терминале снижается для владельца карты с микропроцессором из-за оптимального использования энергии, что увеличивает дружественность к пользователю карты с микропроцессором.

В соответствии с другим вариантом выполнения изобретения контроллер содержит множество периферийных устройств для выполнения связанных заданий, например, модуль УАПП (универсальный асинхронный приемопередатчик - Universal Asynchronous Receiver/Transmitter, UART) для обмена данными с терминалом, чувствительный элемент для проверки параметров, критических с точки зрения безопасности, генератор случайных чисел, фильтр или сопроцессоры для выполнения вычислительных задач, такие как модули DES, RAS или хэш-модуль, и ЦП для приведения в действие множества периферийных устройств, при этом контроллер управляется в функции от задачи процессора, связанных задач и энергии, доступной для контроллера. Управление может вестись так, что, с одной стороны, минимизируется время для вычислений, требуемое для выполнения задачи процессора, кроме того, достаточно доступной энергии. Этого можно достичь тем, что энергия, определенная как доступная, всегда используется в основном для того периферийного устройства и того сопроцессора, который требует наибольшую долю энергии или вычислительной мощности, в приложении или задаче процессора, таком как шифрование, дешифрование, авторизация или подпись в соответствии со стандартом DES, способом AES, алгоритмом RSA или способом эллиптических кривых, а также при передаче данных. Другими словами, контроллером управляют так, чтобы доступной энергии было достаточно для обработки задачи процессора контроллером, и чтобы максимальная энергия выделялась соответствующему периферийному устройству или соответствующему сопроцессору для вычисления.

В одном варианте выполнения доступная энергия распределяется между периферийным устройством и ЦП контроллера путем тактирования ЦП на низкой или медленной тактовой частоте и тактирования периферийного устройства, например сопроцессора, ответственного за умножения по модулю, на высокой или быстрой тактовой частоте вследствие небольшого объема работы, подлежащей выполнению в ЦП во время RSA-кодирования. В другом варианте выполнения доступная энергия распределяется в основном между двумя периферийными устройствами путем тактирования на высокой тактовой частоте во время кодирования по эллиптическим кривым, например, сопроцессора, в основном предусмотренного для такого кодирования, и тактирования на низкой тактовой частоте сопроцессора, требующегося для вторичных вычислений. В итоге обеспечивают сокращение времени, требуемого при оптимальном использовании энергии.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Предпочтительные варианты выполнения настоящего изобретения будут объяснены более подробно со ссылкой на приложенные чертежи, на которых:

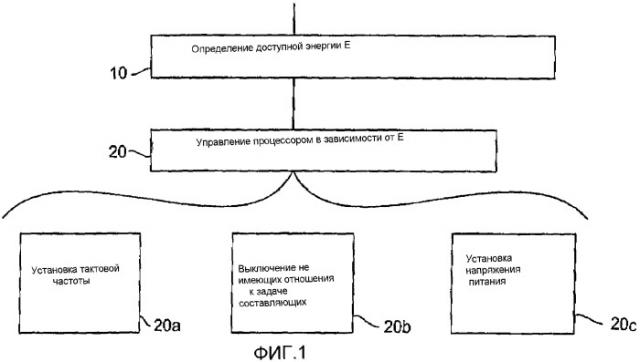

Фиг.1 изображает блок-схему алгоритма, посредством которой будет объяснено управление энергией электронной схемы, согласно изобретению;

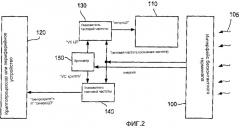

Фиг.2 - блок-схему, отображающую электронную схему в соответствии с вариантом выполнения настоящего изобретения;

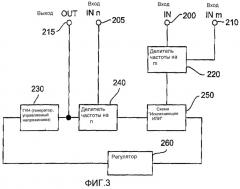

Фиг.3 - блок-схему ФАПЧ, используемую для управления тактированием в электронной схеме по фиг.2, согласно изобретению;

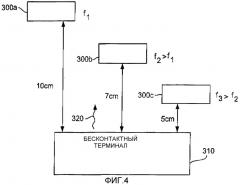

Фиг.4 - схему зависимости тактовой частоты, с которой периферийное устройство, имеющее отношение к текущему заданию процессора, может тактироваться на расстоянии от бесконтактного терминала в случае, если электронная схема собрана на карте с микропроцессором, согласно изобретению.

ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ВОПЛОЩЕНИЯ ИЗОБРЕТЕНИЯ

Хотя настоящее изобретение может быть применено ко всем электронным схемам, содержащим контроллер для обработки задачи процессора, последующее описание относится к области криптографии, и контроллер именуется криптографическим процессором или криптографическим контроллером. Однако возможен переход в другие области, такие как графические карты в переносных компьютерах (в лэптопах).

Управление энергией начинается на шаге 10 (фиг.1), где определяют доступную энергию Е для электронной схемы. Доступная энергия Е может меняться по нескольким причинам. Если электронная схема используется в картах с микропроцессором для контактных терминалов, доступная энергия может меняться, например, от терминала к терминалу или может меняться из-за изменений в качестве контакта между контактным терминалом и электронной схемой. В бесконтактных применениях доступная энергия Е зависит от расстояния между интерфейсом бесконтактного терминала карты с микропроцессором и бесконтактным терминалом, как будет подробно объяснено ниже со ссылкой на фиг.4. В мобильных применениях, таких как мобильные телефоны, лэптопы и т.п., доступная энергия может уменьшаться из-за разряда аккумулятора. Определение доступной энергии само по себе может быть проведено различными путями либо посредством различных устройств, причем в качестве меры доступной энергии могут использоваться различные параметры, такие как входное напряжение и сопряженный ток.

На шаге 20 контроллер электронной схемы управляется в функции доступной энергии Е, которая была определена на шаге 10. Как показано фигурной скобкой, контроллер в функции энергии Е может управляться различными путями, причем три возможности 20а, 20b и 20с приведены просто для примера. Первая возможность 20а управления контроллером заключается в том, что устанавливают тактовую частоту контроллера в функции от доступной энергии Е. Путем изменения тактовой частоты меняется частота переключений переключающих элементов, образующих контроллер, что выражается в изменении в потреблении тока или потреблении мощности, если контроллер выполнен, например, по КМОП технологии. Если в результате доступно меньше энергии, тактовую частоту устанавливают на более низкое значение, а если доступно больше энергии, то тактовая частота и, следовательно, скорость вычислений могут быть увеличены. В случае, когда контроллер состоит из нескольких составляющих, тактовая частота может быть установлена по отдельности для каждой составляющей, такой как ЦП, или периферийного устройства, такого как сопроцессор, как будет объяснено подробнее со ссылкой на фиг.2. Путем установки тактовых частот различных составляющих доступная энергия Е может использоваться оптимальным образом или может быть полностью распределена на все составляющие, требующиеся для текущей задачи процессора. Распределение доступной энергии по различным составляющим путем установки различных тактовых частот может быть проведено для оптимизации времени вычислений для задачи процессора, тем самым время вычислений минимизируется вследствие максимального использования доступной энергии, равно как вследствие одновременного с этим оптимального распределения энергии по отдельным составляющим.

Вторая возможность 20b управления контроллером заключается в выключении составляющих контроллера, не имеющих отношения к текущей задаче процессора. Эти не имеющие отношения к задаче составляющие процессора отключаются от напряжения питания, например, посредством дополнительных переключающих элементов, таких как полевые транзисторы с небольшим током утечки, чтобы привести их в режим ожидания.

Следующая возможность 20с управления контроллером заключается в установке напряжения питания для всего контроллера или для отдельных составляющих контроллера. В случае, когда доступная энергия падает ниже конкретного порогового значения, напряжение питания должно быть установлено на более низкое значение, например, при котором надежность работы контроллера меньше, но еще достаточная. Также напряжение питания может быть изменено для аналоговых составляющих электронной схемы, таких как аналоговая часть интерфейса бесконтактного терминала электронной схемы.

Одно основное преимущество управления энергией, описанного выше, заключается в том, что в действительности доступная энергия Е находится, а затем используется полностью для работы контроллера, по сравнению с существующими электронными схемами, разработанными для конкретного минимальной энергии питания. В этом случае часть доступной энергии, которая превышает минимальную энергию питания, может быть использована для ускоренной обработки задачи процессора. Таким образом, в обычных электронных схемах конкретные периферийные устройства, выносящие решения об общей производительности системы, работают только при фиксированных конкретных частотах, кратных тактовой частоте ЦП, причем это возможно, если доступной энергии для этого достаточно. Отдельные периферийные устройства могут тактироваться на более быстрой тактовой частоте посредством управления энергией согласно изобретению в случае излишней доступной энергии, так что доступная энергия используется оптимальным образом, то есть практически полностью.

Касательно текущей задачи процессора, такой как выполнение конкретного криптографического алгоритма, доступная энергия также может быть распределена по решающим сопроцессорам оптимальным образом для оптимизации времени вычислений, так что доступная энергия не только используется полностью, но используется оптимальным образом, благодаря чему скорость вычислений контроллера может увеличиваться при постоянной энергии, и благодаря этому может быть сокращено время ожидания у терминала для пользователя.

Ниже раскрыта электронная схема в соответствии с вариантом выполнения настоящего изобретения. Электронная схема (фиг.2) содержит криптографический процессор и расположена на карте с микропроцессором, пригодной для использования в бесконтактных терминалах.

Электронная схема содержит интерфейс 100 бесконтактного терминала, а также криптографический процессор, состоящий из ЦП 110, периферийного устройства 120, такого как криптопроцессор, генератор случайных чисел или модуль УАПП, при этом предполагается, что периферийным устройством является криптопроцессор. Как ЦП 110, так и криптопроцессор 120 каждый имеют связанные с ними умножители 130 и 140 тактовой частоты, соответственно, которые формируют тактовый сигнал "синхроЦП" и "синхрокрипт" для ЦП 110 и криптопроцессора 120, соответственно. Возможно также использовать тактовые генераторы вместо умножителей тактовой частоты. Интерфейс 100 бесконтактного терминала для преобразования электромагнитной энергии 105 от бесконтактного терминала (не показан) в электрическую энергию для питания электронной схемы, и состоящий из антенны, выпрямителя и фильтра нижних частот, подает энергию питания на все умножители 130 и 140 тактовой частоты, а также на средство 150 нахождения энергии (эргометр). Эргометр выдает сигналы управления "VC ЦП" и "VC крипто" на оба умножителя 130 и 140 тактовой частоты в функции энергии питания или энергии, доступной от интерфейса 100 бесконтактного терминала, чтобы управлять тактовыми частотами тактовых сигналов умножителей 130 и 140, при этом тактовые сигналы направляются в ЦП 110 и криптопроцессор 120.

Криптографический процессор, который состоит из ЦП 110 и криптопроцессора 120, используется для обработки конкретных задач процессора, таких как шифрование, дешифрование, авторизация или подпись, на основе стандарта DES, способа AES, алгоритма RSA или способа эллиптических кривых. Криптопроцессор 120, в свою очередь, предусмотрен для выполнения конкретной вычислительной задачи, такой как суммирование по модулю или просто суммирование, умножение, возведение в степень или обратное преобразование, вычисление хэш-значения. В качестве криптопроцессора 120 может быть использован генератор случайных чисел, модуль УАПП или датчик. В общем случае вычислительные задачи криптопроцессора 120 требуют существенно больших вычислительных усилий, чем задачи управления ЦП 110, которые состоят в приведении криптопроцессора 120 в действие посредством того сигнала, который выдает ЦП 110 для криптопроцессора 120, например, команд, данных или другой информации, через шину (не показана).

Чтобы увеличить общую скорость вычислений криптопроцессора 120, электрическая энергия, которую интерфейс 100 бесконтактного терминала получает из электромагнитной энергии 105, находится эргометром и распределяется к ЦП 110 и криптопроцессору 120 посредством умножителей 130 и 140 тактовой частоты, так что ЦП запитывается минимально возможной энергией, тогда как криптопроцессор 120 запитывается максимально возможной энергией. При распределении доступной энергии на ЦП 110 и криптопроцессор 120 факт того, что изменение тактовых частот этих составляющих в дальнейшем определяет потребление энергии этих компонентов, является в данном случае преимуществом. Если криптографический процессор выполнен по КМОП технологии, потребление энергии зависит от частоты переключения отдельных МОП-транзисторов. Следовательно, полная оптимизация доступной энергии достигается путем тактирования криптопроцессора 120 с максимально быстрой тактовой частотой, благодаря чему допускается высокая скорость вычислений.

В варианте выполнения, показанном на фиг.2, умножители 130 и 140 тактовой частоты сконструированы так, чтобы при одном и том же сигнале управления они выдавали тактовые сигналы "синхроЦП" и "синхрокрипт", тактовые частоты которых отличаются друг от друга фиксированным кратным значением n. Эргометр преобразует энергию питания от интерфейса 100 бесконтактного терминала в одинаково высокие сигналы управления "VC ЦП" и "VC крипто", так что "синхрокрипт"=n* "синхроЦП". Однако возможно также, чтобы эргометр выдавал различные сигналы управления "VC ЦП" и "VC крипто" на умножители 130 и 140 тактовой частоты. Эргометр либо сформирован как регулятор, преобразующий принятую энергию питания, которая приходит от интерфейса 100 бесконтактного терминала, в пригодные сигналы напряжения тем способом, который определяется конструкцией схемы, такой как линейный регулятор, либо включает в себя АЦП, чтобы преобразовывать энергию питания в цифровые сигналы управления "VC ЦП" и "VC крипто". В случае цифровых сигналов управления может предусматриваться просмотровая таблица, в которой сигналы "VC ЦП" и "VC крипто" хранятся для конкретных областей энергии питания, при этом сигналы "VC ЦП" и "VC крипто" гарантируют оптимальное время вычислений криптографического процессора для соответствующей области энергии питания.

Умножители 130 и 140 тактовой частоты сформированы в виде цепи ФАПЧ, позволяющей проводить умножение тактовой частоты для входной частоты на рациональные кратные значения n/m. Входная частота установлена заранее, например, тактовым сигналом, выработанным интерфейсом 100 бесконтактного терминала. Умножители 130 и 140 тактовой частоты последовательно преобразуют этот тактовый сигнал с входной частотой fвх в тактовый сигнал с выходной частотой fвых=n/m×f0.

Блок-схема умножителей 130 и 140 тактовой частоты показана на фиг.3. Как можно видеть, каждый умножитель тактовой частоты имеет вход IN 200, куда подается тактовый сигнал входной частоты fвх, входы INn и INm, куда подаются значения n числителя и m знаменателя в рациональном кратном значении между входной частотой fвх и выходной частотой fвых, и выход OUT, где выдается тактовый сигнал с тактовой частотой fвых. В дополнение к делителю 220 частоты схема включает в себя цепь ФАПЧ, состоящую из генератора 230, управляемого напряжением (ГУН), делителя 240 частоты, схемы 250 "Исключающее ИЛИ" и регулятора 260. Вход делителя 220 частоты соединен со входом IN 200, а еще один вход соединен со входом INm 210. На выходе делитель 220 частоты выдает выходной сигнал частоты fвх/m, причем этот выход соединен со входом схемы 250 "Исключающее ИЛИ". Еще один вход схемы 250 "Исключающее ИЛИ" соединен с выходом делителя 240 частоты, два входа которого соединены со входом INn 205 и выходом ГУНа 230 соответственно. Вход ГУНа 230 соединен с выходом схемы 230 "Исключающее ИЛИ" через регулятор 260. Выход ГУНа 230 далее соединен с выходом OUT 215.

Ниже будет описан режим работы схемы.

Входы INn и INm управления, которые управляются сигналами управления "VC ЦП" и "VC крипто" (фиг.2), могут использоваться для установки разделяющих коэффициентов n и m (n, m ∈ 1,2,3...), с которыми делители 220 и 240 частоты делят частоты входного тактового сигнала на входе 200 и выходного тактового сигнала генератора 230. Только если выходной сигнал ГУНа 230 имеет выходную частоту fвых=n/m×f0, на оба входа схемы 250 "Исключающее ИЛИ" подаются идентичные сигналы с одинаковыми тактовой частотой fвх/m и фазой. Если это не имеет места, ГУН 230 повторно регулируется схемой 250 "Исключающее ИЛИ" совместно с регулятором 260, чтобы достигнуть желаемого коэффициента разделения между входным тактовым сигналом и выходным тактовым сигналом. Следовательно, тактовый сигнал, поданный на выход OUT, имеет желаемую частоту fвых.

Ниже проиллюстрирован предпочтительный вариант выполнения в картах с микропроцессором для бесконтактных терминалов.

На фиг.4 показана карта с микропроцессором, на которой расположена электронная схема (фиг.2), в трех положениях 300а, 300b и 300с относительно бесконтактного терминала 310, испускающего электромагнитное излучение 320 определенной частоты. Как показано двойными стрелками, различные положения 300а и 300с находятся на разных расстояниях, то есть 10 см, 7 см и 5 см соответственно от бесконтактного терминала 310. Поскольку доступная энергия Е, которая получается из электромагнитного излучения 320 в интерфейсе 100 бесконтактного терминала (фиг.2) электронной схемы, зависит от расстояния d от карты с микропроцессором до бесконтактного терминала 310 для электронной схемы, то тактовые частоты f1, f2 и f3 соответственно для контроллера электронной схемы могут быть установлены в различных положениях 300а, 300b и 300с. При этом тактовые частоты могут быть выше или ниже в зависимости от расстояния карты с микропроцессором до бесконтактного терминала 310. Если карта еще более удаляется от терминала 310, то электронной схеме доступно меньше энергии, так что тактовая частота должна быть ниже. Если карта придвигается ближе к терминалу 310, то доступно больше энергии, так что контроллер может тактироваться с более высокой тактовой частотой. В этом случае тактовая частота всегда регулируется по доступной энергии, так что если доступно больше энергии, то становится возможной меньшая величина времени для вычислений. В противоположность этому, в существующих криптографических решениях на картах с микропроцессором установлено фиксированное потребление энергии, такое как фиксированная тактовая частота, например, для конкретного максимального расстояния от карты с микропроцессором до бесконтактного терминала 310, что является компромиссом между максимальным диапазоном расстояний и максимальной энергией для вычислений. Далее, работа криптографического процессора была возможна только в этом диапазоне, а любое избыточное питание не преобразовывалось в случае меньших расстояний.

Для упрощения описания выше был описан только тот случай, в котором криптографический процессор состоит из ЦП и периферийного устройства или криптопроцессора. В гораздо более типичных случаях криптографический процессор будет состоять из нескольких периферийных устройств и криптопроцессоров. В этом случае доступная энергия может распределяться по сопроцессорам, например так, что минимальное время вычислений будет достигнуто при максимальном использовании энергии. Кроме того, это достигается тем, что текущая задача процессора и/или различные вычислительные задачи сопроцессоров и связанные с ними задачи остальных периферийных устройств принимаются во внимание при распределении доступной энергии (которая найдена эргометром), по сопроцессорам и ЦП. Доступная энергия будет затем всегда использоваться для того или для тех сопроцессора/ов, который/ые более всего используются при решении задачи процессора. В случае, когда должна проводиться авторизация, криптопроцессору назначают максимальную энергию, тогда как ЦП и оставшимся сопроцессорам назначают лишь минимальный объем доступной энергии. Аналогично, доступная энергия распределяется с самой быстрой тактовой частотой, например, для DES модуля в задаче шифрования и для хэш-модуля при вычислении хэш-значения.

Сопроцессоры, которые не имеют отношения к текущей задаче процессора, даже могут быть полностью выключены или установлены в режим ожидания путем их отключения от напряжения питания, чтобы избежать утечки тока.

Оптимальное распределение доступной энергии нескольким сопроцессорам может быть достигнуто так, что каждому сопроцессору назначается умножитель тактовой частоты, на фиг.2 показано, что криптопроцессору 120 назначен умножитель 140 тактовой частоты. В простейшем случае, например, когда сопроцессоры последовательно используются или приводятся в действие ЦП при проведении задачи процессора, ЦП может работать с тактовой частотой fЦП, тогда как сопроцессоры, в текущий момент не требующиеся для задачи процессора, могут быть выключены или работать с частотой fЦП. При этом только тот криптопроцессор, который в текущий момент требуется для выполнения задачи, тактируется с более высокой тактовой частотой, которая установлена так, что доступная энергия используется максимально. Другими словами, оптимизация скорости вычислений и максимальное использование энергии достигаются тем, что тактовая частота сопроцессора, который в текущий момент в основном используется процессором, увеличивается или уменьшается таким образом, что сопроцессор тактируется с максимально возможной тактовой частотой, при этом остающейся доступной энергии достаточно для работы остальных необходимых составляющих.

В случае параллельной работы криптопроцессоров распределение доступной энергии на криптопроцессоры может проводиться обращением к просмотровой таблице, где хранится оптимальный набор тактовых частот для криптопроцессоров, соответственно, для определенных областей доступной энергии и для конкретных приложений, поддерживаемых криптографическим процессором. Каждый набор тактовых частот будет распределять доступную энергию, связанную по существу с теми криптопроцессорами, связанные вычислительные задачи которых требуются в связанном приложении. Кроме того, тактовые частоты в каждом наборе определятся так, что доступная энергия, с которой связан этот набор, необходимым образом используется полностью. Поскольку часто некоторые криптопроцессоры связаны с одним и тем же приложением или выполняют вычислительные задачи, требующиеся в одном и том же приложении, эти криптопроцессоры могут тактироваться с одной и той же тактовой частотой или с помощью цепи ФАПЧ, либо могут всегда тактироваться с фиксированными коэффициентами тактовой частоты друг по отношению к другу в виде дерева тактовых частот, тем самым количество тактовых частот, подлежащих управлению, уменьшается.

Даже несмотря на то, что выше было описано, что умножители тактовых частот или ФАПЧ, которые обеспечивают простые рациональные коэффициенты разделения, используются для установления тактовой частоты тактовых сигналов для ЦП и криптопроцессора(ов), точно так же можно использовать вместо них генераторы, которыми можно управлять независимо друг от друга, так что далее между тактовыми частотами составляющих контроллера возможны относительно простые коэффициенты разделения. Преимущество, достигаемое по сравнению с описанным ранее случаем с умножителями тактовых частот, заключается в том, что доступная энергия может быть использована еще лучше, поскольку тактовые частоты могут быть не только установлены на полностью рациональные кратные значения, но также могут быть установлены как относительно простые по отношению друг к другу. Такая максимизация использования энергии привлекательна, в частности, в областях применения, где доступная энергия очень ограничена, как в случае с бесконтактными и мобильными применениями. Использование конкретных генераторов для всех криптопроцессоров или для группы криптопроцессоров требует, однако, синхронизации криптопроцессоров по запросу, поскольку они тактируются асинхронно с ЦП. Все входы и выходы в главном интерфейсе криптопроцессоров по запросу, следовательно, должны будут синхронизироваться с помощью пригодного средства синхронизации, состоящего, например, из двух триггеров синхронизации, включенных последовательно.

Наконец, следует отметить, что возможен любой тип контроллеров, с сопроцессором или без него, хотя со ссылкой на фиг.2 было описано, что контроллер электронной схемы включает в себя ЦП и сопроцессор. Управление питанием ко всему контроллеру выражается в большинстве преимуществ настоящего изобретения, которые были описаны выше.

Следует отметить, что электронная схема может быть расположена на печатной плате и быть интегрирована в микропроцессор. Аналогично, контроллер может содержать отдельные составляющие, которые расположены на печатной плате или могут быть интегрированы в единый микропроцессор.

Хотя настоящее изобретение было описано для бесконтактного применения, изобретение применимо к приложениям с контактными терминалами или к мобильным приложениям. В этом случае интерфейс контактного терминала может быть заменен единым контактом.

Далее следует отметить, что хотя выше описано, что умножители тактовых частот аппаратно встроены в электронную схему, они могут подключаться к электронной схеме по проводному или беспроводному соединению. Умножители тактовых частот или генераторы могут предусматриваться в соответствующем терминале и взаимодействовать с электронной схемой только при использовании карты с микропроцессором на терминале.

С