Линия радиосвязи с повышенной скрытностью передаваемой информации

Иллюстрации

Показать всеИзобретение относится к области передачи дискретной информации и может быть использовано в радиоканалах для осуществления передачи информации в космических и наземных системах связи, использующих шумоподобные сигналы. Технический результат - повышение скрытности передаваемой информации. Для этого в устройство, содержащее в передающей части источник информации, широтно-импульсный модулятор, фазовый модулятор, балансный модулятор, усилитель мощности, генератор фазоманипулированного сигнала, генератор несущей частоты, синхронизатор передатчика и передающую антенну; в приемной части - приемную антенну, смеситель, усилитель промежуточной частоты, коррелятор, демодулятор, гетеродин, генератор опорного фазоманипулированного сигнала, синхронизатор приемника и получатель информации, введено в передающую и в приемную части по коммутатору, по дешифратору, по счетному триггеру, по оперативному запоминающему устройству и по формирователю адреса оперативного запоминающего устройства. 2 ил.

Реферат

Изобретение относится к области передачи дискретной информации и может быть использовано в радиоканалах для осуществления передачи информации в космических и наземных системах связи, использующих шумоподобные сигналы.

Известны системы радиосвязи с шумоподобными сигналами, например по а.с. 651492, которая служит для передачи дискретной информации. Основным недостатком этой системы является невысокая скрытность передаваемой информации.

Известна также радиотелефонная система связи с фазоманипулированными широкополосными сигналами (см. Варакин Л.Е. "Системы связи с шумоподобными сигналами", М., "Р и С", 1985 г., стр.16, рис.1.7), основным недостатком которой является невысокая скрытность передаваемой информации.

Наиболее близким по технической сущности к заявляемому устройству является устройство, приведенное в книге Варакина Л.Е. "Системы связи с шумоподобными сигналами", М., "Р и С", 1985 г., стр.18, рис.1.9, взятое за прототип.

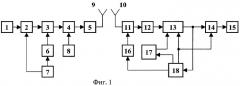

Функциональная схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

передающая часть:

1 - источник информации;

2 - широтно-импульсный модулятор (ШИМ);

3 - фазовый модулятор;

4 - балансный модулятор;

5 - усилитель мощности;

6 - генератор фазоманипулированного (ФМ) сигнала (генератор псевдослучайной последовательности);

7 - синхронизатор передатчика;

8 - генератор несущей частоты;

9 - передающая антенна;

приемная часть:

10 - приемная антенна;

11 - смеситель;

12 - усилитель промежуточной частоты;

13 - коррелятор;

14 - демодулятор;

15 - получатель информации;

16 - гетеродин;

17 - генератор опорного фазоманипулированного (ФМ) сигнала;

18 - синхронизатор приемника.

Устройство-прототип состоит из передающей и приемной части.

Передающая часть содержит последовательно соединенные источник информации 1, который является входом устройства, широтно-импульсный модулятор 2, фазовый модулятор 3, балансный модулятор 4 и усилитель мощности 5, выход которого соединен с передающей антенной 9. Кроме того, содержит синхронизатор передатчика 7, первый выход которого соединен со вторым входом широтно-импульсного модулятора 2, а второй выход - через генератор фазоманипулированного (ФМ) сигнала 6 соединен со вторым входом фазового модулятора 3; а также содержит генератор несущей частоты 8, выход которого соединен со вторым входом балансного модулятора 4.

Приемная часть содержит последовательно соединенные приемную антенну 10, смеситель 11, усилитель промежуточной частоты 12, коррелятор 13, демодулятор 14 и получатель информации 15, который является выходом устройства. Кроме того, содержит синхронизатор приемника 18, первый выход которого через гетеродин 16 соединен со вторым входом смесителя 11, а второй выход синхронизатора приемника 18 соединен со вторыми входами демодулятора 14 и коррелятора 13, выход которого соединен с входом синхронизатора приемника 18, третий выход которого через генератор опорного ФМ сигнала 17 соединен с третьим входом коррелятора 13.

Устройство-прототип работает следующим образом.

От источника информации 1 телефонное сообщение поступает на первый вход широтно-импульсного модулятора (ШИМ) 2, с выхода которого ШИМ сигнал поступает на первый вход фазового модулятора 3, на второй вход которого поступает фазоманипулированный широкополосный сигнал (ФМ ШПС) с выхода генератора ФМ сигнала 6. Работой широтно-импульсного модулятора 2 и генератора ФМ сигнала 6 управляет синхронизатор передатчика 7, который формирует необходимые частоты и управляющие сигналы.

ФМ сигнал с выхода фазового модулятора 3, содержащий информацию, поступает на первый вход балансного модулятора 4, на второй вход которого поступает ФМ сигнал с выхода генератора несущей частоты 8. В балансном модуляторе 4 осуществляется балансная модуляция ФМ сигнала с несущей частотой. В усилителе мощности 5 ФМ сигнал усиливается до необходимой величины и затем через антенну 9 излучается в пространство.

Принятый приемной антенной 10 сигнал поступает на смеситель 11, где переносится с помощью гетеродина 16 на промежуточную частоту, усиливается в усилителе промежуточной частоты 12 и подается на первый вход коррелятора 13, на третий вход которого подаются импульсы с генератора опорного ФМ сигнала 17. В корреляторе 13 производится оптимальная обработка сигнала, в результате чего на выходе коррелятора 13 формируется телефонное сообщение в виде ШИМ сигнала, которое подается на вход синхронизатора приемника 18 и первый вход демодулятора 14, где выделяется информационная составляющая. С выхода демодулятора 14 принятое телефонное сообщение подается получателю информации 15. Синхронизатор приемника 18, управляя гетеродином 16, осуществляет поиск ФМ сигнала по частоте и по времени, а затем поддерживает синхронизм в приемной части, управляя работой генератора опорного ФМ сигнала 17, коррелятора 13 и демодулятора 14.

Недостатком устройства-прототипа является малая скрытность передаваемой информации, т.к. информация в эфир передается в незащищенном виде.

Для устранения указанного недостатка в линию радиосвязи с повышенной скрытностью передаваемой информации, содержащую в передающей части: последовательно соединенные источник информации, который является входом устройства, широтно-импульсный модулятор, фазовый модулятор, балансный модулятор и усилитель мощности, выход которого соединен с передающей антенной, а также содержащую генератор несущей частоты, выход которого соединен со вторым входом балансного модулятора, и синхронизатор передатчика, первый выход которого соединен со вторым входом широтно-импульсного модулятора, а второй выход синхронизатора передатчика соединен с входом генератора фазоманипулированного сигнала; в приемной части: последовательно соединенные приемную антенну, смеситель, усилитель промежуточной частоты, коррелятор, демодулятор и получатель информации, который является выходом устройства, а также содержащую синхронизатор приемника, первый выход которого через гетеродин соединен со вторым входом смесителя, второй выход синхронизатора приемника соединен со вторыми входами демодулятора и коррелятора, выход которого соединен с входом синхронизатора приемника, третий выход которого соединен с входом генератора опорного фазоманипулированного сигнала, введены в передающую часть: коммутатор передатчика, оперативное запоминающее устройство передатчика, формирователь адреса оперативного запоминающего устройства передатчика, счетный триггер передатчика и дешифратор передатчика, при этом второй выход синхронизатора передатчика соединен со счетным входом формирователя адреса оперативного запоминающего устройства передатчика, выход которого соединен с адресным входом оперативного запоминающего устройства передатчика, последовательный выход генератора фазоманипулированного сигнала соединен с первым информационным входом коммутатора передатчика и информационным входом оперативного запоминающего устройства передатчика, выход которого соединен со вторым информационным входом коммутатора передатчика, выход которого соединен со вторым входом фазового модулятора, n параллельных выходов генератора фазоманипулированного сигнала соединены соответственно с n входами дешифратора передатчика, выход которого соединен со счетным входом счетного триггера передатчика, управляющий вход которого является управляющим входом передающей части устройства, прямой выход счетного триггера передатчика соединен с первыми управляющими входами формирователя адреса оперативного запоминающего устройства передатчика, оперативного запоминающего устройства передатчика и коммутатора передатчика, инверсный выход счетного триггера передатчика соединен со вторыми управляющими входами формирователя адреса оперативного запоминающего устройства передатчика, оперативного запоминающего устройства передатчика и коммутатора передатчика; введены в приемную часть: коммутатор приемника, оперативное запоминающее устройство приемника, формирователь адреса оперативного запоминающего устройства приемника, счетный триггер приемника и дешифратор приемника, причем третий выход синхронизатора приемника соединен со счетным входом формирователя адреса оперативного запоминающего устройства приемника, выход которого соединен с адресным входом оперативного запоминающего устройства приемника, последовательный выход генератора опорного фазоманипулированного сигнала соединен с первым информационным входом коммутатора приемника и информационным входом оперативного запоминающего устройства приемника, выход которого соединен со вторым информационным входом коммутатора приемника, выход которого соединен с третьим входом коррелятора, n параллельных выходов генератора опорного фазоманипулированного сигнала соединены соответственно с n входами дешифратора приемника, выход которого соединен со счетным входом счетного триггера приемника, управляющий вход которого является управляющим входом приемной части устройства, прямой выход счетного триггера приемника соединен с первыми управляющими входами формирователя адреса оперативного запоминающего устройства приемника, оперативного запоминающего устройства приемника и коммутатора приемника, инверсный выход счетного триггера приемника соединен со вторыми управляющими входами формирователя адреса оперативного запоминающего устройства приемника, оперативного запоминающего устройства приемника и коммутатора приемника.

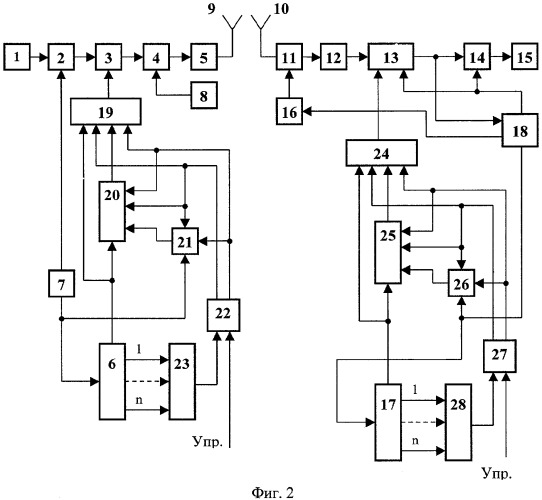

На фиг.2 приведена функциональная схема предлагаемого устройства, где введены обозначения:

передающая часть:

1 - источник информации;

2 - широтно-импульсный модулятор (ШИМ);

3 - фазовый модулятор;

4 - балансный модулятор;

5 - усилитель мощности;

6 - генератор фазоманипулированного (ФМ) сигнала (генератор псевдослучайной последовательности);

7 - синхронизатор передатчика;

8 - генератор несущей частоты;

9 - передающая антенна;

19 - коммутатор передатчика;

20 - оперативное запоминающее устройство (ОЗУ) передатчика;

21 - формирователь адреса оперативного запоминающего устройства (ФА ОЗУ) передатчика;

22 - счетный триггер передатчика;

23 - дешифратор передатчика;

приемная часть:

10 - приемная антенна;

11 - смеситель;

12 - усилитель промежуточной частоты;

13 - коррелятор;

14 - демодулятор;

15 - получатель информации;

16 - гетеродин;

17 - генератор опорного фазоманипулированного (ФМ) сигнала (генератор опорной псевдослучайной последовательности);

18 - синхронизатор приемника;

24 - коммутатор приемника;

25 - оперативное запоминающее устройство (ОЗУ) приемника;

26 - формирователь адреса оперативного запоминающего устройства (ФА ОЗУ) приемника;

27 - счетный триггер приемника;

28 - дешифратор приемника.

Предлагаемое устройство состоит из передающей и приемной части.

Передающая часть устройства содержит последовательно соединенные источник информации 1, который является входом устройства, широтно-импульсный модулятор (ШИМ) 2, фазовый модулятор 3, балансный модулятор 4 и усилитель мощности 5, выход которого соединен с передающей антенной 9, при этом второй вход балансного модулятора 4 соединен с выходом генератора несущей частоты 8. Первый выход синхронизатора передатчика 7 соединен со вторым входом ШИМ 2, а второй выход синхронизатора передатчика 7 соединен со счетным входом формирователя адреса оперативного запоминающего устройства (ФА ОЗУ) передатчика 21, выход которого соединен с адресным входом оперативного запоминающего устройства (ОЗУ) передатчика 20. Кроме того, второй выход синхронизатора передатчика 7 соединен с входом генератора фазоманипулированного (ФМ) сигнала 6, n параллельных выходов которого соединены соответственно с n входами дешифратора передатчика 23, выход которого соединен со счетным входом счетного триггера передатчика 22, управляющий вход которого является управляющим входом передающей части устройства. Последовательный выход генератора фазоманипулированного (ФМ) сигнала 6 соединен с первым информационным входом коммутатора передатчика 19 и информационным входом ОЗУ передатчика 20, выход которого соединен со вторым информационным входом коммутатора передатчика 19, выход которого соединен со вторым входом фазового модулятора 3. Прямой выход счетного триггера передатчика 22 соединен с первыми управляющими входами ФА ОЗУ передатчика 21, ОЗУ передатчика 20 и коммутатора передатчика 19. Инверсный выход счетного триггера передатчика 22 соединен со вторыми управляющими входами ФА ОЗУ передатчика 21, ОЗУ передатчика 20 и коммутатора передатчика 19.

Приемная часть устройства содержит последовательно соединенные приемную антенну 10, смеситель 11, усилитель промежуточной частоты 12, коррелятор 13, демодулятор 14 и получатель информации 15, который является выходом устройства. Первый выход синхронизатора приемника 18 через гетеродин 16 соединен со вторым входом смесителя 11. Второй выход синхронизатора приемника 18 соединен со вторыми входами демодулятора 14 и коррелятора 13, выход которого соединен с входом синхронизатора приемника 18, третий выход которого соединен со счетным входом ФА ОЗУ приемника 26, выход которого соединен с адресным входом ОЗУ приемника 25. Кроме этого, третий выход синхронизатора приемника 18 соединен с входом генератора опорного ФМ сигнала 17, n параллельных выходов которого соединены соответственно с n входами дешифратора приемника 28, выход которого соединен со счетным входом счетного триггера приемника 27, управляющий вход которого является управляющим входом приемной части устройства. Последовательный выход генератора опорного ФМ сигнала 17 соединен с первым информационным входом коммутатора приемника 24 и информационным входом ОЗУ приемника 25, выход которого соединен со вторым информационным входом коммутатора приемника 24, выход которого соединен с третьим входом коррелятора 13. Прямой выход счетного триггера приемника 27 соединен с первыми управляющими входами ФА ОЗУ приемника 26, ОЗУ приемника 25 и коммутатора приемника 24. Инверсный выход счетного триггера приемника 27 соединен со вторыми управляющими входами ФА ОЗУ приемника 26, ОЗУ приемника 25 и коммутатора приемника 24.

Работает предлагаемое устройство следующим образом.

От источника информации 1 телефонное сообщение поступает на первый вход ШИМ 2, на второй вход которого поступают импульсы с первого выхода синхронизатора передатчика 7. С выхода блока 2 ШИМ сигнал поступает на первый вход фазового модулятора 3, на второй вход которого с выхода коммутатора передатчика 19 поступает фазоманипулированный широкополосный сигнал, представляющий собой чередование прямой и обратной псевдослучайных последовательностей (ПСП). В качестве ПСП можно использовать М-последовательность максимальной длины (см. Варакин Л.Е. "Системы связи с шумоподобными сигналами", М., "Р и С", 1985 г., стр.49).

Прямая ПСП формируется на последовательном выходе генератора ФМ сигнала 6, управляемого тактовыми импульсами, поступающими на его вход со второго выхода синхронизатора передатчика 7, и подается на первый информационный вход коммутатора передатчика 19. Обратная ПСП формируется из прямой ПСП путем переворота, то есть тот элемент ПСП, который был первый, становится последним, а тот элемент ПСП, который был последний, становится первым. Переворот ПСП производится следующим образом. С последовательного выхода генератора ФМ сигнала 6 ПСП поступает на информационный вход ОЗУ передатчика 20, которое установлено на запись. Режим записи или считывания ОЗУ передатчика 20 обеспечивается состоянием выходов счетного триггера передатчика 22, на управляющий вход которого подается сигнал лог."1" с управляющего входа приемной части, разрешающий режим засекречивания, то есть чередование прямой и обратной ПСП, а на счетный вход - сигнал с выхода дешифратора передатчика 23, формируемый следующим образом.

С n параллельных выходов генератора ФМ сигнала 6 параллельный двоичный код ПСП (например, при n равном 10 будет М-последовательность длиной 1023) поступает соответственно на n входов дешифратора передатчика 23, настроенного на заданное число (в данном случае, число 1023). При этом на выходе дешифратора передатчика 23 появится сигнал лог."1", определяющий временное переключение счетного триггера передатчика 22, имеющего прямой и инверсный выходы.

Если на прямом выходе счетного триггера передатчика 22 сформируется сигнал уровня лог."1", то он, поступив на первый управляющий вход ОЗУ передатчика 20, устанавливает его в режим записи. При этом на инверсном выходе счетного триггера передатчика 22 и, следовательно, на втором управляющем входе ОЗУ передатчика 20 будет сигнал уровня лог."0".

Кроме того, выходные сигналы счетного триггера передатчика 22 управляют ФА ОЗУ передатчика 21. При поступлении сигнала уровня лог."1" с прямого выхода счетного триггера передатчика 22 на первый управляющий вход ФА ОЗУ передатчика 21 в нем происходит формирование адреса записи путем сложения тактовых импульсов, поступающих на его счетный вход со второго выхода синхронизатора передатчика 7. При этом на инверсном выходе счетного триггера передатчика 22 и, следовательно, на втором управляющем входе ФА ОЗУ передатчика 21 будет сигнал уровня лог."0".

Если на инверсном выходе счетного триггера передатчика 22 сформируется сигнал уровня лог."1", то он, поступив на второй управляющий вход ОЗУ передатчика 20, устанавливает его в режим считывания. При этом на прямом выходе счетного триггера передатчика 22 и, следовательно, на первом управляющем входе ОЗУ передатчика 20 будет сигнал уровня лог."0". При поступлении сигнала уровня лог."1" с инверсного выхода счетного триггера передатчика 22 на второй управляющий вход ФА ОЗУ передатчика 21 в нем происходит формирование адреса считывания путем вычитания тактовых импульсов, поступающих на его счетный вход. Адрес при считывании с ОЗУ передатчика 20 задается таким, что информация считывается в обратном порядке.

Кроме того, сигналы с прямого и обратного выходов счетного триггера передатчика 22 поступают соответственно на первый и второй управляющие входы коммутатора передатчика 19, который коммутирует на свой выход прямую ПСП, если на его первый управляющий вход подается сигнал лог."1" с прямого выхода счетного триггера передатчика 22, или ПСП с обратным порядком следования импульсов, если на его второй управляющий вход подается сигнал лог."1" с инверсного выхода счетного триггера передатчика 22.

ФМ сигнал с выхода фазового модулятора 3, содержащий информацию, поступает на первый вход балансного модулятора 4, на второй вход которого поступает сигнал с выхода генератора несущей частоты 8. В балансном модуляторе 4 осуществляется балансная модуляция ФМ сигнала с несущей частотой. С выхода балансного модулятора 4 ФМ сигнал поступает на вход усилителя мощности 5, где усиливается до необходимой величины и затем через антенну 9 излучается в пространство.

Принятый приемной антенной 10 сигнал поступает на смеситель 11, где переносится с помощью гетеродина 16 на промежуточную частоту, усиливается в усилителе промежуточной частоты 12 и подается на первый вход коррелятора 13, на третий вход которого поступает фазоманипулированный широкополосный сигнал (ФМ ШПС) с выхода коммутатора приемника 24, представляющий собой чередование прямой и обратной ПСП. Прямая ПСП формируется на последовательном выходе генератора опорного ФМ сигнала 17, управляемого тактовыми импульсами, подаваемыми на его вход с третьего выхода синхронизатора приемника 18, и подается на первый информационный вход коммутатора приемника 24. Обратная ПСП формируется из прямой ПСП следующим образом. С последовательного выхода генератора опорного ФМ сигнала 17 ПСП поступает на информационный вход ОЗУ приемника 25, которое установлено на запись. Режим записи или считывания ОЗУ приемника 25 обеспечивается состоянием выходов счетного триггера приемника 27, на управляющий вход которого подается сигнал лог."1" с управляющего входа приемной части, разрешающий режим засекречивания, то есть чередование прямой и обратной ПСП, а на счетный вход - сигнал с выхода дешифратора приемника 28, формируемый следующим образом.

С n параллельных выходов генератора опорного фазоманипулированного (ФМ) сигнала 17 параллельный двоичный код ПСП (как и в передающей части, это М-последовательность длиной 1023) поступает соответственно на n входов дешифратора приемника 28, настроенного на заданное число (в данном случае, число 1023). При этом на выходе дешифратора приемника 28 появится сигнал лог."1", определяющий временное переключение счетного триггера приемника 27.

Если на прямом выходе счетного триггера приемника 27 сформируется сигнал уровня лог."1", то он, поступив на первый управляющий вход ОЗУ приемника 25, установит его в режим записи. При этом на инверсном выходе счетного триггера приемника 27 и, следовательно, на втором управляющем входе ОЗУ приемника 25 будет сигнал уровня лог."0".

Кроме того, выходные сигналы счетного триггера приемника 27 управляют ФА ОЗУ приемника 26, на счетный вход которого подаются тактовые импульсы с третьего выхода синхронизатора приемника 18. При поступлении сигнала уровня лог."1" с прямого выхода счетного триггера приемника 27 на первый управляющий вход ФА ОЗУ приемника 26 в нем происходит формирование адреса записи путем сложения тактовых импульсов, поступающих на его счетный вход. При этом на инверсном выходе счетного триггера приемника 27 и, следовательно, на втором управляющем входе ФА ОЗУ приемника 26 будет сигнал уровня лог."0".

Если на инверсном выходе счетного триггера приемника 27 сформируется сигнал уровня лог."1", то он, поступив на второй управляющий вход ОЗУ приемника 25, установит его в режим считывания. При этом на прямом выходе счетного триггера приемника 27 и, следовательно, на первом управляющем входе ОЗУ приемника 25 будет сигнал уровня лог."0". При поступлении сигнала уровня лог."1" с инверсного выхода счетного триггера приемника 27 на второй управляющий вход ФА ОЗУ приемника 26 в нем происходит формирование адреса считывания путем вычитания тактовых импульсов, поступающих на его счетный вход. Адрес при считывании с ОЗУ приемника 25 задается таким, что информация считывается в обратном порядке.

Кроме того, сигналы с прямого и обратного выходов счетного триггера приемника 27 поступают соответственно на первый и второй управляющие входы коммутатора приемника 24, который коммутирует на свой выход прямую ПСП, если на его первый управляющий вход подается сигнал лог."1" с прямого выхода счетного триггера приемника 27, или ПСП с обратным порядком следования импульсов, если на его второй управляющий вход подается сигнал лог."1" с инверсного выхода счетного триггера приемника 27.

В корреляторе 13 производится оптимальная обработка сигнала, в результате чего на выходе коррелятора 13 формируется телефонное сообщение в виде ШИМ сигнала, которое подается на вход синхронизатора приемника 18 и первый вход демодулятора 14, где выделяется информационная составляющая. С выхода демодулятора 14 принятое телефонное сообщение подается получателю информации 15. Синхронизатор приемника 18, управляя гетеродином 16, осуществляет поиск ФМ сигнала по частоте и по времени, а затем поддерживает синхронизм в приемной части, управляя работой коррелятора 13 и демодулятора 14. Причем поиск по времени осуществляется до тех пор, пока не произойдет совпадение прямой и обратной ПСП на первом и третьем входах коррелятора 13.

В качестве генератора ФМ сигнала 6 и генератора опорного ФМ сигнала 17 может быть использован генератор М-последовательности максимальной длины, выполненный на двоичных триггерах, приведенный на рис.3.18, стр.49. книги Варакина Л.Е. "Системы связи с шумоподобными сигналами", М., "Р и С", 1985 г.

Формирователь адреса ОЗУ передатчика 21 и формирователь адреса ОЗУ приемника 26 могут быть выполнены на основе счетчика с управлением сложением и вычитанием (реверсивного счетчика), приведенного на стр.249 книги Г.И. Пухальского, Т.Я. Новосельцевой "Проектирование дискретных устройств на интегральных микросхемах", М., "Р и С", 1999 г.

Реализация остальных блоков заявляемого устройства также не вызывает никаких затруднений, так как описания их широко опубликованы в технической литературе.

Таким образом, применение в предлагаемом устройстве для передачи информации чередования прямой и обратной ПСП в значительной степени позволило повысить скрытность передаваемой информации.

Линия радиосвязи с повышенной скрытностью передаваемой информации, содержащая в передающей части последовательно соединенные источник информации, который является входом устройства, широтно-импульсный модулятор, фазовый модулятор, балансный модулятор и усилитель мощности, выход которого соединен с передающей антенной, а также содержащая генератор несущей частоты, выход которого соединен со вторым входом балансного модулятора, и синхронизатор передатчика, первый выход которого соединен со вторым входом широтно-импульсного модулятора, а второй выход синхронизатора передатчика соединен с входом генератора фазоманипулированного сигнала, в приемной части: последовательно соединенные приемную антенну, смеситель, усилитель промежуточной частоты, коррелятор, демодулятор и получатель информации, который является выходом устройства, а также содержащая синхронизатор приемника, первый выход которого через гетеродин соединен со вторым входом смесителя, второй выход синхронизатора приемника соединен со вторыми входами демодулятора и коррелятора, выход которого соединен с входом синхронизатора приемника, третий выход которого соединен с входом генератора опорного фазоманипулированного сигнала, отличающаяся тем, что введены в передающую часть коммутатор передатчика, оперативное запоминающее устройство передатчика, формирователь адреса оперативного запоминающего устройства передатчика, счетный триггер передатчика и дешифратор передатчика, при этом второй выход синхронизатора передатчика соединен со счетным входом формирователя адреса оперативного запоминающего устройства передатчика, выход которого соединен с адресным входом оперативного запоминающего устройства передатчика, последовательный выход генератора фазоманипулированного сигнала соединен с первым информационным входом коммутатора передатчика и информационным входом оперативного запоминающего устройства передатчика, выход которого соединен со вторым информационным входом коммутатора передатчика, выход которого соединен со вторым входом фазового модулятора, n параллельных выходов генератора фазоманипулированного сигнала соединены соответственно с n входами дешифратора передатчика, выход которого соединен со счетным входом счетного триггера передатчика, управляющий вход которого является управляющим входом передающей части устройства, прямой выход счетного триггера передатчика соединен с первыми управляющими входами формирователя адреса оперативного запоминающего устройства передатчика, оперативного запоминающего устройства передатчика и коммутатора передатчика, инверсный выход счетного триггера передатчика соединен со вторыми управляющими входами формирователя адреса оперативного запоминающего устройства передатчика, оперативного запоминающего устройства передатчика и коммутатора передатчика, введены в приемную часть коммутатор приемника, оперативное запоминающее устройство приемника, формирователь адреса оперативного запоминающего устройства приемника, счетный триггер приемника и дешифратор приемника, причем третий выход синхронизатора приемника соединен со счетным входом формирователя адреса оперативного запоминающего устройства приемника, выход которого соединен с адресным входом оперативного запоминающего устройства приемника, последовательный выход генератора опорного фазоманипулированного сигнала соединен с первым информационным входом коммутатора приемника и информационным входом оперативного запоминающего устройства приемника, выход которого соединен со вторым информационным входом коммутатора приемника, выход которого соединен с третьим входом коррелятора, n параллельных выходов генератора опорного фазоманипулированного сигнала соединены соответственно с n входами дешифратора приемника, выход которого соединен со счетным входом счетного триггера приемника, управляющий вход которого является управляющим входом приемной части устройства, прямой выход счетного триггера приемника соединен с первыми управляющими входами формирователя адреса оперативного запоминающего устройства приемника, оперативного запоминающего устройства приемника и коммутатора приемника, инверсный выход счетного триггера приемника соединен со вторыми управляющими входами формирователя адреса оперативного запоминающего устройства приемника, оперативного запоминающего устройства приемника и коммутатора приемника.