Устройство для передачи данных

Иллюстрации

Показать всеИзобретение относится к устройствам для передачи данных и может быть использовано в синхронных телекоммуникационных системах. Технический результат - повышение скорости передачи данных. Устройство содержит подключенные к противоположным сторонам линии связи блоки передачи и приема данных. Блок передачи данных содержит блок стаффинга и скремблер, блок приема данных - дескремблер и блок дестаффинга. Технический результат достигается благодаря одновременному распознаванию блоками передачи и приема данных в скремблированном потоке битов определенных кодов, которые формируются в случайные (заранее не известные) моменты времени. Эти моменты, во-первых, служат ориентирами при сортировке битов, принадлежащих разным каналам, и, во-вторых, используется для синхронной установки генераторов псевдослучайных последовательностей битов скремблера и дескремблера в одинаковые состояния. Таким образом, из потока данных исключаются служебные биты разделения потока по каналам и служебные информационные кадры, предназначенные для кодовой синхронизации дескремблера со скремблером. 2 з.п. ф-лы, 16 ил.

Реферат

Изобретение относится к электронным схемам общего назначения, в частности к схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами.

Известно устройство [1] для передачи данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит первый и второй элементы Исключающее ИЛИ, первый усилитель и первый сдвиговый регистр, входы второго элемента Исключающее ИЛИ подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ, вход последовательных данных первого сдвигового регистра соединен с выходом первого элемента Исключающее ИЛИ и с входом первого усилителя, вход синхронизации первого сдвигового регистра является входом синхронизации устройства, второй вход первого элемента Исключающее ИЛИ является входом данных устройства, выход первого усилителя подключен к линии связи, блок приема данных содержит генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого соединен с входом синхронизации второго сдвигового регистра и является выходом синхронизации устройства, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ, выход которого является выходом данных устройства, а второй вход соединен с входом последовательных данных второго сдвигового регистра и с выходом второго усилителя.

В устройстве [1] блоки передачи и приема данных выполняют соответственно функции скремблера и дескремблера. Входные данные преобразуются скремблером к виду, при котором их можно рассматривать как псевдослучайные. Дескремблер выполняет обратное преобразование, т.е. восстанавливает исходные данные. Скремблирование данных позволяет заменить длинные последовательности нулей или единиц (и не только эти последовательности) псевдослучайными битами, что исключает возможность потери синхронизации между блоками приема и передачи данных. Кроме того, разравнивается энергетический спектр передаваемого сигнала, что способствует уменьшению уровня перекрестных помех, наводимых на соседние витые пары проводов кабеля линии связи.

Недостатком устройства [1] является размножение ошибок, которые могут возникнуть при передаче сигнала по линии связи. Так, одиночная ошибка преобразуется в троекратную, так как ошибочный бит сначала непосредственно передается на выход данных устройства, а затем, продвигаясь по второму сдвиговому регистру, еще два раза искажает выходные данные.

Известно устройство [2] для передачи данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит скремблер, содержащий генератор псевдослучайной последовательности битов, первый элемент Исключающее ИЛИ и первый усилитель, генератор псевдослучайной последовательности битов содержит первый сдвиговый регистр и второй элемент Исключающее ИЛИ, входы которого подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ и к входу последовательных данных первого сдвигового регистра, вход синхронизации которого является входом синхронизации скремблера, второй вход первого элемента Исключающее ИЛИ является входом данных скремблера, выход первого усилителя подключен к линии связи, блок приема данных содержит дескремблер, содержащий генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого является выходом синхронизации дескремблера, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ.

В устройстве [2] сдвиговый регистр блока приема данных (дескремблера) логически изолирован от линии связи, поэтому не происходит размножения ошибок, поступающих из линии.

Устройство [2] имеет два недостатка.

Первый недостаток состоит в том, что для поддержания синхронной работы сдвиговых регистров скремблера и дескремблера (в случае нарушения синхронизации устройства или при его начальном включении) необходимо периодически прерывать передачу полезных данных и передавать по линии связи служебные информационные кадры, содержащие достаточно длинные цепочки синхронизирующих битов. Это уменьшает эффективную скорость передачи данных по линии, усложняет протокол обмена и требует значительного времени ожидания дескремблером служебного кадра в случае потери синхронизации. В течение этого времени передача данных невозможна.

Второй недостаток заключается в отсутствии аппаратных средств стаффинга - вставки в передаваемый поток данных управляющих кодов и дестаффинга - выделения этих кодов из потока данных на приемной стороне. Управляющие коды могут быть адресованы соседнему узлу цифровой сети передачи данных для регулирования средней скорости встречного потока данных. Типичные примеры таких кодов: XON - "возобновить поток" и XOFF - "приостановить поток".

Для введения в поток данных управляющих кодов часто применяют байтстаффинг (см. "Transparent XON/XOFF Local Flow Control in Hayes V series Modems" http://vk.pp.ru/docs/hayes/00000536.htm). Байтстаффинг предусматривает просмотр исходного массива произвольных данных с целью отыскания в нем кодов (байтов), случайно совпадающих с множеством управляющих кодов (В это множество входит также некий код DLE.). Найденные коды преднамеренно (обратимо) искажаются, для того чтобы они отличались от управляющих кодов. Искаженные коды предваряются маркерными кодами (DLE) для их последующего распознавания приемной аппаратурой. В подготовленный таким способом массив данных, не содержащий кодов команд управления (кроме искусственно введенных в массив кодов DLE), внедряются "истинные" управляющие коды, затем массив передается в виде последовательного потока битов по линии связи на удаленную сторону. Удаленный приемник данных извлекает и принимает к исполнению "истинные" управляющие коды, отыскивает помеченные маркерными кодами искаженные байты, восстанавливает их, а маркерные коды отбрасывает.

Маркерные коды вносят нежелательную избыточность в поток передаваемых данных. В худшем случае каждый "полезный" байт должен предваряться служебным, в котором передается маркерный код, при этом эффективная скорость передачи данных уменьшается в два раза по сравнению с максимально возможной. Кроме того, для выделения управляющих, маркерных и кодов данных устройство - приемник последовательного потока битов должно распознавать границы между байтами. Для указания этих границ в битовый поток данных вводят избыточные биты, что еще более снижает эффективную скорость передачи.

Например, согласно пат. заявке США US 2002 0191721 А1, к каждому байту в битовом потоке добавляется бит разграничения, полученный от генератора псевдослучайной последовательности битов. Устройство - приемник данных обнаруживает биты разграничения благодаря их устойчивому совпадению с эталонной псевдослучайной последовательностью битов. Другой способ разграничения байтов в битовом потоке данных (пат. США №6011808) также предусматривает добавление бита разграничения к каждому байту. Этот бит формируется дублированием и инвертированием нулевого бита передаваемого байта. В результате начало байта всегда сопровождается передачей одной из комбинаций битов - 01 или 10. Устройство - приемник данных обнаруживает биты разграничения и нулевые биты данных благодаря их статистически устойчивому совпадению с кодами 01 или 10. Оба способа введения битов разграничения неэкономичны - на каждые восемь битов данных приходится вводить один служебный бит.

Оба отмеченных выше недостатка снижают скорость передачи данных через устройство [2].

Цель изобретения - повышение скорости передачи данных через устройство.

Цель достигается тем, что в устройстве для передачи данных, содержащем подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит скремблер, содержащий генератор псевдослучайной последовательности битов, первый элемент Исключающее ИЛИ и первый усилитель, генератор псевдослучайной последовательности битов содержит первый сдвиговый регистр и второй элемент Исключающее ИЛИ, входы которого подключены к выходам первого сдвигового регистра, а выход - к первому входу первого элемента Исключающее ИЛИ и к входу последовательных данных первого сдвигового регистра, вход синхронизации которого является входом синхронизации скремблера, второй вход первого элемента Исключающее ИЛИ является входом данных скремблера, выход первого усилителя подключен к линии связи, блок приема данных содержит дескремблер, содержащий генератор с фазовой автоподстройкой частоты, второй сдвиговый регистр, третий и четвертый элементы Исключающее ИЛИ и второй усилитель, вход которого подключен к линии связи, а выход - к входу генератора с фазовой автоподстройкой частоты, выход которого является выходом синхронизации дескремблера, выходы второго сдвигового регистра соединены с входами третьего элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого элемента Исключающее ИЛИ. Блок передачи данных дополнительно содержит блок стаффинга, первый вход данных и первый выход синхронизации которого являются входом данных и первым выходом синхронизации первого канала, второй вход данных и второй выход синхронизации блока стаффинга являются входом данных и первым выходом синхронизации второго канала, скремблер дополнительно содержит третий сдвиговый регистр, первый дешифратор, первый триггер и первый инвертор, выход которого подключен к входу синхронизации первого триггера, вход первого инвертора соединен с входами синхронизации первого и третьего сдвиговых регистров, а также с третьим выходом синхронизации блока стаффинга, управляющий вход первого сдвигового регистра соединен с выходом первого дешифратора и с управляющим входом блока стаффинга, выход данных которого соединен с входом данных скремблера, вход последовательных данных третьего сдвигового регистра соединен с выходом первого элемента Исключающее ИЛИ и с входом данных первого триггера, выход которого соединен с входом первого усилителя, входы параллельных данных первого сдвигового регистра соединены с выходами первого дешифратора, входы которого соединены с выходами третьего сдвигового регистра. Блок приема данных дополнительно содержит блок дестаффинга, первый выход синхронизации которого является вторым выходом синхронизации первого канала, второй выход синхронизации блока дестаффинга является вторым выходом синхронизации второго канала, дескремблер дополнительно содержит четвертый сдвиговый регистр, второй дешифратор, второй и третий триггеры и второй инвертор, выход которого подключен к входу синхронизации второго триггера и к входам синхронизации второго и четвертого сдвиговых регистров, управляющий вход второго сдвигового регистра соединен с выходом второго дешифратора и с управляющим входом блока дестаффинга, вход синхронизации которого соединен с выходом синхронизации дескремблера, выход третьего триггера является выходом данных дескремблера и соединен с выходами данных первого и второго каналов устройства, вход последовательных данных четвертого сдвигового регистра соединен со вторым входом четвертого элемента Исключающее ИЛИ и с выходом второго триггера, вход данных которого соединен с выходом второго усилителя, входы параллельных данных второго сдвигового регистра соединены с выходами второго дешифратора, входы которого соединены с выходами четвертого сдвигового регистра, вход последовательных данных второго сдвигового регистра соединен с первым входом четвертого элемента Исключающее ИЛИ, выход которого соединен с входом данных третьего триггера, вход синхронизации которого соединен с выходом синхронизации дескремблера и с входом второго инвертора.

Блок стаффинга содержит генератор импульсов, инвертор, элемент задержки, счетчик, первый и второй элементы И, первый - пятый триггеры и мультиплексор, входы данных которого являются первым и вторым входами данных блока, а управляющий вход соединен с выходом пятого триггера, первый выход синхронизации блока соединен с выходом второго элемента И, второй выход синхронизации блока соединен с выходом первого элемента И и со счетным входом счетчика, входы установки нуля счетчика и второго триггера соединены с выходом четвертого триггера и с входом элемента задержки, выход которого соединен с входом установки нуля четвертого триггера, вход данных которого соединен с выходом счетчика, входы синхронизации первого и четвертого триггеров соединены с выходом инвертора, вход которого соединен с выходом генератора импульсов, с входами синхронизации третьего и пятого триггеров и с первыми входами первого и второго элементов И и является третьим выходом синхронизации блока, выход мультиплексора соединен с входом данных третьего триггера, выход которого является выходом данных блока, вход данных первого триггера является управляющим входом блока, выход первого триггера соединен с входом синхронизации второго триггера, вход данных которого подключен к шине положительного напряжения, единичный выход второго триггера соединен с вторым входом первого элемента И и с входом данных пятого триггера, нулевой выход второго триггера соединен с вторым входом второго элемента И.

Блок дестаффинга содержит инвертор, элемент задержки, счетчик, первый и второй элементы И, первый, второй и третий триггеры, вход инвертора соединен с первыми входами первого и второго элементов И и является входом синхронизации блока, вход данных первого триггера является управляющим входом блока, входы синхронизации первого и третьего триггеров соединены с выходом инвертора, входы установки нуля счетчика и второго триггера соединены с выходом третьего триггера и с входом элемента задержки, выход которого соединен с входом установки нуля третьего триггера, вход данных которого соединен с выходом счетчика, счетный вход которого соединен с выходом первого элемента И и является вторым выходом синхронизации блока, выход второго элемента И является первым выходом синхронизации блока, единичный и нулевой выходы второго триггера соединены с вторыми входами первого и второго элементов И, вход данных второго триггера подключен к шине положительного напряжения, вход синхронизации второго триггера подключен к нулевому выходу первого триггера.

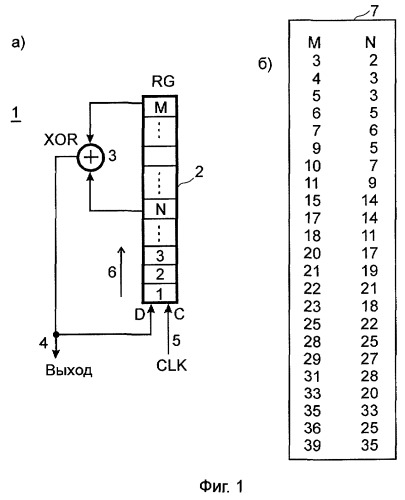

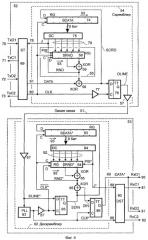

На фиг.1, а и б представлены функциональная схема известного генератора псевдослучайной последовательности битов и таблица - указатель точек подключения цепи обратной связи этого генератора; на фиг.2 - функциональная схема известного устройства [1] для передачи данных; на фиг.3 - функциональная схема известного устройства [2] для передачи данных; на фиг.4 - функциональная схема предлагаемого устройства для передачи данных; на фиг.5 - функциональная схема блока стаффинга предлагаемого устройства; на фиг.6 - функциональная схема блока дестаффинга предлагаемого устройства; на фиг.7, а - в - таблица состояний генератора псевдослучайной последовательности битов, диаграмма состояний этого генератора и пример кодовой ситуации, поясняющий работу предлагаемого устройства; на фиг.8 - временные диаграммы работы скремблера предлагаемого устройства; на фиг.9 - временные диаграммы работы дескремблера предлагаемого устройства; на фиг.10 - 13 - временные диаграммы, поясняющие процесс передачи данных предлагаемым устройством в разных кодовых ситуациях.

Генератор 1 псевдослучайной последовательности битов (фиг.1,а) содержит сдвиговый регистр 2, выходы разрядов М и N которого соединены с входами элемента Исключающее ИЛИ 3, выход которого соединен с входом последовательных данных сдвигового регистра 2 и является выходом 4 генератора 1 псевдослучайной последовательности битов, вход 5 синхронизации сдвигового регистра 2 является входом синхронизации генератора 1 псевдослучайной последовательности битов. Направление сдвига данных в регистре 2 показано стрелкой 6. Номера разрядов М и N регистра 2 выбираются из приведенной на фиг.1, б таблицы 7 - указателя точек подключения цепи обратной связи.

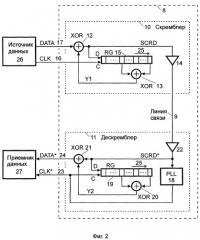

Известное [1] устройство 8 для передачи данных (фиг.2) содержит подключенные к противоположным сторонам линии связи 9 блок 10 передачи данных (скремблер) и блок 11 приема данных (дескремблер), блок 10 передачи данных содержит первый 12 и второй 13 элементы Исключающее ИЛИ, первый 14 усилитель и первый 15 сдвиговый регистр, входы второго 13 элемента Исключающее ИЛИ подключены к выходам первого 15 сдвигового регистра, а выход - к первому входу первого 12 элемента Исключающее ИЛИ, вход последовательных данных первого 15 сдвигового регистра соединен с выходом первого 12 элемента Исключающее ИЛИ и с входом первого 14 усилителя, вход синхронизации первого 15 сдвигового регистра является входом 16 синхронизации устройства, второй вход первого 12 элемента Исключающее ИЛИ является входом 17 данных устройства, выход первого 14 усилителя подключен к линии связи 9, блок 11 приема данных содержит генератор 18 с фазовой автоподстройкой частоты, второй 19 сдвиговый регистр, третий 20 и четвертый 21 элементы Исключающее ИЛИ и второй 22 усилитель, вход которого подключен к линии связи 9, а выход - к входу генератора 18 с фазовой автоподстройкой частоты, выход которого соединен с входом синхронизации второго 19 сдвигового регистра и является выходом 23 синхронизации устройства, выходы второго 19 сдвигового регистра соединены с входами третьего 20 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 21 элемента Исключающее ИЛИ, выход которого является выходом 24 данных устройства, а второй вход соединен с входом последовательных данных второго 19 сдвигового регистра и с выходом второго 22 усилителя. Направления сдвига данных в регистрах 15 и 19 показаны стрелками 25. Внешний источник 26 данных (например, первый компьютер) подключен к входам 16 и 17 устройства 8. Внешний приемник 27 данных (например, второй компьютер) подключен к выходам 23 и 24 устройства 8.

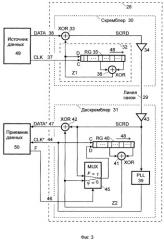

Известное [2] устройство 28 для передачи данных (фиг.3) содержит подключенные к противоположным сторонам линии связи 29 блок 30 передачи данных (скремблер) и блок 31 приема данных (дескремблер), блок 30 передачи данных содержит генератор 32 псевдослучайной последовательности битов, первый 33 элемент Исключающее ИЛИ и первый 34 усилитель, генератор 32 псевдослучайной последовательности битов содержит первый 35 сдвиговый регистр и второй 36 элемент Исключающее ИЛИ, входы которого подключены к выходам первого 35 сдвигового регистра, а выход - к первому входу первого 33 элемента Исключающее ИЛИ и к входу последовательных данных первого 35 сдвигового регистра, вход синхронизации которого является входом 37 синхронизации скремблера 30, второй вход первого элемента Исключающее ИЛИ является входом 38 данных скремблера 30, выход первого 34 усилителя подключен к линии связи 29, блок 31 приема данных (дескремблер) содержит генератор 39 с фазовой автоподстройкой частоты, второй 40 сдвиговый регистр, третий 41 и четвертый 42 элементы Исключающее ИЛИ и второй 43 усилитель, вход которого подключен к линии связи 29, а выход - к входу генератора 39 с фазовой автоподстройкой частоты, выход которого является выходом 44 синхронизации дескремблера 31, выходы второго сдвигового регистра 40 соединены с входами третьего 41 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 42 элемента Исключающее ИЛИ.

В блоке 30 передачи данных выход первого 33 элемента Исключающее ИЛИ соединен с входом первого 34 усилителя. Блок 31 приема данных содержит также мультиплексор 45, выход которого соединен с входом последовательных данных регистра 40, а управляющий вход является управляющим входом 46 устройства 28. Первый вход данных мультиплексора 45 соединен с первым входом четвертого 42 элемента Исключающее ИЛИ. Второй вход данных мультиплексора 45 соединен со вторым входом четвертого 42 элемента Исключающее ИЛИ и с выходом второго 43 усилителя. Выход четвертого 42 элемента Исключающее ИЛИ является выходом 47 данных устройства 28. Вход синхронизации регистра 40 соединен с выходом 44 синхронизации устройства 28. Направления сдвига данных в регистрах 35 и 40 показаны стрелками 48. Внешний источник 49 данных (например, первый компьютер) подключен к входам 37 и 38 устройства 28. Внешний приемник 50 данных (например, второй компьютер) подключен к выходам 44 и 47 и к входу 46 устройства 28.

Предлагаемое устройство для передачи данных (фиг.4) содержит подключенные к противоположным сторонам линии связи 51 блок 52 передачи данных и блок 53 приема данных, блок 52 передачи данных содержит скремблер 54, содержащий генератор 55 псевдослучайной последовательности битов, первый 56 элемент Исключающее ИЛИ и первый 57 усилитель, генератор 55 псевдослучайной последовательности битов содержит первый 58 сдвиговый регистр и второй 59 элемент Исключающее ИЛИ, входы которого подключены к выходам первого 58 сдвигового регистра, а выход - к первому входу первого 56 элемента Исключающее ИЛИ и к входу последовательных данных первого 58 сдвигового регистра, вход синхронизации которого является входом 60 синхронизации скремблера, второй вход первого элемента Исключающее ИЛИ является входом 61 данных скремблера, выход первого 57 усилителя подключен к линии связи 51, блок 53 приема данных содержит дескремблер 62, содержащий генератор 63 с фазовой автоподстройкой частоты, второй 64 сдвиговый регистр, третий 65 и четвертый 66 элементы Исключающее ИЛИ и второй 67 усилитель, вход которого подключен к линии связи 51, а выход - к входу генератора 63 с фазовой автоподстройкой частоты, выход которого является выходом 68 синхронизации дескремблера 62, выходы второго 64 сдвигового регистра соединены с входами третьего 65 элемента Исключающее ИЛИ, выход которого подключен к первому входу четвертого 66 элемента Исключающее ИЛИ.

Блок 52 передачи данных содержит также блок 69 стаффинга, первый вход 70 данных и первый выход 71 синхронизации которого являются входом данных и первым выходом синхронизации первого канала, второй вход 72 данных и второй выход 73 синхронизации блока 69 являются входом данных и первым выходом синхронизации второго канала, скремблер 54 дополнительно содержит третий 74 сдвиговый регистр, первый 75 дешифратор, первый 76 триггер и первый 77 инвертор, выход которого подключен к входу синхронизации первого 76 триггера, вход первого 77 инвертора соединен с входами синхронизации первого 58 и третьего 74 сдвиговых регистров, а также с третьим выходом синхронизации блока 69, управляющий вход первого 58 сдвигового регистра соединен с выходом первого 75 дешифратора и с управляющим входом 78 блока 69, выход данных которого соединен с входом 61 данных скремблера, вход последовательных данных третьего 74 сдвигового регистра соединен с выходом первого 56 элемента Исключающее ИЛИ и с входом данных первого 76 триггера, выход которого соединен с входом первого 57 усилителя, входы 79 параллельных данных первого 58 сдвигового регистра соединены с выходами первого 75 дешифратора, входы которого соединены с выходами третьего 74 сдвигового регистра.

Блок 53 приема данных содержит также блок 80 дестаффинга, первый 81 выход синхронизации которого является вторым выходом синхронизации первого канала, второй 82 выход синхронизации блока 80 является вторым выходом синхронизации второго канала, дескремблер 62 дополнительно содержит четвертый 83 сдвиговый регистр, второй 84 дешифратор, второй 85 и третий 86 триггеры и второй 87 инвертор, выход которого подключен к входу синхронизации второго 85 триггера и к входам синхронизации второго 64 и четвертого 83 сдвиговых регистров, управляющий вход второго 64 сдвигового регистра соединен с выходом второго 84 дешифратора и с управляющим входом 88 блока 80 дестаффинга, вход синхронизации которого соединен с выходом 68 синхронизации дескремблера, выход третьего 86 триггера является выходом 89 данных дескремблера и соединен с выходами 90 и 91 данных первого и второго каналов устройства, вход последовательных данных четвертого 83 сдвигового регистра соединен со вторым входом четвертого 66 элемента Исключающее ИЛИ и с выходом второго 85 триггера, вход данных которого соединен с выходом второго 67 усилителя, входы 92 параллельных данных второго 64 сдвигового регистра соединены с выходами второго 84 дешифратора, входы которого соединены с выходами четвертого 83 сдвигового регистра, вход последовательных данных второго 64 сдвигового регистра соединен с первым входом четвертого 66 элемента Исключающее ИЛИ, выход которого соединен с входом данных третьего 86 триггера, вход синхронизации которого соединен с выходом 68 синхронизации дескремблера 62 и с входом второго 87 инвертора. Стрелки 93 показывают направления сдвига данных в регистрах 58, 64, 74 и 83.

Блок 69 стаффинга (фиг.5) содержит генератор 94 импульсов, инвертор 95, элемент 96 задержки, счетчик 97, первый 98 и второй 99 элементы И, первый 100, второй 101, третий 102, четвертый 103, пятый 104 триггеры и мультиплексор 105, входы данных которого являются первым 70 и вторым 72 входами данных блока 69, а управляющий вход соединен с выходом пятого 104 триггера, первый 71 выход синхронизации блока 69 соединен с выходом второго 99 элемента И, второй 73 выход синхронизации блока 69 соединен с выходом первого 98 элемента И и со счетным входом счетчика 97, входы установки нуля счетчика 97 и второго 101 триггера соединены с выходом четвертого 103 триггера и с входом элемента 96 задержки, выход которого соединен с входом установки нуля четвертого 103 триггера, вход данных которого соединен с выходом счетчика 97, входы синхронизации первого 100 и четвертого 103 триггеров соединены с выходом инвертора 95, вход которого соединен с выходом генератора 94 импульсов, с входами синхронизации третьего 102 и пятого 104 триггеров и с первыми входами первого 98 и второго 99 элементов И и является третьим 60 выходом синхронизации блока 69, выход мультиплексора 105 соединен с входом данных третьего 102 триггера, выход которого является выходом 61 данных блока 69, вход данных первого 100 триггера является управляющим входом 78 блока 69, выход первого 100 триггера соединен с входом синхронизации второго 101 триггера, вход данных которого подключен к шине 106 положительного напряжения, единичный выход второго 101 триггера соединен с вторым входом первого 98 элемента И и с входом данных пятого 104 триггера, нулевой выход второго 101 триггера соединен с вторым входом второго 99 элемента И.

Блок 80 дестаффинга (фиг.6) содержит инвертор 107, элемент 108 задержки, счетчик 109, первый 110 и второй 111 элементы И, первый 112, второй 113 и третий 114 триггеры, вход инвертора 107 соединен с первыми входами первого 110 и второго 111 элементов И и является входом 68 синхронизации блока 80, вход данных первого 112 триггера является управляющим входом 88 блока 80, входы синхронизации первого 112 и третьего 114 триггеров соединены с выходом инвертора 107, входы установки нуля счетчика 109 и второго 113 триггера соединены с выходом третьего 114 триггера и с входом элемента 108 задержки, выход которого соединен с входом установки нуля третьего 114 триггера, вход данных которого соединен с выходом счетчика 109, счетный вход которого соединен с выходом первого 110 элемента И и является вторым 82 выходом синхронизации блока 80, выход второго 111 элемента И является первым 81 выходом синхронизации блока 80, единичный и нулевой выходы второго 113 триггера соединены с вторыми входами первого 110 и второго 111 элементов И, вход данных второго 113 триггера подключен к шине 115 положительного напряжения, вход синхронизации второго 113 триггера подключен к нулевому выходу первого 112 триггера.

В таблице 116 (фиг.7, и) представлен список состояний генератора 55 псевдослучайной последовательности битов; диаграмма 117 состояний этого генератора (фиг.7, б) отражает перемещение указателя 118 текущего состояния по кольцевому пути; линии 119 и 120 разделяют диаграмму на четыре сектора. В таблице 121 (фиг.7, в) приведен пример кодовой ситуации, поясняющий работу предлагаемого устройства.

Временные диаграммы 122 и 123 (фиг.8) соответствуют сигналам на входах 60 и 61 скремблера 54; диаграмма 124 - сигналу на выходе элемента Исключающее ИЛИ 59; диаграмма 125 - сигналу на выходе элемента Исключающее ИЛИ 56; диаграмма 126 - сигналам на выходах регистра 74; диаграмма 127 - сигналу на управляющем входе P/S регистра 58 (точка 78); диаграмма 128 - состояниям генератора 55 псевдослучайной последовательности битов; диаграмма 129 - сигналу на входе усилителя 57.

Временная диаграмма 130 (фиг.9) соответствуют сигналу на выходе усилителя 67; диаграмма 131 - сигналу на выходе инвертора 87; диаграмма 132 - сигналу на выходе триггера 85; диаграмма 133 - сигналам на выходах регистра 83; диаграмма 134 - сигналу на управляющем входе P/S* регистра 64 (точка 88); диаграмма 135 - состояниям регистра 64 генератора псевдослучайной последовательности битов дескремблера 62; диаграмма 136 - сигналу на выходе элемента Исключающее ИЛИ 65; диаграмма 137 - сигналу на выходе элемента Исключающее ИЛИ 66; диаграмма 138 - сигналу на входе инвертора 87; диаграмма 139 - сигналу на выходе 89 дескремблера 62.

Временные диаграммы 140 и 141 (фиг.10) соответствуют сигналам на входе и выходе инвертора 95 (фиг.5); диаграммы 142 и 143 - сигналам на входе данных и выходе триггера 100; диаграммы 144 и 145 - сигналам на единичном и нулевом выходах триггера 101; диаграмма 146 - сигналу на выходе триггера 104; диаграммы 147 и 148 - сигналам в точках 71 и 73; диаграммы 149, 150, 151 и 152 - сигналам L1, L2, L3 на выходах счетчика 97 и на его входе установки нуля; диаграммы 153 и 154 - сигналам в точках 70 и 72; диаграммы 155 и 156 - сигналам на входе данных и выходе триггера 102; диаграмма 157 - сигналу на входе усилителя 57 (фиг.4).

Временные диаграммы 158 и 159 (фиг.11) соответствуют сигналам на входе и выходе инвертора 95 (фиг.5); диаграммы 160 и 161 - сигналам на входе данных и выходе триггера 100; диаграммы 162 и 163 - сигналам на единичном и нулевом выходах триггера 101; диаграмма 164 - сигналу на выходе триггера 104; диаграммы 165 и 166 - сигналам в точках 71 и 73; диаграммы 167, 168, 169 и 170 - сигналам L1, L2, L3 на выходах счетчика 97 и на его входе установки нуля; диаграммы 171 и 172 - сигналам в точках 70 и 72; диаграммы 173 и 174 - сигналам на входе данных и выходе триггера 102; диаграмма 175 - сигналу на входе усилителя 57 (фиг.4).

Временные диаграммы 176, 177 и 178 (фиг.12) соответствуют сигналам на входе данных, входе синхронизации и выходе триггера 85; диаграмма 179 - сигналу во входном разряде регистра 83; диаграммы 180 и 181 - сигналам на входе данных и выходе триггера 112 (фиг.6); диаграммы 182 и 183 - сигналам на единичном и нулевом выходах триггера 113; диаграммы 184 и 185 - сигналам в регистре 64 и на выходе элемента Исключающее ИЛИ 65; диаграммы 186, 187 и 188 - сигналам на входе данных, входе синхронизации и выходе триггера 86; диаграммы 189 и 190 - сигналам в точках 81 и 82; диаграммы 191, 192, 193 и 194 - сигналам L1*, L2*, L3* на выходах счетчика 109 и на его входе установки нуля.

Временные диаграммы 195, 196 и 197 (фиг.13) соответствуют сигналам на входе данных, входе синхронизации и выходе триггера 85; диаграмма 198 - сигналу во входном разряде регистра 83; диаграммы 199 и 200 - сигналам на входе данных и выходе триггера 112 (фиг.6); диаграммы 201 и 202 - сигналам на единичном и нулевом выходах триггера 113; диаграммы 203 и 204 - сигналам в регистре 64 и на выходе элемента Исключающее ИЛИ 65; диаграммы 205, 206 и 207 - сигналам на входе данных, входе синхронизации и выходе триггера 86; диаграммы 208 и 209 - сигналам в точках 81 и 82; диаграммы 210, 211, 212 и 213 - сигналам L1*, L2*, L3* на выходах счетчика 109 и на его входе установки нуля.

Ниже приведено краткое описание работы известных устройств [1, 2].

Скремблеры и дескремблеры обычно содержат генераторы псевдослучайных последовательностей битов или фрагменты таких генераторов. Пример построения генератора псевдослучайной последовательности битов приведен на фиг.1 (см. кн. П.Хоровиц, У.Хилл "Искусство схемотехники": В трех т. - М.: Мир, 1993. - 2 т.). Генератор 1 выполнен на основе сдвигового регистра 2 с логическим элементом Исключающее ИЛИ (XOR) 3 в цепи обратной связи.

В исходном состоянии в регистре 2 присутствует любой ненулевой код (цепь начальной установки регистра не показана). Под действием положительных фронтов синхросигнала CLK на входе 5 этот код циркулирует в генераторе и одновременно видоизменяется. В каждом такте (периоде сигнала CLK) код продвигается в регистре 2 в направлении, указанном стрелкой 6, при этом в освободившийся разряд регистра заносится бит данных с выхода 4. В качестве выхода генератора можно использовать выход элемента Исключающее ИЛИ 3 или выход любого разряда регистра.

В общем случае при использовании М-разрядного регистра 2 цепь обратной связи подключается к разрядам с номерами М и N (М>N). Для того чтобы на выходе генератора формировалась псевдослучайная последовательность битов с периодом повторения, равным 2М - 1, следует выбирать точки подключения цепи обратной связи в соответствии с таблицей 7 (фиг.1, б), которая описывает ряд генераторов различной разрядности. При работе генератора в регистре 2 формируются все возможные М-разрядные коды, за исключением нулевого. (Отметим, что во всех описанных далее устройствах можно применять усовершенствованные генераторы, не имеющие запрещенных состояний, см., например, кн. Шевкопляс Б. В. "Микропроцессорные структуры. Инженерные решения": Справочник. - Дополнение первое. - М.: Радио и связь, 1993. - 256 с.).

Псевдослучайная последовательность битов с периодом повторения, равным 2М - 1, обладает следующими свойствами.

1. В полном цикле (2М - 1 тактов) число лог.1, формируемых на выходе 4 генератора 1, на единицу больше, чем число лог.0. Добавочная лог.1 появляется за счет исключения состояния, при котором в регистре 2 присутствовал бы нулевой код. Это можно интерпретировать так, что вероятности появления лог.0 и лог.1 на выходе 4 генератора 1 практически одинаковы.

2. В полном цикле (2М - 1 тактов) половина серий из последовательных лог.1 имеет длину 1, одна четвертая серий - длину 2, одна восьмая - длину 3 и т. д. Такими же свойствами обладают и серии из лог.0 с учетом пропущенного лог.0. Это говорит о том, что вероятности появления "орлов" и "решек" не зависят от исходов предыдущих "подбрасываний". Поэтому вероятность того, что серия из последовательных лог.1 или лог.0 закончится при следующем подбрасывании, равна 1/2.

3. Если последовательность полного цикла (2М - 1 тактов) сравнивать с этой же последовательностью, но циклически сдвинутой на любое число тактов W (W не является нулем или числом, кратным 2М - 1), то число несовпадений будет на единицу больше, чем число совпадений.

Наиболее распространены две основные схемы устройств для передачи данных (устройств типа "скремблер - дескремблер"): с неизолированными и изолированными (от линии связи) генераторами псевдослучайных последовательностей битов.

В устройстве 8 (фиг.2 [1]) скремблер 10 и дескремблер 11 выполнены с использованием фрагментов рассмотренных ранее генераторов 1 псевдослучайных последовательностей битов (см. фиг.1). В цепь обратной связи генератора на основе сдвигового регистра 15 введен дополнительный элемент Исключающее ИЛИ 12. В дескремблере применен аналогичный генератор на основе сдвигового регистра 19 с разомкнутой цепью обратной связи.

Все процессы, протекающие в устройстве 8, синхронизируются от тактового генератора, размещенного во внешнем источнике данных 26 (возможно также его размещение в блоке 10). Тактовый генератор формирует сигнал CLK - непрерывную последовательность тактовых импульсов со скважностью, равной двум. В каждом такте на вход 17 скремблера 10 подается очередной бит передаваемых данных DATA, а в сдвиговом регистре 15 накопленный код продвигается на один разряд вправо (по стрелке 25).

Если предположить, что источник данных 26 посылает в скремблер 10 длинную последовательность лог.0 (DATA=0), то элемент И