Способ и устройство для параллельного объединения данных со сдвигом вправо

Иллюстрации

Показать всеИзобретение относится к области микропроцессоров и компьютерных систем, более конкретно к способу и устройству для параллельного объединения данных со сдвигом вправо. Техническим результатом является обеспечение эффективной поддержки операций SIMD без существенного снижения эффективности в целом. Указанный результат достигается за счет того, что параллельно со сдвигом влево на 'L - М' элементов данных первого операнда, имеющего первый набор из L элементов данных, сдвигают второй операнд, имеющий второй набор из L элементов данных, вправо на М элементов данных, и объединяют упомянутый сдвинутый первый набор с упомянутым сдвинутым вторым набором для получения результата, имеющего L элементов данных. 6 н. и 38 з.п. ф-лы, 23 ил., 1 табл.

Реферат

ОБЛАСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение относится в общем случае к области микропроцессоров и компьютерных систем. Более конкретно, настоящее изобретение относится к способу и устройству для параллельного объединения данных со сдвигом вправо.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

По мере развития технологии процессоров также создаются новые коды программ для работы на компьютерах с этими процессорами. Пользователи в общем случае ожидают и требуют более высокой производительности от своих компьютеров независимо от типа используемого программного обеспечения. Одна из таких проблем может возникнуть из-за типов команд и операций, которые в текущий момент выполняются в процессоре. Некоторые типы операций требуют большего времени для завершения из-за сложности операций и/или необходимых для них схем. Это создает возможность оптимизации способа, которым некоторые сложные операции выполняются в процессоре.

Медиаприложения (мультимедийные прикладные программы) способствуют разработкам микропроцессоров в течение более десяти лет. Фактически, большинство обновлений вычислительной техники за последние годы были вызваны медиаприложениями. Эти обновления преобладающим образом происходили в пределах потребительского сегмента, хотя существенные усовершенствования также имели место в предпринимательском сегменте, например, для целей образования и коммуникации с учетом развлекательного аспекта. Однако будущие медиаприложения будут предъявлять все более высокие требования к вычислениям. В результате, в ближайшем будущем пользование персональными компьютерами (ПК) будет характеризоваться более интересными аудиовизуальными эффектами, а также будет более легким в практическом применении, и что еще более важно, компьютеры будут объединены со средствами связи.

Соответственно, отображение изображений так же, как воспроизведение аудио и видеоданных, которое все вместе упоминается как содержимое, стало все более и более популярными приложениями для существующих вычислительных устройств. Операции фильтрации и свертки являются примерами самых обычных операций, выполняемых с данными содержимого, такого как изображение, аудио и видеоинформация. Как известно специалистам, вычисления фильтрации и корреляции выполняют с помощью операции умножения с накоплением, которая суммирует произведения данных и коэффициентов. Корреляция двух векторов А и B состоит в вычислении суммы S:

уравнение (1), которое очень часто используется при k=0:

уравнение (2)

В случае, когда N-отводный фильтр f применяют к вектору V, сумма S может быть рассчитана следующим образом:

уравнение (3)

Такие операции требуют большого объема вычислений, но обеспечивают высокий уровень параллелизма данных, который может использоваться при эффективном воплощении с использованием различных устройств хранения данных, таких, например, как регистры с одним потоком команд и множеством потоков данных (SIMD).

Применение операций фильтрации можно найти в большом множестве задач обработки изображений и видеоинформации, а также связи. Примерами использования фильтров являются уменьшение артефактов формирования блоков данных в видеоизображении стандарта MPEG (стандарт, выработанный экспертной группой по кинематографии), уменьшение шумов и звуков, отделение водяных знаков от значений пикселов для улучшения обнаружения водяных знаков, корреляция для сглаживания, увеличение резкости, сокращение шума, обнаружение краев и масштабирование размеров изображений или видеокадров, дискретизация видеокадров для оценки движения суб-пикселов, улучшение качества аудиосигнала и изменение формы импульсов и коррекция сигналов в связи. Соответственно, операции фильтрации так же, как свертки, жизненно важны для вычислительных устройств, которые обеспечивают воспроизведение содержимого, которое включает в себя изображение, аудио и видеоданные.

К сожалению, существующие способы и команды направлены на общие потребности фильтрации и не являются всесторонними. Фактически, многие виды архитектур не поддерживают средство для эффективного вычисления фильтрации для разных длин фильтра и типов данных. Кроме того, упорядочивание данных в устройствах хранения данных, таких как регистры SIMD, так же, как возможность суммирования смежных значений в регистре и частичных переносов данных между регистрами, в общем случае не поддерживаются. В результате, существующие виды архитектур требуют ненужных изменений типа данных, которые минимизируют количество операций за одну команду и значительно увеличивают количество тактовых циклов, требуемых для упорядочивания данных для арифметических операций.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Настоящее изобретение показано для примера, а не для ограничения, на чертежах, на которых одинаковые ссылочные позиции обозначают сходные элементы и на которых:

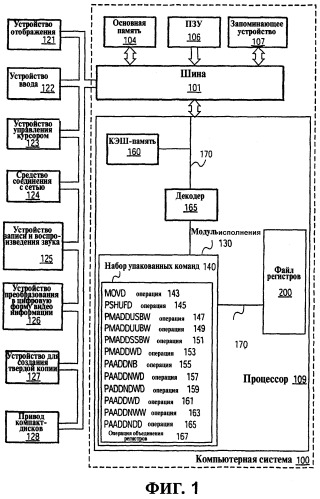

Фиг.1 - структурная схема компьютерной системы, реализующей один из вариантов осуществления настоящего изобретения;

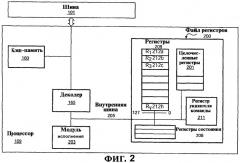

Фиг.2 - структурная схема варианта осуществления процессора, как показано на фиг.1, в соответствии с другим вариантом осуществления настоящего изобретения;

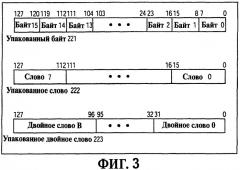

Фиг.3 - иллюстрация видов упакованных данных согласно другому варианту осуществления настоящего изобретения;

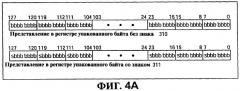

Фиг.4A - представление в регистре упакованного байта согласно одному из вариантов осуществления настоящего изобретения;

Фиг.4B - представление в регистре упакованного слова согласно одному из вариантов осуществления настоящего изобретения;

Фиг.4C - представление в регистре упакованного двойного слова согласно одному из вариантов осуществления настоящего изобретения;

Фиг.5 - диаграмма, иллюстрирующая действие команды перемещения байтов в соответствии с вариантом осуществления настоящего изобретения;

Фиг.6 - диаграмма, иллюстрирующая команду умножения с накоплением байтов в соответствии с вариантом осуществления настоящего изобретения;

Фиг.7A-7C - диаграммы, иллюстрирующие команду перемещения байтов по фиг.5, объединенную с командой умножения с накоплением байтов по фиг.6, для получения множества сумм пар произведений в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.8A-8D - диаграммы, иллюстрирующие команду суммирования смежных элементов в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.9A и 9B - команда объединения регистров в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.10 - блок-схема последовательности операций для эффективной обработки данных содержимого в соответствии с одним из вариантов осуществления настоящего изобретения;

Фиг.11 - блок-схема способа обработки данных содержимого согласно операции обработки данных в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.12 - блок-схема последовательности операций для продолжения обработки данных содержимого в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.13 - блок-схема последовательности операций, иллюстрирующая операцию объединения регистров в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг.14 - блок-схема последовательности операций способа выбора необработанных элементов данных из устройства-источника хранения данных в соответствии с примерным вариантом осуществления настоящего изобретения;

Фиг.15 - структурная схема микроархитектуры процессора одного из вариантов осуществления, которая включает в себя логические схемы для параллельного выполнения операции объединения со сдвигом вправо в соответствии с настоящим изобретением;

Фиг.16A - структурная схема одного из вариантов осуществления логической схемы для выполнения операции параллельного объединения со сдвигом вправо с операндами данных в соответствии с настоящим изобретением;

Фиг.16B - структурная схема другого варианта осуществления логической схемы для выполнения операции объединения со сдвигом вправо;

Фиг.17A - иллюстрирующая действия параллельной команды объединения со сдвигом вправо в соответствии с первым вариантом осуществления настоящего изобретения;

Фиг.17B - иллюстрирующая действия команды объединения со сдвигом вправо в соответствии со вторым вариантом осуществления;

Фиг.18А - последовательность операций одного из вариантов осуществления способа параллельного сдвига вправо и объединения операндов данных;

Фиг.18B - последовательность операций другого варианта осуществления способа сдвига вправо и объединения данных;

Фиг.19A-B - примеры оценки движения;

Фиг.20 - пример применения оценки движения и результирующего предсказания;

Фиг.21A-B - пример текущего и предыдущего кадров, обрабатываемых во время оценки движения;

Фиг.22A-D - операции оценки движения в кадрах в соответствии с одним из вариантов осуществления настоящего изобретения; и

Фиг.23A-B - последовательность операций одного из вариантов осуществления способа предсказания и оценки движения.

ПОДРОБНОЕ ОПИСАНИЕ

Ниже описаны способ и устройство для выполнения параллельного объединения данных со сдвигом вправо. Также описаны способ и устройство для эффективной фильтрации и свертки данных содержимого. Также раскрыты способ и устройство для оценки движения быстрого полного поиска с помощью операций объединения SIMD. Описанные варианты осуществления описаны в контексте микропроцессора, но не ограничены им. Хотя последующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления могут применяться к другим типам интегральных схем и логических устройств. Те же самые методы и идеи настоящего изобретения могут легко применяться к другим типам полупроводниковых схем или устройств, которые могут использовать преимущества более высокой пропускной способности конвейера и улучшенной производительности. Принципы настоящего изобретения применимы к любому процессору или устройству, которые выполняют обработку данных. Однако настоящее изобретение не ограничено процессорами или устройствами, которые выполняют операции с 256-битными, 128-битными, 64-битными, 32-битными или 16-битными данными и могут применяться на любом процессоре и устройстве, в которых необходимо объединение данных со сдвигом вправо.

В последующем описании для целей объяснения многочисленные конкретные подробности изложены для обеспечения полного понимания настоящего изобретения. Однако специалистам должно быть ясно, что эти конкретные подробности не являются необходимыми для практической реализации настоящего изобретения. В других случаях известные электрические структуры и схемы не излагаются подробно, чтобы не затенять сущность настоящего изобретения. Кроме того, в последующем описании приведены примеры, и на чертежах показаны различные примеры для целей иллюстрации. Однако эти примеры не должны рассматриваться в качестве ограничения, поскольку они предназначены только для представления примеров настоящего изобретения, а не для обеспечения исчерпывающего списка всех возможных воплощений настоящего изобретения.

В одном из вариантов осуществления способы настоящего изобретения воплощены в командах, исполняемых компьютером. Команды могут использоваться для выполнения этапов настоящего изобретения в универсальном процессоре или в специализированном процессоре, который запрограммирован с помощью данных команд. Альтернативно, этапы настоящего изобретения могут выполняться определенными аппаратными компонентами, которые содержат логические схемы с постоянными соединениями для выполнения этапов, или комбинацией программируемых компьютерных компонентов и заказных аппаратных компонентов.

Настоящее изобретение может обеспечиваться как компьютерная программа или программное обеспечение, которое может включать в себя считываемый компьютером носитель, который имеет хранящиеся на нем команды, которые могут использоваться для программирования компьютера (или других электронных устройств) для выполнения способа согласно настоящему изобретению. Такое программное обеспечение может храниться в памяти системы. Точно так же код может распространяться через сеть или посредством другого считываемого компьютером носителя. Считываемый компьютером носитель может включать в себя гибкие дискеты, оптические диски, компакт-диски (CD-ROM) и магнитооптические диски, постоянное запоминающее устройство (ПЗУ), оперативную память (ОП), стираемое программируемое постоянное запоминающее устройство (СППЗУ), электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ), магнитные или оптические платы, флэш-память, передачу по Интернет или подобные им средства, но не ограничивается перечисленным.

Соответственно, считываемый компьютером носитель включает в себя любой тип среды передачи данных/машинно-считаемых носителей, которые подходят для хранения или передачи электронных команд или информации в форме, считываемой устройством (например, компьютером). Кроме того, настоящее изобретение может также загружаться как компьютерная программа. Также, программа может пересылаться с удаленного компьютера (например, сервера) на запрашивающий компьютер (например, клиент). Пересылка программы может быть выполнена посредством электрического, оптического, акустического сигналов передачи данных или сигналов передачи данных другой формы, воплощенных в несущей или другой среде распространения сигнала через канал связи (например, модем, сетевое соединение или иное подобное средство).

В современных процессорах используется множество различных исполнительных модулей для обработки и исполнения различных кодов и команд. Не все команды одинаковы, так некоторые быстрее завершаются, в то время как другие могут занимать огромное количество тактовых циклов. Чем быстрее выполняются команды, тем выше производительность в целом процессора. Таким образом было бы выгодно иметь максимально возможное количество команд, которые выполняются с максимально возможной скоростью. Однако существуют некоторые команды, которые отличаются высокой сложностью и требуют больше ресурсов процессора и времени выполнения. Например, существуют команды с плавающей запятой, операции загрузки/хранения, перемещения данных и т.д.

Поскольку все большее количество компьютерных систем используют в приложениях Интернет и мультимедиа, их дополнительная поддержка процессором увеличивается с течением времени. Например, целочисленные/с плавающей запятой команды для обработки в архитектуре с одной командой множеством потоков данных и (SIMD) и расширение для потоковых команд (SIMD) (SSE) являются командами, которые уменьшают общее количество команд, требуемых для выполнения конкретной задачи программы. Эти команды могут увеличивать производительность программного обеспечения, обрабатывая множество элементов данных параллельно. В результате можно достичь увеличения производительности в широком диапазоне приложений, которые включают в себя обработку видеоинформации, речи и изображений/фотографий. Выполнение команд SIMD в микропроцессорах и подобных типах логических схем обычно создает множество проблем. Кроме того, сложность операций SIMD часто требует дополнительных схем для правильной обработки и управления данными.

Варианты осуществления настоящего изобретения обеспечивают способ реализации параллельной команды сдвига вправо как алгоритм, который использует относящиеся к архитектуре SIMD аппаратные средства. Для одного из вариантов осуществления алгоритм основан на принципе сдвига вправо требуемого количества сегментов данных одного операнда в сторону наибольшей значимости второго операнда, когда то же самое количество сегментов данных сдвигают в сторону наименьшей значимости второго операнда. В принципеоперацию объединения со сдвигом вправо можно рассматривать как объединение двух блоков данных в один блок и сдвиг данного объединенного блока для выравнивания сегментов данных в требуемом положении для формирования новой комбинации данных. Таким образом, варианты осуществления алгоритма объединения со сдвигом вправо в соответствии с настоящим изобретением могут осуществляться в процессоре для эффективной поддержки операций SIMD без существенного снижения эффективности в целом.

ВЫЧИСЛИТЕЛЬНАЯ АРХИТЕКТУРА

Фиг.1 показывает компьютерную систему 100, в которой может быть воплощен вариант осуществления настоящего изобретения. Компьютерная система 100 содержит шину 101 для передачи информации и процессор 109, присоединенный к шине 101, для обработки информации. Компьютерная система 100 также включает в себя подсистему памяти 104-107, присоединенную к шине 101, предназначенную для хранения информации и команд для процессора 109.

Процессор 109 включает в себя модуль 130 исполнения, файл 200 регистров, кэш-память 160, декодер 165 и внутреннюю шину 170. Кэш-память 160 присоединена к модулю 130 исполнения и хранит часто используемую и/или недавно использованную информацию для процессора 109. Файл 200 регистров хранит информацию в процессоре 109 и присоединен к модулю 130 исполнения через внутреннюю шину 170. В одном из вариантов осуществления изобретения файл 200 регистров включает в себя регистры мультимедиа, например регистры SIMD, предназначенные для хранения мультимедийной информации. В одном из вариантов осуществления каждый из регистров мультимедиа хранит до ста двадцати восьми битов упакованных данных. Регистры мультимедиа могут быть специализированными регистрами мультимедиа или регистрами, которые используются для хранения мультимедийной и другой информации. В одном из вариантов осуществления регистры мультимедиа хранят данные мультимедиа при выполнении операций мультимедиа и хранят данные с плавающей запятой при выполнении операций с плавающей запятой.

Модуль 130 исполнения оперирует с упакованными данными согласно командам, принятым процессором 109, которые включены в набор 140 упакованных команд. Модуль 130 исполнения также оперирует со скалярными данными согласно командам, реагируемым в универсальных процессорах. Процессор 109 способен поддерживать набор команд микропроцессора Pentium® и набора 140 упакованных команд. За счет включения набора 140 упакованных команд в стандартный набор команд микропроцессора, такой как набор команд микропроцессора Pentium®, команды с упакованными данными могут быть легко помещены в существующее программное обеспечение (ранее написанное для стандартного набора команд микропроцессора). Другие стандартные наборы команд, такие как наборы команд процессоров PowerPC™ и Альфа™, могут также использоваться в соответствии с описанным изобретением. (Pentium® - зарегистрированный товарный знак корпорации Intel. PowerPC™ - товарный знак компаний IBM, APPLE COMPUTER и MOTOROLA. Alpha™ - товарный знак корпорации Digital Equipment.)

В одном из вариантов осуществления набор 140 упакованных команд включает в себя команды (как описано более подробно ниже) для операции 143 пересылки данных (MOVD) и операции 145 перемещения данных (PSHUFD) для организации данных в пределах устройства хранения данных; операцию упакованного умножения с накоплением для первого регистра-источника без знака и второго регистра-источника со знаком (операция 147 PMADDUSBW); операцию упакованного умножения с накоплением (операция 149 PMADDUUBW) для выполнения умножения с накоплением для первого регистра-источника без знака и второго регистра-источника без знака; операцию упакованного умножения с накоплением (операция 151 PMADDSSBW) для первого и второго регистров-источников со знаком, и стандартного умножения с накоплением (операция 153 PMADDWD) для первого и второго регистров-источников со знаком, содержащих 16-разрядные данные. Наконец, система упакованных команд включает в себя команду суммирования смежных значений для суммирования смежных байтов (операция 155 PAADDNB), слов (операция 157 PAADDNWD) и двойных слов (PAADDNDWD 159), двух значений слова (PAADDWD 161), двух слов для получения 16-разрядного результата (операция 163 PAADDNWW), двух учетверенных слов квадраслов для получения результата в виде квадраслова (операция 165 PAADDNDD) и операцию 167 объединения регистров.

За счет включения набора 140 упакованных команд в набор команд универсального процессора 109, вместе с соответствующими схемами для исполнения команд, операции, используемые многими существующими мультимедийными приложениями, могут выполняться с использованием упакованных данных в универсальном процессоре. Таким образом, многие мультимедийные приложения могут выполняться быстрее и эффективнее с использованием полной разрядности шины данных процессора для выполнения операций с упакованными данными. Это устраняет потребность перемещения небольших блоков данных по шине данных процессора для выполнения одной или более операций с одним элементом данных в определенный момент времени.

Согласно Фиг.1 компьютерная система 100, соответствующая настоящему изобретению, может включать в себя устройство 121 отображения, такое как монитор. Устройство 121 отображения может включать в себя промежуточное устройство, такое как буфер кадров. Компьютерная система 100 также включает в себя устройство 122 ввода данных, такое как клавиатура, и устройство 123 управления курсором, такое как «мышь», или шаровой манипулятор («трекбол»), или сенсорная панель. Устройство 121 отображения, устройство 122 ввода данных и устройство 123 управления курсором присоединены к шине 101. Компьютерная система 100 может также включать в себя средство 124 соединения с сетью, так что компьютерная система 100 является частью локальной сети (ЛС) или глобальной сети (ГС).

Дополнительно, компьютерная система 100 может быть присоединена к устройству 125 для записи и/или воспроизведения звука, такому как устройство преобразования в цифровую форму аудиоинформации, соединенное с микрофоном для записи речевого ввода для распознавания речи. Компьютерная система 100 может также включать в себя устройство 126 преобразования в цифровую форму видеоинформации, которое может использоваться для ввода видеоизображений, устройство 127 для создания твердой (документальной) копии, такое как принтер, и устройство 128 CD-ROM. Устройства 124 - 128 также присоединены к шине 101.

Процессор

Фиг.2 показывает подробную схему процессора 109. Процессор 109 может быть осуществлен на одной или более подложках, используя любую из множества технологий процесса, такую как BiCMOS (биполярная комплементарная структура металл-оксид-полупроводник (КМОП)), CMOS (КМОП) и NMOS (n-канальный металл-оксид-полупроводник). Процессор 109 содержит декодер 202 для декодирования сигналов управления и данных, используемых процессором 109. Затем данные могут сохраняться в файле 200 регистров через внутреннюю шину 205. Следует уточнить, что регистры варианта осуществления не ограничиваются конкретным типом схемы. Регистр в рассматриваемом варианте осуществления должен быть способен только обеспечивать хранение и передачу данных и выполнение описанных функций.

В зависимости от типа данных данные могут храниться в целочисленных регистрах 201, регистрах 209, регистрах 208 состояния или регистре 211 указателя команды. Файл 204 регистров может включать в себя другие регистры, например регистр с плавающей запятой. В одном из вариантов осуществления целочисленные регистры 201 хранят тридцатидвухбитные целочисленные данные. В одном из вариантов осуществления регистры 209 содержат восемь регистров мультимедиа R0 212a-R7 212h, например, регистры SIMD, содержащие упакованные данные. Каждый регистр в регистрах 209 имеет длину сто двадцать восемь битов. R1 212a, R2 212b и R3 212c - примеры отдельных регистров в регистрах 209. Тридцать два бита данных в регистрах 209 могут перемещаться в один из целочисленных регистров 201. Точно так же значение целочисленного регистра может быть перемещено в тридцать два бита одного из регистров 209.

Регистры 208 состояния указывают состояние процессора 109. Регистр 211 указателя команды хранит адрес следующей команды, которая будет выполняться. Целочисленные регистры 201, регистры 209, регистры 208 состояния и регистр 211 указатель команды, все они соединяются с внутренней шиной 205. Любые дополнительные регистры также соединяются с внутренней шиной 205.

В другом варианте осуществления некоторые из этих регистров могут использоваться для двух различных типов данных. Например, регистры 209 и целочисленные регистры 201 могут быть объединены, причем каждый регистр может хранить или целочисленные данные, или упакованные данные. В другом варианте осуществления регистры 209 могут использоваться как регистры с плавающей запятой. В данном варианте осуществления в регистрах 209 могут храниться упакованные данные или данные с плавающей запятой. В одном из вариантов осуществления объединенные регистры имеют длину сто двадцать восемь битов, и целые числа представлены как сто двадцать восемь битов. В данном варианте осуществления при хранении упакованных данных и целочисленных данных не требуется, чтобы регистры различали между собой эти два типа данных.

Функциональный модуль 203 выполняет операции, выполняемые процессором 109. Такие операции могут включать в себя сдвиг, сложение, вычитание и умножение и т.д. Функциональный модуль 203 соединяется с внутренней шиной 205. Кэш 160 - дополнительный элемент процессора 109 и может использоваться для кэширования данных и/или сигналов управления, например, из оперативной памяти 104. Кэш 160 соединен с декодером 202 и подсоединен с возможностью приема сигналов 207 управления.

Форматы данных и памяти

Фиг.3 иллюстрирует три типа упакованных данных: упакованный байт 221, упакованное слово 222 и упакованное двойное слово (dword) 223. Упакованный байт 221 имеет длину сто двадцать восемь битов и содержит шестнадцать элементов данных - упакованных байтов. В общем случае, элемент данных - отдельная часть данных, которая хранится в одном регистре (или ячейке памяти) с другими элементами данных той же самой длины. В упакованных последовательностях данных количество элементов данных, хранящихся в регистре, равно 128 битам, деленным на длину в битах элемента данных.

Упакованное слово 222 имеет длину 128 битов и содержит восемь элементов данных упакованного слова. Каждое упакованное слово содержит 16 битов информации. Упакованное двойное слово 223 имеет длину 128 битов и содержит четыре элемента данных упакованного двойного слова. Каждый элемент данных упакованного двойного слова содержит 32 бита информации. Упакованное квадраслово имеет длину 128 битов и содержит два элемента данных упакованного квадраслова.

Фиг.4A - 4C иллюстрируют представление в регистре хранения упакованных данных согласно одному из вариантов осуществления изобретения. Представление 310 в регистре упакованного байта без знака показывает хранение упакованного байта 201 без знака в одном из регистров 209 мультимедиа, который показан на Фиг.4A. Информация для каждого элемента данных - байта - хранится в битах с седьмого по нулевой (с 7 по 0) для нулевого байта, с 15 по 8 для первого байта, с 23 по 16 для второго байта и, наконец, с 120 по 127 для 15-го байта.

Таким образом, все доступные биты используются в регистре. Такая структура памяти увеличивает эффективность хранения данных процессора. Также, при обращении к 16 элементам данных теперь одна операция может одновременно выполняться с 16 элементами данных. Представление 311 в регистре упакованного байта со знаком показывает хранение упакованного байта 221 со знаком. Следует обратить внимание, что восьмой бит каждого элемента данных - байта - является индикатором знака.

Представление 312 в регистре упакованного слова без знака показывает, как слова с седьмого по нулевое хранятся в регистре 209 мультимедиа, который показан на Фиг.4B. Представление 313 в регистре упакованного слова со знаком подобно представлению 312 в регистре упакованного слова без знака. Следует обратить внимание, что 16 бит каждого элемента данных типа слова является индикатором знака. Представление 314 в регистре упакованного двойного слова без знака показывает регистр 209 мультимедиа, хранящий два элемента данных типа двойного слова, как показано на Фиг.4C. Представление 315 в регистре упакованного двойного слова со знаком подобно представлению 314 в регистре упакованного двойного слова без знака. Заметим, что знаковым разрядом является 32-й бит элемента данных типа двойного слова.

Эффективная фильтрация и свертка данных содержимого, как раскрывается в настоящем изобретении, начинаются с загрузки устройства-источника данных коэффициентами фильтрации/свертки и данными. Во многих случаях порядок данных или коэффициентов в устройстве хранения данных, таком, например, как регистр SIMD, требует изменения, прежде чем смогут быть выполнены арифметические вычисления. Соответственно, эффективные вычисления фильтрации и свертки требуют не только соответствующих арифметических команд, но также и эффективных способов организации данных, требуемых для вычислений.

Например, как упомянуто при описании предшествующего уровня техники, изображения фильтруются с помощью замены значения, например, заданного пиксела I на S [I]. Значения пикселов с обеих сторон от пиксела I используют при вычислении фильтра S [I]. Точно так же пикселы с обеих сторон от пиксела I+1 требуются для вычисления S [I+1]. Следовательно, чтобы вычислить результаты фильтрации для больше, чем одного пиксела в регистре SIMD, данные копируются и размещаются в регистре ОКМД для вычисления.

К сожалению, современные вычислительные архитектуры испытывают недостаток в эффективном способе упорядочения данных для всех соответствующих размеров данных в пределах вычислительной архитектуры. Соответственно, как изображено на Фиг.5, настоящее изобретение включает в себя команду перемещения байтов (PSHUFB) 145, которая эффективно упорядочивает данные любого размера. Операция 145 перемещения байтов упорядочивает данные, размеры которых больше, чем байт, поддерживая относительное расположение байтов в пределах больших данных во время операции перемещения. Кроме того, операция 145 перемещения байтов может изменять относительное расположение данных в регистре SIMD и может также копировать данные.

На Фиг.5 показан пример операции 145 перемещения байтов для фильтра с тремя коэффициентами. Используя обычные методы, коэффициенты фильтра (не показаны) применяют к трем пикселам, и затем коэффициенты фильтра перемещают к другому пикселу и снова применяют. Однако для параллельного выполнения этих операций настоящее изобретение описывает новую команду для упорядочения данных. Соответственно, как изображено на Фиг.5, данные 404 формируются в устройстве-адресате 406 хранения данных, которое в одном из вариантов осуществления является устройством-источником 404 хранения данных, используя маску 402 для определения адреса, по которому соответствующие элементы данных хранятся в регистре-адресате 406. В одном из вариантов осуществления конфигурация маски основана на требуемой операции обработки данных, которая может включать в себя, например, операцию фильтрации, операцию свертки или подобные им.

Соответственно, используя маску 402, обработка данных 406 вместе с коэффициентами может выполняться параллельно. В описанном примере запоминающим устройством-источником 404 данных является 128-битный регистр SIMD, который первоначально хранит 16 8-битных пикселов. При использовании фильтра пикселов с тремя коэффициентами четвертый коэффициент устанавливают в ноль. В одном из вариантов осуществления в зависимости от количества элементов данных в запоминающем устройстве-источнике 404 данных регистр-источник 404 может использоваться как устройство-адресат хранения данных, или регистр-адресат, таким образом сокращая количество регистров, которые необходимы в общем случае. Также, перезаписываемые данные в устройстве-источнике 404 хранения данных могут повторно загружаться из памяти или из другого регистра. Кроме того, множество регистров могут использоваться в качестве устройства-источника 404 хранения данных, причем их соответствующие данные формируются в устройстве-адресате 406 хранения данных, когда требуется.

Когда упорядочивание элементов данных, а также коэффициентов закончено, данные и соответствующие коэффициенты должны обрабатываться в соответствии с операцией обработки данных. Специалистам должно быть понятно, что для вычислений фильтрации необходимы операции с различной точностью так же, как для вычислений свертки с использованием различного количества коэффициентов фильтра и различных размеров данных. Базовая операция фильтрации умножает две пары чисел и суммирует их результаты. Эту операцию называют командой умножения с накоплением.

К сожалению, существующая вычислительная архитектура не обеспечивает поддержки эффективного вычисления умножения с накоплением для множества длин массива или фильтра и множества размеров данных с использованием коэффициентов без знака или со знаком. Кроме того, не поддерживаются операции с байтами. В результате, вычислительные системы обычной архитектуры должны преобразовывать 16-битные данные, используя команды распаковывания. Эти виды архитектур вычислительной системы в общем случае включают в себя поддержку операции умножения с накоплением, которые вычисляют произведения 16-разрядных данных в отдельных регистрах и затем складывают смежные произведения для получения 32-разрядного результата. Это решение приемлемо для коэффициентов фильтра для данных, которые требуют 16-разрядной точности, но для 8-битных коэффициентов фильтра для 8-битных данных (что является общим случаем для изображений и видеоинформации) параллелизм уровня команд и данных бесполезен.

Фиг.6 изображает первый регистр-источник 452 и второй регистр-источник 454. В одном из вариантов осуществления первый и второй регистры-источники являются регистрами SIMD длиной N-бит, такие, например, как 128-битные регистры XMM технологии SSE2 корпорации Intel®. Команда умножения с накоплением, выполненная с таким регистром, дает следующие результаты для двух векторов 452 и 454 пикселов, которые сохраняют в регистре-адресате 456. Соответственно, пример показывает команду умножения с накоплением 8-битного байта на 16 слов, которая называется операцией 147 PMADDUSBW (фиг.1), в которой символы U и S в команде относятся к байтам со знаком и без знака. В одном из регистров-источников байты используют со знаком, а в другом они без знака.

В одном из вариантов осуществления настоящего изобретения регистр с данными без знака является адресатом и содержит 16 результатов умножения с накоплением. Причиной для такого выбора является то, что в большинстве реализаций данные используют без знака, а коэффициенты - со знаком. Соответственно, предпочтительно перезаписать данные, потому что менее вероятно, что эти данные будут необходимы в будущих вычислениях. Дополнительные команды умножения с накоплением байтов, как показано на фиг.1, являются операцией 149 PMADDUUBW для байтов без знака в обоих регистрах и операцией 151 PMADDSSBW для байтов со знаком в обоих регистрах-источниках. Команды умножения с накоплением заканчиваются командой 153 PMADDWD, которая применяется к парам 16-разрядных слов со знаком для получения 32-разрядного произведения со знаком.

Как в общем случае операций фильтрации, второй вектор обычно содержит коэффициенты фильтра. Соответственно, чтобы подготовить регистр XMM, коэффициенты могут загружаться в часть регистра и копироваться в остальную часть регистра, используя команду 145 перемещения. Например, как изображено на Фиг.7A, устройство 502 хранения данных коэффициентов, такое, например, как 128-битный регистр XMM, первоначально загружают тремя коэффициентами в ответ на выполнение команды загрузки данных. Однако специалистам должно быть понятно, что коэффициенты фильтра могут быть сформированы в памяти до обработки данных. Также, коэффициенты могут первоначально загружаться, как показано на фиг.7B, на основе их организации в памяти, до операции фильтрации.

Регистр 502 коэффициентов включает в себя коэффициенты фильтра F3, F2 и F1, которые могут кодироваться как байты со знаком или б