Когерентный приемник рлс с цифровым устройством для амплитудной и фазовой корректировки квадратурных составляющих принимаемого сигнала

Иллюстрации

Показать всеИзобретение относится к технике обработки сигналов радиолокационных станций (РЛС). Технический результат состоит в расширении функциональных возможностей и улучшении основных технических параметров РЛС. Сущность изобретения состоит в обеспечении управляемого усиления, преобразования частоты, разложении на квадратурные составляющие, аналого-цифровое преобразование сигналов, обеспечении идентичности амплитудных и фазовых характеристик мнимой и реальной составляющих сигнала, цифрового гетеродинирования, накоплении, оптимальной фильтрации (сжатие фазокодоманипулированных сигналов), поступающих с высокочастотного приемника РЛС. 3 ил.

Реферат

Изобретение относится к технике обработки сигналов радиолокационных станций (РЛС).

Из уровня техники известен некогерентный приемник (Авторское свидетельство СССР №1525933, Н 04 L 17/30, 1989) с повышенной помехоустойчивостью, но он не производит обработку фазовой структуры сигнала.

Известно устройство распознавания движущихся объектов (Свидетельство РФ на полезную модель №21250, G 01 K 9/00, 2001), которое определяет класс объекта, но не решает задачу расширения динамического диапазона приемника.

Радиоприемное устройство когерентной РЛС (Заявка РФ на изобретение №2000120020, бюллетень "Изобретения, полезные модели" №16, 2002, с 126) не обеспечивает цифровое гетеродинирование обрабатываемого сигнала и имеет ошибку при цифровой корректировке квадратур принимаемых сигналов.

Наиболее близким по технической сущности является некогерентный обнаружитель сигналов в шумах (Заявка РФ на изобретение №200102468, бюллетень "Изобретения, полезные модели" №8, 2002, с 71), включающий некогерентный гетеродин, фазосдвигающую цепочку, аналого-цифровой преобразователь, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, первые входы упомянутых смесителей соединены с входом сигнала, второй вход первого смесителя соединен с выходом гетеродина через фазосдвигающую цепочку, второй вход второго смесителя частоты соединен также с выходом гетеродина, выходы первого и второго смесителей соединены с входами первого и второго фильтров промежуточной частоты соответственно, в схему введены первый и второй компараторы напряжений, логическая схема «исключающее ИЛИ», счетчик-делитель на 2n, N-разрядный накапливающий сумматор, третий компаратор чисел и m-разрядный регистр, выход одного из фильтров промежуточной частоты соединен с сигнальным входом аналого-цифрового преобразователя и не инвертирующим входом первого компаратора напряжений, выход второго фильтра соединен с не инвертирующим входом второго компаратора напряжений, инвертирующие входы упомянутых компараторов соединены с нулевым потенциалом, выходы первого и второго компараторов соединены с первым и вторым входами логической схемы «исключающее ИЛИ», выход упомянутой схемы соединен с тактовым входом упомянутого аналого-цифрового преобразователя и с входом счетчика-делителя на n, шина цифрового выхода упомянутого аналого-цифрового преобразователя без знакового разряда соединена с входом N-разрядного накапливающего сумматора, m=N-n выходных старших разрядов накапливающего сумматора соединены с входом третьего компаратора чисел, второй вход третьего компаратора чисел соединен с выходом m-разрядного регистра, в который записан двоичный код порога, управляющий вход упомянутого компаратора чисел соединен с выходом упомянутого счетчика-делителя на n.

Однако при его использовании он не обеспечивает идентичности амплитудных, фазовых характеристик сигнала по квадратурам, что приведет к высокому уровню зеркальной составляющей сигнала при цифровом гетеродинировании в приемнике и когерентной обработки принимаемого сигнала, так как это схемно-конструктивно в известном техническом решении не предусмотрено.

Технический результат предлагаемого технического решения направлен на расширение функциональных возможностей и улучшение основных технических параметров РЛС.

Технический результат достигается тем, что когерентный приемник РЛС с цифровым устройством для амплитудной и фазовой корректировки квадратурных составляющих принимаемого сигнала содержит первый аналого-цифровой преобразователь, первый и второй смесители частот, первый N-разрядный накапливающий сумматор, первый и второй компараторы напряжения, а в первый канал приема входит устройство квадратурного фазового детектирования первого канала и устройство предварительной обработки первого канала, при этом устройство квадратурного фазового детектирования первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую и вторую схемы контроля, схему формирования сигнала исправности, в свою очередь устройство предварительной обработки первого канала состоит из первого и второго аналого-цифрового преобразователя, первого и второго цифроаналоговых преобразователей, первого и второго устройства корректировки коэффициентов, устройства цифрового гетеродинирования, постоянного запоминающего устройства устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго накапливающих N-разрядных сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных запоминающих устройств череспериодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo "первый вошел, первый вышел", устройства управления, первого и второго коммутаторов, при этом второй канал приема содержит устройство квадратурного фазового детектирования второго канала и устройство предварительной обработки второго канала, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования первого канала и устройству предварительной обработки первого канала, а также в когерентный приемник РЛС с цифровым устройством для амплитудной и фазовой корректировки квадратурных составляющих принимаемого сигнала включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры, синхронизатор сигналов, при этом вход приемника по первому каналу соединен с первым входом устройства квадратурного фазового детектирования первого канала, первый выход устройства квадратурного фазового детектирования первого канала соединен со вторым входом устройства предварительной обработки первого канала, первый выход устройства предварительной обработки первого канала соединен с первым входом третьего мультиплексора, выход третьего мультиплексора соединен с разъемом выходного сигнала реальной составляющей, разъем входного опорного сигнала соединен с входом делителя частоты и входом преобразователя уровня, выход делителя частоты соединен с входом полосового фильтра, выход полосового фильтра соединен с входом дифференцирующей цепочки и входом интегрирующей цепочки, выход дифференцирующей цепочки соединен с входом первого резонансного усилителя, первый выход резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования первого канала, второй выход первого резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования второго канала, выход интегрирующей цепочки соединен с входом второго резонансного усилителя, первый выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования первого канала, второй выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования второго канала, первый выход устройства квадратурного фазового детектирования второго канала соединен со вторым входом устройства предварительной обработки второго канала, первый выход устройства предварительной обработки второго канала соединен со вторым входом четвертого мультиплексора, выход четвертого мультиплексора соединен с разъемом выходного сигнала мнимой составляющей, первый выход синхронизатора сигналов соединен с входом кварцевого генератора, первый выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования первого канала, второй выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования второго канала, второй выход синхронизатора сигналов соединен с входом первого дешифратора, выход первого дешифратора соединен с пятым входом устройства квадратурного фазового детектирования первого канала, третий выход синхронизатора сигналов соединен с входом второго дешифратора, выход второго дешифратора соединен с пятым входом устройства квадратурного фазового детектирования второго канала, выход преобразователя уровня соединен с первым входом синхронизатора сигналов, второй выход устройства квадратурного фазового детектирования второго канала соединен с третьим входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования второго канала соединен с третьим входом устройства предварительной обработки второго канала, второй выход устройства квадратурного фазового детектирования первого канала соединен со вторым входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования первого канала соединен с третьим входом устройства предварительной обработки первого канала, пятый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки второго канала, шестой выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки второго канала, седьмой выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки второго канала, восьмой выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки второго канала, девятый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки второго канала, десятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки второго канала, одиннадцатый выход синхронизатора сигналов является выходом импульса для формирования строба перестройки антенны, двенадцатый выход синхронизатора сигналов является выходом сигнала запуска оконечной ступени передатчика, тринадцатый выход синхронизатора сигналов является выходом сигнала, определяющего длительность импульса запуска передатчика, четырнадцатый выход синхронизатора сигналов является выходом сигнала, определяющего фазу импульса запуска передатчика, пятнадцатый выход синхронизатора сигналов является выходом сигнала импульса бланкирования приемника, шестнадцатый выход синхронизатора сигналов является выходом импульса, сопровождающего основной сигнал, семнадцатый выход синхронизатора сигналов является выходом импульса начала передачи, восемнадцатый выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки второго канала, девятнадцатый выход синхронизатора сигналов соединен с третьим входом третьего мультиплексора и третьим входом четвертого мультиплексора, двадцатый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки первого канала, двадцать первый выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки первого канала, двадцать второй выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки первого канала, двадцать третий выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки первого канала, двадцать четвертый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки первого канала, двадцать пятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки первого канала, двадцать шестой выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки первого канала, разъем магистрали параллельной информации соединен параллельно с первым, одиннадцатым, двенадцатым, тринадцатым входами устройства предварительной обработки первого канала и с первым, одиннадцатым, двенадцатым, тринадцатым входами устройства предварительной обработки второго канала и с четвертым выходом синхронизатора сигналов, второй выход устройства предварительной обработки первого канала соединен с первым входом четвертого мультиплексора, второй выход устройства предварительной обработки второго канала соединен со вторым входом третьего мультиплексора, в устройстве квадратурного фазового детектирования первого канала первый вход соединен с первым входом сумматора, выход сумматора соединен с первым входом блока усилителей с временной автоматической регулировкой усиления, выход блока усилителей с временной автоматической регулировкой усиления соединен с первым входом первого смесителя частот и с первым входом второго смесителя частот, выход первого смесителя частот соединен с первым входом первого операционного усилителя, выход первого операционного усилителя соединен с входом первого фильтра низких частот, выход первого фильтра низких частот соединен с первым выходом устройства квадратурного фазового детектирования первого канала, с входом первой схемы контроля и с входом первого интегратора, выход первого интегратора соединен с входом первого компаратора напряжений, выход первого компаратора напряжений соединен со вторым входом первого операционного усилителя, выход второго смесителя частот соединен с первым входом второго операционного усилителя, выход второго операционного усилителя соединен с входом второго фильтра низких частот, выход второго фильтра низких частот соединен с третьим выходом устройства квадратурного фазового детектирования первого канала, с входом второй схемы контроля и с входом второго интегратора, выход второго интегратора соединен с входом второго компаратора напряжений, выход второго компаратора напряжений соединен со вторым входом второго операционного усилителя, выход первой схемы контроля соединен с первым входом схемы формирования сигнала исправности, выход второй схемы контроля соединен со вторым входом схемы формирования сигнала исправности, выход схемы формирования сигнала исправности соединен со вторым выходом устройства квадратурного фазового детектирования первого канала, четвертый вход устройства квадратурного фазового детектирования первого канала соединен со вторым входом сумматора, второй вход устройства квадратурного фазового детектирования первого канала соединен со вторым входом первого смесителя частот, третий вход устройства квадратурного фазового детектирования первого канала соединен со вторым входом второго смесителя частот, пятый вход устройства квадратурного фазового детектирования первого канала соединен со вторым входом блока усилителей с временной автоматической регулировкой усиления, разъем входного сигнала второго канала соединен с первым входом устройства фазового детектирования второго канала, первый вход устройства предварительной обработки первого канала соединен с третьим входом первого мультиплексора, второй вход устройства предварительной обработки первого канала соединен со вторым входом первого аналого-цифрового преобразователя, выход первого аналого-цифрового преобразователя соединен с первым входом первого устройства корректировки коэффициентов, выход первого устройства корректировки коэффициентов соединен с пятым входом устройства цифрового гетеродинирования, первый выход устройства цифрового гетеродинирования соединен с первым входом первого N-разрядного накапливающего сумматора, первый выход первого N-разрядного накапливающего сумматора соединен с первым входом первого мультиплексора, выход первого мультиплексора соединен с первым входом оперативного запоминающего устройства череспериодной обработки и со вторым входом первого коммутатора, выход первого оперативного запоминающего устройства череспериодной обработки соединен с первым входом оптимального фильтра, выход первого оптимального фильтра соединен с первым входом первой микросхемы FiFo, выход первой микросхемы FiFo соединен с первым входом первого коммутатора напряжений, выход первого коммутатора напряжений соединен с первым выходом устройства предварительной обработки первого канала, третий вход устройства предварительной обработки первого канала соединен с первым входом второго аналого-цифрового преобразователя, выход второго аналого-цифрового преобразователя соединен с первым входом второго устройства корректировки коэффициентов, выход второго устройства корректировки коэффициентов соединен со вторым входом устройства цифрового гетеродинирования, второй выход устройства цифрового гетеродинирования соединен с первым входом второго N-разрядного накапливающего сумматора, первый выход второго N-разрядного накапливающего сумматора соединен с первым входом второго мультиплексора, выход второго мультиплексора соединен с первым входом второго оперативного запоминающего устройства череспериодной обработки и со вторым входом второго коммутатора, выход второго оперативного запоминающего устройства череспериодной обработки соединен с первым входом второго оптимального фильтра, выход второго оптимального фильтра соединен с первым входом второй микросхемы FiFo, выход второй микросхемы FiFo соединен с первым входом второго коммутатора, выход второго коммутатора соединен со вторым выходом устройства предварительной обработки первого канала, второй выход первого N-разрядного накапливающего сумматора соединен с первым входом первого реверсивного счетчика, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, выход первого цифроаналогового преобразователя соединен с первым входом первого аналого-цифрового преобразователя, второй выход второго N-разрядного накапливающего сумматора соединен с первым входом второго реверсивного счетчика, выход второго реверсивного счетчика соединен с входом второго цифроаналогового преобразователя, выход второго цифроаналогового преобразователя соединен со вторым входом аналого-цифрового преобразователя, четвертый вход устройства предварительной обработки первого канала соединен параллельно с третьим входом второго аналого-цифрового преобразователя, с третьим входом первого аналого-цифрового преобразователя, с первым входом устройства цифрового гетеродинирования, с третьим входом второго устройства корректировки коэффициентов, с третьим входом первого устройства корректировки коэффициентов, пятый вход устройства предварительной обработки первого канала соединен с входом постоянного запоминающего устройства устройства цифрового гетеродинирования, первый выход постоянного запоминающего устройства устройства цифрового гетеродинирования соединен с третьим входом устройства цифрового гетеродинирования, второй выход постоянного запоминающего устройства цифрового гетеродинирования соединен с четвертым входом устройства цифрового гетеродинирования, шестой вход устройства предварительной обработки первого канала соединен со вторым входом второго N-разрядного накапливающего сумматора и со вторым входом первого N-разрядного накапливающего сумматора, седьмой вход устройства предварительной обработки первого канала соединен с третьим входом второго N-разрядного накапливающего сумматора и с третьим входом первого N-разрядного накапливающего сумматора, восьмой вход устройства предварительной обработки первого канала соединен со вторым входом второго реверсивного счетчика, со вторым входом второго мультиплексора, с входом формирователя адреса записи, со вторым входом первого мультиплексора и со вторым входом первого реверсивного счетчика, девятый вход устройства предварительной обработки первого канала соединен с входом формирователя адреса чтения, с входом формирователя опорных сигналов, со вторым входом второй микросхемы FiFo, с входом устройства управления и со вторым входом первой микросхемы FiFo, десятый вход устройства предварительной обработки первого канала соединен с третьим входом первого коммутатора и третьим входом второго коммутатора, первый выход устройства управления соединен с третьим входом первой микросхемы FiFo, второй выход устройства управления соединен с четвертым входом первой микросхемы FiFo, третий выход устройства управления соединен с третьим входом второй микросхемы FiFo, четвертый выход устройства управления соединен с четвертым входом второй микросхемы FiFo, первый выход формирователя опорных сигналов соединен со вторым входом первого оптимального фильтра, второй выход формирователя опорных сигналов соединен со вторым входом второго оптимального фильтра, выход формирователя адреса записи соединен со вторым входом первого оперативного запоминающего устройства череспериодной обработки и вторым входом второго оперативного запоминающего устройства череспериодной обработки, выход формирователя адреса чтения соединен с третьим входом первого оперативного запоминающего устройства череспериодной обработки и с третьим входом второго оперативного запоминающего устройства череспериодной обработки, одиннадцатый вход устройства предварительной обработки первого канала соединен с третьим входом второго мультиплексора, межкаскадные связи в устройстве квадратурного фазового детектирования второго канала аналогичны межкаскадным связям в устройстве квадратурного фазового детектирования первого канала, межкаскадные связи устройства предварительной обработки второго канала аналогичны межкаскадным связям в устройстве предварительной обработки первого канала.

Отличительными признаками от прототипа является то, что в первый канал приема входит устройство квадратурного фазового детектирования и устройство предварительной обработки, при этом устройство квадратурного фазового детектирования первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую и вторую схемы контроля и схему формирования сигнала исправности, в свою очередь устройство предварительной обработки первого канала состоит из первого и второго аналого-цифровых преобразователей, первого и второго устройства корректировки коэффициентов, первого и второго цифроаналоговых преобразователей, устройства цифрового гетеродинирования, постоянного запоминающего устройства устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго накапливающих сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных запоминающих устройств череспериодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo "первый вошел, первый вышел", устройства управления, первого и второго коммутаторов, при этом второй канал приема содержит устройство квадратурного фазового детектирования второго канала и устройство предварительной обработки второго канала, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования первого канала и устройству предварительной обработки первого канала, а также в радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры, синхронизатор сигналов и новые межкаскадные связи между ними.

Предлагаемое техническое решение обеспечивает управляемое усиление, преобразование частоты, разложение на квадратурные составляющие, аналого-цифровое преобразование сигналов, идентичность амплитудных и фазовых характеристик мнимой и реальной составляющих сигнала, цифровое гетеродинирование, накопление, оптимальную фильтрацию (сжатие фазокодоманипулированных сигналов), поступающих с высокочастотного приемника РЛС.

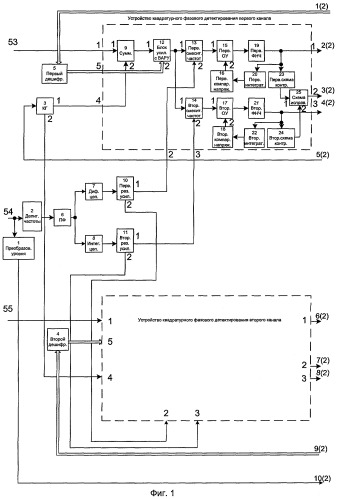

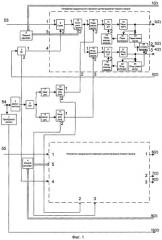

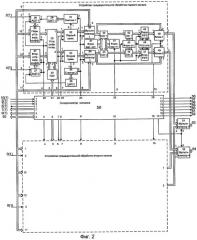

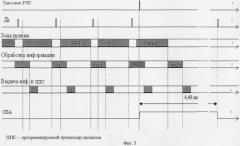

На фиг.1 приведена функциональная электрическая схема предлагаемого устройства, на фиг.2 - то же, продолжение фиг.1, на фиг.3 приведены временные диаграммы работы устройства при наличии команды «Вкл. строба перестройки частоты».

Когерентный приемник РЛС с цифровым устройством для амплитудной и фазовой корректировки квадратурных составляющих принимаемого сигнала содержит первый и второй каналы приема.

В первый канал приема входит устройство квадратурного фазового детектирования первого канала и устройство предварительной обработки первого канала, при этом устройство квадратурного фазового детектирования первого канала содержит сумматор 9, блок усилителей с временной автоматической регулировкой усиления 12, первый 13 и второй 14 смесители частот, первый 15 и второй 17 операционные усилители, первый 16 и второй 18 компараторы напряжений, первый 19 и второй 21 фильтры низких частот, первый 20 и второй 22 интеграторы, первую 23, вторую 24 схемы контроля и схему формирования сигнала исправности 25. В свою очередь устройство предварительной обработки первого канала состоит из первого 26 и второго 27 аналого-цифровых преобразователей, первого 66 и второго 67 устройства корректировки коэффициентов, первого 28 и второго 35 цифроаналоговых преобразователей, устройства цифрового гетеродинирования 29, постоянного запоминающего устройства устройства цифрового гетеродинирования 30, первого 31 и второго 34 реверсивных счетчиков, первого 32 и второго 33 N-разрядных накапливающих сумматоров, первого 36 и второго 38 мультиплексоров, формирователя адреса записи 37, первого 39 и второго 40 оперативных запоминающих устройств череспериодной обработки, формирователя адреса чтения 41, первого 42 и второго 44 оптимальных фильтров, формирователя опорных сигналов 43, первой 45 и второй 47 микросхем FiFo ("первый вошел, первый вышел"), устройства управления 46, первого 48 и второго 49 коммутаторов.

Второй канал приема содержит устройство квадратурного фазового детектирования второго канала и устройство предварительной обработки второго канала, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования первого канала и устройству предварительной обработки первого канала.

В когерентный приемник РЛС с цифровым устройством для амплитудной и фазовой корректировки квадратурных составляющих принимаемого сигнала включены первый 5 и второй 4 дешифраторы, кварцевый генератор 3, преобразователь уровня 1, делитель частоты 2, полосовой фильтр 6, дифференцирующая цепочка 7, интегрирующая цепочка 8, первый 10 и второй 11 резонансные усилители, третий 51 и четвертый 52 мультиплексоры и синхронизатор сигналов 50.

Когерентный приемник также содержит разъем входного сигнала 53 первого канала, разъем входного опорного сигнала 54, разъем входного сигнала второго канала 55, контакт импульса для формирования строба перестройки антенны 56, контакт сигнала запуска оконечной ступени передатчика 57, контакт сигнала, определяющего длительность импульса запуска передатчика 58, контакт сигнала, определяющего фазу импульса запуска передатчика 59, контакт сигнала импульса бланкирования приемника 60, контакт импульса, сопровождающего основной сигнал 61, контакт импульса начала передачи 62, разъем выходного сигнала реальной составляющей 63, разъем выходного сигнала мнимой составляющей 64 и магистраль параллельной информации 65.

Разъем входного сигнала первого канала 53 соединен с первым входом устройства квадратурного фазового детектирования первого канала. Первый выход устройства квадратурного фазового детектирования первого канала соединен со вторым входом устройства предварительной обработки первого канала. Первый выход устройства предварительной обработки первого канала соединен с первым входом третьего мультиплексора 51.

Выход третьего мультиплексора 51 соединен с разъемом выходного сигнала реальной составляющей 63. Разъем входного опорного сигнала 54 соединен с входом делителя частоты 2 и входом преобразователя уровня 1. Выход делителя частоты 2 соединен с входом полосового фильтра 6. Выход полосового фильтра 6 соединен с входом дифференцирующей цепочки 7 и входом интегрирующей цепочки 8. Выход дифференцирующей цепочки 7 соединен с входом первого резонансного усилителя 10. Первый выход резонансного усилителя 10 соединен со вторым входом устройства квадратурного фазового детектирования первого канала.

Второй выход первого резонансного усилития 10 соединен со вторым входом устройства квадратурного фазового детектирования второго канала. Выход интегрирующей цепочки 8 соединен с входом второго резонансного усилителя 11. Первый выход второго резонансного усилителя 11 соединен с третьим входом устройства квадратурного фазового детектирования первого канала. Второй выход второго резонансного усилителя 11 соединен с третьим входом устройства квадратурного фазового детектирования второго канала.

Разъем входного сигнала второго канала 55 соединен с первым входом устройства квадратурного фазового детектирования второго канала. Первый выход устройства квадратурного фазового детектирования второго канала соединен со вторым входом устройства предварительной обработки второго канала.

Первый выход устройства предварительной обработки второго канала соединен со вторым входом четвертого мультиплексора 52. Выход четвертого мультиплексора 52 соединен с разъемом выходного сигнала мнимой составляющей 64.

Первый выход синхронизатора сигналов 50 соединен с входом кварцевого генератора 3. Первый выход кварцевого генератора 3 соединен с четвертым входом устройства квадратурного фазового детектирования первого канала. Второй выход кварцевого генератора 3 соединен с четвертым входом устройства квадратурного фазового детектирования второго канала.

Второй выход синхронизатора сигналов 50 соединен с входом первого дешифратора 5. Выход первого дешифратора 5 соединен с пятым входом устройства квадратурного фазового детектирования первого канала.

Третий выход синхронизатора сигналов 50 соединен с входом второго дешифратора 4. Выход второго дешифратора 4 соединен с пятым входом устройства квадратурного фазового детектирования второго канала. Выход преобразователя уровня 1 соединен с первым входом синхронизатора сигналов 50. Второй выход устройства квадратурного фазового детектирования второго канала соединен с третьим входом синхронизатора сигналов 50. Третий выход устройства квадратурного фазового детектирования второго канала соединен с третьим входом устройства предварительной обработки второго канала.

Второй выход устройства квадратурного фазового детектирования первого канала соединен со вторым входом синхронизатора сигналов 50.

Третий выход устройства квадратурного фазового детектирования первого канала соединен с третьим входом устройства предварительной обработки первого канала.

Пятый выход синхронизатора сигналов 50 соединен с четвертым входом устройства предварительной обработки второго канала.

Шестой выход синхронизатора сигналов 50 соединен с пятым входом устройства предварительной обработки второго канала.

Седьмой выход синхронизатора сигналов 50 соединен с шестым входом устройства предварительной обработки второго канала.

Восьмой выход синхронизатора сигналов 50 соединен с седьмым входом устройства предварительной обработки второго канала.

Девятый выход синхронизатора сигналов 50 соединен с восьмым входом устройства предварительной обработки второго канала.

Десятый выход синхронизатора сигналов 50 соединен с девятым входом устройства предварительной обработки второго канала.

Одиннадцатый выход синхронизатора сигналов 50 соединен с контактом импульса для формирования строба перестройки антенны 56.

Двенадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала запуска оконечной ступени передатчика 57.

Тринадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала, определяющего длительность импульса запуска передатчика 58.

Четырнадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала, определяющего фазу импульса запуска передатчика 59.

Пятнадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала импульса бланкирования приемника 60.

Шестнадцатый выход синхронизатора сигналов 50 соединен с контактом импульса, сопровождающего основной сигнал 61.

Семнадцатый выход синхронизатора сигналов 50 соединен с контактом импульса начала передачи 62.

Восемнадцатый выход синхронизатора сигналов 50 соединен с десятым входом устройства предварительной обработки второго канала.

Девятнадцатый выход синхронизатора сигналов 50 соединен с третьим входом третьего мультиплексора 51 и третьим входом четвертого мультиплексора 52.

Двадцатый выход синхронизатора сигналов 50 соединен с четвертым входом устройства предварительной обработки первого канала.

Двадцать первый выход синхронизатора сигналов 50 соединен с пятым входом устройства предварительной обработки первого канала.

Двадцать второй выход синхронизатора сигналов 50 соединен с шестым входом устройства предварительной обработки первого канала.

Двадцать третий выход синхронизатора сигналов 50 соединен с седьмым входом устройства предварительной обработки первого канала.

Двадцать четвертый выход синхронизатора сигналов 50 соединен с восьмым входом устройства предварительной обработки первого канала.

Двадцать пятый выход синхронизатора сигналов 50 соединен с девятым входом устройства предварительной обработки первого канала.

Двадцать шестой выход синхронизатора сигналов 50 соединен с десятым входом устройства предварительной обработки первого канала.

Разъем магистрали параллельной информации 65 соединен параллельно с первым, одиннадцатым, двенадцатым, тринадцатым входами устройства предварительной обработки первого канала и с первым, одиннадцатым, двенадцатым, тринадцатым входами устройства предварительной обработки второго канала и четвертым выходом синхронизатора сигналов 50.

Второй выход устройства предварительной обработки первого канала соединен с первым входом четвертого мультиплексора 52.

Второй выход устройства предварительной обработки второго канала соединен со вторым входом третьего мультиплексора 51.

В устройстве квадратурного фазового детектирования первого канала первый вход соединен с первым входом сумматора 9. Выход сумматора 9 соединен с первым входом блока усилителей с временной автоматической регулировкой усиления 12. Выход блока усилителей с временной автоматической регулировкой усиления соединен с первым входом первого смесителя частоты 13 и с первым входом второго смесителя частоты 14.

Выход первого смесителя частот 13 соединен с первым входом первого операционного усилителя 15. Выход первого операционного усилителя 15 соединен с входом первого фильтра низких частот 19. Выход первого фильтра низких частот 19 соединен с первым выходом устройства квадратурного фазового детектирования первого канала, с входом первой схемы контроля 23 и с входом первого интегратора 20.

Выход первого интегратора 20 соединен с входом первого компаратора напряжений 16. Выход первого компаратора напряжений 16 соединен со вторым входом первого операционного усилителя 15. Выход второго смесителя частот 14 соединен с первым входом второго операционного усилителя 17. Выход второго операционного усилителя 17 соединен с входом второго фильтра низких частот 21. Выход второго фильтра низких частот 21 соединен с третьим выходом устройства квадратурного фазового детектирования первого канала, с входом второй схемы контроля 24, с входом второго интегратора 22.

Выход второго интегратора 22 соединен с входом второго компаратора напряжений 18. Выход второго компаратора напряжений 18 соединен со вторым входом второго операционного усилителя 17. Выход первой схем