Способ, устройство и команда для выполнения знаковой операции умножения

Иллюстрации

Показать всеЗаявленное изобретение относится к области устройств обработки и соответствующего программного обеспечения и программных последовательностей, которые выполняют математические операции. Техническим результатом является уменьшение количества команд, требуемых для реализации знаковой обработки, повышение скорости вычисления алгоритмов кодирования, повышение пропускной способности и освобождение ресурсов обработки. Указанный результат достигается за счет того, что устройство содержит ячейку памяти и исполнительные ресурсы, предназначенные для исполнения команды над первым операндом и сохранения результата, имеющего значение первого операнда для всех значений соответствующего второго операнда, больших нуля, нуля, если значение соответствующего второго операнда равно нулю, отрицательной версии первого операнда для всех значений соответствующего второго операнда, меньших нуля. 8 н. и 38 з.п. ф-лы, 11 ил.

Реферат

Область техники

Настоящее изобретение относится к области устройств обработки и соответствующего программного обеспечения и программных последовательностей, которые выполняют математические операции.

Предшествующий уровень техники

Компьютерные системы все больше проникают в жизнь современного общества. Возможности обработки компьютеров повысили эффективность и производительность труда работников в широком спектре профессий. Поскольку стоимость покупок и приобретения в собственность компьютеров продолжает падать, все больше и больше потребителей обретают возможность получения выгод от более новых и более быстродействующих машин. Кроме того, многие люди получают удовольствие от использования портативных компьютеров (ноутбуков) ввиду предоставляемой ими свободы. Мобильные компьютеры позволяют пользователям легко переносить свои данные и работать с ними, когда они покидают офис или находятся в путешествии. Данный сценарий хорошо знаком маркетинговым группам, руководителям корпораций и даже студентам.

По мере развития технологии процессоров происходит создание новых кодов программного обеспечения для исполнения на машинах этими процессорами. Пользователи в общем случае ожидают и требуют более высоких рабочих характеристик от своих компьютеров независимо от типа используемого программного обеспечения. Один такой вопрос может возникнуть из типов команд и операций, которые действительно выполняются в процессоре. Некоторые типы операций требуют больше времени для исполнения ввиду сложности операций и/или типа требующихся схем. Это обеспечивает возможность оптимизировать путь, которым в процессоре исполняются некоторые сложные операции.

Медийные прикладные программы (приложения) стимулируют развитие микропроцессоров уже больше десятка лет. В действительности, большинство компьютерных модернизаций в последние годы стимулировалось медийными приложениями. Эти модернизации преобладающим образом происходили в потребительских сегментах, хотя значительный прогресс также наблюдается в производственных сегментах в области развлечений, высшего образования и коммуникации. Тем не менее будущие медийные приложения сделают необходимыми еще более высокие вычислительные требования. В результате практический опыт персональных компьютеров ближайшего будущего будет отличаться разнообразием аудио визуальных эффектов, а также они будут проще в использовании и, что более важно, вычисления сольются с коммуникациями.

Соответственно, отображение изображений, а также воспроизведение аудио и видеоданных, которые совместно определяются понятием «информационное содержание», станут все более популярными приложениями для будущих вычислительных устройств. Операции фильтрации и свертки являются некоторыми из наиболее обычных операций, выполняемых над данными информационного содержания, такими как аудио- и видеоданные изображений. Такие операции требуют высокой вычислительной мощности, но обуславливают высокий уровень параллелизма данных, что может быть использовано за счет эффективной реализации с применением различных устройств хранения данных, таких, например, как регистры одного потока команд и множества потоков данных (SIMD-регистры). Ряд современных архитектур также требуют не являющегося необходимым изменения типа данных, что снижает пропускную способность команд и существенно увеличивает число тактовых циклов, требуемых для упорядочивания данных для арифметических операций.

Различные связанные со знаком команды, известные из предшествующего уровня техники, такие как знаковая команда, определяют знак двоичного числа. Однако возможности этих известных знаковых команд имеют ограниченную полезность, особенно в приложениях, где необходима дальнейшая обработка знаковых результатов, поскольку эти результаты являются промежуточными результатами более масштабных алгоритмов. Потребность в дополнительных командах для достижения желательных результатов обуславливала дополнительные затраты, связанные с ресурсами обработки и интервалами времени конвейерной обработки.

Краткое описание чертежей

Настоящее изобретение иллюстрируется в качестве примера, но не ограничения, на чертежах, на которых одинаковыми ссылочными позициями обозначены сходные элементы.

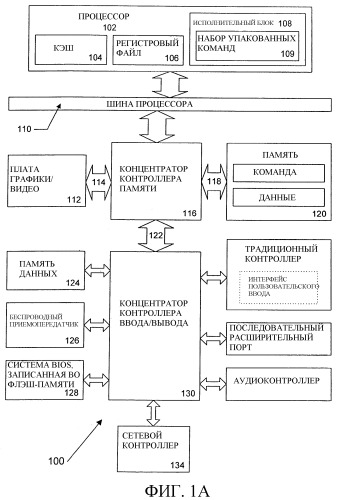

Фиг.1А - блок-схема компьютерной системы с процессором, который включает в себя исполнительные блоки для исполнения команды для знаковой операции умножения в соответствии с одним вариантом осуществления настоящего изобретения;

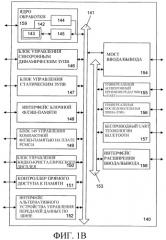

Фиг.1В - блок-схема другой примерной компьютерной системы, соответствующей альтернативному варианту осуществления настоящего изобретения;

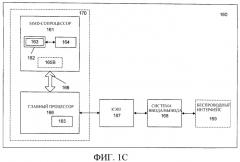

Фиг.1С - блок-схема еще одной примерной компьютерной системы, соответствующей другому альтернативному варианту осуществления настоящего изобретения;

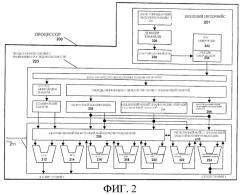

Фиг.2 - блок-схема микроструктуры для процессора одного варианта осуществления, которая включает в себя логические схемы для выполнения знаковой операции умножения в соответствии с настоящим изобретением;

Фиг.3А - представления различных типов упакованных данных в мультимедийных регистрах в соответствии с одним вариантом осуществления настоящего изобретения;

Фиг.3В - типы упакованных данных в соответствии с альтернативным вариантом осуществления;

Фиг.3С - различные представления упакованных типов данных со знаком и без знака в мультимедийных регистрах в соответствии с вариантом осуществления настоящего изобретения;

Фиг.3D - возможный вариант осуществления формата кода операции;

Фиг.3Е - альтернативный формат кода операции;

Фиг.3F - еще один альтернативный формат кода операции;

Фиг.4 - блок-схема варианта осуществления логики для выполнения знаковой операции над операндами упакованных данных в соответствии с настоящим изобретением;

Фиг.5 - иллюстрация действия знаковой операции умножения элементов данных в соответствии с возможным вариантом осуществления настоящего изобретения;

Фиг.6А - блок-схема возможного варианта осуществления схемы для выполнения знаковой операции в соответствии с настоящим изобретением;

Фиг.6В - блок-схема другого варианта осуществления схемы для выполнения знаковой операции в соответствии с настоящим изобретением;

Фиг.7 - иллюстрация действия упакованной знаковой команды на множество элементов данных в соответствии с возможным вариантом осуществления настоящего изобретения;

Фиг.8А - блок-схема последовательности операций, иллюстрирующая возможный вариант осуществления способа для выполнения знаковой операции;

Фиг.8В - блок-схема последовательности операций, иллюстрирующая другой вариант осуществления способа для выполнения знаковой операции;

Фиг.9 - блок-схема возможного варианта осуществления логики для выполнения операции абсолютного значения над операндом упакованных данных;

Фиг.10 - иллюстрация действия алгоритма деблокирования с использованием команд архитектуры с одним потоком команд и множеством потоков данных (SIMD-команд);

Фиг.11 - блок-схема последовательности операций, иллюстрирующая возможный вариант осуществления способа выполнения алгоритма деблокирования с использованием SIMD-команд.

Детальное описание

Последующее описание раскрывает варианты осуществления способа, устройства и команды для выполнения знаковой операции и умножения. В последующем описании многочисленные конкретные детали, такие как типы процессоров, микроструктурные условия, события, механизмы разрешения (разблокировки) и тому подобное, излагаются для того, чтобы обеспечить более глубокое понимание настоящего изобретения. Однако специалистам в данной области техники должно быть понятно, что изобретение может быть реализовано без таких конкретных деталей. Дополнительно, некоторые хорошо известные структуры, схемы и тому подобное не показаны в деталях, чтобы не затемнять сущность изобретения несущественными деталями.

Хотя последующие варианты осуществления описаны со ссылками на процессор, другие варианты осуществления применимы с другими типами интегральных схем и логических устройств. Те же самые методы и указания настоящего изобретения могут быть легко применены в других типах схем или полупроводниковых устройств, которые могут обеспечить выгоды от применения более высокой пропускной способности конвейерной обработки и улучшенных рабочих характеристик. Указания настоящего изобретения применимы к любому процессору или машине, которые исполняют операции над данными. Однако настоящее изобретение не ограничено процессорами и машинами, которые выполняют операции над 256-битовыми, 128-битовыми, 64-битовыми, 32-битовыми или 16-битовыми данными, и может быть применено к любому процессору и машине, в которых необходимо манипулирование с упакованными данными.

В последующем описании, в целях пояснения, изложены различные конкретные детальные особенности, чтобы обеспечить более глубокое понимание настоящего изобретения. Однако специалисту в данной области техники должно быть понятно, что эти конкретные детали не являются необходимыми для практической реализации настоящего изобретения. В других случаях хорошо известные структуры и схемы не поясняются в конкретных деталях, чтобы не затенять сущность настоящего изобретения. Кроме того, в последующем описании приведены примеры, и на чертежах показаны различные примеры в целях иллюстрации. Однако эти примеры не должны трактоваться в ограничительном смысле, так как они приведены только в качестве примеров настоящего изобретения, а не для обеспечения исчерпывающего перечня возможных реализаций настоящего изобретения.

Хотя приведенные ниже примеры описывают обработку команд и распределение в контексте исполнительных блоков и логических схем, другие варианты осуществления настоящего изобретения могут быть реализованы с помощью программного обеспечения. В одном варианте осуществления способы, соответствующие настоящему изобретению, реализованы посредством исполняемых машиной команд. Команды могут быть использованы для обеспечения того, чтобы универсальный или специализированный процессор, который программируется командами, выполнял этапы настоящего изобретения. Настоящее изобретение может обеспечиваться как компьютерный программный продукт или программное обеспечение, которое может включать в себя машино- или компьютерно-читаемый носитель, на котором сохранены команды, которые могут быть использованы для программирования компьютера (или иных электронных устройств) для выполнения процесса соответственно настоящему изобретению. Альтернативно, этапы настоящего изобретения могут выполняться конкретными компонентами программного обеспечения, которые содержат логические схемы с жесткими (постоянными) соединениями («зашитую» логику) для выполнения этапов, или любой комбинацией программируемых компьютерных компонентов и заказных аппаратных компонентов. Такое программное обеспечение может быть сохранено в памяти в системе. Аналогичным образом, код может распространяться по сети или посредством другого считываемого компьютером носителя.

Данный считываемый машиной носитель может включать в себя любой механизм для хранения или передачи информации в форме, обеспечивающей возможность считывания машиной (например, компьютером), но не ограничен гибкими дискетами, оптическими дисками, постоянной памятью на компакт-дисках (CD-ROM), магнитооптическими дисками, постоянной памятью (ROM, ПЗУ), оперативной памятью (RAM, ОЗУ), стираемой программируемой постоянной памятью (EPROM), электрически стираемой программируемой постоянной памятью (EEPROM), магнитными или оптическими картами, флэш-памятью, передачей по сети Интернет, электрической, оптической, акустической или другими формами передаваемых сигналов (например, несущие колебания, инфракрасные сигналы, цифровые сигналы и т.д.). Соответственно, считываемый компьютером носитель включает в себя любой тип носителя (среды передачи)/считываемого компьютером носителя, пригодного для хранения или передачи электронных команд или информации в форме, считываемой машиной (например, компьютером). Кроме того, настоящее изобретение может также предусматривать загрузку в качестве программного продукта. Как таковая, программа может быть перенесена с удаленного компьютера (например, сервера) в запрашивающий компьютер (например, клиент). Перенос программы может производиться посредством электрической, оптической, акустической или других форм сигналов данных, воплощенных в несущем колебании или в среде распространения, по каналу связи (например, модему, сетевому соединению и т.п.).

Процесс проектирования может проходить различные этапы, от создания, моделирования и до изготовления. Данные, представляющие конструкцию, могут представлять такую конструкцию различными путями. Во-первых, как это полезно при моделировании, аппаратные средства могут быть представлены с использованием языка описания аппаратных средств или другого языка функционального описания. Кроме того, на некоторых этапах процесса проектирования может создаваться модель схемного уровня с логическими и/или транзисторными вентилями. Кроме того, большинство конструкций, на некотором этапе, достигают уровня данных, представляющих физическое размещение различных устройств в модели аппаратных средств. В случае, когда используются обычные методы изготовления полупроводников, данные, представляющие модель аппаратных средств, могут быть данными, определяющими наличие или отсутствие различных признаков на различных уровнях маски, для масок, используемых в производстве интегральных схем. В любом представлении конструкции данные могут сохраняться на машиночитаемом носителе любой формы. Оптическая или электрическая волна, модулируемая или иным образом генерируемая для передачи такой информации, память или магнитное или оптическое запоминающее устройство, такое как диск, может представлять собой машиночитаемый носитель. Любой из этих носителей может «нести» или «индицировать» информацию о конструкции или информацию программного обеспечения. Если передается колебание электрической несущей, в котором проявляется код или которое является носителем кода или разрабатываемого продукта, таким образом, что выполняется копирование, буферизация или повторная передача электрического сигнала, то создается новая копия. Таким образом, провайдер коммуникационного обслуживания или сетевой провайдер может сделать копию изделия (несущего колебания), воплощающего в себе методы настоящего изобретения.

В современных процессорах ряд различных исполнительных блоков используется для обработки и исполнения разнообразных кодов и команд. Не все команды создаются одинаковыми, поскольку некоторые являются более быстродействующими для исполнения, в то время как другие могут требовать огромного количества тактовых импульсов. Чем быстрее пропускная способность команд, тем лучше общие рабочие характеристики процессора. Таким образом, было бы предпочтительным иметь как можно больше команд, исполняемых с максимально возможным быстродействием. Однако имеются некоторые команды, которые имеют более высокую сложность и требуют большего в смысле времени исполнения и ресурсов процессора. Например, имеются команды с плавающей запятой, операции загрузки/сохранения, перемещения данных и т.д.

По мере того как все больше компьютерных систем используется в Интернет-приложениях и мультимедийных приложениях, с течением времени вводится дополнительная поддержка процессоров. Например, одиночная команда, команды c множеством данных с целыми числами/с плавающей запятой типа «один поток команд и множество потоков данных» (SIMD) и потокового SIMD расширения (SSE) являются командами, которые сокращают общее количество команд, требуемых для исполнения конкретной программной задачи, что в свою очередь может снизить потребляемую мощность. Эти команды могут ускорять выполнение программного обеспечения за счет операций с множеством элементов данных, осуществляемых параллельно. В результате выигрыш по рабочим характеристикам может быть достигнут в широком диапазоне приложений, включая обработку видео, речи и изображений/фотоснимков. Реализация SIMD-команд в процессорах и логических схемах подобного типа обычно связана с рядом вопросов. Кроме того, сложность SIMD-операций часто приводит к необходимости дополнительных схем, чтобы корректным образом осуществлять обработку и манипулирование данными. В настоящее время нет знаковой SIMD-команды для осуществления умножения. А также нет SIMD-команды для операций с абсолютными значениями. Без наличия знаковой операции умножения, требуется большое число команд и регистров данных для достижения тех же результатов в приложениях, таких как аудио/видео сжатие, обработка и манипуляция. Таким образом, знаковые команды в соответствии с настоящим изобретением могут снизить непроизводительные издержки на кодирование и требования к ресурсам. Варианты осуществления настоящего изобретения обеспечивают путь реализации знаковой операции в качестве алгоритма, который использует связанные с архитектурой SIMD аппаратные средства. Некоторые варианты осуществления также обеспечивают пути реализации операции с абсолютными значениями. В настоящее время обработка данных в SIMD-регистре является до некоторой степени трудной и утомительной. Некоторые алгоритмы требуют больше команд для упорядочения данных для арифметических операций, чем действительное число команд для выполнения этих операций. За счет реализации вариантов осуществления знаковой операции, выполняющей умножение в соответствии с настоящим изобретением, можно в значительной степени уменьшить количество команд, требуемых для реализации знаковой обработки.

Варианты осуществления настоящего изобретения связаны с командой для реализации версии знаковой операции. Знаковая операция определяет то, является ли данное число положительным, отрицательным или нулем. В процессе знаковой (signum) операции функция оценивает число следующим образом: для x>0 signum(x)=1; для x=0 signum(x)=0 и для x<0 signum(x)=-1. Однако в мультимедийных приложениях умножение значения данных на знак другого значения часто требуется в процессе выполнения различных алгоритмов. Знаковая операция, которая осуществляет умножение, может устранить необходимость в выполнении многих отдельных операций. Варианты осуществления представляемой знаковой операции обеспечивают более значительную функциональность, чем обычная знаковая операция, а также включают осуществление умножения.

Знаковая команда в соответствии с настоящим изобретением вычисляет следующую операцию: DEST(адресат)=SRC(источник)1 x (SIGNUM(знак)(SRC(источник)2). Если SRC2 положительно, знаковая (signum) операция над SRC2 даст значение '+1'. Если SRC2 равно нулю, то результатом знаковой операции (signum) над SRC2 будет нуль. Если SRC2 отрицательно, то знаковая (signum) операция над SRC2 даст значение '-1'. Знаковая операция умножения в виде варианта осуществления настоящего изобретения заключается во взятии знака второго элемента данных и умножении результата знаковой операции на значение первого элемента данных для получения результирующего продукта. Такая знаковая операция, согласно одному варианту осуществления, может быть представлена как

если SOURCE2<0, то DEST=SOURCE1 x '-1';

иначе, если SOURCE2=0, то DEST=0;

иначе, если SOURCE2>0, то DEST=SOURCE1 x '+1'

Для операнда упакованных данных этот процесс может быть применен к каждой позиции элемента данных.

Кроме того, в одном варианте осуществления знаковая операция с умножением также может имитировать знаковую (signum) операцию путем использования значения '1' в качестве первого элемента источника и представляющего интерес значения в качестве второго элемента источника в знаковой операции. Поскольку знаковая операция данного варианта осуществления обуславливает умножение первого элемента источника на одно из следующего: '+1', '0' или '-1', на основе знакового значения второго элемента, операция signum здесь может быть дублирована. Аналогичным образом, варианты осуществления знаковой операции данного изобретения могут также выполнять операции с абсолютными значениями путем установки первого элемента источника на знаковую операцию, соответствующую второму элементу источника. Это достижимо, поскольку значение источника по существу будет умножаться на свой собственный знак, тем самым приводя к результату в виде '0' или положительного значения.

На фиг.1А показана блок-схема приведенной для примера компьютерной системы, выполненной с процессором, который включает в себя исполнительные блоки для выполнения знаковой операции умножения в соответствии с одним вариантом осуществления настоящего изобретения. Система 100 включает в себя компонент, такой как процессор 102, для использования исполнительных блоков, включающих в себя логику для выполнения алгоритмов для обработки данных, в соответствии с настоящим изобретением, как в описываемом здесь варианте осуществления. Система 100 представляет системы обработки, основанные на микропроцессорах PENTIUM® III, PENTIUM® 4, XeonTM, Itanium®, XScaleTM и/или StrongARMTM, доступных от компании Intel Corporation (Santa Clara, California), хотя могут использоваться и другие системы (включая персональные компьютеры с другими микропроцессорами, рабочие станции для проектирования, компьютерные приставки и тому подобные средства). В одном варианте осуществления образцовая система 100 может исполнять версию операционной системы WINDOWSTM, доступной от компании Microsoft Corporation (Redmond, Washington), хотя также могут использоваться и другие операционные системы (например, UNIX и Lunix), встроенное программное обеспечение и/или графические пользовательские интерфейсы. Таким образом, настоящее изобретение не ограничено какой-либо конкретной комбинацией аппаратных схемных средств и программного обеспечения.

Представленное усовершенствование не ограничивается компьютерными системами. Альтернативные варианты осуществления настоящего изобретения могут использоваться в других устройствах, таких как портативные устройства и встроенные прикладные программы. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства протокола Интернет, цифровые камеры, персональные цифровые помощники (PDA) и карманные ПК. Встроенные прикладные программы могут включать в себя микроконтроллер, цифровой процессор сигналов, встроенную (накристальную) систему, сетевые компьютеры, компьютерные приставки к телевизорам, сетевые концентраторы, коммутаторы глобальных сетей или любую другую систему, которая выполняет знаковые операции и/или операции абсолютного значения над операндами. Кроме того, некоторые архитектуры реализованы для обеспечения возможности командам воздействовать на различные данные одновременно для улучшения эффективности мультимедийных приложений. По мере того как тип и объем данных увеличивается, компьютеры и их процессоры должны совершенствоваться для манипулирования данными более эффективными способами.

На фиг.1А показана блок-схема компьютерной системы 100 с процессором 102, который включает в себя один или несколько исполнительных блоков 108 для обработки алгоритма выделения знака элемента данных из одного операнда и умножения этого знака на другой элемент данных в соответствии с настоящим изобретением. Настоящий вариант осуществления описан в контексте однопроцессорной настольной или серверной системы, но альтернативные варианты осуществления могут быть включены в мультипроцессорную систему. Система 100 является примером архитектуры концентратора. Компьютерная система 100 включает в себя процессор 102 для обработки сигналов данных. Процессор 102 может представлять собой, например, микропроцессор компьютера с полным набором команд (CISC), микропроцессор с командными словами сверхбольшой длины (VLIW), процессор, реализующий комбинацию наборов команд, или любое другое процессорное устройство, такое как цифровой процессор сигналов (DSP). Процессор 102 связан с процессорной шиной 110, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 выполняют свои обычные функции, которые хорошо известны специалистам в данной области техники.

В одном варианте осуществления процессор 102 включает в себя память 104 внутреннего кэша уровня 1 (L1). В зависимости от архитектуры, процессор 102 может иметь отдельный внутренний кэш или множество уровней внутреннего кэша. Альтернативно, в другом варианте осуществления память кэша может быть внешней по отношению к процессору 102. Другие варианты осуществления могут также включать в себя комбинацию как внутреннего, так и внешнего кэша, в зависимости от конкретной реализации и потребностей. Регистровый файл 106 может сохранять различные типы данных в различных регистрах, включая целочисленные регистры, регистры с плавающей запятой, регистры статуса и регистры указателей команд.

Исполнительный блок 108, включающий в себя логику для выполнения целочисленных операций и операций с плавающей запятой, также находится в процессоре 102. Процессор 102 также включает в себя ПЗУ микрокода, которое сохраняет микрокод для некоторых макрокоманд. Для данного варианта осуществления исполнительный блок 108 включает в себя логику для обработки набора 109 упакованных команд. В одном варианте осуществления набор 109 упакованных команд включает в себя упакованную знаковую команду для модифицирования значения знака данных. За счет включения упакованного набора 109 команд в набор команд универсального процессора 102, вместе со связанными схемами для выполнения команд, операции, используемые многими мультимедийными приложениями, могут выполняться с использованием упакованных данных в универсальном процессоре 102. Это может исключить потребность в переносе меньших блоков данных по процессорной шине данных для выполнения одной или нескольких операций над элементом данных в каждый данный момент времени.

Альтернативные варианты осуществления исполнительного блока 108 также могут использоваться в микроконтроллерах, встроенных процессорах, графических устройствах, ЦПБ и других типах логических схем. Система 100 включает в себя память 120. Память 120 может представлять собой динамическое запоминающее устройство с произвольной выборкой (ЗУПВ) (DRAM), статическое ЗУПВ (SRAM), устройство флэш-памяти или другие устройства памяти. Память 120 может сохранять команды и/или данные, представленные сигналами данных, которые могут исполняться процессором 102.

Микросхема 116 системной логики связана с шиной 110 процессора и памятью 120. Микросхема 116 системной логики в показанном варианте осуществления представляет собой концентратор контроллера памяти (ККП). Процессор 102 может осуществлять информационный обмен с ККП 116 через шину 110 процессора. ККП 116 обеспечивает широкополосный канал 118 памяти к блоку 120 памяти для хранения команд и данных и для хранения команд графики, данных и текстур. ККП 116 предназначен для пересылки сигналов данных между процессором 102, блоком 120 памяти и другими компонентами в системе 100 и для шунтирования сигналов данных между шиной 110 процессора, блоком 120 памяти и системой 122 ввода/вывода. В некоторых вариантах осуществления микросхема 116 системной логики может обеспечить графический порт для связи с контроллером 112 графики. ККП 116 связан с блоком 120 памяти через интерфейс 118 памяти. Графическая плата 112 связана с ККП 116 через межсоединение 114 ускоренного графического порта.

Система 100 использует специализированную шину 122 интерфейса концентратора для соединения ККП 116 с концентратором контроллера ввода/вывода (ККВВ) 130. ККВВ 130 обеспечивает прямые соединения с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Локальная шина ввода/вывода является высокоскоростной шиной ввода/вывода для соединения периферийных устройств с блоком 120 памяти, набором микросхем и процессором 102. В качестве примеров могут служить контроллер аудиоданных, концентратор 128 программно-аппаратных средств (система BIOS, записанная во флэш-памяти), беспроводный приемопередатчик 126, блок 124 хранения данных, традиционный контроллер ввода/вывода, содержащий интерфейсы пользовательского ввода и клавиатуры, последовательный расширительный порт, например, соответствующий универсальной последовательной шине (USB), и сетевой контролер 134. Блок 124 хранения данных может содержать дисковод на жестких дисках, ПЗУ на компакт-дисках (CD-ROM), устройство флэш-памяти или другое устройство массовой памяти.

В другом варианте осуществления системы исполнительный блок для исполнения алгоритма со знаковой командой может быть использован с системой на микросхеме. Один вариант осуществления системы на микросхеме содержит процессор и память. В качестве памяти для такой системы может быть использована флэш-память. Флэш-память может находиться на том же кристалле, что и процессор и другие компоненты системы. Дополнительно, другие логические блоки, такие как контроллер памяти или графический контролер, могут также находиться в системе на микросхеме.

На фиг.1В показан альтернативный вариант осуществления системы 140 обработки данных, которая реализует принципы настоящего изобретения. Возможным вариантом системы 140 обработки данных могут быть процессоры прикладных программ Intel®PCA (персональная архитектура Интернет-клиента), основанные на технологии XScaleTM (как описано в WWW, адрес developer.intel.com). Специалистам в данной области техники должно быть понятно, что описанные здесь варианты осуществления могут быть использованы с альтернативными системами обработки без отклонения от сущности настоящего изобретения.

Компьютерная система 140 содержит ядро 159 обработки, обеспечивающее выполнение SIMD-операций, включая знаковую операцию и операцию абсолютного значения. В одном варианте осуществления ядро 159 обработки представляет собой блок обработки с архитектурой любого типа, включая, но не ограничиваясь, архитектуры CISC, RISC или VLIW. Ядро 159 обработки может также быть пригодным для изготовления по одному или нескольким технологическим процессам и, будучи представленным на машино-читаемых носителях с достаточной детальностью, может быть пригодным для облегчения такого изготовления.

Ядро 159 обработки включает в себя исполнительный блок 142, набор регистровых файлов 145 и декодер 144. Ядро 159 обработки также включает в себя дополнительные схемы (не показаны), что не является существенным для понимания настоящего изобретения. Исполнительный блок 142 используется для исполнения команд, принимаемых ядром 159 обработки. В дополнение к распознаванию типовых команд процессора, исполнительный блок 142 может распознавать команды в наборе 143 упакованных (в упакованном формате) команд для выполнения операций с использованием упакованных форматов данных. Набор 143 упакованных команд включает в себя команды для поддержки операций со знаками и абсолютными значениями и может также включать в себя другие упакованные команды. Исполнительный блок 142 связан с регистровым файлом 145 внутренней шиной. Регистровый файл 145 представляет область памяти в ядре 159 обработки для хранения информации, включая данные. Как упомянуто выше, понятно, что область памяти, используемая для хранения упакованных данных, не является критичной. Исполнительный блок 142 связан с декодером 144. Декодер 144 используется для декодирования команд, полученных ядром 159 обработки, для получения сигналов управления и/или точек входа в микрокод. В ответ на эти сигналы управления и/или точки входа в микрокод исполнительный блок 142 выполняет соответствующие операции.

Ядро 159 обработки связано с шиной 141 для информационного обмена с различными другими системными устройствами, которые могут включать в себя, не ограничиваясь указанным, например, блок 146 управления синхронным динамическим запоминающим устройством с произвольной выборкой (ЗУПВ) (SDRAM), блок 147 управления статическим ЗУПВ, интерфейс 148 блочной флэш-памяти, блок 149 управления компактной флэш-памятью на плате PCMCIA, блок 150 управления жидкокристаллического дисплея, контроллер 151 прямого доступа к памяти, интерфейс 152 альтернативного устройства управления передачей данных по шине («хозяина» шины). В одном варианте осуществления система 140 обработки данных может также содержать мост 154 ввода/вывода для информационного обмена с различными устройствами ввода/вывода через шину 153 ввода/вывода. Такие устройства ввода/вывода могут включать в себя, без каких-либо ограничений, например, универсальный асинхронный приемопередатчик (UART) 155, универсальную последовательную шину (USB) 156, беспроводный UART 157, выполненный по технологии Bluetooth, и интерфейс 158 расширения ввода/вывода.

Один вариант осуществления системы 140 обработки данных обеспечивает мобильную, сетевую и/или беспроводную связь и ядро 159 обработки, обеспечивающее выполнение SIMD-операций, включая операцию знака или абсолютного значения. Ядро 159 обработки может программироваться с использованием различных алгоритмов передачи аудио, видео, формирования изображений и информационного обмена, включая дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование Фурье, дискретное косинусное преобразование и их соответствующие инверсные преобразования; методы сжатия/восстановления (сжатых данных), такие как преобразование цветового пространства, анализ движения для кодирования видеоданных или компенсации движения для декодирования видеоданных; и функции модуляции/демодуляции (модем), такие как импульсно-кодовая модуляция (ИКМ).

На фиг.1С показан еще один альтернативный вариант осуществления системы обработки данных, имеющей возможность выполнения SIMD-операций знака или абсолютного значения. В соответствии с альтернативным вариантом осуществления, система 160 обработки данных может включать в себя главный процессор 166, SIMD-сопроцессор 161, кэш-память (быстродействующую буферная память небольшой емкости) 167 и систему 168 ввода/вывода. Система 168 ввода/вывода дополнительно может быть связана с беспроводным интерфейсом 169. SIMD-сопроцессор 161 имеет возможность выполнения SIMD-операций, включая операцию знака или абсолютного значения. Ядро 170 обработки может быть пригодным для изготовления по одному или нескольким технологическим процессам и, будучи представленным на машино-читаемых носителях с достаточной детальностью, может быть пригодным для облегчения изготовления всей или части системы 160 обработки данных, включая ядро 170 обработки.

В одном варианте осуществления SIMD-сопроцессор включает в себя исполнительный блок 162 и набор регистровых файлов 164. Вариант осуществления главного процессора 165 содержит декодер для распознавания команд из набора 163 команд, включая упакованные SIMD-команды знака и абсолютного значения для исполнения исполнительным блоком 162. В альтернативных вариантах SIMD-сопроцессор 161 также содержит по меньшей мере часть декодера 165В для декодирования команд из набора 163 команд. Ядро 170 обработки также включает в себя дополнительные схемы (не показаны), которые не являются необходимыми для понимания сущности настоящего изобретения.

В процессе работы главный процессор 166 исполняет поток команд обработки данных, которые управляют операциями обработки данных общего типа, включая взаимодействия с кэш-памятью 167 и системой ввода/вывода 168. В поток команд обработки данных встроены команды SIMD-сопроцессора. Декодер 165 главного процессора 166 распознает эти команды SIMD-сопроцессора как команды того типа, которые должны выполняться присоединенным SIMD-сопроцессором 161. Соответственно, главный процессор 166 выдает эти команды SIMD-сопроцессора (или сигналы управления, представляющие команды SIMD-сопроцессора) в шину 166 сопроцессора, из которой они принимаются присоединенными SIMD-сопроцессорами. В этом случае SIMD-сопроцессор будет принимать и исполнять любые принятые команды SIMD-сопроцессора, предназначенные для него.

Данные могут приниматься через беспроводный интерфейс 169 для обработки команд SIMD-сопроцессором. Например, речевая передача может приниматься в форме цифрового сигнала, который может обраб