Обработка данных с помощью сопроцессора

Иллюстрации

Показать всеИзобретение относится к системам обработки данных. Техническим результатом является повышение быстродействия. Система обработки данных содержит основной процессор и сопроцессор, включающий память, команды (USALD) загрузки, поступающие в сопроцессор, предназначены для загрузки изменяющегося значения данных после выравнивания, для задания операций обработки данных, осуществляемых над операндами в пределах загружаемых слов данных для формирования слов данных результата. Операции обработки обуславливают вычисление суммы абсолютных разностей для ряда значений байтов элементов изображения. Результат этого вычисления сохраняется в накапливающем регистре. 3 н. и 9 з.п. ф-лы, 7 ил.

Реферат

Настоящее изобретение относится к системам обработки данных. Более конкретно, это изобретение относится к системам обработки данных, включающим в себя как основной процессор, так и сопроцессор.

Возможность создания систем обработки данных, включающих в себя как основной процессор, так и сопроцессор, известна. Примерами таких систем обработки данных являются системы, разрабатываемые фирмой ARM Limited, Кембридж, Англия, поставляющей такие основные процессоры, как ARM7 или ARM9, которые можно объединить с таким сопроцессором, как сопроцессор Piccolo, для выполнения таких функций, как специализированные операции цифровой обработки сигналов. В качестве других примеров сопроцессоров можно привести сопроцессоры для осуществления арифметических операций в режиме с плавающей точкой и т.д.

Сопроцессоры часто используют для того, чтобы в пределах системы обработки данных обеспечить дополнительные функциональные возможности, которые не требуются в основной системе, но могут оказаться полезными в некоторых обстоятельствах, когда оказывается оправданной подача дополнительных служебных сигналов или данных с помощью подходящего сопроцессора. В частности, к пользующимся спросом средам обработки данных относятся те, которые предусматривают цифровую обработку сигналов, такую как манипулирование видеоизображениями. Объемы данных, требующих обработки в таких приложениях, могут быть большими. Вследствие этого возникает проблема создания систем обработки данных, способных справляться с необходимым объемом обработки и одновременно имеющих относительно низкую стоимость и низкое энергопотребление.

Один из подходов к решению задач в таких приложениях, характеризующихся интенсивностью вычислений, заключается в разработке схем специального назначения для цифровой обработки сигналов. Такие схемы специального назначения могут иметь архитектуру, специально приспособленную для выполнения операций обработки в относительно ограниченном диапазоне, но с относительно высокой скоростью. В качестве примера отметим, что можно предусмотреть многочисленные каналы данных для пересылки данных в соответствующие части схемы и из них в параллельном режиме. Хотя такая компоновка и может быть способна справиться с требуемыми большими объемами обработки данных, ее обычным недостатком является отсутствие гибкости. Эта негибкость может означать, что сравнительно незначительное изменение в алгоритме, который требуется выполнить, может потребовать дорогостоящих соответствующих изменений аппаратного обеспечения. Это является отличием от процессора общего назначения, который обычно изначально сконструирован с возможностью выполнения огромного количества разных алгоритмов.

В одном аспекте настоящего изобретения предложено устройство для обработки данных, содержащее

основной процессор, реагирующий на команды программы для выполнения операций обработки данных, и

сопроцессор, подключенный к упомянутому основному процессору и реагирующий на команду загрузки в сопроцессор, выдаваемую упомянутым основным процессором для загрузки одного или более загружаемых слов данных в упомянутый сопроцессор и выполнения, по меньшей мере, одной операции обработки посредством сопроцессора, предписываемой упомянутой командой загрузки в сопроцессор, с использованием упомянутого одного или более загружаемых слов данных для выдачи данных операндов с формированием, по меньшей мере, одного слова данных результата,

при этом по упомянутой команде загрузки в сопроцессор изменяющееся количество загружаемых слов данных загружается в упомянутый сопроцессор в зависимости от того, выровнен ли начальный адрес упомянутых данных операндов в пределах упомянутого одного или нескольких слов данных по границе слова.

В изобретении отражен тот факт, что в системе, содержащей основной процессор общего назначения, можно предусмотреть сопроцессор с весьма специфичными функциями. В частности, можно достичь значительных преимуществ в скорости обработки и плотности кодов, предусмотрев возможность, в соответствии с которой команды загрузки в сопроцессор также будут запускать операции обработки данных, выполняемые над операндами в пределах загружаемых слов, с формированием слов данных результата. Хотя такой сопроцессор играет весьма специфичную роль в пределах системы, обнаружено, что если предусмотреть сочетание его с основным процессором общего назначения, то такое сочетание окажется в состоянии обеспечить выгодное увеличение производительности обработки с одновременным сохранением способности процессора общего назначения приспосабливаться к различным алгоритмам и обстоятельствам.

Хотя системы памяти и структуры шин зачастую предусмотрены для работы только при определенном выравнивании с базовым адресом системы, желаемые значения операндов, которыми манипулирует и пользуется сопроцессор, могут иметь другое выравнивание. Таким образом, чтобы обеспечить улучшенную рабочую характеристику, количество загружаемых слов данных, которые загружаются в сопроцессор, должно зависеть от выравнивания. В качестве примера отметим, что если желательно загрузить восемь восьмиразрядных операндов по команде загрузки в сопроцессор с использованием пословно выровненных тридцатидвухразрядных слов данных, то этого можно достичь либо с помощью двух слов данных, если операнды выровнены с границей слова, либо с помощью трех слов данных, если операнды не выровнены с границей слова.

В частности, предпочтительными конкретными вариантами осуществления изобретения являются те, в которых внутри сопроцессора предусмотрена память сопроцессора для локального хранения слов данных, используемых в качестве операндов в сочетании с загружаемыми словами данных. Эта компоновка отражает тот факт, что во многих ситуациях вычислений, встречающихся в повседневной действительности, относительно малый поднабор слов данных часто требуется для использования со значительно более обширным набором слов данных, которые требуются менее часто. Этот признак воплощается в рассматриваемой компоновке за счет локального хранения часто требующихся слов данных таким образом, что требуемая пропускная способность канала данных между основным процессором и сопроцессором преимущественно уменьшается. В отличие от обычной системы цифровой обработки сигналов в рассматриваемой системе, как правило, труднее просто добавить больше каналов данных между основным процессором и сопроцессором по потребности, поскольку на архитектуру основного процессора могут накладывать ограничения другие факторы.

Рабочая характеристика (производительность) системы улучшается в тех конкретных вариантах осуществления, в которых загружаемые слова данных, выбираемые из памяти, подключенной к основному процессору, передаются в сопроцессор без сохранения в регистрах основного процессора. В этой ситуации будет видно, что основной процессор сможет сыграть роль механизма генератора адреса и доступа в память для сопроцессора.

В частности, удобен вариант, в котором основной процессор включает в себя регистр, выполненный с возможностью хранения значения адреса, указывающего слова данных, загружаемых в сопроцессор. Это позволяет основному процессору управлять указателем адреса, обеспечивая тем самым повышенную степень гибкости применительно к типу поддерживаемого алгоритма.

Следует по достоинству оценить тот факт, что слова данных, загружаемые и подвергающиеся манипулированию, могут иметь множество значений ширины. В качестве примера отметим, что слова данных могут быть тридцатидвухразрядными словами данных, содержащими по четыре восьмиразрядных операнда, каждый из которых представляет собой восьмиразрядное значение элемента изображения. Вместе с тем, следует по достоинству оценить тот факт, что слова данных и операнды могут иметь огромное множество размеров, например могут быть шестнадцатиразрядными, шестидесятичетырехразрядными, стодвадцативосьмиразрядными и т.п.

Хотя выравнивание и может изменяться во многих ситуациях, встречающихся в повседневной действительности, обычно оно является одинаковым для большого количества последовательных доступов. В такой ситуации, в предпочтительных конкретных вариантах осуществления можно использовать некоторое значение содержимого регистра внутри сопроцессора для хранения некоторого значения выравнивания, которое указывает выравнивание между операндами данных и словами данных и на которое может реагировать сопроцессор с целью управления количеством слов данных, загружаемых по каждой команде загрузки в сопроцессор.

Хотя сопроцессор может выполнять огромное множество операций обработки над операндами в пределах загружаемых слов и в зависимости от конкретной системы, изобретение применимо, в частности, в системах, где желательно выполнять суммирование абсолютных разностей между значениями из некоторого множества значений операндов. Получение суммы абсолютных разностей для большого количества данных часто представляет собой значительную часть нагрузки обработки, которую должен выполнять процессор общего назначения при выполнении таких операций, как согласование блоков элементов изображения во время обработки изображений. Перекладывание выполнения огромной массы относимых к низкому уровню вычислений суммы абсолютных разностей на сопроцессор обеспечивает достижение значительного улучшения рабочей характеристики при одновременном сохранении гибкости процессора общего назначения и позволяет использовать имеющие специальное назначение вычисления суммы абсолютных разностей в качестве части огромного множества различных алгоритмов.

В пределах системы для вычисления суммы абсолютных значений можно предусмотреть накапливающий регистр внутри сопроцессора для накапливания общей суммы вычисляемых абсолютных разностей. В этом накапливающем регистре, находящемся внутри сопроцессора, можно находить данные и выдавать их обратно в основной процессор для дальнейших манипуляций, если это необходимо, но при этом удерживать такие данные внутри сопроцессора для ускорения работы и снижения требований к передаче данных между сопроцессором и основным процессором.

Чтобы сделать более важной роль основного процессора в качестве генератора адреса для сопроцессора, команды загрузки в сопроцессор в предпочтительном варианте могут включать в себя значение смещения, применяемое к значению адреса, хранящемуся в качестве указателя внутри основного процессора. Это значение смещения можно - по выбору - использовать для обновления значения указателя либо перед использованием значения указателя, либо после такого использования.

В изобретении также предложен компьютерный программный продукт, включающий в себя команды загрузки в сопроцессор, описанные выше. Этот компьютерный программный продукт может быть выполнен в форме такого поставляемого носителя информации, как компакт-диск или флоппи-диск, или может быть частью программно-аппаратных средств, встраиваемых в устройство, или может быть динамически загружаемым, например, через посредство линии связи с сетью.

Ниже, лишь в качестве примера, приводится описание конкретного варианта осуществления изобретения со ссылками на чертежи, при этом:

на фиг.1 условно изображено желаемое вычисление суммы абсолютных значений;

на фиг.2 условно изображено сочетание основного процессора и сопроцессора;

на фиг.3 представлена схема последовательности операций, условно иллюстрирующая пример типа операций, которые может выполнять система, показанная на фиг.2;

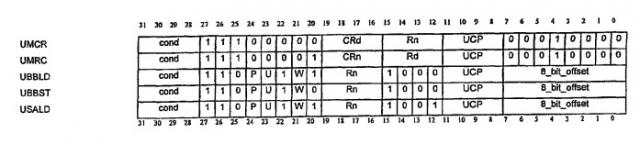

на фиг.4 изображены три возможные команды загрузки в сопроцессор; и

на фиг.5-7 показаны дополнительные подробности сопроцессора в соответствии с одним возможным конкретным вариантом осуществления.

На фиг.1 изображен текущий блок 2 элементов изображения, для которого желательно найти наилучшее согласование в пределах опорного изображения. Этот текущий блок 2 элементов изображения содержит блок 8×8 из 8-битных значений байта элементов изображения. Этот текущий блок 2 элементов изображения сравнивают с эталонными блоками 4 элементов изображения, расположенными с различными векторными смещениями от текущего блока 2 элементов изображения. При каждом векторном смещении желательно провести тест на согласование, поэтому вычисляют выражение суммы абсолютных разностей, показанное на фиг.1. Это выражение определяет абсолютную разность между соответствующими значениями соответственных элементов изображения для обоих рассматриваемых блоков и отражает суммирование получаемых шестидесяти четырех значений абсолютных разностей. Хорошее согласование изображения в общем случае демонстрируется малым значением суммы абсолютных разностей. В пределах системы обработки изображений, например, системы, обеспечивающей обработку по стандарту типа MPEG, такое вычисление суммы абсолютных значений часто бывает необходимым и может приводить к появлению нежелательно большого объема служебных данных обработки для процессора общего назначения.

На фиг.2 изображена система 6 обработки данных, включающая в себя основной процессор 8, сопроцессор 10, кэш-память 12 и основную память 14. Основной процессор 8 включает в себя блок 16 регистров, хранящий значения регистров общего назначения, которые могут использоваться основным процессором 8. Основной процессор 8 может быть, например, одним из основных процессоров, разрабатываемых фирмой ARM Limited, Кембридж, Англия.

Основной процессор 8 подключен к кэш-памяти 12, которая служит для обеспечения высокоскоростного доступа к наиболее часто требующимся значениям данных. Вне кэш-памяти 12 предусмотрена менее скоростная, но более емкая основная память 14.

Сопроцессор 10 подключен к шине сопроцессора, имеющейся в основном процессоре 8, и реагирует на команды для сопроцессора, принимаемые и выполняемые основным процессором 8 с целью выполнения предварительно определенных операций. В рамках архитектуры ARM предусмотрены команды загрузки в сопроцессор, которые служат для загрузки некоторого значения данных в сопроцессор. Сопроцессор 10, изображенный на фиг.2, распространяет функциональные возможности таких команд загрузки в сопроцессор на использование их также для направления в сопроцессор указаний о том, что он должен выполнить некоторые предварительно заданные операции обработки над значениями операндов в пределах слов данных, загружаемых в сопроцессор 10.

Более конкретно, сопроцессор 10 включает в себя память 18 сопроцессора, выравнивающий регистр 20, накапливающий регистр 22 и функциональный блок 24 управления и арифметических операций. Конкретные команды загрузки в сопроцессор можно использовать для загрузки шестнадцати тридцатидвухразрядных слов данных в память 18 сопроцессора. Каждое из этих шестнадцати слов данных содержит четыре восьмиразрядных значений элементов изображения и соответствует блоку размером 8х8 элементов изображения, который является текущим блоком 2, изображенным на фиг.1. Эти значения элементов изображения в пределах текущего блока 2 будут сравниваться в качестве блока - с использованием суммы абсолютных разностей - с эталонными блоками 4 элементов изображения, отбираемыми из множества различных положений в пределах эталонного изображения, для определения эталонного блока 4, который дает наименьшую сумму абсолютных разностей и поэтому соответствует наилучшему согласованию изображения. Локальное хранение часто используемых значений элементов изображения текущего блока 2 в памяти 18 сопроцессора представляет собой эффективное использование ресурсов обработки. Сразу же после загрузки текущего блока 2 в память 18 сопроцессора основной процессор 8 выполняет специальные команды загрузки в сопроцессор (команды USALD (ВЗсВСАРиНАК - команды выполнения загрузки с побайтным выравниванием восьми байтов из памяти, выполнения вычислений суммы абсолютных разностей (SAD (ВСАР)) и накопления в регистре накопления сопроцессора - CR_ACC (НАК_РС)), которые служат для загрузки либо двух, либо трех слов данных в сопроцессор 10, и обеспечивают вычисление значения суммы абсолютных разностей для операндов, представляющих собой восьмиразрядные значения элементов изображения, в пределах таких загружаемых слов данных. Команда USALD в потоке команд основного процессора 10 также проходит (либо напрямую, либо в форме одного или более сигналов управления) в сопроцессор 10, где она запускает логический функциональный блок 24 управления и арифметических операций, обеспечивая управление загрузкой требуемого количества слов данных либо из кэш-памяти 12, либо из основной памяти 14 через посредство основного процессора 8, а также последующее выполнение вычисления суммы абсолютных разностей с использованием упомянутых загруженных значений, а также значений их памяти 18 сопроцессора. Выравнивающий регистр 20 хранит значение выравнивания, которое заранее задается командой загрузки в регистр сопроцессора, выполняемой основным процессором 8. Логический функциональный блок 24 управления и арифметических операций реагирует на это значение выравнивания, осуществляя загрузку либо двух тридцатидвухразрядных слов данных, когда операнды выровнены с границами слов, либо трех тридцатидвухразрядных слов данных, когда такое выравнивание отсутствует. Сбоку от кэш-памяти 12 на фиг.2 изображены восемь желательных значений операндов элементов изображения, хранящихся в кэш-памяти и не выровненных с границами слов, вместе со значением смещения выравнивания из регистра CR_BYO (СМБ_РСО, это регистр сопроцессора, хранящий смещение в байтах, используемое для загрузки блока из эталонного кадра). В показанном примере три тридцатидвухразрядных слова данных нужно загрузить в сопроцессор 10 в ответ на значение адреса [Rn], хранящееся в одном из регистров, имеющихся в блоке 16 регистров, и указывающее на слово, совпадающее (выровненное) по адресу, как показано на чертеже. Когда осуществляется выборка трех тридцатидвухразрядных слов данных, логический функциональный блок 24 управления и арифметических операций осуществляет операцию мультиплексирования для выделения требуемых операндов из тех, которые имеются в пределах слов данных, в зависимости от указанного значения выравнивания. Значения операндов, извлекаемые из загружаемых слов данных, подвергаются вычислению суммы абсолютных разностей, которое образует часть вычисления, изображенного на фиг.1, с использованием стандартных арифметико-логических средств обработки, таких как блоки суммирования и вычитания. Следует по достоинству оценить тот факт, что в изображенном примере восьмибайтные операнды элементов изображения на самом деле представляют собой один ряд в рамках сравнения блоков, проводимого между текущим блоком 2 элементов изображения и эталонным блоком 4 элементов изображения, изображенными на фиг.1. Чтобы провести все вычисление, изображенное на фиг.1, потребуется поочередно выполнить восемь таких команд загрузки в сопроцессор. Сумма абсолютных разностей, вычисляемая по каждой из этих команд для сопроцессора, накапливается в накапливающем регистре 22. Следовательно, после выполнения всех восьми команд загрузки в сопроцессор, каждая из которых задает сумму абсолютных разностей для ряда, будет найдена сумма абсолютных разностей для блока, результат вычисления которой сохранится в накапливающем регистре 22. Это сохраненное знание можно затем возвратить в основной процессор 8, например, по командам основного процессора, предписывающим возврат значения регистра сопроцессора в один из регистров, имеющихся в блоке 16 регистров.

В примере, рассмотренном выше, указатель адреса, который хранится в регистре, имеющемся в блоке 16 регистров, непосредственно указывает начальный адрес первого слова данных, подлежащего выборке. Вместе с тем, возможен и вариант, в котором это хранящееся значение указателя может подвергаться смещению, например, смещению на десять двоичных разрядов, которое применяется к хранящемуся значению указателя для указания действительного адреса, по которому следует осуществить доступ. В некоторых обстоятельствах удобна возможность дополнительного использования такого смещения для обновления значения указателя после каждого использования. В сущности, это позволяет командам загрузки в сопроцессор перескакивать через подходящие количества данных, задающих эталонное изображение, для выборки различных рядов по восемь элементов изображения, необходимых для конкретного эталонного блока 4, без обязательного привлечения дополнительных команд основного процессора к изменению указателя.

На фиг.3 представлена схема последовательности операций, условно иллюстрирующая один пример типа операций, которые может выполнять система, показанная на фиг.2. На этапе 26 шестнадцать слов, представляющих текущий блок 2 элементов изображения, загружаются из кэш-памяти 12 или основной памяти 14 в память 18 сопроцессора. На этапе 28 в регистр Rn, находящийся внутри основного процессора 8, загружается значение указателя, которое указывает начало эталонного блока 4 в памяти. На этапе 30 находящееся в выравнивающем регистре 20 сопроцессора 10 значение выравнивания загружается с использованием команды загрузки в регистр сопроцессора, выдаваемой основным процессором 8. Следует по достоинству оценить тот факт, что этапы 26, 28 и 30 обеспечивают установление среды обработки данных для выполнения команд загрузки в сопроцессор и вычисления суммы абсолютных разностей. Во многих ситуациях нужно осуществить это установление один раз, а потом остается лишь протестировать большое количество эталонных блоков 4 на соответствие конкретному текущему блоку 2. При этих обстоятельствах необходимость выдачи дополнительных служебных данных во время обработки, связанная с этапами 26, 28 и 30, относительно уменьшается.

Этап 32 представляет собой выполнение восьми команд USALD загрузки в сопроцессор, рассмотренных выше. Каждая из этих команд соответственно обеспечивает вычисление суммы абсолютных значений для некоторого ряда в пределах текущего блока 2 и эталонного блока 4, а также обновление накапливаемого значения в накапливающем регистре 22.

На этапе 34 можно осуществить выборку значения вычисленной суммы абсолютных разностей для всего эталонного блока 4 из накапливающего регистра 22 в основной процессор 8 по команде перемещения данных из регистра сопроцессора в регистр основного процессора. Это накопленное значение затем можно сравнить с предыдущими накопленными значениями или другими параметрами для идентификации наилучшего согласования изображения или для других целей.

На фиг.4 изображены три варианта команды USALD. В первом варианте не используется смещение, а посредством указателя, хранящегося в регистре Rn, просто указывается адрес, и при этом сама команда выполняется в зависимости от условных кодов, обозначаемых ниже символом {cond}. Во втором варианте используется указатель адреса, представленный в виде десятиразрядного значения смещения, которое можно либо прибавлять к начальному значению, либо вычитать из начального значения перед использованием этого значения или после такого использования, в зависимости от флага, обозначаемого ниже символом {!}. В третьем варианте опять используется значение смещения, которое применяется к значению указателя, находящемуся в регистре Rn, перед его использованием, причем значение указателя не изменяется.

Дополнительное и более конкретное описание возможного конкретного варианта осуществления можно найти в нижеследующем тексте.

1.1. ТЕРМИНЫ И ОПРЕДЕЛЕНИЯ

В данном документе употребляются термины и определения, указанные ниже.

| ТЕРМИН | СМЫСЛ ТЕРМИНА |

| ASIC | Интегральная схема прикладной ориентации (называемая также специализированной интегральной схемой), ИСПО (СИС) |

| BIST | Встроенное самотестирование, ВстС |

| JTAG | Объединенная группа по автоматизации тестирования, ОГАТ |

ОБЪЕМ ИЗЛОЖЕНИЯ

Данный документ охватывает особенности инженерной проработки конструкции применительно к сопроцессору для процессора ARM9X6 и предназначенные для улучшения работы в приложениях, связанных с кодированием в соответствии со стандартом MPEG. Документ охватывает функциональные технические характеристики в контексте как аппаратного, так и программного обеспечения. Этот документ не включает в себя подробности реализации ни аппаратного, ни программного обеспечения.

ВВЕДЕНИЕ

Сопроцессор модели Urchin (далее сокращенно именуемый UCP) представляет собой сопроцессор для процессора ARM9X6, предназначенный для ускорения выполнения операций вычисления суммы абсолютных разностей (далее сокращенно именуемых операциями SAD (ВСАР)). Операция SAD используется при реализации алгоритмов оценки движения в соответствии со стандартом MPEG при сравнении блока размером 8×8 из эталонного кадра с блоком размером 8×8 в текущем кадре. Этот алгоритм является частью приложения, обуславливающего кодирование видеоинформации в соответствии со стандартом MPEG4 (стандарт сжатия движущегося изображения и звука, предназначенный для передачи данных с низкой скоростью, например, по телефонным линиям).

1.2. СТРУКТУРА UCP

UCP интерпретирует набор команд для сопроцессора, которые представляют собой часть набора команд процессора ARM. Команды для сопроцессора, работающего совместно с процессором ARM, позволяют процессору ARM:

осуществлять передачу данных между UCP и памятью (с использованием команд загрузки в сопроцессор (далее сокращенно именуемых LDC) и команд хранения в сопроцессоре (далее сокращенно именуемых STC));

осуществлять передачу данных между регистрами UCP и процессора ARM (с использованием команд перемещения данных в сопроцессор (далее сокращенно именуемых MCR) и команд перемещения данных в процессор ARM (далее сокращенно именуемых MRC)).

Процессор ARM действует как блок генератора адреса и перекачивания данных для UCP.

UCP состоит из блока регистров и логического блока обеспечения канала данных и управления. Это показано на фиг.5, где изображена общая блок-схема UCP.

1.3. ИНТЕРФЕЙС СОПРОЦЕССОРА

Единственное соединение процессора ARM с UCP осуществляется через интерфейс сопроцессора. Все остальные системные соединения (такие, как AMBA или прерывания) поддерживаются через посредство процессора ARM.

1.4. КОНСТРУКТИВНЫЕ ОГРАНИЧЕНИЯ

С самого начала реализация UCP представляет собой целенаправленное решение, предназначавшееся для создания библиотеки с технологией 0,18um. Это позволит объединить UCP с процессором ARM926. UCP будет лишь сопроцессором в этой системе. Главным ограничением, накладываемым на конструкцию, являются жесткие требования временного масштаба, и на этом ограничении основаны все конструкторские решения.

Другими важными конструктивными ограничениями являются: число логических элементов, максимальная рабочая частота (в наихудшем случае) и энергопотребление.

1.4.1. КОЛИЧЕСТВО ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Этот параграф изъят из данного описания, поскольку не имеет отношения к этой заявке на патент.

1.4.2. РАБОЧАЯ ЧАСТОТА

Этот параграф изъят из данного описания, поскольку не имеет отношения к этой заявке на патент.

1.4.3. ЭНЕРГОПОТРЕБЛЕНИЕ

Этот параграф изъят из данного описания, поскольку не имеет отношения к этой заявке на патент.

МОДЕЛЬ ПРОГРАММАТОРА

1.5. РЕГИСТРЫ

Сопроцессор UCP содержит два типа памяти для хранения данных:

регистры: они используются для обмена данными непосредственно между регистрами процессора ARM и сопроцессором; доступ в эти регистры можно получить посредством операций MCR и MRC;

буфер блока: это память с восемью строками по восемь байт (шестьдесят четыре бита), в которую можно лишь осуществлять загрузку или непосредственное сохранение из областей расширенной памяти (т.е. не из регистров процессора ARM). Доступ в буфер блока получают с помощью набора специальных команд для UCP (процессор ARM рассматривает соответствующие им операции как операции LDC и STC).

Ниже приведено краткое описание регистров, находящихся в UCP.

| Название регистра | Значение возврата | Номер регистра | Описание |

| CR_ACC(НАК_РС) | 0 | 7 | Хранит накопленные результаты операций ВСАР (SA) |

| CR_IDX(ИНД_РС) | 0 | 4 | Хранит индекс строки для буфера блока |

| CR_BYO(СМБ_РСО) | 0 | 2 | Хранит смещение в байтах, используемое для загрузки блока из эталонного кадра |

| CR_CFG(КОНФ_РС) | 0 | 1 | Хранит конфигурацию UCP |

| CR_ID(ИД_РС) | * | 0 | Это регистр идентификатора (ИД) UCP (* значение возврата равно значению ИД) |

Зарезервированные или неопределенные разряды регистров должны быть замаскированы при операциях считывания из регистров и иметь нулевые значения при операциях записи в регистры. Исключениями из этого правила являются регистры CR_ACC и CR_BYO. Эти регистры всегда будут возвращаться к нулевому значению при операциях считывания из неиспользуемых разрядов, а операции записи в эти регистры можно осуществлять, задавая любое значение для неиспользуемых двоичных разрядов (УСП будет игнорировать эти значения).

1.5.1. CR_ACC

Это 14-разрядный регистр считывания/записи. Его содержимое можно обновлять прямым путем - с помощью операций MCR, а также косвенным путем - с помощью операций SAD.

1.5.2. CR_IDX

Это трехразрядный регистр считывания/записи. Его содержимое можно обновлять прямым путем - с помощью операций MCR, а также косвенным путем - с помощью операций загрузки/считывания буфера блока с осуществлением приращения индекса строки.

Этот регистр указывает индекс строки в буфере блока. Такой индекс обозначает строку, к которой будет произведено обращение во время следующей операции, во время которой осуществляется доступ в буфер блока (при этих операциях всегда используется лишь одна строка из буфера блока).

Когда значение в регистре при приращении превышает значение 7, оно устанавливается в 0.

1.5.3. CR_BYO

Это двухразрядный регистр считывания/записи. Его содержимое можно обновлять с помощью операций MCR.

UCP поддерживает доступы к эталонному кадру из адресов с побайтным выравниванием. В этом регистре хранятся младшие два разряда шины адреса для таких загрузок.

Отметим, что сопроцессор не имеет возможности "непосредственно рассмотреть" значение адреса, используемое процессором ARM для осуществления доступов в память, и именно по этой причине программное обеспечение должно программно вводить смещение в байтах в регистр CR_BYO отдельно. Процессор ARM также не осуществляет непосредственную поддержку никаких пословно выровненных загрузок для сопроцессора, так что UCP приходится осуществлять три загрузки слов, а потом выделять из них восьмибайтные, если это необходимо.

1.5.4. CR_CFG

Это одноразрядный регистр считывания/записи. Его содержимое можно обновлять с помощью операций MCR.

Разряд IDX_INC (ПРИР_ИНД) обеспечивает контроль, чтобы выявить, получает ли регистр CR_IND (ИНД_РС) приращение, после операции загрузки/запоминания в буфер блока или операции SAD. Если бит установлен в "0", приращения нет. После его задания разряд IDX_INC получает приращение по завершении операции с буфером блока или операции SAD.

1.5.5. CR_ID

Этот четырнадцатиразрядный регистр только для считывания содержит код архитектуры UCP и версии.

| 31 | 14 | 13 | 8 | 7 | 4 | 3 | 0 |

| Зарезервированные | Архитектура | 0×F | Обновление |

Разряды [3:0] содержат номер версии для реализации.

Разряды [7:4] содержат значение 0xF для ARM-ориентированных реализаций.

Разряды [13:8] содержат версию архитектуры UCP, причем код 0х00 соответствует Версии 1.

1.6. НАБОР КОМАНД

Синтаксис ассемблера сопроцессора UCP использует тот же формат, что и синтаксис ассемблера процессора ARM.

Символ {} обозначает необязательное поле.

Символ поля cond обозначает код состояния команды процессора ARM.

dest обозначает код назначения UCP.

Rn обозначает регистр процессора ARM.

CRn обозначает регистр UCP.

! указывает, что вычисленный адрес должен быть записан в базовый регистр

Символ UCP обозначает номер сопроцессора семейства UCP.

10_bit_offset (смещение_10_разрядов) - это выражение, оценивающее смещение на десятиразрядное слово. Это смещение добавляют в базовый регистр для образования адреса загрузки. Отметим, что такое смещение должно быть кратным числу 4.

6_bit_offset (смещение_6_разрядов) - это выражение, оценивающее смещение на шестиразрядное слово. Это смещение добавляют в базовый регистр для образования адреса загрузки. Отметим, что такое смещение должно быть кратным числу 4.

Примечание. Допускается пост-индексация с обратной записью или без нее.

На нижеследующих страницах приводится описание набора команд UCP.

1.6.1. СВОДКА НАБОРА КОМАНД

| Команда UCP | Описание |

| UMCR(ПДРПвРС) | Перемещение данных из регистра процессора ARM в регистр сопроцессора (UCP) |

| UMRC(ПДРСвРП) | Перемещение данных из регистра сопроцессора (UCP) в регистр процессора ARM |

| UBBLD(ЗДСиПвББ) | Загрузка двух слов из памяти в буфер блока |

| UBBST(СДСиББвП) | Сохранение двух слов из буфера блока в памяти |

| USALD(ВЗсВСАРиНАК) | Выполнение загрузки с побайтным выравниванием восьми байтов из памяти, выполнение SAD и накопление в CR_ACC |

1.6.2. КОДИРОВАНИЕ КОМАНД

| Команда UCP | Код в сопроцессоре семейства UCP |

| UMCR | MCR |

| UMRC | MRC |

| UBBLD | LDC (множественная загрузка) |

| UBBST | STC (множественная загрузка) |

| USALD | LDC (множественная загрузка) |

cond: код состояния.

UCP: номер сопроцессора семейства UCP.

Rn: регистр процессора ARM, являющийся источником данных.

Rd: регистра процессора ARM, являющийся местом назначения информации.

CRd: регистр UCP, являющийся местом назначения информации.

8_bit_offset: восьмиразрядное число (0-256), используемое для указания смещения адреса.

P: бит индексации добавления смещения: =0 при добавлении смещения после передачи; =1 при добавлении смещения перед передачей.

U: бит направления отсчета: =0 при вычитании смещения из данных из базового регистра; =1 при прибавлении смещения к содержимому базового регистра.

W: бит обратной записи: =0 при отсутствии обратной записи в базовый регистр; =1 при проведении обратной записи в базовый регистр.

Примечание. Действительными для UCP являются только вышеупомянутые коды операций. Любые изменения этих кодов операцию (сохраняющие номер UCP в битах с 11 по 8) приведут к непредсказуемым последствиям.

1.6.3. UMCR

Команду UMCR используют для записи в регистры UCP. UMCR обеспечивает перемещение данных из регистра Rn процессора ARM в регистр CRd UCP.

ДЕЙСТВИЕ

1. Перемещение данных из регистра Rn процессора ARM в регистр CRd UCP.

МНЕМОНИКА

UMCR CRd, Rn, {cond}

ПРИМЕРЫ

UMCR CR_ID, R0; загрузка содержимого R0 в CR_ID.

1.6.4. UMRC

Команду UMRC используют для считывания из регистров UCP. UMRC обеспечивает перемещение данных из регистра CRn UCP в регистр Rd процессора ARM.

ДЕЙСТВИЕ

1. Перемещение данных из регистра CRn UCP в регистр Rd процессора ARM.

МНЕМОНИКА

UMRC Rd, CRn, {cond}

ПРИМЕРЫ

UMRC R6, CR_ID; загрузка содержимого регистра CR_ID в R6.

1.6.5. UBBLD

Команду UBBLD используют для загрузки данных в буфер блока.

ДЕЙСТВИЯ

1. Загрузка слова в буфер блока (CR_IDX, 0).

2. Загрузка слова в буфер блока (CR_IDX, 1).

3. Проверка условия (CR_IDX==1).

4. Приращение ++CR_IDX.

МНЕМОНИКА

UBBLD [Rn], #0, {cond}

UBBLD [Rn, #±10_bit_offset]{!), {cond}

UBBLD [Rn, #±10_bit_offset]{!), {cond}

ПРИМЕРЫ

UBBLD [R0], #320!; загрузка двух слов в буфер блока из памяти (R0) и последующее приращение содержимого (R0) для перехода к следующей строке.

1.6.6. UBBST

Команду UBBST используют для сохранения данных из буфера блока. Эта операция предназначена только для целей идентификации и не должна использоваться в наборе прикладных команд.

ДЕЙСТВИЯ

1. Сохранение слова