Выходной каскад усилителя мощности

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в устройствах усиления широкополосных и импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения, стабилизаторах напряжения при малых напряжениях питания. Технический результат заключается в повышении максимального выходного напряжения примерно на 0,7 В. Выходной каскад содержит основной вход (1), связанный с базой входного транзистора (Т) (3), эмиттер которого соединен по переменному току с шиной источника питания (ИП) (4), а коллектор подключен к базе первого выходного Т (5), второй выходной Т (6), проводимость которого совпадает с проводимостью входного Т (3) и противоположна проводимости первого выходного Т (5), причем коллектор второго выходного Т (6) соединен с эмиттером первого выходного Т (5) и основным выходом (2), а эмиттер соединен по переменному току с шиной ИП (4). Указанный результат достигается тем, что коллектор первого выходного Т (6) соединен с шиной ИП (4), а основной вход (1) связан с базой второго выходного Т (6). 2 з.п. ф-лы, 16 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов в радиотехнических системах с низковольтным питанием (Еп=1,2÷1,5 В).

Известны выходные каскады усилителей мощности с малым выходным сопротивлением (5-50 Ом), выполненные на n-р-n и р-n-р транзисторах, которые стали основой построения буферных усилителей (в том числе двухтактных) различных аналоговых и аналого-цифровых устройств [Патент США №5467058, H 03 f 3/26, патент США №3938053, H 03 f 3/187, патент США №5444419, H 03 f 3/30, патент США №4454479, H 03 f 3/18, патент США №3944944, H 03 f 1/26, патент США №4334197, H 03 f 3/30, патент США №4935704, H 03 f 3/26, патент США №4916408, H 03 f 3/45, патент США №6166603, H 03 f 3/18, патент США №5786731, H 03 f 3/30, Грэбен А. Б. Проектирование аналоговых интегральных схем. М.: Мир, стр.247 (рис.1, 13), стр.131 (рис.6, 7), Авт. свид. СССР №650211, H 03 f 3/26]. Однако в устройствах с низковольтным питанием они не эффективны. Проблема получения максимальной амплитуды выходного напряжения выходных каскадов усилителей мощности, близкой к напряжению питания, является одной из актуальных проблем современной аналоговой микросхемотехники. В значительной степени она проявляется при напряжениях питания Еп=1,2÷1,5 В.

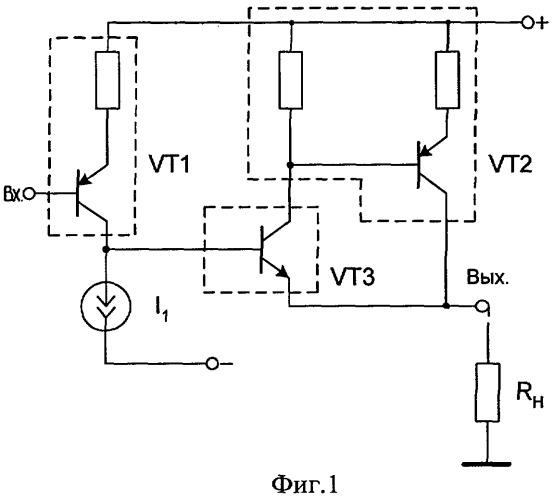

Ближайшим прототипом заявляемого устройства является выходной каскад усилителя мощности фиг.1 [Патент США №3944944, H 03 f 1/26, Грэбен А.Б. Проектирование аналоговых интегральных схем. М.: Мир, стр.247 (рис.1, 13), стр.131 (рис.6, 7)], содержащий основной вход и основной выход, входной р-n-р транзистор, эмиттер которого соединен по переменному току с шиной источника питания, а коллектор подключен к базе первого выходного n-р-n транзистора, причем основной вход связан с базой входного транзистора, второй выходной транзистор, приводимость которого совпадает с проводимостью входного транзистора и противоположна проводимости первого выходного транзистора, причем коллектор второго выходного транзистора соединен с эмиттером первого выходного транзистора и основным выходом, а эмиттер соединен по переменному току с шиной питания. Коллектор первого выходного транзистора подключен к базе второго выходного транзистора.

В соответствии с [Грэбен А.Б. Проектирование аналоговых интегральных схем. М.: Мир, стр.247, (рис.6, 7), стр.131] схема фиг.1 относится к числу трех базовых схем выходных каскадов современных усилителей мощности. Она является основой построения различных двухтактных усилителей, которые представляют собой формальное соединение двух симметричных подсхем фиг.1 при их реализации на транзисторах противоположного типа проводимости.

Существенный недостаток известного устройства состоит в том, что его архитектура не позволяет получить (при сохранении малых величин выходного сопротивления) максимальное значение выходного напряжения, незначительно (на 10÷100 мВ) отличающееся от напряжения питания - Еп.

Основная цель предлагаемого изобретения состоит в повышении максимальной амплитуды выходного напряжения (увеличении коэффициента использования напряжения питания) при сохранении малых значений выходного сопротивления.

Поставленная цель достигается тем, что в выходной каскад усилителя мощности, содержащий основной вход и основной выход, входной транзистор, эмиттер которого соединен по переменному току с шиной источника питания, а коллектор подключен к базе первого выходного транзистора, причем основной вход связан с базой входного транзистора, второй выходной транзистор, приводимость которого совпадает с проводимостью входного транзистора и противоположна проводимости первого выходного транзистора, причем коллектор второго выходного транзистора соединен с эмиттером первого выходного транзистора и основным выходом, а эмиттер соединен по переменному току с шиной питания, вводятся новые связи и элементы - коллектор первого выходного транзистора соединен с шиной источника питания, а основной вход связан с базой второго выходного транзистора.

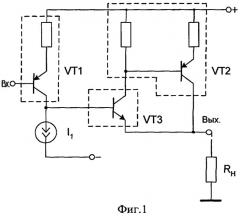

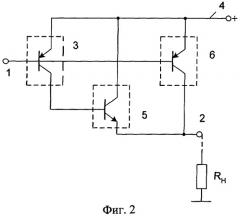

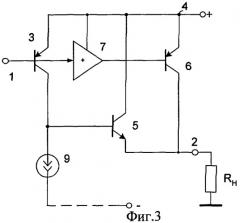

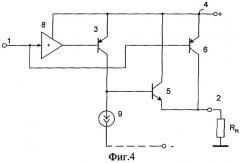

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2. На фиг.3 и 4 изображена схема заявляемого выходного каскада усилителя мощности, в котором в соответствии с п.2, п.3 формулы изобретения вводятся согласующие неинвертирующие усилители тока, обеспечивающие выравнивание коэффициентов передачи по току при разных уровнях выходного сигнала.

На фиг.5 приведена схема заявляемого устройства, в котором раскрыта схемотехника неинвертирующих согласующих усилителей тока, соответствующая п.2 и п.3 формулы изобретения.

На фиг.6-10 показаны частные случаи применения заявляемого выходного каскада в структурах различных усилителей. На фиг.11 и 12 приведены схемы исследованных операционных усилителей с заявляемым (фиг.11) и известным (фиг.12) выходными каскадами.

На фиг.13 показана зависимость выходного напряжения (Uout.1) в замкнутом ОУ с заявляемым выходным каскадом (Фиг.11) и выходного напряжения (Uout.2) в ОУ с выходным каскадом-прототипом (Фиг.12). Кроме этого, на фиг.13 приведен график зависимости эмиттерного тока выходного транзистора 5 (Iэ.VT3) от Uвх, который выключается при определенном уровне Uout.1.

На фиг.14 показана исследованная авторами схема интегрального ОУ с заявленным выходным каскадом, образующим двухтактную структуру буферного каскада ОУ.

На фиг.15 приведены результаты компьютерного моделирования заявляемого выходного каскада в структуре операционного усилителя фиг.14 с использованием моделей транзисторов ГУН НПП "Пульсар".

Фиг.16 иллюстрирует применение заявленного устройства в аналоговых устройствах других классов - в схеме компенсационного стабилизатора напряжения, который работает в более широком диапазоне входных напряжений.

Двухтактный выходной каскад усилителя мощности фиг.2 содержит основной вход 1 и основной выход 2, входной транзистор 3, эмиттер которого соединен по переменному току с шиной источника питания 4, а коллектор подключен к базе первого выходного транзистора 5, причем основной вход 1 связан с базой входного транзистора 3, второй выходной транзистор 6, приводимость которого совпадает с проводимостью входного транзистора 3 и противоположна проводимости первого выходного транзистора 5, причем коллектор второго выходного транзистора 6 соединен с эмиттером первого выходного транзистора 5 и основным выходом 2, а эмиттер соединен по переменному току с шиной источника питания 4. Коллектор первого выходного транзистора 5 соединен по переменному току с шиной источника питания 4, а основной вход 1 связан с базой второго выходного транзистора 6.

В устройстве по п.2 формулы изобретения (фиг.4) основной вход 1 связан с базой второго выходного транзистора 6 через первый согласующий неинвертирующий усилитель тока 7.

В устройстве по п.3 формулы изобретения (фиг.3) основной вход 1 связан с базой входного транзистора 3 через второй согласующий неинвертирующий усилитель тока 8. В частных случаях к коллектору транзистора 3 может подключаться источник опорного тока 9 (фиг.3, фиг.4).

В схеме фиг.5, которая объединяет частные варианты построения заявляемого устройства (фиг.3 и фиг.4), согласующие усилители тока 7 и 8 включают элементы 7* и 7**, 8* и 8**.

Основой построения двухтактных усилителей фиг.6 и фиг.7 являются соответственно базовые схемы фиг.4 и 3.

Схема фиг.8 соответствует функциональным схемам фиг.6 и фиг.7. Схема фиг.9 иллюстрирует частные варианты построения согласующих усилителей 7 и 8 и также соответствует функциональным схемам усилителей фиг.6 и 7.

На фиг.10 показан фрагмент схемы широкополосного усилителя на базе архитектуры фиг.7.

Для исследования свойств заявляемого устройства было выполнено компьютерное моделирование ОУ фиг.11 с выходным каскадом фиг.2 в среде PSpice с использованием моделей интегральных транзисторов ГУП НПП "Пульсар" (г.Москва). Для сравнения был также исследован ОУ (фиг.12) с выходным каскадом - прототипом.

На фиг.13 показаны графические зависимости выходного напряжения от входного двух неинвертирующих ОУ фиг.11 и 12 при коэффициенте передачи в схеме с обратной связью Кп=2, а также график эмиттерного тока выходного транзистора 5, характеризующий режимы его работы в заявляемой схеме (фиг.2) выходного каскада.

Рассмотрим работу заявляемого устройства на примере анализа схемы фиг.2 с привлечением для пояснений графиков фиг.13.

Устройство фиг.2 характеризуется нелинейным переключением каналов передачи входного сигнала в зависимости от амплитуды выходного напряжения и степени его отличия от напряжения питания Еп. При этом точкой переключения каналов является выходная координата Uвых≈Еп-0,7 В.

При малых выходных сигналах выходной транзистор 5 функционирует в активном режиме класса "А", передает приращения тока коллектора входного транзистора 3 в нагрузку Rн, обеспечивая достаточно низкое выходное сопротивление. Основное усиление по току создают транзисторы 3 и 5, а транзистор 6 незначительно влияет на работу схемы, т.к. имеет высокоомный выход.

При увеличении под действием входного сигнала (Uвх) тока коллектора транзистора 3 потенциал на базе транзистора 5 возрастает, и, как следствие, напряжение на выходе 2 увеличивается.

При напряжении на выходе 2 Uвых, равном Еп - 0,7 В, работа схемы существенно изменяется - транзистор 6 запирает транзистор 5 по цепи эмиттера (график Ie.VT3, фиг.13), обеспечивая этим режимом переключения дальнейшее увеличение выходного напряжения (Uout.1, фиг.13). При этом максимальное значение Uвых (в отличие от Uout.2 схемы прототипа фиг.12) получается близким к Еп.

Применение устройства фиг.2 наиболее эффективно в схемах с низковольтным питанием (Еп=1,2-1,5 В). Так, из фиг.13 следует, что в заявляемом устройстве при Еп=1,5 В выходное напряжение Uвых.max=1,41 B, а в схеме-прототипе Uвых.max=0,72 В.

В качестве согласующих усилителей тока 7 и 8 авторы рекомендуют использовать простейшие эмиттерные повторители. Таким образом, в зависимости от вариантов построения согласующих усилителей тока возможно изменение состава функциональных узлов заявляемого устройства и связей между ними, что нашло отражение в многозвенной формуле заявки на изобретение.

На основе заявляемого выходного каскада возможно построение более 30 вариантов построения двухтактных усилителей мощности, которые по совокупности свойств и обобщенным параметрам не имеют аналогов.

Таким образом, результаты компьютерного моделирования в среде PSpice показывают, что заявляемое устройство имеет при (Еп=1,5В) более высокие (в 2 раза) значения максимальной амплитуды выходного напряжения.

1. Выходной каскад усилителя мощности, содержащий основной вход и основной выход, входной транзистор, эмиттер которого соединен по переменному току с шиной источника питания, а коллектор подключен к базе первого выходного транзистора, причем основной вход связан с базой входного транзистора, второй выходной транзистор, проводимость которого совпадает с проводимостью входного транзистора и противоположна проводимости первого выходного транзистора, причем коллектор второго выходного транзистора соединен с эмиттером первого выходного транзистора и основным выходом, а эмиттер соединен по переменному току с шиной источника питания, отличающийся тем, что коллектор первого выходного транзистора соединен с шиной источника питания, а основной вход связан с базой второго выходного транзистора.

2. Устройство по п.1, отличающееся тем, что основной вход связан с базой второго выходного транзистора через первый согласующий неинвертирующий усилитель тока.

3. Устройство по п.1, отличающееся тем, что основной вход связан с базой входного транзистора через второй согласующий неинвертирующий усилитель тока.