Аналого-цифровой преобразователь

Иллюстрации

Показать всеИзобретение относится к области электротехники, а именно к устройствам преобразования аналоговых сигналов в цифровой код. Техническим результатом является повышение точности преобразования. Устройство содержит интегратор на усилителе постоянного тока, источник образцового напряжения, коммутатор, генератор, пороговое устройство, блок управления, триггер, инверторы, элементы 2И-НЕ, реверсивный счетчик, регистр, процессор. 4 ил.

Реферат

Изобретение относится к области электротехники, а именно к устройствам преобразования аналоговых сигналов в цифровой код.

Известен аналого-цифровой преобразователь [1], содержащий схему сравнения, подключенную к генератору, датчик преобразуемого напряжения, блок управления, соединенный с генератором импульсов, счетчик.

Наиболее близким по технической сущности является аналого-цифровой преобразователь, содержащий интегратор на усилителе постоянного тока, пороговое устройство, коммутатор, источник образцового напряжения с выходами положительного и отрицательного потенциалов, генератор с первым выходом первой тактовой частоты, блок управления, первый триггер, счетчик, причем вход аналого-цифрового преобразователя и выход коммутатора подключены к входу усилителя постоянного тока, выход которого подключен к первому входу порогового устройства, выход порогового устройства соединен с первым входом триггера, инверсный выход которого подключен к управляющему входу коммутатора, выходы положительного и отрицательного потенциалов источника образцового напряжения подключены к входам коммутатора, первый выход блока управления подключен к входу обнуления счетчика.

Недостатком такого аналого-цифрового преобразователя является погрешность преобразования аналогового сигнала в цифровой код вследствие потери информации при преобразовании.

Техническим результатом изобретения является повышение точности преобразования аналогового сигнала в цифровой код.

Данный результат достигается в аналого-цифровом преобразователе, содержащем интегратор на усилителе постоянного тока, пороговое устройство, коммутатор, источник образцового напряжения с выходами положительного и отрицательного потенциалов, генератор с первым выходом первой тактовой частоты, блок управления, первый триггер, счетчик, причем вход аналого-цифрового преобразователя и выход коммутатора подключены к входу усилителя постоянного тока, выход которого подключен к первому входу порогового устройства, выход порогового устройства соединен с первым входом триггера, инверсный выход которого подключен к управляющему входу коммутатора, выходы положительного и отрицательного потенциалов источника образцового напряжения подключены к входам коммутатора, первый выход блока управления подключен к входу обнуления счетчика, тем, что введены первый и второй инверторы, первое и второе логические устройства 2И-НЕ, регистр, процессор, в качестве счетчика применен реверсивный счетчик, генератор дополнительно имеет второй выход второй тактовой частоты, по крайней мере, в два раза меньшей первой тактовой частоты, третий выход третьей тактовой частоты, по крайней мере, на два порядка меньшей первой тактовой частоты, четвертый выход с напряжением пилообразной формы, частота которого больше третьей тактовой частоты, но меньше второй тактовой частоты по крайней мере на порядок, к второму входу порогового устройства подключен четвертый выход генератора, второй выход генератора подключен к тактовому входу первого триггера и к входу первого инвертора, выход которого подключен к первым входам первого и второго логических устройств 2И-НЕ, к инверсному выходу первого триггера подключены второй вход второго логического устройства 2И-НЕ и вход второго инвертора, к выходу которого подключен второй вход первого логического устройства 2И-НЕ, выход первого логического устройства 2И-НЕ подключен к первому входу блока управления, к второму входу которого подключен выход второго логического устройства 2И-НЕ, к третьему входу блока управления подключен первый выход генератора, третий выход которого подключен к четвертому входу блока управления, второй выход блока управления подключен к суммирующему входу реверсивного счетчика, к вычитающему входу которого подключен третий выход блока управления, четвертый выход блока управления подключен к входу разрешения записи регистра, выход реверсивного счетчика соединен многопроводной линией с входом данных регистра, выход которого соединен многопроводной линией с входом процессора, выход процессора подключен к входу разрешения чтения регистра, блок управления выполнен на третьем, четвертом, пятом, шестом, седьмом, восьмом, девятом и десятом инверторах, втором, третьем, четвертом, пятом, шестом, седьмом и восьмом триггерах, третьем, четвертом и пятом логических устройствах 2И-НЕ, логическом устройстве И, триггеры с первого по восьмой по счету выполнены как D-триггеры, вход третьего инвертора является первым входом блока управления, вход четвертого инвертора является вторым входом блока управления, к выходу третьего инвертора подсоединен вход D второго триггера, с входом С второго триггера, являющимся третьим входом блока управления, соединены входы С третьего и восьмого триггеров, а также вход пятого инвертора, вход С четвертого триггера является четвертым входом блока управления, к входам логического устройства И подключены выход четвертого триггера и инверсные выходы второго и третьего триггеров, к входам С пятого, шестого и седьмого триггеров подключен выход пятого инвертора, прямой выход второго триггера подсоединен к первому входу третьего логического устройства 2И-НЕ и к входу D пятого триггера, инверсный выход которого подключен к второму входу третьего логического устройства 2И-НЕ, прямой выход третьего триггера подсоединен к первому входу четвертого логического устройства 2И-НЕ и к входу D седьмого триггера, инверсный выход которого подключен ко второму входу четвертого логического устройства 2И-НЕ, выход логического устройства И подключен к входу D шестого триггера, выход которого соединен с входом D восьмого триггера и с первым входом пятого логического устройства 2И-НЕ, инверсный выход восьмого триггера подключен к второму входу пятого логического устройства 2И-НЕ, выход которого соединен с входом R четвертого триггера и с входом шестого инвертора, выход шестого инвертора подключен к входу седьмого инвертора, выход которого соединен с входом восьмого инвертора, выход восьмого инвертора соединен с входом девятого инвертора, выход которого подключен к входу десятого инвертора, выход третьего логического устройства 2И-НЕ, являющийся вторым выходом блока управления, предназначен для подключения к суммирующему входу реверсивного счетчика, выход четвертого логического устройства 2И-НЕ, являющийся третьим выходом блока управления, предназначен для подключения к вычитающему входу реверсивного счетчика, выход шестого инвертора, являющийся четвертым выходом блока управления, предназначен для подключения к входу разрешения записи регистра, выход десятого инвертора, являющийся первым выходом блока управления, предназначен для подключения к входу обнуления реверсивного счетчика.

Введение в аналого-цифровой преобразователь первого и второго инверторов, первого и второго логических устройств 2И-НЕ, регистра, процессора, применение в качестве счетчика реверсивного счетчика, выполнение в генераторе второго выхода второй тактовой частоты и третьего выхода третьей тактовой частоты, выполнение блока управления в составе семи D-триггеров, восьми инверторов, трех логических устройств 2И-НЕ, логического устройства И, подключение выхода первого логического устройства 2И-НЕ к первому входу блока управления, подключение выхода второго логического устройства 2И-НЕ к второму входу блока управления, подключение к третьему входу блока управления первого выхода генератора, подключение второго выхода генератора к тактовому входу первого триггера, подключение второго выхода блока управления к суммирующему входу реверсивного счетчика, подключение третьего выхода блока управления к вычитающему входу реверсивного счетчика, соединение четвертого выхода блока управления с входом разрешения записи регистра, соединение выхода реверсивного счетчика с входом данных регистра, соединение выхода регистра с входом процессора, подключение выхода процессора к входу разрешения чтения регистра приводит к повышению точности преобразования аналогового сигнала в цифровой код вследствие достигаемой синхронизации процесса преобразования, устраняющей потерю информации.

Выполнение четвертого выхода генератора с напряжением пилообразной формы, его подключение к второму входу порогового устройства обеспечивает повышение точности преобразования аналогового сигнала в цифровой код, так как повышается точность сравнения преобразуемого и опорного напряжений.

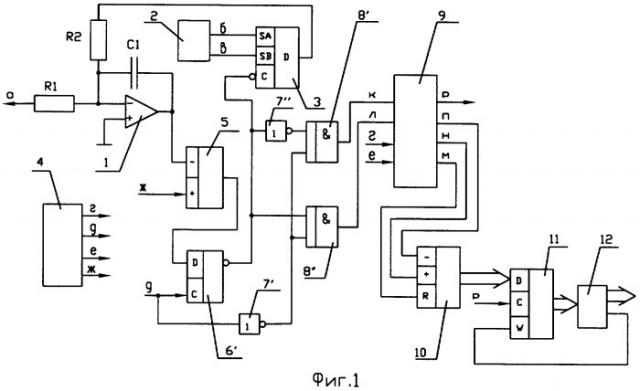

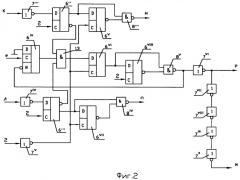

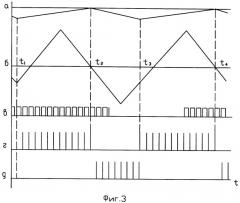

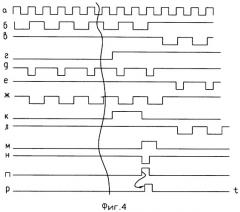

На фиг.1 представлена общая схема аналого-цифрового преобразователя; на фиг.2 - принципиальная электрическая схема блока управления; на фиг.3, 4 - циклограммы сигналов аналого-цифрового преобразователя.

Аналого-цифровой преобразователь (фиг.1) содержит интегратор с конденсатором С1 на усилителе постоянного тока (УПТ) 1, к инверсному входу которого через резистор R1 подсоединен вход "а" аналого-цифрового преобразователя. Выход "б" положительного потенциала и выход "в" отрицательного потенциала источника образцового напряжения 2 подключены к входам коммутатора 3, выход которого через резистор R2 подключен к инверсному входу УПТ 1. В генераторе 4 образованы первый выход "г" первой тактовой частоты f1, второй выход "д" второй тактовой частоты f2, по крайней мере, в два раза меньшей первой тактовой частоты f1, третий выход "е" третьей тактовой частоты f3, по крайней мере, на два порядка меньшей первой тактовой частоты f1, четвертый выход "ж" с напряжением пилообразной формы, частота f4 которого больше третьей тактовой частоты f3, но меньше второй тактовой частоты f2, по крайней мере, на порядок.

Выход УПТ 1 подключен к первому входу порогового устройства 5, к второму входу которого подключен четвертый выход "ж" генератора 4. Выход порогового устройства 5 соединен с тактовым входом D первого триггера 6', к входу С которого, а также к входу первого инвертора 7' подключен второй выход "д" генератора 4. Первый триггер 6' выполнен как D-триггер. Выход первого инвертора 7' подключен к первым входам первого 8' и второго 8'' логических устройств 2И-НЕ. К инверсному выходу первого триггера 6' подключены управляющий вход коммутатора 3, второй вход второго логического устройства 2И-НЕ 8'' и вход второго инвертора 7'', к выходу которого подключен второй вход второго логического устройства 2И-НЕ 8''.

Выход первого логического устройства 2И-НЕ 8' подключен к первому входу "к" блока управления 9, к второму входу "л" которого подключен выход второго логического устройства 2И-НЕ 8''. К третьему входу блока управления 9 подключен первый выход "г" генератора 4, третий выход "е" которого подключен к четвертому входу блока управления 9. Первый выход "м" блока управления 9 соединен с входом R обнуления реверсивного счетчика 10. Второй выход "н" блока управления 9 подключен к суммирующему входу реверсивного счетчика 10, к вычитающему входу которого подключен третий выход "п" блока управления 9. Четвертый выход "р" блока управления 9 соединен с входом разрешения записи регистра 11, вход данных которого соединен, например, шестнадцатипроводной линией с выходом реверсивного счетчика 10.

Выход регистра 11 соединен, например, шестнадцатипроводной линией с входом процессора 12, выход которого подключен к входу разрешения чтения регистра 11.

Блок управления 9 (фиг.2) выполнен на третьем 7''', четвертом 7IV, пятом 7V, шестом 7VI, седьмом 7VII, восьмом 7VIII, девятом 7IX и десятом 7X инверторах, втором 6'', третьем 6''', четвертом 6IV, пятом 6V, шестом 6VI, седьмом 6VII и восьмом 6VIII D-триггерах, третьем 8''', четвертом 8IV и пятом 8V логических устройствах 2И-НЕ, логическом устройстве И 13.

Вход "к" третьего инвертора 7''' является первым входом блока управления 9 и предназначен для подключения к выходу первого логического устройства 2И-НЕ 8'. К выходу третьего инвертора 7''' подсоединен вход D второго триггера 6''. С входом С второго триггера 6, являющимся третьим входом блока управления 9 и предназначенным для подключения к первому выходу "г" генератора 4, соединены входы С третьего 6''' и восьмого 6VIII триггеров, а также вход пятого инвертора 7V. Вход четвертого инвертора 7IV, являющийся вторым входом "л" блока управления 9, предназначен для подключения к выходу второго логического устройства 2И-НЕ 8''. Вход С четвертого триггера 6IV, являющийся четвертым входом блока управления 9, предназначен для подключения к третьему выходу "е" генератора 4. К входам логического устройства И 13 подключены выход четвертого триггера 6IV и инверсные выходы второго 6'' и третьего 6''' триггеров. К входам С пятого 6V, шестого 6VI и седьмого 6VII триггеров подключен выход пятого инвертора 7V. Прямой выход второго триггера 6'' подсоединен к первому входу третьего логического устройства 2И-НЕ 8''' и к входу D пятого триггера 6V, инверсный выход которого подключен к второму входу третьего логического устройства 2И-НЕ 8'''. Прямой выход третьего триггера 6''' подсоединен к первому входу четвертого логического устройства 2И-НЕ 8IV и к входу D седьмого триггера 6VII, инверсный выход которого подключен к второму входу четвертого логического устройства 2И-НЕ 8IV. Выход логического устройства И 13 подключен к входу D шестого триггера 6VI, выход которого соединен с входом D восьмого триггера 6VIII и с первым входом пятого логического устройства 2И-НЕ 8V. Инверсный выход восьмого триггера 6VIII подключен к второму входу пятого логического устройства 2И-НЕ 8V выход которого соединен с входом R четвертого триггера 6IV и с входом шестого инвертора 7VI. Выход шестого инвертора 7VI подключен к входу седьмого инвертора 7VII, выход которого соединен со входом восьмого инвертора 7VIII, выход восьмого инвертора 7VIII соединен с входом девятого инвертора 7IX, выход которого подключен к входу десятого инвертора 7X.

Выход третьего логического устройства 2И-НЕ 8''' является вторым выходом "н" блока управления 9 и предназначен для подключения к суммирующему входу реверсивного счетчика 10. Выход четвертого логического устройства 2И-НЕ 8IV является третьим выходом "п" блока управления 9 и предназначен для подключения к вычитающему входу реверсивного счетчика 10. Выход шестого инвертора 7VI является четвертым выходом "р" блока управления 9 и предназначен для записи регистра 11. Выход десятого инвертора 7X является первым выходом "м" блока управления 9 и предназначен для подключения к входу обнуления реверсивного счетчика 10.

На инверсный вход УПТ 1 поступают протекающий с входа "а" через резистор R1 входной аналоговый ток и протекающий через резистор R2 ток обратной связи с выхода коммутатора 3. При этом напряжения на выходе УПТ 1 (фиг.3, а) плавно изменяется.

При превышении в момент времени t1 напряжения с выхода УПТ 1 значения пилообразного напряжения частотой f4 (фиг.3, б), подаваемого на вход порогового устройства 5 с выхода "ж" генератора 4, сигнал на выходе порогового устройства 5 изменится на противоположный. При этом напряжение на выходе коммутатора 3 изменяется на противоположное. Если, например, к входу коммутатора 3 было подключено напряжение с выхода "в" источника образцового напряжения 2, то станет подключенным напряжение с его выхода "б".

Теперь на вход УПТ 1 подается ток обратной связи противоположной полярности (амплитуда которого больше входного тока), напряжение на выходе УПТ 1 начнет плавно изменяться в другую сторону, оставаясь большим, чем напряжение на входе "ж" порогового устройства 5. Когда в момент времени t2 напряжение на выходе УПТ 1 станет меньшим напряжения на входе "ж" порогового устройства 5, сигнал на выходе порогового устройства 5 изменится на противоположный. При этом на выход коммутатора 3 подключится напряжение с выхода "в", и в интервале времени от t2 до t3 будет повторяться описанный выше процесс.

При наличии на входе "а" аналого-цифрового преобразователя постоянного напряжения интервал времени от момента времени t1 до момента времени t2 не будет равным интервалу времени от момента времени t2 до момента времени t3. При неизменном значении постоянного напряжения на входе "а" процесс переключения порогового устройства 5 будет проходить с периодом, равным интервалу времени от момента времени t1 до момента времени t2. При этом на первый вход "к" блока управления 9 с первого логического устройства 2И-НЕ 8' в интервале от момента времени t1 до момента времени t2 (фиг.3, г) пройдет N1 импульсов частотой f2 (фиг.3, в), поступающей на вход С первого триггера 6' с второго выхода "д" генератора 4. А на второй вход "л" блока управления 9 с выхода второго логического устройства 2И-НЕ 8'' в интервале от момента времени t2 до момента времени t3 пройдет N2 импульсов частотой f2 (фиг.3, д). Поступающими на вход пятого инвертора 7V и входы С второго 6'' и третьего 6''' триггеров блока управления 9 импульсами частотой f1 с первого выхода "г" генератора 4 (фиг.4, а) тактируются приходящие на первый вход "к" блока управления 9 импульсы частотой f2 (фиг.4, б) так, что с второго выхода "н" блока управления 9 на суммирующий вход реверсивного счетчика 10 поступает N1 импульсов частотой f2 и длительностью 1/f1 (фиг.4, д). Поступающие на второй вход "л" импульсы частотой f2 (фиг.4, в) тактируются так, что с третьего выхода "п" на вычитающий вход реверсивного счетчика 10 поступает N2 импульсов частотой f2 и длительностью 1/f1 (фиг.4, е). На первый вход логического устройства И 13 с инверсного выхода второго триггера 6" подаются тактированные частотой f1 импульсы частотой f2 с длительностью 2/f1 (фиг.4, ж), на второй вход логического устройства И 13 с инверсного выхода третьего триггера 6''' подаются тактированные частотой f1 импульсы частотой f2 с длительностью 2/f1 (фиг.4, л). Импульсы частотой f3 на входе С четвертого триггера 6IV (фиг.4, г) с третьего выхода "е" генератора 4 на выходе четвертого триггера 6IV преобразуются в импульсы частотой f3 и длительностью 2/f1 (фиг.4, к), которые поступают на третий вход логического устройства И 13. В результате на выходе шестого триггера 6VI образуются импульсы частотой f3 и длительностью 2/f1 (фиг.4, м), а на выходе пятого логического устройства 2И-НЕ 8 и на входе R четвертого триггера 6IV образуются импульсы частотой f3 и длительностью 1/f1 (фиг.4, н).

В течение времени, которое определяется интервалами между импульсами частотой f3 с выхода шестого инвертора 7VI (фиг.4, п), реверсивный счетчик 10 считает поступающие на его входы с выходов "н", "п" блока управления 9 импульсы частотой f2, и в момент прихода очередного импульса с выхода шестого инвертора 7VI (четвертый выход "р" блока управления 9) содержимое реверсивного счетчика 10 (разность между количеством импульсов N1 и количеством импульсов N2) переписывается в регистр 11. Разность между количеством импульсов N1 и N2 является кодом аналогового сигнала, приходящего на вход "а" аналого-цифрового преобразователя. По приходу на вход обнуления реверсивного счетчика 10 импульса с первого выхода "м" блока управления 9 (фиг.4, р), передний фронт которого отстает от переднего фронта импульса с выхода "р" вследствие запаздывания распространения сигнала между шестым 7VI и десятым 7X инверторами, реверсивный счетчик 10 обнуляется. По получении сигнала с выхода процессора 12 на вход чтения регистра 11 регистр 11 транслирует код аналогового сигнала в процессор 12.

Сравнение на входах порогового устройства 5 двух пилообразных напряжений повышает точность срабатывания порогового устройства 5, в результате чего повышается точность широтно-импульсного преобразования.

Тактирование импульсами более высокой частоты f1 счетных импульсов частотой f2 и времени счета, определяемого частотой f3, позволяет уменьшить количество выпадающих из счета счетных импульсов частотой f2 при преобразовании аналогового сигнала в цифровой код.

Источники информации

1. Авторское свидетельство СССР №476680 кл. Н 03 М 1/62. Преобразователь напряжения в код, 1976 г.

2. Авторское свидетельство СССР №312279 кл. Н 03 М 1/00. Аналого-цифровой преобразователь, 1972 г.

Аналого-цифровой преобразователь, содержащий интегратор на усилителе постоянного тока, пороговое устройство, коммутатор, источник образцового напряжения с выходами положительного и отрицательного потенциалов, генератор с первым выходом первой тактовой частоты, блок управления, первый триггер, счетчик, вход аналого-цифрового преобразователя и выход коммутатора подключены к входу усилителя постоянного тока, выход которого подключен к первому входу порогового устройства, выход порогового устройства соединен с первым входом триггера, инверсный выход которого подключен к управляющему входу коммутатора, выходы положительного и отрицательного потенциалов источника образцового напряжения подключены к входам коммутатора, первый выход блока управления подключен к входу управления счетчика, отличающийся тем, что введены первый и второй инверторы, первое и второе логические устройства 2И-НЕ, регистр, процессор, в качестве счетчика применен реверсивный счетчик, генератор дополнительно имеет второй выход второй тактовой частоты, по крайней мере, в два раза меньшей первой тактовой частоты, третий выход третьей тактовой частоты, по крайней мере, на два порядка меньшей первой тактовой частоты, четвертый выход с напряжением пилообразной формы, частота которого больше третьей тактовой частоты, но меньше второй тактовой частоты, по крайней мере, на порядок, к второму выходу порогового устройства подключен четвертый выход генератора, второй выход генератора подключен к тактовому входу первого триггера и к входу первого инвертора, выход которого подключен к первым входам первого и второго логических устройств 2И-НЕ, к инверсному выходу первого триггера подключены второй вход второго логического устройства 2И-НЕ и вход второго инвертора, к выходу которого подключен второй вход первого логического устройства 2И-НЕ, выход первого логического устройства 2И-НЕ подключен к первому входу блока управления, к второму входу которого подключен выход второго логического устройства 2И-НЕ, к третьему входу блока управления подключен первый выход генератора, третий выход которого подключен к четвертому входу блока управления, второй выход блока управления подключен к суммирующему входу реверсивного счетчика, к вычитающему входу которого подключен третий выход блока управления, четвертый выход блока управления подключен к входу разрешения записи регистра, выход реверсивного счетчика соединен многопроводной линией с входом данных регистра, выход которого соединен многопроводной линией с входом процессора, выход процессора подключен к входу разрешения чтения регистра, блок управления выполнен на третьем, четвертом, пятом, шестом, седьмом, восьмом, девятом и десятом инверторах, втором, третьем, четвертом, пятом, шестом, седьмом, восьмом триггерах, третьем, четвертом, пятом логических устройствах 2И-НЕ, логическом устройстве И, триггеры с первого по восьмой по счету выполнены как D-триггеры, вход третьего инвертора является первым входом блока управления, вход четвертого инвертора является вторым входом блока управления, к выходу третьего инвертора подсоединен вход D второго триггера, с входом С второго триггера, являющимся третьим входом блока управления, соединены входы С третьего и восьмого триггеров, а также вход пятого инвертора, вход С четвертого триггера является четвертым входом управления, к входам логического устройства И подключены выход четвертого триггера и инверсные выходы второго и третьего триггеров, к входам С пятого, шестого и седьмого триггеров подключен выход пятого инвертора, прямой выход второго триггера подсоединен к первому входу третьего логического устройства 2И-НЕ и к входу D пятого триггера, инверсный выход которого подключен к второму входу третьего логического устройства 2И-НЕ, прямой выход третьего триггера подсоединен к первому входу четвертого логического устройства 2И-НЕ и к входу D седьмого триггера, инверсный выход которого подключен ко второму входу четвертого логического устройства 2И-НЕ, выход логического устройства И подключен к входу D шестого триггера, выход которого соединен с входом D восьмого триггера и с первым входом пятого логического устройства 2И-НЕ, инверсный выход восьмого триггера подключен ко второму входу пятого логического устройства 2И-НЕ, выход которого соединен с входом R четвертого триггера и с входом шестого инвертора, выход шестого инвертора подключен к входу седьмого инвертора, выход которого соединен с входом восьмого инвертора, выход восьмого инвертора соединен с входом девятого инвертора, выход которого подключен к входу десятого инвертора, выход третьего логического устройства 2И-НЕ, являющийся вторым выходом блока управления, предназначен для подключения к суммирующему входу реверсивного счетчика, выход четвертого логического устройства, являющийся третьим выходом блока управления, предназначен для подключения к вычитающему входу реверсивного счетчика, выход шестого инвертора, являющийся четвертым выходом блока управления, предназначен для подключения к входу разрешения записи регистра, выход десятого инвертора, являющийся первым выходом блока управления, предназначен для подключения к входу обнуления реверсивного счетчика.