Мостовой дифференциальный усилитель

Иллюстрации

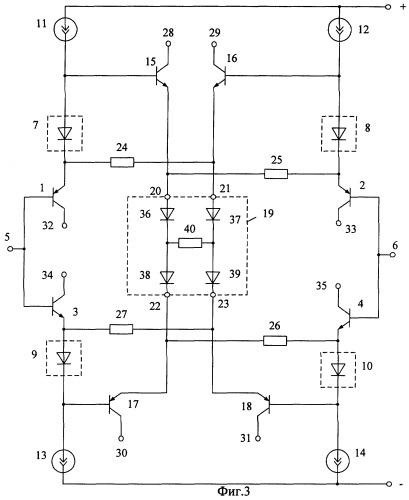

Показать всеИзобретение относится к радиотехнике для усиления широкополосных и импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения. Технический результат заключается в повышении быстродействия за счет уменьшения влияния на динамические параметры нелинейных процессов перезаряда емкостей коллекторных переходов. Усилитель (фиг.3) содержит входные транзисторы (Т) (1-4), эмиттеры которых связаны с базами соответствующих выходных Т (15-18), эмиттеры которых соединены с эмиттерами соответствующих входных Т (1-4) через дополнительные резисторы (24-26), а между эмиттерами выходных Т (15-18) включена резистивно-диодная согласующая подсхема (19). 3 з.п. ф-лы, 17 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов, в структуре операционных усилителей, усилителей мощности и аналоговых интерфейсов различного функционального назначения.

В современных аналоговых микросхемах находят применение два типа входных каскадов - классический дифференциальный усилитель [1-3] и мостовой дифференциальный каскад на составных n-р-n и р-n-р транзисторах (МДК) [4-15].

Мостовой дифференциальный каскад (МДК) стал основой построения практически всех быстродействующих операционных усилителей (ОУ) ведущих микроэлектронных фирм (Texas Instruments: патенты США №6710655, 6710654, 6492870, 6542032, 6249187, Analog Devices: патенты США №5150074, 6262633, Maxim: патенты США №6188281, 6429744, National Semiconductor: патенты США №5512859, 5399991, 5510754) [4-15].

Однако известные МДК имеют недостаточно высокое быстродействие из-за нелинейных режимов работы при большом импульсном сигнале. Это не позволяет (из-за эффектов второго порядка) получить предельные (теоретические) значения максимальной скорости нарастания выходного напряжения (ϑвых.max), которая оказывается в 5-10 раз выше экспериментальных значений (ϑвых≪ϑвых.max). Проблема достижения предельно возможного быстродействия МДК и ОУ на их основе является одной из актуальных проблем современной аналоговой микросхемотехники.

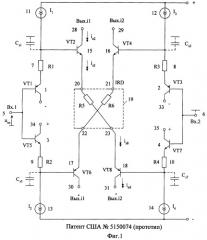

Ближайшим прототипом заявляемого устройства является дифференциальный усилитель (фиг.1) [9], содержащий первый 1 и второй 2 р-n-р входные транзисторы, первый 3 и второй 4 n-p-n входные транзисторы, базы которых связаны с базами соответствующих входных транзисторов 1 и 2 и входами усилителей 5 и 6. Эмиттеры транзисторов 1, 2 и 3, 4 соединены через первую 7, вторую 8, третью 9 и четвертую 10 цепи согласования потенциалов с первым 11, вторым 12, третьим 13 и четвертым 14 источниками опорного тока, а также с соответствующими базами первого 15 и второго 16 выходных n-p-n транзисторов и базами первого 17 и второго 18 выходных р-n-р транзисторов. Между эмиттерами транзисторов 15, 16, 17, 18 включена резистивно-диодная согласующая подсхема 19, выполненная на резисторах R5, R6, со входами 20, 21 и 22, 23, которая может иметь ряд частных случаев построения.

Существенный недостаток известного устройства состоит в том, что его архитектура не позволяет полностью исключить нелинейные режимы работы и тем самым получить предельные значения максимальной скорости нарастания выходного напряжения для большого сигнала, т.е. обеспечить ϑвых≈ϑвых.max.

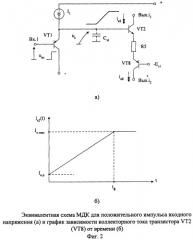

Рассмотрим работу МДК-прототипа. Если на вход 5 (база VT1) МДК фиг.1 подать импульс большой амплитуды uвх.1, то транзистор VT1 достаточно быстро закроется и переходный процесс напряжения на емкости Сэ1 uc(t) будет определяться зарядом этой емкости постоянным током I1 (эквивалентная схема МДК для данного случая показана на фиг.2а):

Емкость Сэ1 (Сэ3, Сэ5, Сэ7) складывается из выходной емкости источников тока I1 (I2, I5, I4) (емкости на подложку) и емкостей коллектор-база транзисторов VT2, VT4, VT6, VT8. Численные значения Сэ1 лежат для современных технологий с изоляцией р-n переходом в диапазоне 2-4 пФ.

Напряжение uc(t) поступает на базу VT2 (фиг.2а) и поэтому зависимость приращения коллекторного тока выходного транзистора VT2 (VT8) от времени имеет линейный характер (фиг.2б):

где τэ1=Сэ1·R5.

Таким образом, время (tф.МДК) изменения тока коллектора VT2 от статического уровня Iк.р до некоторого заданного значения Iк.max≫Ik.р:

Из уравнения (3) следует, что выходной коллекторный ток транзистора VT2 имеет форму «пилы» (фиг.2б), а время его нарастания до заданного значения Iк.max при типовых параметрах элементов изменяется десятками наносекунд. Так, при I1=1 мА и Iк.max=50 мА, R2=200 Ом, Сэ1=1 пФ время фронта tф.МДК=10 нс. Данные (сравнительно большие) значения tф.МДК не позволяют создавать на базе известных мостовых ДК быстродействующие ОУ с предельно высокими значениями максимальной скорости нарастания выходного напряжения ϑвых, которая определяется передним фронтом тока iк2. Это объясняется тем, что быстродействие МДК должно быть значительно больше, чем быстродействие ОУ с МДК в целом, так как МДК «включается» в работу и форсирует процессы перезаряда самого инерционного элемента схемы (корректирующей емкости ОУ Ск) только во время фронта выходного напряжения ОУ, которое связано с максимальной скоростью нарастания выходного напряжения (ϑвых) следующей приближенной формулой:

где ЕП - напряжение питания ОУ,

tф.ОУ - время фронта выходного напряжения ОУ при 100% обратной связи.

Должно быть

Если проектируемый ОУ имеет ϑвых= 5000 В/мкс и Еп=5 В, то tф.ОУ≈1 нс.

С учетом формул (1)-(4) можно найти, что при заданной ϑвых в схеме фиг.1 должно выполняться неравенство

При рассматриваемых параметрах элементов из формулы (5) следует, что МДК-прототип при напряжении питания, равном, например, 5 В, не эффективен, если на его основе необходимо спроектировать ОУ, имеющий максимальную скорость нарастания выходного напряжения более 100-300 В/мкс. Указанное обстоятельство становится еще более доминирующим при работе входных транзисторов МДК в микрорежиме, т.е. при малых токах I1.

Таким образом, невысокое быстродействие известного устройства ограничивает быстродействие различных аналоговых систем, в т.ч. операционных усилителей на его основе, НЧ-усилителей мощности с обратной связью и т.п.

Основная цель предлагаемого изобретения состоит в повышении быстродействия устройства. Это позволит получить максимальную скорость нарастания выходного напряжения в ОУ на его основе (ϑвых) в диапазоне сотен вольт на микросекунду при использовании отечественных микронных технологий.

Поставленная цель достигается тем, что в известном дифференциальном усилителе-прототипе, содержащем первый 1 и второй 2 входные р-n-р транзисторы, первый 3 и второй 4 входные n-р-n транзисторы, базы которых связаны с базами соответствующих входных транзисторов 1 и 2 и входами усилителей 5 и 6, эмиттеры транзисторов 1, 2 и 3, 4 через первую 7, вторую 8, третью 9 и четвертую 10 цепи согласования потенциалов соединены с первым 11, вторым 12, третьим 13 и четвертым 14 источниками опорного тока, а также с соответствующими базами первого 15 и второго 16 выходных n-р-n транзисторов и базами первого 17 и второго 18 выходных р-n-р транзисторов, причем между эмиттерами транзисторов 15, 16, 17, 18 включена резистивно-диодная согласующая подсхема 19 со входами 20, 21, 22, 23, вводятся новые элементы и связи между ними - эмиттер первого выходного n-р-n транзистора соединен с эмиттером второго р-n-р входного транзистора через первый дополнительный резистор, эмиттер второго выходного n-р-n транзистора соединен с эмиттером первого входного р-n-р транзистора через второй дополнительный резистор, а эмиттер первого выходного р-n-р транзистора соединен с эмиттером второго входного n-р-n транзистора через третий дополнительный резистор, а эмиттер второго выходного р-n-р транзистора соединен с эмиттером первого входного n-р-n транзистора через четвертый дополнительный резистор.

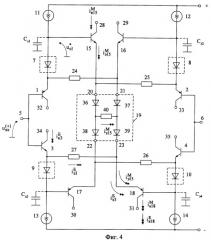

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.3. На фиг.4 показана схема усилителя фиг.3 с указанием токов и напряжений, поясняющая его работу. На фиг.5 и 6 показаны частные варианты построения резистивно-диодной согласующей подсхемы 19 в соответствии с п.2-п.3 формулы изобретения. На фиг.7 и 8 приведены схемы практического включения заявляемого устройства в ОУ (в соответствии с п.4 формулы изобретения). На фиг.9 и 10 показаны результаты компьютерного моделирования заявляемого устройства в среде PSpice с использованием моделей транзисторов ФГУП «Пульсар» (г.Москва).

Мостовой дифференциальный усилитель (фиг.3) содержит первый 1 и второй 2 р-n-р входные транзисторы, первый 3 и второй 4 n-p-n входные транзисторы, базы которых связаны с базами соответствующих входных транзисторов 1 и 2 и входами усилителей 5 и 6. Эмиттеры транзисторов 1, 2 и 3, 4 соединены через первую 7, вторую 8, третью 9 и четвертую 10 цепи согласования потенциалов соответственно с первым 11, вторым 12, третьим 13 и четвертым 14 источниками опорного тока, а также с соответствующими базами первого 15 и второго 16 выходных n-p-n транзисторов и базами первого 17 и второго 18 выходных р-n-р транзисторов. Между эмиттерами транзисторов 15, 16, 17, 18 включена резистивно-диодная согласующая подсхема 19 со входами 20, 21, 22, 23, которая может иметь ряд частных случаев построения (фиг.5-фиг.6). С целью повышения быстродействия эмиттер первого выходного n-p-n транзистора 15 соединен с эмиттером второго р-n-р входного транзистора 2 через первый дополнительный резистор 24, эмиттер второго 16 выходного n-p-n транзистора соединен с эмиттером первого входного р-n-р транзистора 1 через второй 25 дополнительный резистор, а эмиттер первого выходного р-n-р транзистора 17 соединен с эмиттером второго входного n-р-n транзистора 4 через третий дополнительный резистор 26, эмиттер второго выходного р-n-р транзистора 18 соединен с эмиттером первого входного n-р-n транзистора 3 через четвертый дополнительный резистор 27.

Основными токовыми выходами заявляемого ДУ являются узлы 28-31, дополнительными токовыми выходами узлы 32-35, которые могут соединяться с узлами 28-31 в соответствии с п.4 формулы изобретения.

Рассмотрим работу заявляемого устройства при большом импульсном сигнале на входе 5 относительно входа 6 (фиг.4).

Если скачок положительного напряжение на входе 5 относительно входа 6 достаточно велик (uвх≈4÷5 В), что характерно для работы МДК в ОУ с напряжением питания пять и более вольт, то транзистор 1 достаточно быстро войдет в отсечку, так как во время фронта uвх потенциал его эмиттера «зафиксирован» емкостью Сэ1=1-4 пФ. В результате эмиттерный ток транзисторов 15 и 18 (фиг.2) будет иметь медленно изменяющуюся составляющую

где R40 - эквивалентное сопротивление двухполюсника 40.

Благодаря введению нового элемента 27 в схеме фиг.3 (фиг.4) образуется дополнительный путь формирования «быстрой» составляющей эмиттерных и коллекторных токов транзисторов 3 и 18:

где R27 - сопротивление резистора 27.

Инерционность этих составляющих выходных токов узлов 31 и 34 МДУ фиг.4 не зависит от паразитных емкостей Сэi, что позволяет сформировать хороший фронт токов в цепях выходных узлов 31 и 34. При соединении узлов 34 и 28 суммарный выходной ток также будет иметь «быструю» составляющую, что положительно сказывается на быстродействии устройства.

При другой полярности импульсного входного сигнала или его подаче на вход 6 относительно входа 5 схема фиг.3 (фиг.4) работает относительно выходов 28, 29, 30, 31, 32, 33, 34, 35 аналогичным образом.

По мере завершения переходного процесса - увеличения напряжения на емкости Сэi в работу включается основной канал передачи сигнала - через подсхему 19.

Варианты включения заявляемого МДК в схемах быстродействующих операционных усилителей показаны на чертеже фиг.7 и 8. Эти схемы ОУ содержат входной МДК, повторители токов 36-37, корректирующий конденсатор Ск 38 и буферный усилитель 39, а также (фиг.8) транзисторы «перегнутого» каскада 40, 41 и источники опорного тока 42, 43.

Схема заявляемого МДК, исследованного в среде Pspice, приведена на фиг.9. Для измерения токов в цепи выходов включены низкоомные резисторы: 28-Rc1, 30-Rc2, 29-Rc3, 31-Rc4, 34-Rncc1, 32-Rncc2, 33-Rncc4, 35-Rncc5. Модели транзисторов в данной съеме соответствуют интегральным транзисторам ФГУП «Пульсар». Статический режим устанавливается токами I1=I2=I3=I4=I0, которые выбирались равными 0,5 мА и 0,1 мА. Паразитная емкость источников тока Cs=2 пФ. Сопротивление резисторов R11=R12=R2=R13=R=200 Ом.

Переходный процесс токов выходов 28 (IRc1) и 34 (IRncc1) при Io=0,5 мА усилителя фиг.9 показан на фиг.10. Время фронта Тфр(IRc1)=48 нс, Тфр(IRncc1)=0,96 нс. Аналогичные динамические характеристики имеют синфазные выходы 29 и 35, 31 и 33, 30 и 38 при соответствующих полярностях импульсного сигнала на входах 5 и 6.

На фиг.11 показан переходный процесс токов выходов 31 (IRc4) и 34 (IRncc1) в схеме фиг.9. Время фронта Тфр(IRс4)=0,49 нс, Тфр(IRnсс1)=0,96 нс при I0=0,5 мА.

Схема исследованного операционного усилителя с предлагаемым (по п.4 формулы изобретения) входным каскадом представлена на фиг.12.

На фиг.13 приведены графики переходных процессов на выходе ОУ фиг.12 (кривая 1) и ОУ с известным входным каскадом (прототипом) (кривая 2).

На фиг.14 показана логарифмическая АЧХ разомкнутого ОУ фиг.12 и замкнутого ОУ фиг.12 при 100% обратной связи.

Схема исследованного ОУ с предлагаемым (по п.1 формулы изобретения) входным каскадом дана на фиг.15. В этой схеме выходы входного каскада 32-35 не используются.

На фиг.16 приведены графики переходных процессов на выходе ОУ фиг.15 (кривая 1) и ОУ с известным входным каскадом (прототипом) (кривая 2).

На фиг.17 показана логарифмическая АЧХ разомкнутого ОУ фиг.15 и замкнутого ОУ фиг.15 при 100% обратной связи.

Из их рассмотрения следует, что заявляемый МДК имеет значительно лучшие динамические параметры.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Операционные усилители с непосредственной связью каскадов / В.И.Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М.Соколов. - Л., 1979.

3. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с.

4. Патент США №6710655.

5. Патент США №6710654.

6. Патент США №6492870.

7. Патент США №6542032.

8. Патент США №6249187.

9. Патент США №5150074.

10. Патент США №6262633.

11.Патент США №6188281.

12. Патент США №6429744.

13. Патент США №5512859.

14. Патент США №5399991.

15. Патент США№5510754.

1. Дифференциальный усилитель, содержащий первый и второй р-n-р-входные транзисторы, первый и второй n-р-n-входные транзисторы, базы которых связаны с базами соответствующих входных р-n-р-транзисторов и входами усилителя, эмиттеры входных р-n-р- и n-р-n-транзисторов через первую, вторую, третью и четвертую цепи согласования потенциалов соединены соответственно с первым, вторым, третьим и четвертым источниками опорного тока, а также с соответствующими базами первого и второго выходных n-р-n-транзисторов и базами первого и второго выходных р-n-р-транзисторов, причем между эмиттерами выходных транзисторов включена резистивно-диодная согласующая подсхема с четырьмя входами, отличающийся тем, что эмиттер первого выходного n-р-n-транзистора соединен с эмиттером второго р-n-р-входного транзистора через первый дополнительный резистор, эмиттер второго выходного n-р-n-транзистора соединен с эмиттером первого входного р-n-р-транзистора через второй дополнительный резистор, а эмиттер первого выходного р-n-р-транзистора соединен с эмиттером второго входного n-р-n-транзистора через третий дополнительный резистор, эмиттер второго выходного р-n-р-транзистора соединен с эмиттером первого входного n-р-n-транзистора через четвертый дополнительный резистор.

2. Устройство по п.1, отличающееся тем, что резистивно-диодная согласующая подсхема содержит два последовательно включенных р-n-перехода левого плеча и два последовательно включенных р-n-перехода правого плеча, между средней точкой которых включен вспомогательный резистор.

3. Устройство по п.1, отличающееся тем, что резистивно-диодная согласующая подсхема содержит последовательно включенные вспомогательный резистор и два р-n-перехода левого плеча, а также вспомогательный резистор и два последовательно включенных р-n-перехода правого плеча.

4. Устройство по п.1, отличающееся тем, что коллектор первого входного n-р-n-транзистора соединен с коллектором первого выходного n-р-n-транзистора, коллектор второго выходного n-р-n-транзистора соединен с коллектором второго входного n-р-n-транзистора, коллектор первого входного р-n-р-транзистора соединен с коллектором первого выходного р-n-р-транзистора, а коллектор второго входного р-n-р-транзистора соединен с коллектором второго выходного р-n-р-транзистора.