Дифференциальный усилитель с повышенным ослаблением синфазного сигнала

Иллюстрации

Показать всеУстройство относится к радиотехнике и связи для использования в различных микроэлектронных устройствах усиления и преобразования аналоговых сигналов. Техническим результатом является повышение коэффициента ослабления входного синфазного сигнала. Дифференциальный усилитель содержит входной дифференциальный каскад на первом и втором входных транзисторах, эмиттеры которых соединены с выходом первого токового зеркала, первый и второй транзисторы канала компенсации входного тока, базы которых соединены с базами первого и второго входных транзисторов, а эмиттеры подключены к выходам цепи стабилизации статического режима. Коллекторы первого и второго транзисторов канала компенсации входного тока связаны со входом первого токового зеркала. 3 з.п.ф-лы, 15 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны дифференциальные усилители (ДУ) с источником опорного тока в общей эмиттерной цепи на базе токового зеркала, которые стали основой построения многих современных операционных усилителей [1-9]. Однако они имеют недостаточно высокое ослабление входного синфазного сигнала из-за сравнительно небольших значений выходного сопротивлений токового зеркала (десятки килоом). Проблема повышения коэффициента ослабления входного синфазного сигнала ДУ данного класса (Кос.сф) (или коэффициента преобразования входного синфазного напряжения ДУ в выходное напряжение Кус), которые широко используются в операционных усилителях с «минимальной электрической длиной», является одной из актуальных проблем современной аналоговой микросхемотехники.

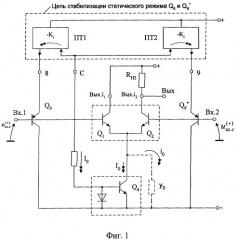

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель [Патент США 4451800, H 03 f 3/45], содержащий входной дифференциальный каскад на первом Q1 и втором Q2 входных транзисторах, эмиттеры которых соединены с выходом первого токового зеркала Q4, первый Q9 и второй Q*9 транзисторы канала компенсации входного тока, базы которых соединены с базами первого Q1 и второго Q3 входных транзисторов, а эмиттеры подключены к выходам цепи стабилизации статического режима Q9 и Q*9.

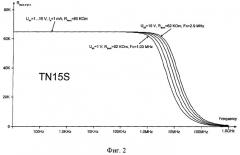

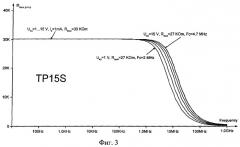

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно большое ослабление входного синфазного сигнала. Для современных интегральных транзисторов, например, ФГУП «Пульсар», выходное сопротивление типовых токовых зеркал, например, Q4 фиг.1 на n-р-n (фиг.2) и р-n-р (фиг.3) транзисторах лежит в диапазоне единиц-десятков килоом, что не позволяет получить высокий Кос.сф (Кус).

Анализ ДУ прототипа.

Коэффициент ослабления входного синфазного напряжения ДУ-прототипа для случая, когда сопротивление нагрузки RH2 включено в цепь коллектора Q2 (фиг.1) равен

где Куд=RH2/(rэ1+rэ2)=(I0RH2)/(4ϕт)=uвых/uвх.д - дифференциальный коэффициент передачи напряжения ДУ;

rэ1=rэ2=2ϕт/I0 - дифференциальные сопротивления эмиттерных переходов Q1 и Q2;

Кус=uвых/uвх.c (+) - коэффициент преобразования входного синфазного напряжения ДУ в выходное напряжение ДУ;

ϕт≈25 мВ - температурный потенциал.

Численное значение Кус можно найти с учетом следующих соотношений

где α2 - коэффициент передачи по току эмиттера транзистора Q2;

у0 - выходная проводимость токового зеркала на транзисторе Q4.

Поэтому

Из (5) и (6) следует, что величины Кус и Кос.сф зависят от выходной проводимости у0 токового зеркала, которая, как показывает эксперимент (фиг.2 и фиг.3), при типовом построении токового зеркала Q4 на n-р-n транзисторах и Iо=1÷3 mA лежит в диапазоне нескольких десятков килоом:

где yК4≈r-1 K4 - проводимость коллектор-база транзистора Q4 в схеме с общей базой;

μ4=10-3 - коэффициент внутренней обратной связи транзистора Q4 в схеме с общей базой;

- сопротивление эмиттерного перехода транзистора Q4;

Кi≈1 - коэффициент передачи по току токового зеркала Q4.

Поэтому

Большие значения y0 в схеме ДУ-прототипа отрицательно сказываются на его коэффициенте ослабления синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входного синфазного напряжения.

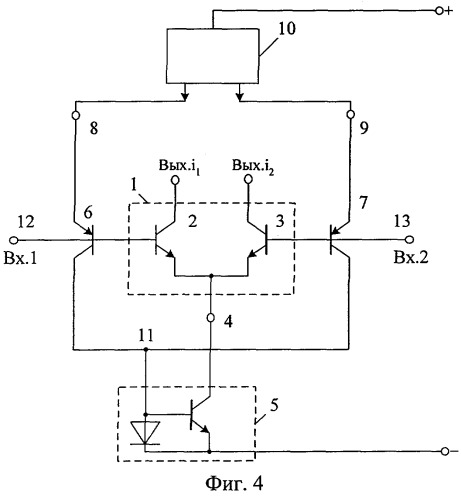

Поставленная цель достигается тем, что в дифференциальный усилитель, содержащий входной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах, эмиттеры которых соединены с выходом 4 первого 5 токового зеркала, первый 6 и второй 7 транзисторы канала компенсации входного тока ДУ, базы которых соединены с базами первого 2 и второго 3 входных транзисторов, а эмиттеры подключены к выходам 8 и 9 цепи стабилизации статического режима 10, вводятся новые связи - коллекторы первого 6 и второго 7 транзисторов канала компенсации входного тока ДУ соединены со входом 11 первого токового зеркала 5.

Схема заявляемого устройства показана на фиг.4. Дифференциальный усилитель (фиг.4) содержит входной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах, эмиттеры которых соединены с выходом 4 первого 5 токового зеркала, первый 6 и второй 7 транзисторы канала компенсации входного тока ДУ, базы которых соединены с базами первого 2 и второго 3 входных транзисторов, а эмиттеры подключены к выходам цепи стабилизации статического режима 10. Коллекторы первого 6 и второго 7 транзисторов канала компенсации входного тока ДУ связаны со входом 11 первого токового зеркала 5. Входами ДУ 12 и 13 являются базы транзисторов 2 и 3.

На фиг.5, фиг.6 показаны частные случаи выполнения цепей стабилизации статического режима 10. Схема фиг.5 включает выходные р-n-р транзисторы 14, 15 и транзистор в диодном включении 16 токовых зеркал, а также источник опорного тока 17, который подключен ко входу 18 цепи стабилизации статического режима 10.

В схеме фиг.6 цепь стабилизации 10 реализована на токовом зеркале, содержащем транзистор 19 и диод 20, а также источники опорного тока 21.

На фиг.7 приведена схема фиг.4, которая реализована в соответствии с п.4 формулы изобретения и содержит цепь стабилизации статического режима по схеме фиг.6, а также включение параллельно транзисторам 6 и 7 дополнительных транзисторов 6* и 7*, коллекторы которых соединены с шиной отрицательного источника питания. На схеме фиг.7 такое соединение элементов изображено в виде двух коллекторных транзисторов.

Статический режим типового токового зеркала 5 может также устанавливаться двухполюсником 22. Это позволяет за счет изменения статического режима обеспечить более глубокое ослабление синфазных сигналов в ДУ фиг.7, т.к. численные значения выходных проводимостей y0 и y*0 токовых зеркал 5 и 10 зависят от статических токов двухполюсников 21 и 22.

На фиг.8 показаны токи и напряжения в схеме фиг.4 при подаче на входы 12 и 13 одинаковых значений низкочастотного входного напряжения u1 (+)=u2 (+)=uвх.с, которое называется входным синфазным сигналом. Эта схема поясняет работу заявляемого устройства.

Высокочастотные составляющие переменных токов в заявляемой схеме ДУ для случая, когда в качестве цепей стабилизации 10 применяются источники опорного тока I1 и I2 (фиг.5) с паразитными выходными емкостями , показаны на фиг.9.

Переменные токи и напряжения в схеме фиг.7 для области низких частот приведены на фиг.10.

На фиг.11 изображена схема ДУ фиг.10, у которой исследовалась степень ослабления синфазных сигналов в диапазоне низких частот (фиг.12) для двух случаев - когда в ней отсутствуют новые связи (прототип) и когда схема соответствует формуле изобретения (заявляемое устройство).

Схемы фиг.13 и фиг.14 исследовались авторами в среде PSpice с использованием моделей интегральных транзисторов ФГУП «Пульсар» (г.Москва). Схема фиг.13 соответствует ДУ-прототипу, а схема фиг.14 - заявляемому ДУ (фиг.9). Результаты их компьютерного моделирования показаны на фиг.15.

Рассмотрим работу ДУ фиг.4. Его соответствующая эквивалентная схема для диапазона низких частот изображена на фиг.8, где обозначено: у0 - выходная проводимость токового зеркала 5, определяемая формулами (7), (8); - выходная проводимость цепей стабилизации статического режима 10, которая для рассматриваемой цепи 10 также определяется формулами (7) и (8), однако для р-n-р транзисторов; I1 - статический выходной ток цепи 10.

Если на вход ДУ подается синфазный сигнал uвх.c, то напряжение на элементах у0 и у*0 будет близко к Поэтому приращение напряжений и токов в элементах схемы можно определить с учетом законов Ома и Кирхгофа по следующим формулам:

где Кi5 - коэффициент передачи по току токового зеркала 5.

Из формулы (15) можно найти коэффициент преобразования входного синфазного сигнала в выходное напряжение ДУ

Для ДУ-прототипа этот коэффициент определяется формулой (5). Сравнение формул (5) и (16) показывает, что заявляемый ДУ имеет в n-раз меньшее значение Кус:

Для обеспечения N=∝ необходимо выбирать

В частном случае, когда Кi5=1, условие N=∝ реализуется при равенстве выходной проводимости цепей стабилизации 10 и выходной проводимости токового зеркала

Как правило, выходная проводимость цепей стабилизации в несколько раз больше выходной проводимости токового зеркала 5 y0 (фиг.2, фиг.3). Чтобы при Кi5=1 было проще реализовывать N=∝ схему в соответствии с п.4 формулы изобретения, вводятся делители токов эмиттеров транзисторов 6 и 7, которые реализованы на транзисторах 6* и 7* (фиг.10). Изменяя отношение площадей эмиттера транзисторов 6 и 6*, 7 и 7*, можно получить необходимый выигрыш по ослаблению синфазных сигналов практически при любых реальных соотношениях между у0 и у0*.

Представленные на фиг.12 результаты компьютерного моделирования схемы фиг.11 подтверждают данные выводы. За счет изменения величины статического тока I0 в схеме фиг.11 изменялась величина у0 при Как следствие, при I0=1,05 мА обеспечивалось равенство и поэтому заявляемая схема в диапазоне низких частот имела более чем в 1000 раз лучшее ослабление синфазных сигналов (на 72 дБ, фиг.12).

Анализ работы заявляемого ДУ в диапазоне высоких частот.

Схема для расчета переменных составляющих токов в заявляемом ДУ для высоких частот и варианта фиг.5 цепи 10 показана на фиг.9, где обозначено:

- Сп1=3÷5 пФ - емкость на подложку выходного транзистора токового зеркала 5;

- - емкость на подложку выходных транзисторов источников опорного тока I1, I2, входящих в подсхему стабилизации статического режима 10 транзисторов 6 (VT3) и 7 (VT4);

- Скпт=0.3÷1 пФ - емкость коллектор-база выходного транзистора токового зеркала 5;

- СK3≈СK4≈CK1≈СK2=0.3÷1 пФ - емкость коллектор-база транзисторов 3, 4, 1, 2.

На входы ДУ фиг.9 подается высокочастотное (сотни мегагерц) синфазное напряжение uc=u1 (+)=u1 (-), которое передается в эмиттерные цепи VT1, VT2 и VT3, VT4, создавая переменные составляющие токов через паразитные емкости транзисторов:

Высокочастотная составляющая суммарного тока общей эмиттерной цепи ДУ:

где - комплексные коэффициенты передачи по току эмиттера транзисторов VT3, VT4 и токового зеркала 5.

С учетом (1) формулу (2) можно привести к виду

Если в рассматриваемом диапазоне частот то

где

Если обеспечить то высокочастотная составляющая тока общей эмиттерной цепи ДУ iΣ будет мала, что положительно скажется на ослаблении синфазных сигналов ДУ. Компьютерное моделирование этих эффектов показывает, что в заявляемой схеме на высоких частотах обеспечивается уменьшение коэффициента преобразования входного синфазного напряжения в более широком диапазоне частот.

Таким образом, заявляемый ДУ имеет более высокое ослабление синфазных сигналов как на постоянном токе (в сотни-тысячи раз), так и в диапазоне высоких частот.

Источники информации

1. Патент США №4451800, H 03 f 3/45 (прототип).

2. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.

3. Патент США №3693108, H 03 f 3/45.

4. Патент США №3997850, H 03 f 3/45.

5. Патент США №6501333, H 03 f 3/45.

6. Патент США №4439696, H 03 f 3/45.

7. Патент США №6433636, H 03 f 3/45.

8. Патент США №3401351, H 03 f 3/45.

9. Патент США №5065112, H 03 f 3/45.

1. Дифференциальный усилитель, содержащий входной дифференциальный каскад на первом и втором входных транзисторах, эмиттеры которых соединены с выходом первого токового зеркала, первый и второй транзисторы канала компенсации входного тока, базы которых соединены с базами первого и второго входных транзисторов, а эмиттеры подключены к выходам цепи стабилизации статического режима, отличающийся тем, что коллекторы первого и второго транзисторов канала компенсации входного тока связаны со входом первого токового зеркала.

2. Устройство по п.1, отличающееся тем, что цепь стабилизации статического режима реализована на основе вспомогательных токовых зеркал, входы которых объединены и соединены с источником опорного тока, а выходы являются выходами цепи стабилизации статического режима.

3. Устройство по п.1, отличающееся тем, что цепь стабилизации статического режима реализована на основе токового зеркала, вход которого соединен с источником опорного ток, а выход связан с выходами цепи стабилизации статического режима.

4. Устройство по п.1, отличающееся тем, что параллельно первому и второму транзисторам цепи компенсации входного тока включены дополнительные транзисторы, коллекторы которых соединены с шиной источника питания.