Система спутниковой связи

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может быть использовано в системах дуплексной связи с множественным доступом с частотным разделением, обработкой и коммутацией сигналов корреспондентов на борту спутникового ретранслятора связи. Достигаемым техническим результатом изобретения является обеспечение более высокой помехозащищенности сигналов с низким уровнем за счет исключения их подавления полезными сигналами с высоким уровнем на входе спутникового ретранслятора. Система спутниковой связи состоит из N>2 земных станций спутниковой связи и спутникового ретранслятора. Каждая земная станция спутниковой связи содержит антенно-фидерный тракт, усилитель мощности, дуплексер, входной блок, возбудитель, блок частотного разделения, приемник, блок разделения и объединения, сумматор по модулю два, линию задержки, блок управления возбудителем, блок формирования информационно-тестовых сигналов и спутниковый ретранслятор с обработкой сигналов на борту. 3 з.п. ф-лы, 19 ил.

Реферат

Изобретение относится к области радиотехники и может быть использовано в системах дуплексной связи с множественным доступом с частотным разделением, обработкой и коммутацией сигналов корреспондентов на борту спутникового ретранслятора связи.

Известна спутниковая система связи (см. Хуан Р. и Хутен Ф. Ретранслятор системы спутниковой связи с обработкой сигналов на борту, ТИИЭР, N2, 1971, с.139-155), которая состоит из спутникового ретранслятора с обработкой сигналов на борту, содержащего приемную антенну, предварительный усилитель, блок дешифрации и разделения, генератор кода, N узкополосных фильтров, N демодуляторов, сумматор, усилитель мощности, передающую антенну и N земных оконечных станций.

Недостатком данной спутниковой системы связи является низкая помехозащищенность от информационных сигналов с повышенным уровнем сигнала вследствие отсутствия возможности выравнивания уровней сигналов, имеющих разрешенные кодовые комбинации.

Также известна система спутниковой связи (см. Игнатов В.В., Чистяков А.П. Обоснование основных технических параметров перспективной техники многоканальной радиосвязи. - Л.: ВАС, 1988, с.29-35), которая состоит из спутникового ретранслятора с обработкой сигналов на борту, содержащего приемную и передающую антенные системы, малошумящий усилитель мощности, смеситель, N индивидуальных трактов, каждый из которых состоит из усилителя промежуточной частоты, полосового фильтра, демодулятора. Общими для N трактов являются аппаратура временного объединения, модулятор и усилитель мощности. Каждая земная станция спутниковой связи содержит антенно-фидерный тракт, дуплексер, входное устройство, устройство частотного разделения, приемник, аппаратуру разделения и объединения, возбудитель, усилитель мощности.

Недостатком данной спутниковой системы связи является относительно низкая помехозащищенность, т.к. отсутствует возможность автоматического регулирования мощности земных станций спутниковой связи на передачу для обеспечения одинакового уровня информационного сигнала на входе малошумящего усилителя мощности спутникового ретранслятора.

Наиболее близкой по технической сущности к заявляемой системе спутниковой связи является система спутниковой связи по патенту РФ №2090003, опубл. 10.09.97 г., Бюл. N25.

Система спутниковой связи - прототип состоит из N земных станций спутниковой связи, каждая из которых содержит антенно-фидерный тракт, усилитель мощности, дуплексер, входное устройство, возбудитель, устройство частотного разделения, приемник, аппаратуру разделения и объединения, линию задержки, сумматор по модулю два и спутниковый ретранслятор с обработкой сигналов на борту, который содержит приемную антенную систему, малошумящий усилитель мощности, смеситель, N усилителей промежуточной частоты, N полосовых фильтров, N демодуляторов, коммутатор, К сумматоров по модулю два, аппаратуру временного объединения, модулятор, усилитель мощности, передающую антенную систему, гетеродин.

При этом в каждой земной станции спутниковой связи последовательно соединены антенно-фидерный тракт, выход которого подключен к первому входу дуплексера, выход которого подключен к входу входного устройства, выход которого подключен к входу устройства частотного разделения, выход которого подключен к входу приемника, выход которого подключен к первому входу аппаратуры разделения и объединения, второй выход которой подключен к второму входу сумматора по модулю два, первый выход аппаратуры разделения и объединения одновременно подключен к входу линии задержки и к входу возбудителя, выход которого подключен к входу усилителя мощности, выход которого подключен к второму входу дуплексера, выход задержки подключен к первому входу сумматора по модулю два, к выходу которого подключаются абоненты земной станции спутниковой связи, абонентский вход земной станции спутниковой связи подключен к второму входу аппаратуры разделения и объединения, в спутниковом ретрансляторе последовательно соединены приемная антенная система, малошумящий усилитель, смеситель, выход которого одновременно подключен к входам N усилителей промежуточной частоты, выход каждого из которых подключен к входам соответствующих полосовых фильтров, выход каждого из которых подключен к входам соответствующих демодуляторов, выходы которых подключены к соответствующим входам коммутатора, выходы которого подключены к соответствующим первым и вторым входам сумматоров по модулю два, выходы которых подключены к соответствующим входам аппаратуры временного объединения, выход которой подключен к первому входу модулятора, выход которого подключен к входу усилителя мощности, выход которого подключен к передающей антенной системе, на вторые входы смесителя и модулятора подключены соответствующие выходы гетеродина.

Достоинствами рассмотренной системы спутниковой связи по сравнению с аналогами является обеспечение более высокой оперативности установления соединений между земными станциями спутниковой связи и уменьшение скорости и полосы частот радиолинии спутниковый ретранслятор - земная станция спутниковой связи при сохранении пропускной способности.

Недостатком прототипа является относительно низкая помехозащищенность из-за эффекта подавления информационных сигналов с низким уровнем информационными сигналами с высоким уровнем на входе спутникового ретранслятора, что вызвано отсутствием объективного контроля качества информационного канала связи, обусловленного передачей тестовой информации по каналам служебной связи.

Целью изобретения является разработка системы спутниковой связи, обеспечивающей более высокую помехозащищенность сигналов с низким уровнем за счет исключения их подавления информационными сигналами с высоким уровнем на входе спутникового ретранслятора.

Для достижения сформулированной цели в известной системе спутниковой связи, включающей N≥2 земных станций спутниковой связи и спутниковый ретранслятор, который содержит приемную антенну, выход которой подключен к входу малошумящего усилителя мощности, выход которого подключен к сигнальному входу смесителя, N избирательных трактов, каждый из которых состоит из последовательно включенных усилителя промежуточной частоты, полосового фильтра, демодулятора, причем вход усилителя промежуточной частоты и выход демодулятора являются соответственно входом и выходом избирательного тракта, входы избирательных трактов объединены и подключены к сигнальному выходу смесителя, гетеродинный вход которого подключен к выходу гетеродина, выход i-го избирательного тракта, где i=1,2,...N, подключен к i-му входу коммутатора, N/2 сумматоров по модулю два, выход j-го, где j=1,2,...N/2, сумматора по модулю два подключен к j-му входу блока временного объединения, выход которого подключен к сигнальному входу модулятора, а гетеродинный вход к выходу гетеродина, выход модулятора подключен к входу усилителя мощности, выход которого подключен к входу передающей антенны, а каждая земная станция спутниковой связи включает дуплексер, приемопередающий вход-выход которого подключен к антенно-фидерному тракту, сигнальный вход дуплексера подключен к выходу усилителя мощности, вход которого подключен к выходу возбудителя, сигнальный выход дуплексера подключен к входу входного блока, выход которого подключен к входу блока частотного разделения, выход которого подключен к входу приемника, выход которого подключен к сигнальному входу блока разделения и объединения, линию задержки, выход которой подключен к информационному входу сумматора по модулю два, сигнальный вход которого подключен к сигнальному выходу блока разделения и объединения, а информационный выход которого подключен к входу линии задержки, причем информационный вход блока разделения и объединения и выход сумматора по модулю два являются соответственно информационными входом и выходом земной станции спутниковой связи, на спутниковый ретранслятор дополнительно введены N/2 коммутаторов тестового сигнала, i-й и i+1-й выходы коммутатора подключены соответственно к информационному и сигнальному входам [j=(i+1)/2]-го коммутатора тестового сигнала, а информационный и сигнальный выходы j-го коммутатора тестового сигнала подключены соответственно к информационному и сигнальному входам j-го сумматора по модулю два. На каждой земной станции спутниковой связи дополнительно введены блок управления возбудителем и блок формирования информационно-тестовых сигналов, управляющий и информационный выходы которого подключены соответственно к управляющему входу блока управления возбудителем и к информационному входу возбудителя. Информационный и сигнальный входы блока формирования информационно-тестовых сигналов подключены к входам соответственно линии задержки и сумматора по модулю два. Выход блока управления возбудителем подключен к управляющему входу возбудителя.

Коммутатор тестового сигнала состоит из формирователя сигнала запуска таймера, таймера, счетчика четных циклов, счетчика нечетных циклов, одновибратора, первого и второго логических элементов И и первого и второго логических элементов ИЛИ. Выход формирователя сигнала запуска таймера подключен к входу таймера, первый, второй и третий выходы которого подключены к входам соответственно счетчика четных циклов, одновибратора, счетчика нечетных циклов. Выходы счетчика четных циклов и счетчика нечетных циклов подключены к первым входам логических элементов И соответственно, а выход одновибратора подключен ко вторым входам логических элементов И. Выходы логических элементов И подключены ко вторым входам соответственно логических элементов ИЛИ, причем первые выходы логических элементов ИЛИ подключены соответственно к первому и второму входам формирователя сигнала запуска таймера и являются первым и вторым входами коммутатора тестового сигнала. Выходы логических элементов ИЛИ являются соответственно первым и вторым выходами коммутатора тестового сигнала.

Блок формирования информационно-тестовых сигналов состоит из первого логического элемента НЕ, выход которого подключен к второму входу первого логического элемента И, первый вход которого подключен к входу таймера и является первым входом блока формирования информационно-тестовых сигналов. Выход первого логического элемента И подключен к первому входу логического элемента ИЛИ, второй вход которого подключен к выходу третьего логического элемента И. Выход логического элемента ИЛИ является вторым выходом блока формирования информационно-тестовых сигналов. Вход первого логического элемента НЕ подключен к первому входу третьего логического элемента И, входу формирователя тестовой последовательности, выходу одновибратора, второму входу пятого логического элемента И и входу первой линии задержки. Второй вход третьего логического элемента И подключен к выходу формирователя тестовой последовательности и входу второго логического элемента НЕ, выход которого подключен к первому входу пятого логического элемента И, выход которого подключен к входу второй линии задержки, выход которой подключен к второму входу сумматора по модулю два, первый вход которого является вторым входом блока формирования информационно-тестовых сигналов. Выход таймера подключен к входу одновибратора. Выход первой линии задержки подключен к первому входу четвертого логического элемента И, второй вход которого подключен к выходу сумматора по модулю два, причем выход четвертого логического элемента И является первым выходом блока формирования информационно-тестовых сигналов.

Блок управления возбудителем состоит из элемента разрешения, информационный вход которого подключен к выходу второго одновибратора, а синхронизирующий к синхронизирующему входу входного элемента, сигнальный вход которого подключен к выходу первого одновибратора, управляющему входу анализатора ошибок и управляющему входу элемента синхронизации. Информационный вход элемента синхронизации подключен к выходу генератора тактовых импульсов и синхронизирующему входу входного элемента. Выход элемента разрешения подключен к входу первого одновибратора. Выход входного элемента подключен к информационному входу анализатора ошибок, сигнальный вход которого подключен к выходу второго одновибратора. Выход анализатора ошибок подключен к информационному входу элемента памяти, синхронизирующий и сигнальный входы которого подключены соответственно к синхронизирующему и сигнальному выходам элемента синхронизации. Управляющий вход элемента памяти подключен к выходу элемента установки начального состояния и управляющему входу коммутатора и управляющему входу формирователя кода. Выход элемента памяти подключен к информационному входу элемента оценки состояния, управляющий вход которого подключен к выходу формирователя порогов оценки качества. Выход элемента оценки состояния подключен к информационному входу коммутатора, сигнальный вход которого подключен к сигнальному входу элемента памяти и входу второго одновибратора. Сигнальный выход элемента установки начального состояния подключен к сигнальному входу формирователя кода, синхронизирующий и сдвигающий входы которого подключены соответственно к синхронизирующему и сдвигающему выходам коммутатора. Установочный вход формирователя кода подключен к выходу формирователя начального кода, причем информационный вход входного элемента и информационный выход формирователя кода являются соответственно входом и выходом блока управления возбудителем.

Благодаря новой совокупности существенных признаков за счет введения на спутниковый ретранслятор коммутатора тестового сигнала и обеспечения на нем поочередной коммутации информационного и тестового сигналов, а на каждую земную станцию спутниковой связи - блока управления возбудителем и блока формирования информационно-тестовых сигналов, обеспечивающих возможность формирования тестового сигнала и его передачу на спутниковый ретранслятор, прием, обработку и формирование управляющего сигнала для возбудителей земных станций спутниковой связи обеспечивается автоматическое определение качества канала спутниковой связи по значению коэффициента ошибок тестовых сигналов, в соответствии с которым формируются управляющие сигналы и производится управление уровнем сигнала возбудителя, чем достигается помехозащищенность линий спутниковой связи.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами:

Фиг.1 - Система спутниковой связи.

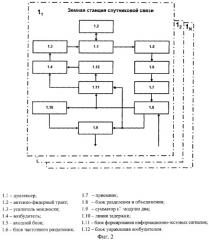

Фиг.2 - Функциональная схема системы спутниковой связи.

Фиг.3 - Функциональная схема коммутатора тестового сигнала.

Фиг.4 - Функциональная схема формирователя сигнала запуска таймера.

Фиг.5 - Функциональная схема блока формирования информационно-тестовых сигналов.

Фиг.6 - Функциональная схема блока управления возбудителем.

Фиг.7 - Функциональная схема элемента разрешения.

Фиг.8 - Функциональная схема входного элемента.

Фиг.9 - Функциональная схема анализатора ошибок.

Фиг.10 - Функциональная схема блока синхронизации.

Фиг.11 - Функциональная схема элемента памяти.

Фиг.12 - Функциональная схема элемента оценки состояния.

Фиг.13 - Функциональная схема формирователя порогов оценки качества.

Фиг.14 - Функциональная схема элемента установки начального состояния.

Фиг.15 - Функциональная схема коммутатора.

Фиг.16 - Функциональная схема формирователя кода.

Фиг.17 - Функциональная схема формирователя начального кода.

Фиг.18 - Эпюры напряжений, функционирования элементов коммутатора тестового сигнала.

Фиг.19 - Эпюры напряжений, функционирования элементов блока формирования информационно-тестовых сигналов.

Система спутниковой связи, показанная на фиг.1, состоит из N>2 земных станций спутниковой связи 1...N и спутникового ретранслятора. Каждая земная станция спутниковой связи 1, показанная на фиг.2., содержит антенно-фидерный тракт 1.2, усилитель мощности 1.3, дуплексер 1.1, входной блок 1.5, возбудитель 1.4, блок частотного разделения 1.6, приемник 1.7, блок разделения и объединения 1.8, сумматор по модулю два 1.9, линию задержки 1.10, блок управления возбудителем 1.12, блок формирования информационно-тестовых сигналов 1.11 и спутниковый ретранслятор 2 с обработкой сигналов на борту, который содержит приемную антенну 2.1, малошумящий усилитель мощности 2.2, смеситель 2.3, N избирательных трактов 2.41...2.4N, N усилителей промежуточной частоты 2.4.11...2.4.1N, N полосовых фильтров 2.4.21...2.4.2N, N демодуляторов 2.4.31...2.4.3N, гетеродин 2.5, коммутатор 2.6, N/2 коммутаторов тестового сигнала 2.71...2.7N/2 и сумматоров по модулю два 2,81...2.8N/2, аппаратуру временного объединения 2.9, модулятор 2.10, усилитель мощности 2.11, передающую антенну 2.12.

При этом в каждой земной станции спутниковой связи 1...N (см. фиг.2) приемо-передающий вход-выход дуплексера 1.1 подключен к антенно-фидерному тракту 1.2. Сигнальный вход дуплексера 1.1 подключен к выходу усилителя мощности 1.3, вход которого подключен к выходу возбудителя 1.4. Сигнальный выход дуплексера подключен к входу входного блока 1.5, выход которого подключен к входу блока частотного разделения 1.6, выход которого подключен к входу приемника 1.7, выход которого подключен к сигнальному входу блока разделения и объединения 1.8. Выход линии задержки 1.10 подключен к информационному входу сумматора по модулю два 1.9, сигнальный вход которого подключен к сигнальному выходу блока разделения и объединения 1.8, а его информационный выход подключен к входу линии задержки 1.10, причем информационный вход блока разделения и объединения 1.8 и выход сумматора по модулю два 1.9 являются соответственно входом и выходом земной станции спутниковой связи 1. В спутниковом ретрансляторе 2 выход приемной антенны 2.1 подключен к входу малошумящего усилителя мощности 2.2, выход которого подключен к сигнальному входу смесителя 2.3. Каждый из N избирательных трактов 2.4 состоит из последовательно включенных усилителя промежуточной частоты 2.4.1, полосового фильтра 2.4.2, демодулятора 2.4.3, причем вход усилителя промежуточной частоты 2.4.1 и выход демодулятора 2.4.3 являются соответственно входом и выходом избирательного тракта 2.4. Входы избирательных трактов 2.4 объединены и подключены к сигнальному выходу смесителя 2.3, гетеродинный вход которого подключен к выходу гетеродина 2.5. Выход i-го избирательного тракта 2.4i, где i=1, 2,...,N, подключен к i-му входу коммутатора 2.6, i-й и (i+1)-й выходы которого, где i-нечетное, подключены соответственно к информационному и сигнальному входам [j=(i+1)/2]-го коммутатора тестового сигнала 2.7j. Выход j-го N/2 сумматора по модулю два 2.8, где j=1, 2,..., N/2, подключен к j-му входу аппаратуры временного объединения 2.9, выход которой подключен к сигнальному входу модулятора 2.10, а гетеродинный вход - к выходу гетеродина. Выход модулятора 2.10 подключен к входу усилителя мощности 2.11, выход которого подключен к входу передающей антенной системы 2.12.

Составляющие части заявляемого устройства являются типовыми и реализованы в действующих системах спутниковой связи, а их описание содержится в следующих источниках информации. Дуплексер 1.1 земной станции спутниковой связи 1 фиг.2 предназначен для развязки по частоте трактов приема и передачи, так как антенно-фидерный тракт является для них общим. В качестве дуплексера может быть использован фильтр разделения приема и передачи, схемы таких фильтров известны и описаны, например, в книге: Г.Б.Аскинази, В.Л.Быков, Г.В.Водопьянов и др. Справочник по спутниковой связи и вещанию. Под ред. Л.Я.Кантора. - М.: Радио и связь, 1983, с.13. рис.1.4. Антенно-фидерный тракт 1.2 фиг.2 предназначен для приема сигналов, излучаемых спутниковым ретранслятором 2 фиг.2. Схемы таких антенно-фидерных трактов известны и описаны в той же книге на с.176-196. Усилитель мощности 1.3 фиг.2 предназначен для усиления до необходимого уровня мощности СВЧ радиосигнала, поступающего от возбудителя 1.4. Схема усилителя мощности известна и описана, например, в книге: В.А.Буковский, В.В.Игнатов, А.П.Родимов и др. Военные системы космической связи. Под ред. А.П.Родимова. - Л.: ВАС, 1984, с.181-183, рис.8.5. Возбудитель 1.4 фиг.2 предназначен для формирования высокочастотных колебаний в диапазоне станции и модуляции групповым сигналом. Схема возбудителя известна и описана в той же книге на с.175-181, рис.8.1. Входной блок 1.5 фиг.2 предназначен для максимально возможного увеличения ее чувствительности. Схемы входных блоков известны и описаны, например, в книге: Справочник по спутниковой связи и вещанию. Под ред. Л.Я.Кантора. - М.: Радио и связь, 1983, с.146-154. Блок частотного разделения 1.6 и приемник 1.7 фиг.2 предназначены для выделения из широкой полосы частот ствола любой узкой полосы, в которой находится сигнал корреспондента, и его усиление, фильтрацию и демодуляцию. Схемы блоков частотного разделения и приемников известны и аналогичны описанным, например, в книге: Справочник по радиорелейной связи. Под. ред. С.В.Бородича. - М.: Радио и связь, 1981, с.115-152. Блок разделения и объединения 1.8 фиг.2 предназначен для объединения индивидуальных абонентских сигналов в единую групповую импульсную последовательность при передаче и разделении групповых сигналов на абонентские при приеме. Схемы таких блоков разделения и объединения известны и описаны, например, в книге: В.А.Буковский, В.В.Игнатов, А.П.Родимов и др. Военные системы космической связи. Под ред. А.П.Родимова. - Л.: ВАС, 1984, с.192-207, рис.9.7., 9.8. Сумматор по модулю два 1.9 фиг.2 предназначен для вычитания из принятого сигнала своего сигнала, задержанного в линии задержки на время распространения сигнала на участках линии земная станция спутниковой связи - спутниковый ретранслятор - земная станция спутниковой связи, и выделения на его выходе только сигнала корреспондента. В качестве сумматора по модулю два может быть использован сумматор, описанный в книге: В.А.Бушуев, В.Н.Вениаминов, В.Г.Ковалев и др. Микросхемы и их применение. - М.: Энергия, 1978, с.178-180. Линия задержки 1.10 фиг.2 предназначена для задержки входного сигнала на время, сопоставимое с временем распространения сигнала на линии земная станция спутниковой связи - спутниковый ретранслятор - земная станция спутниковой связи. Линия задержки может быть реализована путем применения двоично-дискретной линии задержки, описанной в книге: Антенны. Сб. статей. Вып.26. / Под ред. А.А.Пистолькорса. - М.: Связь, 1978, с.120-170.

Блок формирования информационно-тестовых сигналов 1.11, показанный на фиг.5, предназначен для формирования тестовых сигналов на земной станции спутниковой связи 1 фиг.2, включения данных тестовых сигналов в последовательность информационных сигналов в регламентированные временные интервалы и состоит из первого логического элемента НЕ 1.11.1, первого логического элемента И 1.11.2, логического элемента ИЛИ 1.11.3, третьего логического элемента И 1.11.4, четвертого логического элемента И 1.11.5, сумматора по модулю два 1.11.6, первой линии задержки 1.11.7, второй линии задержки 1.11.8, второго логического элемента НЕ 1.11.9, пятого логического элемента И 1.11.10, формирователя тестовой последовательности 1.11.11, одновибратора 1.11.12, таймера 1.11.13.

Выход первого логического элемента НЕ 1.11.1 подключен к второму входу первого логического элемента И 1.11.2, первый вход которого подключен к входу таймера 1.11.13 и является первым входом блока формирования информационно-тестовых сигналов 1.11. Выход первого логического элемента И 1.11.2 подключен к первому входу логического элемента ИЛИ 1.11.3, второй вход которого подключен к выходу третьего логического элемента И 1.11.4. Выход логического элемента ИЛИ 1.11.3 является вторым выходом блока формирования информационно-тестовых сигналов 1.11. Вход первого логического элемента НЕ 1.11.1 подключен к первому входу третьего логического элемента И 1.11.4, входу формирователя тестовой последовательности 1.11.11, выходу одновибратора 1.11.12, второму входу пятого логического элемента И 1.11.10 и входу первой линии задержки 1.11.7. Второй вход третьего логического элемента И 1.11.4 подключен к выходу формирователя тестовой последовательности 1.11.11 и входу второго логического элемента НЕ 1.11.9, выход которого подключен к первому входу пятого логического элемента И 1.11.10, выход которого подключен к входу второй линии задержки 1,11.8, выход которой подключен к второму входу сумматора по модулю два 1.11.6, первый вход которого является вторым входом блока формирования информационно-тестовых сигналов 1.11. Выход таймера 1.11.13 подключен ко входу одновибратора 1.11.12. Выход первой линии задержки 1.11.7 подключен к первому входу четвертого логического элемента И 1.11.5, второй вход которого подключен к выходу сумматора по модулю два 1.11.6, причем выход четвертого логического элемента И 1.11.5 является первым выходом блока формирования информационно-тестовых сигналов 1.11.

Входящие в общую структуру блока формирования информационно-тестовых сигналов 1.11, показанного на фиг.5, элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании современной элементной базы. Сумматор по модулю два 1.11.6 фиг.5 предназначен для выделения сигнала ошибки относительно переданного тестового сигнала и принятого от спутникового ретранслятора 2. фиг.2. В качестве сумматора по модулю два может быть использован сумматор, описанный в книге: В.А.Бушуев, В.Н.Вениаминов, В.Г.Ковалев и др. Микросхемы и их применение. - М.: Энергия, 1978, с.178-180. Первая линия задержки 1.11.7 фиг.5 предназначена для разрешения выделения сигнала ошибки, формируемого в сумматоре по модулю два 1.11.6 фиг.4. Вторая линия задержки 1.11.8 фиг.5 предназначена для синхронизации обработки информационно-тестовых сигналов, переданных земной станцией спутниковой связи 1 и принятых от спутникового ретранслятора 2 фиг.2. Формирователь тестовой последовательности 1.11.11 фиг.5 предназначен для формирования тестовой последовательности. В качестве формирователя тестовой последовательности может быть использован генератор импульсов, описанный в книге: Шелестов И.П. Радиолюбителям: полезные схемы. Кн.2. - М.: Солон, 1998, с.27, рис.1.30.а. Одновибратор 1.11.12 фиг.5 предназначен для формирования единичного импульса длительностью, соответствующей тестовому сигналу в структуре информационно-тестового сигнала. В качестве одновибратора 1.11.12 могут быть использованы ждущие мультивибраторы, которые описаны, например, в книге: В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалева и др. Микросхемы и их применение. - М.: Энергия, 1978, с.193 или В.Л.Шило. Линейные интегральные схемы в радиоэлектронной аппаратуре. - М.: Советское радио, 1979, с.210-214. Таймер 1.11.13 фиг.5 предназначен для формирования импульсов запуска одновибратора 1.1.12 фиг.5 относительно структуры кадра сигнала в моменты времени, соответствующие прохождению тестовой последовательности четных или нечетных циклов. Схемы таких таймеров известны и приведены, например, в книге: А.А.Бокуняев, Н.М. Борисов, Е.Б.Гумеля и др. Справочная книга радиолюбителя-конструктора. Кн.1. / Под ред. Н.И.Чистякова. - М.: Радио и связь, 1993, с.314, рис.8.123. Первая и вторая линии задержки могут быть реализованы путем применения двоично-дискретной линии задержки, описанной в книге: Антенны. Сб. статей. Вып.26. / Под ред. А.А.Пистолькорса. - М.: Связь, 1978, с.120-170. Схемы логических элементов НЕ, И, ИЛИ известны и описаны, например, в книге: А.А.Бокуняев, Н.М.Борисов, Е.Б.Гумеля и др. Справочная книга радиолюбителя-конструктора. Кн.1. / Под ред. Н.И.Чистякова. - М.: Радио и связь, 1993, с.304, рис.8.92.В., рис.8.92.6. и рис.8.92.а. соответственно.

Блок управления возбудителем 1.12, показанный на фиг.6, предназначен для регулировки усиления выходного сигнала возбудителя 1.4 фиг.2 в зависимости от качества информационного канала и состоит из элемента разрешения 1.12.1, генератора тактовых импульсов 1.12.2, первого одновибратора 1.12.3, входного элемента 1.12.4, анализатора ошибок 1.12.5, элемента синхронизации 1.12.6, второго одновибратора 1.12.7, элемента памяти 1.12.8, элемента оценки состояния 1.12.9, формирователя порогов оценки качества 1.12.10, элемента установки начального состояния 1.12.11, коммутатора 1.12.12, формирователя кода 1.12.13, формирователя начального кода 1.12.14.

Управляющий вход элемента разрешения 1.12.1 подключен к выходу второго одновибратора 1.12.7, а синхронизирующий вход - к синхронизирующему входу входного элемента 1.12.4, сигнальный вход которого подключен к выходу первого одновибратора 1.12.3, управляющему входу анализатора ошибок 1.12.5 и управляющему входу элемента синхронизации 1.12.6. Тактовый вход элемента синхронизации 1.12.6 подключен к выходу генератора тактовых импульсов 1.12.2 и тактовому входу входного элемента 1.12.4. Выход элемента разрешения 1.12.1 подключен к входу первого одновибратора 1.12.3. Выход входного элемента 1.12.4 подключен к информационному входу анализатора ошибок 1.12.5, обнуляющий вход которого подключен к выходу второго одновибратора 1.12.7. Выход анализатора ошибок 1.12.5 подключен к информационному входу элемента памяти 1.12.8, тактовый и разрешающий входы которого подключены соответственно к тактовому и разрешающему выходам элемента синхронизации 1.12.6. Управляющий вход элемента памяти 1.12.8 подключен к управляющему выходу элемента установки начального состояния 1.12.11, управляющему входу коммутатора 1.12.12 и управляющему входу формирователя кода 1.12.13. Выход элемента памяти 1.12.8 подключен к информационному входу элемента оценки состояния 1.12.9, установочный вход которого подключен к выходу формирователя порогов оценки качества 1.12.10. Выход элемента оценки состояния 1.12.9 подключен к информационному входу коммутатора 1.12.12, разрешающий вход которого подключен к разрешающему входу элемента памяти 1.12.8 и входу второго одновибратора 1.12.7. Разрешающий выход элемента установки начального состояния 1.12.11 подключен к разрешающему входу формирователя кода 1.12.13, информационный и переключающий входы которого подключены соответственно к информационному и переключающему выходам коммутатора 1.12.12. Установочный вход формирователя кода 1.12.13 подключен к выходу формирователя начального кода 1.12.14, причем информационный вход входного элемента 1.12.4 и выход формирователя кода 1.12.13 являются соответственно входом и выходом блока управления возбудителем 1.12.

Входящие в общую структуру блока управления возбудителем элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании современной элементной базы. Элемент разрешения 1.12.1 (фиг.7) предназначен для запуска первого одновибратора 1.12.3 и может быть реализован на логических элементах И-НЕ, И, описанных, например, в справочнике: Цифровые интегральные микросхемы. - М.: Радио и связь, 1994, с.234-237. Второй вход элемента И 1.12.1.2 является тактовым вводом элемента разрешения 1.12.1. Вход логического элемента И-НЕ 1.12.1.1 является управляющим входом элемента разрешения 1.12.1. Выход логического элемента И-НЕ 1.12.1.1 соединен с первым входом логического элемента И 1.12.1.2, выход которого является выходом элемента разрешения 1.12.1. Генератор тактовых импульсов 1.12.2 обеспечивает синхронную работу всех элементов блока управления возбудителем. Схемы таких генераторов известны и приведены, например, в книге: Справочник по интегральным микросхемам. / Под ред. В.В.Тарабрина. - М.: Энергия, 1980, с.588 рис.5.35, 5.36. Первый одновибратор 1.12.3 предназначен для выставления интервала измерения tизмер (формирования импульса требуемой длительности). В качестве первого одновибратора 1.12.3 могут быть использованы ждущие мультивибраторы, которые описаны, например, в книге: В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалева и др. Микросхемы и их применение. - М.: Энергия, 1978, с.193 или В.Л.Шило. Линейные интегральные схемы в радиоэлектронной аппаратуре. - М.: Советское радио, 1979, с.210-214. Входной элемент 1.12.4 предназначен для выделения информационной последовательности из длительной серии последовательности сигналов одного знака. В частности, он может быть реализован на трехвходовом логическом элементе И (фиг.8). Такие логические элементы известны и описаны, например, в книге: В.Ю.Лавриенко. Справочник по полупроводниковым приборам. - Киев: Техника, 1980, с.399, рис.173. Первый, второй и третий входы логического элемента И являются соответственно управляющим, тактовым и информационным входами входного элемента 1.12.4, а выход логического элемента И является выходом входного элемента 1.12.4. Анализатор ошибок 1.12.5, показанный на фиг.9, предназначен для вычисления kтек (подсчета неправильно принятых бит информационной последовательности). Он может быть реализован на двоичных счетчиках, построенных с использованием цифровых интегральных микросхем, описанных, например, в справочнике: Цифровые интегральные микросхемы. - М.: Радио и связь, 1994, с.68. Соединенные входы V1 и НЕ-V2 двоичного счетчика являются управляющим входом анализатора ошибок 1.12.5. Вход синхронизации С и установочный вход двоичного счетчика соответствуют информационному и обнуляющему входам анализатора ошибок 1.12.5. Q-выходы двоичного счетчика соответствуют выходу анализатора ошибок 1.12.5, который представляет собой четырехразрядную шину. Блок синхронизации 1.12.6, изображенный на фиг.10, предназначен для записи и считывания информации в блок памяти 1.12.8, а также для управления коммутатором 1.12.12. Блок синхронизации может быть реализован на логических элементах И, И-НЕ, описанных, например, в справочнике: Цифровые интегральные микросхемы. - М.: Радио и связь, 1994, с.234-237. Первый вход логического элемента И 1.12.6.1, соединенный с входом логического элемента И-НЕ 1.12.6.2, является управляющим входом элемента синхронизации 1.12.6. Второй вход логического элемента И 1.12.6.1 является тактовым входом элемента синхронизации 1.12.6. Выходы логических элементов И 1.12.6.1 и И-НЕ 1.12.6.2 являются соответственно первым и вторым выходами элемента синхронизации 1.12.6. Второй одновибратор 1.12.7 предназначен для формирования сигналов длительностью, соответствующей времени регулирования мощности передачи. В качестве первого и второго одновибраторов могут быть использованы ждущие мультивибраторы, описанные, например, в книге: В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалева и др. Микросхемы и их применение. - М.: Энергия, 1978, с.193 или В.Л.Шило. Линейные интегральные схемы в радиоэлектронной аппаратуре. - М.: Советское радио, 1979, с.210-214. Элемент памяти 1.12.8 предназначен для хранения результатов вычисления анализатора ошибок 1.12.5 на время регулирования уровня выходного сигнала возбудителя 1.4 фиг.2 на каждом интервале измерения tизмер. В частности, он может быть реализован на регистре сдвига 1.12.8.1 и четырех логических элементах И 1.12.8.2-1.12.8.5 (фиг.11). Схемы таких регистров известны и описаны, например, в справочнике: Цифровые интегральные микросхемы. - М.: Радио и связь, 1994, с.62, рис.2.49.а. Схемы логических элементов И 1.12.8.2-1.12.8.5 также известны и описаны, например, в справочнике: Цифровые интегральные микросхемы. - М.: Радио и связь. 1994, с.234-237. Вторые входы логических элементов И 1.12.8.2-1.12.8.5 соединены и являются разрешающим входом элемента памяти 1.12.8. Вход синхронизации С и информационные входы D1-D4 регистра сдвига 1.12.8.1 являются соответственно тактовым и информационным входами элемента памяти 1.12.8. Установочный вход регистра сдвига 1.12.8.1 является управляющим входом элемента памяти 1.12.8. Выходы Q1-Q4 регистра сдвига 1.12.8.1 соответственно соединены с первыми входами логических элементов И 1.12.8.2-1.12.8.5, выходы которых являются выходом элемента памяти 1.12.8. Информационный вход и выход элемента памяти 1.12.8 представляют собой четырехраз