Устройство для измерения характеристик случайных процессов

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и может быть использовано для контроля характеристик случайных процессов. Техническим результатом является повышение точности определения вида закона распределения случайных величин. Устройство содержит дешифраторы, индикатор, элементы И-НЕ, нормирующий усилитель, двойной квадратичный детектор, интеграторы, делители, детекторы, умножители, элемент ИЛИ-НЕ, блоки извлечения квадратного корня, элементы И, компараторы, ключи, коммутаторы, мультиплексоры, регистры, амплитудные селекторы, генератор ступенчатого напряжения, вычитающее устройство, логарифмический усилитель и блок вычисления экспоненциальной функции. 2 табл., 4 ил.

Реферат

Изобретение относится к области радиоизмерений и может быть использовано для контроля характеристик случайных процессов.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для измерения характеристик случайных процессов [1], выбранное в качестве прототипа. Известное устройство содержит первый дешифратор, индикатор, нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор и первый интегратор подключен к первому входу первого делителя, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя, при этом последовательно соединенные первый умножитель, третий интегратор и второй делитель, выход которого подключен одновременно к первым входам первого и второго компараторов, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, выход которого подключен к объединенным вторым входам первого и второго ключей, при этом первый вход второго умножителя непосредственно, а второй вход через первый блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен к второму входу второго делителя, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключены к выходу нормирующего усилителя, при этом выход третьего делителя подключен к первому входу первого ключа, выход которого подключен одновременно к первым входам пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, при этом выход второго ключа подключен к объединенным первым входам третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, выходы первого, второго, третьего, четвертого, пятого, шестого и седьмого элементов И-НЕ соответственно подключены к первому, второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора, восьмой, девятый, десятый и одиннадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами коммутатора, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого и второго мультиплексоров, при этом второй вход второго дешифратора одновременно соединен с входной шиной и объединенными десятыми входами первого и второго мультиплексоров, а объединенные девятые и объединенные десятые входы первого и второго регистров соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, при этом третий, седьмой, четвертый и восьмой выходы первого регистра подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, а первый, пятый, второй и шестой выходы второго регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора, второй выход первого дешифратора одновременно подключен к первым входам первого и второго элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора, десятый выход которого подключен к второму входу четвертого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами третьего и второго элементов И-НЕ и двенадцатым выходом первого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ, третьему входу третьего элемента И-НЕ и второму входу второго элемента И-НЕ, при этом первый выход первого дешифратора подключен к четвертому входу седьмого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ и пятнадцатым выходом первого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И и третьего элемента И-НЕ, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ и третьим выходом первого дешифратора, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И и первого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И и первым входом третьего элемента И, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ и первому входу пятого элемента И-НЕ, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ и четвертым выходом первого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам пятого и второго элементов И-НЕ, при этом седьмой выход первого дешифратора подключен к третьему входу второго элемента И-НЕ, а девятый выход подключен к третьему входу пятого элемента И-НЕ, выход второго элемента И одновременно подключен к второму входу третьего элемента И, первому входу седьмого элемента И-НЕ и объединенным четвертому и третьему входам шестого элемента И-НЕ, а выход четвертого элемента И подключен к третьему входу четвертого элемента И-НЕ, при этом вход второго блока извлечения квадратного корня соединен с выходом первого делителя, а выход подключен к первому входу третьего делителя, второй вход которого соединен с входной шиной, первые входы первого и второго амплитудных селекторов одновременно соединены с выходом нормирующего усилителя, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения, вход которого соединен с входной шиной, при этом выходы первого и второго амплитудных селекторов подключены соответственно к первому и второму входам вычитающего устройства, выход которого подключен к входу четвертого интегратора, выход которого одновременно подключен к входу логарифмического усилителя и второму входу третьего умножителя, первый вход которого соединен с выходом логарифмического усилителя, а выход подключен к входу пятого интегратора, выход которого подключен к входу блока вычисления экспоненциальной функции, выход которого подключен к первому входу четвертого делителя, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя, второй вход которого соединен с выходом первого блока извлечения квадратного корня, а выход подключен к первому входу второго ключа.

Недостатком известного устройства является низкая точность определения вида закона распределения у классов трапецеидальных, арксинусоидальных и экспоненциальных двухсторонних распределений.

Технический результат от использования предлагаемого устройства заключается в повышении точности определения вида закона распределения у классов трапецеидальных, арксинусоидальных и экспоненциальных двухсторонних распределений за счет уменьшения неопределенности границ (параметров) определяемых распределений.

Сущность изобретения заключается в том, что в устройство для измерения характеристик случайных процессов, содержащее так же, как прототип, первый дешифратор, индикатор, нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор и первый интегратор подключен к первому входу первого делителя, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя, при этом последовательно соединенные первый умножитель, третий интегратор и второй делитель, выход которого подключен одновременно к первым входам первого и второго компараторов, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, выход которого подключен к объединенным вторым входам первого и второго ключей, при этом первый вход второго умножителя непосредственно, а второй вход через первый блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен к второму входу второго делителя, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключены к выходу нормирующего усилителя, при этом выход третьего делителя подключен к первому входу первого ключа, выход которого подключен одновременно к первым входам пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, выход второго ключа подключен к объединенным первым входам третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, выходы первого, второго, третьего, четвертого, пятого, шестого и седьмого элементов И-НЕ соответственно подключены к первому, второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора, восьмой, девятый, десятый и одиннадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами первого коммутатора, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого и второго мультиплексоров, при этом второй вход второго дешифратора одновременно соединен с входной шиной и объединенными десятыми входами первого и второго мультиплексоров, а объединенные девятые и объединенные десятые входы первого и второго регистров соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, при этом третий, седьмой, четвертый и восьмой выходы первого регистра подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, а первый, пятый, второй и шестой выходы второго регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора, второй выход первого дешифратора одновременно подключен к первым входам первого и второго элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора, десятый выход которого подключен к второму входу четвертого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами третьего и второго элементов И-НЕ и двенадцатым выходом первого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ, третьему входу третьего элемента И-НЕ и второму входу второго элемента И-НЕ, при этом первый выход первого дешифратора подключен к четвертому входу седьмого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ и пятнадцатым выходом первого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И и третьего элемента И-НЕ, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ и третьим выходом первого дешифратора, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И и первого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И и первым входом третьего элемента И, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ и первому входу пятого элемента И-НЕ, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ и четвертым выходом первого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам пятого и второго элементов И-НЕ, при этом седьмой выход первого дешифратора подключен к третьему входу второго элемента И-НЕ, а девятый выход подключен к третьему входу пятого элемента И-НЕ, выход второго элемента И одновременно подключен к второму входу третьего элемента И, первому входу седьмого элемента И-НЕ и объединенным четвертому и третьему входам шестого элемента И-НЕ, а выход четвертого элемента И подключен к третьему входу четвертого элемента И-НЕ, при этом вход второго блока извлечения квадратного корня соединен с выходом первого делителя, а выход подключен к первому входу третьего делителя, второй вход которого соединен с входной шиной, первые входы первого и второго амплитудных селекторов одновременно соединены с выходом нормирующего усилителя, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения, вход которого соединен с входной шиной, при этом выходы первого и второго амплитудных селекторов подключены соответственно к первому и второму входам вычитающего устройства, выход которого подключен к входу четвертого интегратора, выход которого одновременно подключен к входу логарифмического усилителя и второму входу третьего умножителя, первый вход которого соединен с выходом логарифмического усилителя, а выход подключен к входу пятого интегратора, выход которого подключен к входу блока вычисления экспоненциальной функции, выход которого подключен к первому входу четвертого делителя, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя, второй вход которого соединен с выходом первого блока извлечения квадратного корня, а выход подключен к первому входу второго ключа, в отличие от прототипа, дополнительно введены девятнадцатый, двадцатый, двадцать первый, двадцать второй, двадцать третий, двадцать четвертый, двадцать пятый и двадцать шестой компараторы, вторые входы которых соединены соответственно с входными шинами, а объединенные первые входы соединены с выходом первого ключа, при этом выход второго ключа одновременно подключен к первым входам двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого, тридцать первого, тридцать второго, тридцать третьего и тридцать четвертого компараторов, вторые входы, которых соединены соответственно с входными шинами, при этом введены восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый элементы И-НЕ, выходы которых соответственно подключены к шестнадцатому, семнадцатому, восемнадцатому, девятнадцатому, двадцатому, двадцать первому и двадцать второму входам индикатора, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами второго коммутатора, пятый вход которого соединен с пятым входом первого коммутатора, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами третьего дешифратора, первый вход которого одновременно соединен с объединенными девятыми входами первого, второго, третьего и четвертого мультиплексоров, при этом второй вход третьего дешифратора одновременно соединен с объединенными десятыми входами первого, второго, третьего и четвертого мультиплексоров, а объединенные девятые и объединенные десятые входы третьего и четвертого регистров соединены соответственно с объединенными девятыми и объединенными десятыми входами первого и второго регистров, первый, второй, пятый и шестой входы третьего мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами третьего регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами девятнадцатого, двадцатого, двадцать первого, двадцать второго, двадцать третьего, двадцать четвертого, двадцать пятого и двадцать шестого компараторов, при этом третий, седьмой, четвертый и восьмой выходы третьего регистра подключены соответственно к первому, второму, пятому и шестому входам четвертого мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами четвертого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого, тридцать первого, тридцать второго, тридцать третьего и тридцать четвертого компараторов, а первый, пятый, второй и шестой выходы четвертого регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам третьего мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам четвертого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами четвертого мультиплексора, второй выход четвертого дешифратора одновременно подключен к первым входам пятого и шестого элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами четвертого дешифратора, десятый выход которого подключен к второму входу одиннадцатого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами десятого и девятого элементов И-НЕ и двенадцатым выходом четвертого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу четырнадцатого элемента И-НЕ, третьему входу десятого элемента И-НЕ и второму входу девятого элемента И-НЕ, при этом первый выход четвертого дешифратора подключен к четвертому входу четырнадцатого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом восьмого элемента И-НЕ и пятнадцатым выходом четвертого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам восьмого элемента И и десятого элемента И-НЕ, четвертый вход которого одновременно соединен с вторым входом тринадцатого элемента И-НЕ и третьим выходом четвертого дешифратора, тринадцатый выход которого одновременно подключен к первым входам восьмого элемента И и восьмого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом пятого элемента И и первым входом седьмого элемента И, выход которого одновременно подключен к четвертому входу одиннадцатого элемента И-НЕ и первому входу двенадцатого элемента И-НЕ, второй вход которого одновременно соединен с первым входом тринадцатого элемента И-НЕ и четвертым выходом четвертого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам двенадцатого и девятого элементов И-НЕ, при этом седьмой выход четвертого дешифратора подключен к третьему входу девятого элемента И-НЕ, а девятый выход подключен к третьему входу двенадцатого элемента И-НЕ, выход шестого элемента И одновременно подключен к второму входу седьмого элемента И, первому входу четырнадцатого элемента И-НЕ и объединенным четвертому и третьему входам тринадцатого элемента И-НЕ, а выход восьмого элемента И подключен к третьему входу одиннадцатого элемента И-НЕ.

Сущность изобретения поясняется чертежами и таблицами, где

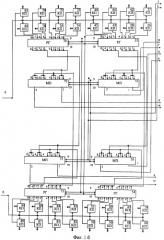

на фиг.1а, б, в представлена структурная электрическая схема устройства,

на фиг.2 приведены графики и числовые характеристики (параметры) законов распределения случайных величин,

на фиг.3а, б, в, г приведены временные диаграммы, поясняющие принцип формирования импульсов единичной амплитуды на выходе вычитающего устройства и плотности распределения вероятности,

на фиг.4 приведена электрическая схема коммутатора,

в табл.1 приведен порядок считывания содержимого регистров, через мультиплексоры на дешифраторы,

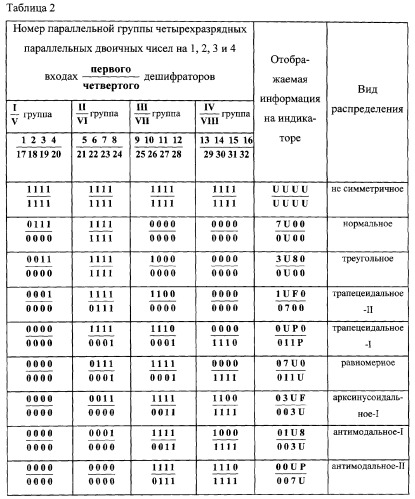

в табл.2 приведена информация о виде закона распределения в нестандартном шестнадцатиричном коде.

Предлагаемое устройство (см. фиг.1) содержит так же, как и прототип, нормирующий усилитель (НУ) 1, двойной квадратичный детектор (ДКД) 2, первый детектор (Д) 3, второй детектор (Д) 4, второй интегратор (ИГ) 5, первый интегратор (ИГ) 6, первый делитель (ДЛ) 7, второй блок извлечения квадратного корня (БИКК) 8, индикатор (ИД) 9, входную шину 10, третий детектор (Д) 11, первый умножитель (УМ) 12, третий интегратор (ИГ) 13, второй делитель (ДЛ) 14, первый блок извлечения квадратного корня (БИКК) 15, второй умножитель (УМ) 16, первый компаратор (КП) 17, второй компаратор (КП) 18, третий компаратор (КП) 19, четвертый компаратор (КП) 20, элемент ИЛИ-НЕ 21, второй дешифратор (ДШ) 22, первый элемент И-НЕ 23, первый ключ (КЛ) 24, третий делитель (ДЛ) 25, пятый компаратор (КП) 26, шестой компаратор (КП) 27, седьмой компаратор (КП) 28, первый дешифратор (ДШ) 29, первый амплитудный селектор (АС) 30, генератор ступенчатого напряжения (ГСН) 31, второй амплитудный селектор (АС) 32, вычитающее устройство (ВУ) 33, четвертый интегратор (ИГ) 34, логарифмический усилитель (ЛУ) 35, третий умножитель (УМ) 36, пятый интегратор (ИГ) 37, блок вычисления экспоненциальной функции (БВЭФ) 38, четвертый делитель (ДЛ) 39, пятый делитель (ДЛ) 40, второй ключ (КЛ) 41, восьмой компаратор (КП) 42, девятый компаратор (КП) 43, десятый компаратор (КП) 44, одиннадцатый компаратор (КП) 45, двенадцатый компаратор (КП) 46, тринадцатый компаратор (КП) 47, четырнадцатый компаратор (КП) 48, пятнадцатый компаратор (КП) 49, шестнадцатый компаратор (КП) 50, семнадцатый компаратор (КП) 51, восемнадцатый компаратор (КП) 52, первый регистр (РГ) 53, второй регистр (РГ) 54, первый мультиплексор (МП) 55, второй мультиплексор (МП) 56, первый элемент И 57, второй элемент И 58, третий элемент И (И) 59, четвертый элемент И 60, второй элемент И-НЕ 61, третий элемент И-НЕ 62, четвертый элемент И-НЕ 63, пятый элемент И-НЕ 64, шестой элемент И-НЕ 65, седьмой элемент И-НЕ 66 и первый коммутатор (КМ) 67.

В отличие от прототипа в устройство дополнительно введены второй коммутатор (КМ) 68, третий дешифратор (ДШ) 69, третий регистр (РГ) 70, четвертый регистр (РГ) 71, третий мультиплексор (МП) 72, четвертый мультиплексор (МП) 73, девятнадцатый компаратор (КП) 74, двадцатый компаратор (КП) 75, двадцать первый компаратор (КП) 76, двадцать второй компаратор (КП) 77, двадцать третий компаратор (КП) 78, двадцать четвертый компаратор (КП) 79, двадцать пятый компаратор (КП) 80, двадцать шестой компаратор (КП) 81, двадцать седьмой компаратор (КП) 82, двадцать восьмой компаратор (КП) 83, двадцать девятый компаратор (КП) 84, тридцатый компаратор (КП) 85, тридцать первый компаратор (КП) 86, тридцать второй компаратор (КП) 87, тридцать третий компаратор (КП) 88, тридцать четвертый компаратор (КП) 89, пятый элемент И 90, шестой элемент И (И) 91, седьмой элемент И 92, восьмой элемент И 93, восьмой элемент И-НЕ 94, девятый элемент И-НЕ 95, десятый элемент И-НЕ 96, одиннадцатый элемент И-НЕ 97, двенадцатый элемент И-НЕ 98, тринадцатый элемент И-НЕ 99, четырнадцатый элемент И-НЕ 100 и четвертый дешифратор (ДШ) 101.

Вход нормирующего усилителя 1 соединен с входной шиной 10, а выход через последовательно соединенные двойной квадратичный детектор 2 и первый интегратор 6 подключен к первому входу первого делителя 7, при этом выход нормирующего усилителя 1 через последовательно соединенные первый детектор 3, второй интегратор 5 и второй детектор 4 подключен также к второму входу первого делителя 7, при этом последовательно соединенные первый умножитель 12, третий интегратор 13 и второй делитель 14, выход которого подключен одновременно к первым входам первого компаратора 17 и второго компаратора 18, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к первому и второму входам элемента ИЛИ-НЕ 21, выход которого подключен к объединенным вторым входам первого ключа 24 и второго ключа 41, при этом первый вход второго умножителя 16 непосредственно, а второй вход через первый блок извлечения квадратного корня 15 подключены к выходу второго интегратора 5, выход второго умножителя 16 подключен к второму входу второго делителя 14, при этом первый вход первого умножителя 12 непосредственно, а второй через третий детектор 11 подключены к выходу нормирующего усилителя 1, при этом выход третьего делителя 25 подключен к первому входу первого ключа 24, выход которого подключен одновременно к первым входам пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46, вторые входы которых соединены соответственно с входными шинами, выход второго ключа 41 подключен к объединенным первым входам третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52, вторые входы которых соединены соответственно с входными шинами, выходы первого элемента И-НЕ 23, второго элемента И-НЕ 61, третьего элемента И-НЕ 62, четвертого элемента И-НЕ 63, пятого элемента И-НЕ 64, шестого элемента И-НЕ 65 и седьмого элемента И-НЕ 66 соответственно подключены к первому, второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора 9, восьмой, девятый, десятый и одиннадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами первого коммутатора 67, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора 22, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого мультиплексора 55 и второго мультиплексора 56, при этом второй вход второго дешифратора 22 одновременно соединен с входной шиной и объединенными десятыми входами первого мультиплексора 55 и второго мультиплексора 56, а объединенные девятые и объединенные десятые входы первого регистра 53 и второго регистра 54 соединены соответственно с входными шинами первый, второй, пятый и шестой входы первого мультиплексора 55 соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра 53, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46, при этом третий, седьмой, четвертый и восьмой выходы первого регистра 53 подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора 56, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра 54, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52, а первый, пятый, второй и шестой выходы второго регистра 54 подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора 55, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора 29, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора 56, второй выход первого дешифратора 29 одновременно подключен к первым входам первого элемента И 57 и второго элемента И 58, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора 29, десятый выход которого подключен к второму входу четвертого элемента И-НЕ 63, первый вход которого одновременно соединен с первыми входами третьего элемента И-НЕ 62 и второго элемента И-НЕ 61 и двенадцатым выходом первого дешифратора 29, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ 66, третьему входу третьего элемента И-НЕ 62 и второму входу второго элемента И-НЕ 61, при этом первый выход первого дешифратора 29 подключен к четвертому входу седьмого элемента И-НЕ 66, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ 23 и пятнадцатым выходом первого дешифратора 29, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И 60 и третьего элемента И-НЕ 62, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ 65 и третьим выходом первого дешифратора 29, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И 60 и первого элемента И-НЕ 23, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И 57 и первым входом третьего элемента И 59, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ 63 и первому входу пятого элемента И-НЕ 64, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ 65 и четвертым выходом первого дешифратора 29, шестой выход которого одновременно подключен к объединенным четвертым входам пятого элемента И-НЕ 64 и второго элемента И-НЕ 61, при этом седьмой выход первого дешифратора 29 подключен к третьему входу второго элемента И-НЕ 61, а девятый выход подключен к третьему входу пятого элемента И-НЕ 64, выход второго элемента И 58 одновременно подключен к второму входу третьего элемента И 59, первому входу седьмого элемента И-НЕ 66 и объединенным четвертому и третьему входам шестого элемента И-НЕ 65, а выход четвертого элемента И 60 подключен к третьему входу четвертого элемента И-НЕ 63, при этом вход второго блока извлечения квадратного корня 8 соединен с выходом первого делителя 7, а выход подключен к первому входу третьего делителя 25, второй вход которого соединен с входной шиной, первые входы первого амплитудного селектора 30 и второго амплитудного селектора 32 одновременно соединены с выходом нормирующего усилителя 1, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения 31, вход которого соединен с входной шиной, при этом выходы первого амплитудного селектора 30 и второго амплитудного селектора 32 подключены соответственно к первому и второму входам вычитающего устройства 33, выход которого подключен к входу четвертого интегратора 34, выход которого одновременно подключен к входу логарифмического усилителя 35 и второму входу третьего умножителя 36, первый вход которого соединен с выходом логарифмического усилителя 35, а выход подключен к входу пятого интегратора 37, выход которого подключен к входу блока вычисления экспоненциальной функции 38, выход которого подключен к первому входу четвертого делителя 39, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя 40, второй вход которого соединен с выходом первого блока извлечения квадратного корня 15, а выход подключен к первому входу второго ключа 41, вторые входы девятнадцатого компаратора 74, двадцатого компаратора 75, двадцать первого компаратора 76, двадцать второго компаратора 77, двадцать третьего компаратора 78, двадцать четвертого компаратора 79, двадцать пятого компаратора 80 и двадцать шестого компаратора 81 соединены соответственно с входными шинами, а объединенные первые входы соединены с выходом первого ключа 24, выход второго ключа 41 одновременно подключен к первым входам двадцать седьмого компаратора 82, двадцать восьмого компаратора 83, двадцать девятого компаратора 84, тридцатого компаратора 85, тридцать первого компаратора 86, тридцать второго компаратора 87, тридцать третьего компаратора 88 и тридцать четвертого компаратора 89, вторые входы которых соединены соответственно с входными шинами, выходы восьмого элемента И-НЕ 94, девятого элемента И-НЕ 95, десятого элемента И-НЕ 96, одиннадцатого элемента И-НЕ 97, двенадцатого элемента И-НЕ 98, тринадцатого элемента И-НЕ 99 и четырнадцатого элемента И-НЕ 100 соответственно подключены к шестнадцатому, семнадцатому, восемнадцатому, девятнадцатому, двадцатому, двадцать первому и двадцать второму входам индикатора 9, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами второго коммутатора 68, пятый вход которого соединен с пятым входом первого коммутатора 67, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами третьего дешифратора 69, первый вход которого одновременно соединен с объединенными девятыми входами первого мультиплексора 55, второго мультиплексора 56, третьего мультиплексора 72 и четвертого мультиплексора 73, второй вход третьего дешифратора 69 одновременно соединен с объединенными десятыми входами первого мультиплексора 55, второго мультиплексора 56, третьего мультиплексора 72 и четвертого мультиплексора 73, а объединенные девятые и объединенные десятые входы третьего регистра 70 и четвертого регистра 71 соединены соответственно с объединенными девятыми и объединенными десятыми входами первого регистра 53 и второго регистра 54, первый, второй, пятый и шестой входы третьего мультиплексора 72 соединены соответственно с первым, пятым, вторым и шестым выходами третьего регистра 70, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами девятнадцатого компаратора 74, двадцатого компаратора 75, двадцать первого компаратора 76, двадцать второго компаратора 77, двадцать третьего компаратора 78, двадцать четвертого компаратора 79, двадцать пятого компаратора 80 и двадцать шестого компаратора 81, третий, седьмой, четвертый и восьмой выходы третьего регистра 70 подключены соответственно к первому, второму, пятому и шестому входам четвертого мультиплексора 73, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами четвертого регистра 71, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами двадцать седьмого компаратора 82, двадцать восьмого компаратор