Операционный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления широкополосных и импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения. Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения до 10000-160000 В/мкс с использованием микронных технологий. Операционный усилитель содержит входной дифференциальный каскад (ДК) (1) на транзисторах (Т) (2, 3) с первым (4) источником опорного тока (ИОТ), входной ДК (5) на Т (6, 7) с вторым (8) ИОТ, причем основные входы (9, 10) ДК (1) соединены с основными входами (11, 12) ДК (5), промежуточный двухтактный каскад на промежуточных усилителях (ПУ) (13, 15), инвертирующие входы которых соединены соответственно с коллекторами Т (2, 6), выходы (17, 20) ПУ (13, 15) связаны по переменному току с входом (18) выходного каскада (ВК) (19), а также корректирующим конденсатором (21). Выход (22) ВК (19) связан по переменному току через первый (25) и второй (26) резисторы соответственно с эмиттерами Т (2, 3) и эмиттерами Т (6, 7). 6 з.п. ф-лы, 19 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения.

Известны операционные усилители (ОУ) на базе двух параллельно включенных параллельно-балансных каскадов [1-17], которые стали основой построения современных операционных усилителей, например AD8631, НА2539, НА5190 и др. [1, 2, 3]. Однако они имеют недостаточно высокое быстродействие из-за нелинейных режимов работы при большом импульсном сигнале [4, 5]. Проблема повышения быстродействия ОУ данного класса, относящихся к числу наиболее широкополосных двухтактных структур, является одной из актуальных проблем современной аналоговой микросхемотехники [6-17].

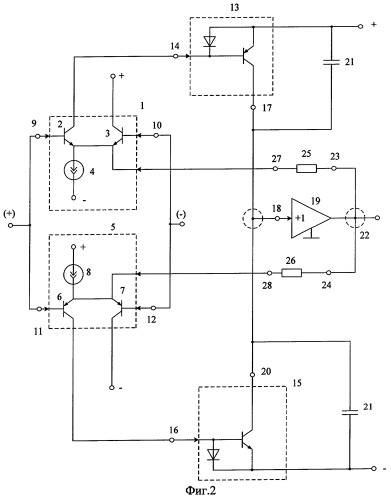

Ближайшим прототипом заявляемого устройства является операционный усилитель [Патент США №5291149 «Операционный усилитель», H 03 f 3/48 - прототип] (фиг.1), содержащий входной дифференциальный каскад 1 на первом 2 и втором 3 входных n-p-n транзисторах, эмиттеры которых связаны с первым 4 источником опорного тока, входной дифференциальный каскад 5 на первом 6 и втором 7 входных p-n-p транзисторах, эмиттеры которых связаны с вторым 8 источником опорного тока, причем основные входы 9, 10 входного дифференциального каскада на n-p-n транзисторах соединены с основными входами 11, 12 входного дифференциального каскада 5 на p-n-p транзисторах, промежуточный двухтактный каскад, содержащий первый промежуточный усилитель 13, инвертирующий вход которого 14 соединен с коллектором первого входного n-p-n транзистора. 2 входного дифференциального каскада 1 на n-p-n транзисторах, второй промежуточный усилитель 15, инвертирующий вход которого 16 соединен с коллектором первого входного p-n-p транзистора 6 дифференциального каскада 5 на p-n-p транзисторах, причем выход 17 первого промежуточного усилителя 13 связан по переменному току с входом 18 выходного каскада 19 и выходом 20 второго промежуточного усилителя 15, а также корректирующим конденсатором 21.

Существенный недостаток известного ОУ состоит в том, что его архитектура не позволяет исключить нелинейные режимы и тем самым получить предельные значения максимальной скорости нарастания выходного напряжения (ϑвых) для большого сигнала.

Основная цель предполагаемого изобретения состоит в повышении быстродействия - получении ϑвых на уровне 4000÷6000 В/мкс с использованием отечественных микронных технологий (с топологическими нормами ≥1,5÷2 мкм).

Поставленная цель достигается тем, что в операционный усилитель (фиг.1), содержащий входной дифференциальный каскад 1 на первом 2 и втором 3 входных n-p-n транзисторах, эмиттеры которых связаны с первым 4 источником опорного тока, входной дифференциальный каскад 5 на первом 6 и втором 7 входных p-n-p транзисторах, эмиттеры которых связаны с вторым 8 источником опорного тока, причем основные входы 9, 10 входного дифференциального каскада на n-p-n транзисторах соединены с основными входами 11, 12 входного дифференциального каскада 5 на p-n-p транзисторах, промежуточный двухтактный каскад, содержащий первый промежуточный усилитель 13, инвертирующий вход которого 14 соединен с коллектором первого входного n-p-n транзистора 2 входного дифференциального каскада 1 на n-p-n транзисторах, второй промежуточный усилитель 15, инвертирующий вход которого 16 соединен с коллектором первого входного p-n-p транзистора 6 дифференциального каскада 5 на p-n-p транзисторах, причем выход 17 первого промежуточного усилителя 13 связан по переменному току с входом 18 выходного каскада 19 и выходом 20 второго промежуточного усилителя 15, а также корректирующим конденсатором 21, вводятся новые элементы и связи между ними - выход выходного каскада связан по переменному току с первыми выводами и первого и второго дополнительных резисторов, вторые выводы которых и подключены соответственно к эмиттерам первого входного n-p-n транзистора входного дифференциального каскада на n-p-n транзисторах и эмиттеру первого и второго входного p-n-p транзистора входного дифференциального каскада на p-n-p транзисторах.

Схема устройства-прототипа приведена на фиг.1.

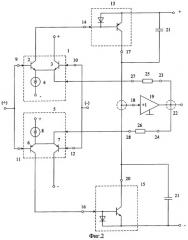

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

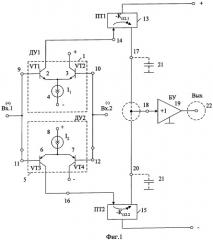

На фиг.3 показана схема ОУ, соответствующая п.2 формулы изобретения.

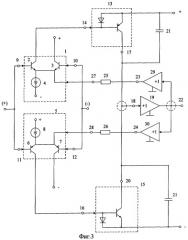

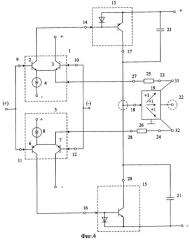

На фиг.4, фиг.5, фиг.6, фиг.7, фиг.8 приведены схемы ОУ, соответствующие п.3, п.4, п.5, п.6, п.7 формулы изобретения.

На фиг.9 показан пример построения ОУ фиг.3, в котором первая (29) и вторая (30) цепи смещения статического управления реализованы на основе транзисторов VT4 VT4, источниках тока I3, I4 и диодах VDN1, VDN2.

На фиг.10-19 показаны варианты построения выходной подсхемы заявляемого ОУ в соответствии с п.3 формулы изобретения (фиг.4).

Операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 на первом 2 и втором 3 входных n-p-n транзисторах, эмиттеры которых связаны с первым 4 источником опорного тока, входной дифференциальный каскад 5 на первом 6 и втором 7 входных p-n-p транзисторах, эмиттеры которых связаны с вторым 8 источником опорного тока, причем основные входы 9, 10 входного дифференциального каскада на n-p-n транзисторах соединены с основными входами 11, 12 входного дифференциального каскада 5 на p-n-p транзисторах, промежуточный двухтактный каскад, содержащий первый промежуточный усилитель 13, инвертирующий вход которого 14 соединен с коллектором первого входного n-p-n транзистора 2 входного дифференциального каскада 1 на n-p-n транзисторах, второй промежуточный усилитель 15, инвертирующий вход которого 16 соединен с коллектором первого входного p-n-p транзистора 6 дифференциального каскада 5 на p-n-p транзисторах, причем выход 17 первого промежуточного усилителя 13 связан по переменному току с входом 18 выходного каскада 19 и выходом 20 второго промежуточного усилителя 15, а также корректирующим конденсатором 21, выход 22 выходного каскада 19 связан по переменному току с первыми выводами 23 и 24 первого 25 и второго 26 дополнительных резисторов, вторые выводы которых 27 и 28 подключены соответственно к эмиттерам первого 2 и второго 3 входных n-p-n транзисторов входного дифференциального каскада 1 на n-p-n транзисторах и к эмиттерам первого 6 и второго 7 входных p-n-p транзисторов входного дифференциального каскада 5 на p-n-p транзисторах.

В схеме фиг.3 по п.2 формулы изобретения выход 22 выходного каскада 19 связан с первыми выводами 23 и 24 первого 25 и второго 26 дополнительных резисторов через первую 29 и вторую 30 цепи смещения статического уровня.

На фиг.4, соответствующей п.3 формулы изобретения, выходной каскад 19, кроме основного выхода 22, имеет два синфазных основному выходу 22 вспомогательных выхода 31 и 32, статические уровни которых смещены на +/-Uэб.р≈+/-0.7В относительно статического уровня основного выхода 22, причем вспомогательные выходы 31 и 32 связаны с первыми выводами 23 и 24 дополнительных резисторов 25 и 26.

В схеме фиг.5 по п.4 формулы изобретения эмиттеры первого 2 и второго 3 входных n-p-n транзисторов входного дифференциального каскада на n-p-n транзисторах 1 связаны с вторым выводом 27 первого дополнительного резистора 25 через эмиттерно-базовый переход вспомогательного n-p-n транзистора 33, коллектор которого соединен с инвертирующим входом 14 первого промежуточного усилителя тока 13, а эмиттеры первого 6 и второго 7 входных p-n-p транзисторов входного дифференциального каскада на p-n-p транзисторах связаны с вторым 28 выводом второго дополнительного резистора 26 через эмиттерно-базовый переход второго вспомогательного p-n-p транзистора 34, коллектор которого подключен к инвертирующему входу 16 второго промежуточного усилителя 15.

В схеме фиг.6 по п.5 формулы изобретения вход 9 входного дифференциального каскада на n-p-n транзисторах 1 связан по переменному току с выходом 22 выходного каскада 19 через эмиттерно-базовый переход первого 35 дополнительного n-p-n транзистора и первый вспомогательный резистор 36, причем коллектор первого дополнительного n-p-n транзистора 35 соединен с инвертирующим входом 14 первого промежуточного усилителя тока 13, а вход 11 входного дифференциального каскада на p-n-p транзисторах 5 связан по переменному току с выходом 22 выходного каскада 19 через эмиттерно-базовый переход второго дополнительного p-n-p транзистора 37 и второй вспомогательный резистор 38, причем коллектор второго дополнительного n-p-n транзистора 37 соединен с инвертирующим входом 16 второго промежуточного усилителя тока 15.

В схеме фиг.7 по п.6 формулы изобретения выход 22 выходного каскада 19 связан с первыми выводами 23 и 24 дополнительных резисторов 25, 26 через четырехполюсник токовой отрицательной обратной связи 39.

В схеме фиг.8 по п.7 формулы изобретения выход 22 выходного каскада 19 связан с первыми выводами 23 и 24 первого 25 и второго 26 дополнительных резисторов через последовательно соединенные четырехполюсник обратной связи 39, первую 29 и вторую 30 цепи смещения статического уровня.

Рассмотрим работу операционного усилителя - прототипа (фиг.1) в режиме повторителя импульсного сигнала со 100% отрицательной обратной связью, когда его инвертирующий вход Вх(-).2 соединен с выходом 22 выходного каскада 19 (буферного усилителя).

Особенность входных каскадов ДУ1 и ДУ2 ОУ фиг.1 состоит в том, что при подаче на базы транзисторов VT1 (VT3) входного импульсного сигнала большой амплитуды (соизмеримой с напряжением питания) они работают в режиме «переключателя» тока I1 (I2) [1, 4, 5]. Действительно, при Uвх (+).1≫Uгр=50 мВ транзисторы VT1 и VT3 запираются, а токи эмиттеров и коллекторов транзисторов VT1 и VT4 становятся равными токам источников I1 и I2: Iэ1=Iк1=I1, Iэ4=Iк4=I2. Это приводит к запиранию промежуточного усилителя тока 15 (ПТ2). Как следствие, выходной ток промежуточного усилителя 3, заряжающий корректирующий конденсатор 21, будет также равен току I1. Поэтому напряжение на конденсаторе 21 изменяется по линейному закону:

Учитывая, что выходной каскад 19 имеет коэффициент передачи по напряжению, близкий к единице, из (1) можно найти, что максимальная скорость нарастания выходного напряжения ОУ фиг.1 (ϑвых) равна

Учитывая, что параметры, входящие в уравнение (2), связаны с параметрами ОУ и элементами его схемы следующим образом [4]:

можно найти, что

где ωв - верхняя граничная частота (по уровню - 3дб) разомкнутого ОУ,

Т - петлевое усиление разомкнутого ОУ,

Rэкв.18 - эквивалентное сопротивление, включенное параллельно корректирующему конденсатору C21,

f1 - частота единичного усиления ОУ (ω1=2 πf1=T ωв).

Таким образом, максимальная скорость нарастания выходного напряжения ОУ-прототипа не лучше, чем

или (что одно и то же)

Учитывая, что напряжение ограничения проходной характеристики ДУ1-ДУ2 (Uгр) в схеме-прототипе Uгр≈50 мВ, получаем, что в достаточно широкополосном ОУ, фиг.1 (например при f1=100 МГц):

В большинстве случаев этого недостаточно для построения современных аналоговых интерфейсов.

Введение резисторов 25 и 26 в схеме ОУ фиг.2 существенно изменяет его динамику.

В статическом (установившемся) режиме, за счет цепей смещения статического уровня (п.2, фиг.3) и специального построения выходного каскада 19 (п.3, фиг.4), можно обеспечить нулевое значение тока через резисторы 25 и 26. Таким образом, работа заявляемого ОУ на постоянном токе ни чем не отличается от работы ОУ-прототипа.

Если на неинвертирующий вход ОУ(+) подать импульсный сигнал, то уже при U(+) вх=2Uгр=2ϕт =50 мВ перераспределение тока источника 4 (I1=I4) между транзисторами 2 и 3 завершится. Однако при U(+) вх≫2Uгр=2ϕт ≈50 мВ ограничение эмиттерного тока транзистора 2 и, следовательно, тока заряда конденсатора 21 не произойдет, так как в заявляемой схеме создается дополнительный канал формирования сигнала динамической ошибки - через резисторы 25 и 26. При этом дополнительный зарядно-разрядный ток емкости С21, протекающий через эти резисторы, равен:

Если выбрать R26=R25 порядка сотен Ом, то в схеме фиг.1 существенно ускоряются процессы перезаряда корректирующей емкости 21 и, следовательно, возрастает максимальная скорость нарастания выходного напряжения ОУ. Моделирование в среде PSpice показывает, что ϑвых улучшается по сравнению с ϑвых ОУ-прототипа на два порядка.

При введении цепей смещения статического уровня 29 и 30 в соответствии с п.2 формулы изобретения (или выполнении выходного каскада по специальной схеме фиг.4) обеспечивается необходимый статический режим заявляемого ОУ, что позволяет уменьшить влияние зон нечувствительности входного каскада на его быстродействие. Однако при работе ОУ (фиг.2) с большим напряжением питания и при больших импульсных сигналах значительное повышение быстродействия обеспечивается и без цепей смещения 29 и 30. В частных случаях для минимизации влияния резисторов 25 и 26 на статику ОУ последовательно с ними можно включать p-n переходы 33 и 34 (фиг.5), которые обеспечивают нулевые значения токов через R25 и R26 при uвх=0, но в тоже время создают дополнительный канал передачи сигнала динамической ошибки на вход 14 (16).

Достоинство схемы фиг.5 состоит также в том, что при работе с импульсным сигналом она обеспечивает меньшие значения входной проводимости и исключает дополнительный разогрев эмиттерных областей транзисторов 2 и 3 (6 и 7). Это улучшает статическую точность ОУ. Для уменьшения зоны нечувствительности в схеме фиг.5 могут применятся цепи смещения статического уровня 29 и 30 (фиг.3), а также специальный выходной каскад 19 (фиг.4).

Введение транзисторов 35 и 37 (фиг.6) позволяет также уменьшить разогрев эмиттерных областей транзисторов 2 и 3 (6 и 7), обусловленный протеканием через них больших импульсных токов во время переходного процесса, и, кроме этого, создает условия для независимой регулировки крутизны преобразования сигнала ошибки во входной ток усилителя 13 (15) при разных амплитудах входного сигнала. Это обеспечивается за счет выбора сопротивлений резисторов 25, 36, и 27, 38, а также цепей смещения статического уровня.

Схема фиг.7, соответствующая п.6 формулы изобретения, применяется в тех случаях, когда коэффициент передачи по напряжению замкнутого неинвертирующего ОУ больше единицы. Это обеспечивается введением традиционного резисторного делителя (РД) между входом 22 и инвертирующим входом ОУ (Вх(-)). В частном случае авторы рекомендуют выбирать коэффициент передачи делителя токовой обратной связи 39 равным коэффициенту передачи РД. Следует заметить, что в заявляемом ОУ (например, фиг.7) одновременно реализуются два типа обратных связей - по напряжению с выхода 22 на инвертирующий вход и так называемая «токовая - обратная связь», обеспечивающая предельное быстродействие ОУ через четырехполюсник 39.

Таким образом, в заявляемом ОУ могут быть достигнуты параметры, присущие операционным усилителям двух различных классов. По имеющимся у авторов сведениям, такое техническое решение предлагается впервые.

В схеме фиг.8 для формирования заданного порога включения токовой обратной связи применяются цепи согласования статического уровня.

Рассмотренные выше особенности заявляемого устройства послужили основой для построения большого числа частных вариантов построения его выходной подсхемы, которые приведены на фиг.9-19.

Компьютерное моделирование заявляемого устройства по схеме фиг.2 в среде «PSpise» с использованием моделей интегральных транзисторов ФГУП «Пульсар» (г.Москва.) показало, что за счет введения новых элементов и связей выигрыш по максимальной скорости нарастания выходного напряжения в ОУ фиг.2 достигает 30÷40 раз. При этом исследованный ОУ имел следующие параметры:

- разомкнутый коэффициент усиления - 800;

- верхняя граничная частота неинвертирующего замкнутого ОУ со 100% отрицательной обратной связью (по уровню - 3дБ) - 820 МГц;

- выброс АЧХ замкнутого ОУ - 0.1 дБ;

- напряжение питания ±15 В;

- сопротивление двухполюсников 25, 26 - 100 Ом;

- токи источников 4 и 8 - 2 мА;

- выходной буферный усилитель 19 с единичным коэффициентом передачи на основе двухтактного эмиттерного повторителя с током потребления 4мА на p-n-p и n-p-n транзисторах, соответствующий схемам фиг.11, фиг.12;

- емкость коррекции (C21) - 5pF;

- максимальная скорость нарастания выходного напряжения при R25=R26=100 Ом - 16450 В/мкс;

- максимальная скорость нарастания выходного напряжения при R25=R26=∞ (прототип) - 350 В/мс.

Источники информации

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Двухтактный операционный усилитель. Патент РФ № 2193273, H 03 F 3/45.

3. Дифференциальный усилитель. Патент США № 4649352, кл. 330-261.

4. Операционные усилители с непосредственной связью каскадов / В.И. Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М. Соколов. - Л., 1979.

5. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983, 216 с.

6. Патент США № 5291149, H 03 f 3/48 (прототип).

7. Патент США № 6268769, H 03 f 3/45 (фиг.3) (прототип 2).

8. Патент США № 3974455, H 03 f 3/45 (фиг.7, фиг.9).

9. Патент США № 3968451, H 03 f 3/45.

10. Патент Японии 981(5)А332 №53-25232, H 03 f 3/26.

11. Патент США № 4783637, H 03 f 3/45.

12. Патент США № 4146845, кл. 330/225.

13. Патент США № 4595883, кл. 330/255.

14. Патент США № 4636743, кл. 330/295.

15. Патент США № 5515005, H 03 f 3/45.

16. Патент США № 4600893, H 03 f 3/45.

17. Журнал "Радио", № 1, 1980 г., стр.44, рис.2.

1. Операционный усилитель, содержащий входной дифференциальный каскад (1) на первом (2) и втором (3) входных n-p-n транзисторах, эмиттеры которых связаны с первым (4) источником опорного тока, входной дифференциальный каскад (5) на первом (6) и втором (7) входных p-n-p транзисторах, эмиттеры которых связаны со вторым (8) источником опорного тока, причем основные входы (9, 10) входного дифференциального каскада на n-p-n транзисторах соединены с основными входами (11, 12) входного дифференциального каскада (5) на p-n-p транзисторах, промежуточный двухтактный каскад, содержащий первый промежуточный усилитель (13), инвертирующий вход которого (14) соединен с коллектором первого входного n-p-n транзистора (2) входного дифференциального каскада (1) на n-p-n транзисторах, второй промежуточный усилитель (15), инвертирующий вход (16) которого соединен с коллектором первого входного p-n-p транзистора (6) дифференциального каскада (5) на p-n-p транзисторах, причем выход (17) первого промежуточного усилителя (13) связан по переменному току с входом (18) выходного каскада (19) и выходом (20) второго промежуточного усилителя (15), а также корректирующим конденсатором (21), отличающийся тем, что выход (22) выходного каскада (19) связан по переменному току с первыми выводами (23, 24) первого (25) и второго (26) дополнительных резисторов, вторые выводы которых (27, 28) связаны соответственно с эмиттерами первого (2) и второго (3) входных n-p-n транзисторов входного дифференциального каскада (1) на n-p-n транзисторах и эмиттерами первого (6) и второго (7) входных p-n-p транзисторов входного дифференциального каскада (5) на p-n-p транзисторах.

2. Устройство по п.1, отличающееся тем, что выход (22) выходного каскада (19) связан с первыми выводами (23, 24) первого (25) и второго (26) дополнительных резисторов через первую (29) и вторую (30) цепи смещения статического уровня.

3. Устройство по п.1, отличающееся тем, что выходной каскад (19) имеет два вспомогательных выхода (31, 32), статические уровни которых смещены относительно статического уровня его выхода (22), причем вспомогательные выходы (31, 32) связаны с первыми выводами (23, 24) дополнительных резисторов (25, 26).

4. Устройство по п.1, отличающееся тем, что эмиттеры первого (2) и второго (3) входных n-p-n транзисторов входного дифференциального каскада на n-p-n транзисторах (1) связаны со вторым выводом (27) первого дополнительного резистора (25) через эмиттерно-базовый переход вспомогательного n-p-n транзистора (33), коллектор которого соединен с инвертирующем входом (14) первого промежуточного усилителя тока (13), а эмиттер первого (6) и второго (7) входных p-n-p транзисторов входного дифференциального каскада на p-n-p транзисторах связаны со вторым выводом (28) второго дополнительного резистора (26) через эмиттерно-базовый переход второго вспомогательного p-n-p транзистора (34), коллектор которого подключен к инвертирующему входу (16) второго промежуточного усилителя (15).

5. Устройство по п.1, отличающееся тем, что вход (9) входного дифференциального каскада (1) на n-p-n транзисторах связан по переменному току с выходом (22) выходного каскада (19) через эмиттерно-базовый переход первого (35) дополнительного n-p-n транзистора и первый вспомогательный резистор (36), причем коллектор первого дополнительного n-p-n транзистора соединен с инвертирующем входом (14) первого промежуточного усилителя тока (13), а вход (11) входного дифференциального каскада на p-n-p транзисторах (5) связан по переменному току с выходом (22) выходного каскада (19) через эмиттерно-базовый переход второго дополнительного p-n-p транзистора (37) и второй вспомогательный резистор (38), причем коллектор второго дополнительного n-p-n транзистора (37) соединен с инвертирующим входом (16) второго промежуточного усилителя тока (15).

6. Устройство по п.1, отличающееся тем, что выход (22) выходного каскада (19) связан с первыми выводами (23, 24) дополнительных резисторов (25, 26) через четырехполюсник токовой отрицательной обратной связи (39).

7. Устройство по п.2, отличающееся тем, что выход (22) выходного каскада (19) связан с первыми выводами (23, 24) первого (25) и второго (26) дополнительных резисторов через последовательно соединенные четырехполюсник токовой обратной связи (39), первую (29) и вторую (30) цепи смещения статического уровня.