Синтезатор частот с частотной или фазовой модуляцией

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может использоваться в качестве возбудителя передатчика с широкополосной частотной или фазовой модуляцией. Технический результат заключается в повышении качества частотной или фазовой модуляции наряду с высоким быстродействием устройства. Предлагаемый синтезатор частот на основе импульсно-фазовой автоподстройки частоты имеет равномерные модуляционные характеристики в широком диапазоне выходных частот, что наблюдается как при частотной, так и при фазовой модуляции в пределах и вне ширины полосы системы импульсно-фазовой автоподстройки частоты. Предлагаемая схема позволяет существенным образом улучшить качество частотной или фазовой модуляции со стабильными параметрами, так как в этой схеме происходит полное устранение сигнала ошибки по фазе на выходе частотно-фазового детектора в результате действия компенсирующего сигнала на входе фильтра нижних частот. 4 ил.

Реферат

Изобретение относится к радиотехнике и может использоваться в качестве возбудителя передатчика с широкополосной частотной или фазовой модуляцией.

Широко известна схема синтезатора частот с частотной или фазовой модуляцией, включающая опорный генератор, делитель частоты с фиксированным коэффициентом деления, управляемый генератор, делитель частоты с дробным переменным коэффициентом деления, управляемый с помощью дельта-сигма модулятора, частотно-фазовый детектор и фильтр нижних частот, образующих кольцо фазовой автоподстройки частоты управляемого генератора (см. Seste Dell'Aera, Тот Riley "Applied Microwave & Wireless", July 2002, p.34-39) [1].

Известна аналогичная схема синтезатора с частотной или фазовой модуляцией, в которой используется частотно-фазовый детектор, фильтр нижних частот, управляемый генератор и делитель с дробным переменным коэффициентом деления, управляемый дельта-сигма модулятором (см., например, патент США №6011815) [2].

Такие схемы синтезаторов с частотной или фазовой модуляцией характеризуются простотой схемной реализации и обеспечивают высокие качественные параметры выходного модулированного сигнала. В таких схемах синтезаторов полоса модулирующих частот ограничена частотой среза системы импульсно-фазовой автоподстройки частоты.

Основным недостатком приведенных выше схем синтезаторов с частотной или фазовой модуляцией является довольно низкое качество модуляции из-за возникновения комбинационных составляющих в спектре выходного сигнала с частотой сравнения и помех дробности в случае применения делителя с дробным переменным коэффициентом деления.

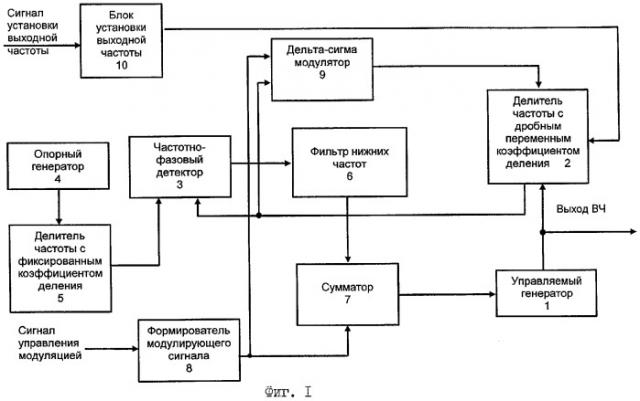

Наиболее близким по физической сущности и технической реализации к предлагаемому синтезатору с частотной или фазовой модуляцией является синтезатор частот, описанный в Европейском патенте №322139 "Frequency or phase modulation" [3], структурная схема которого приведена на фиг.1.

Синтезатор частот с частотной или фазовой модуляцией содержит управляемый генератор 1, делитель 2 частоты с дробным переменным коэффициентом деления, частотно-фазовый детектор 3, опорный генератор 4, делитель 5 частоты с фиксированным коэффициентом деления, фильтр 6 нижних частот, сумматор 7, формирователь 8 модулирующего сигнала, дельта-сигма модулятор 9, блок 10 установки выходной частоты.

Выход управляемого генератора 1 синтезатора является выходом высокой частоты и соединен с первым входом делителя 2 частоты с дробным переменным коэффициентом деления. Второй вход делителя 2 частоты с дробным переменным коэффициентом деления является входом сигнала управления коэффициентом деления и соединен с выходом дельта-сигма модулятора 9. Третий вход делителя 2 частоты с дробным переменным коэффициентом деления соединен с выходом блока 10 установки выходной частоты, формирующим сигнал выбора коэффициента деления для новой выходной частоты. Выход делителя 2 частоты с дробным переменным коэффициентом деления соединен с синхронизируемым входом частотно-фазового детектора 3 и тактовым входом дельта-сигма модулятора 9. Вход синхронизации частотно-фазового детектора 3 соединен с выходом делителя 5 частоты с фиксированным коэффициентом деления. Вход делителя 5 частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора 4, формирующего опорный сигнал. Выход частотно-фазового детектора 3, на котором формируется сигнал рассогласования или сигнал ошибки, соединен с фильтром 6 нижних частот. Выход фильтра 6 нижних частот соединен с первым входом сумматора 7, который является входом сигнала коррекции. Выход формирователя 8 модулирующего сигнала, являющийся выходом модулирующего сигнала, соединен со входом дельта-сигма модулятора 9 и вторым входом сумматора 7. Выход сумматора 7, который является выходом суммарного управляющего сигнала, соединен с входом управляемого генератора 1. Вход блока 10 установления выходной частоты является входом сигнала установки выходной частоты. Вход формирователя 8 модулирующего сигнала является входом сигнала управления модуляцией.

Схема устройства-прототип работает следующим образом.

Синтезатор с частотной или фазовой модуляцией с постоянной составляющей сигнала модуляции содержит управляемый генератор 1, выходной сигнал которого синхронизирован по фазе с выходным сигналом делителя 5 частоты с фиксированным коэффициентом деления. Синхронизация осуществляется за счет деления частоты выходного сигнала управляемого генератора 1 в коэффициент деления разделителем 2 частоты с дробным переменным коэффициентом деления и сравнения выходных сигналов этих делителей в частотно-фазовом детекторе 3. Сигнал с выхода частотно-фазового детектора 3 проходит через фильтр 6 нижних частот, и полученный сигнал используется для автоподстройки частоты управляемого генератора 1. Частотная или фазовая модуляция осуществляется подачей модулирующего сигнала от формирователя 8 модулирующего сигнала в две точки контура импульсно-фазовой автоподстройки частоты. Во-первых, управляемый генератор 1 модулируется непосредственно путем сложения модулирующего входного сигнала с выхода формирователя 8 с выходным напряжением фильтра 6 нижних частот в сумматоре 7. Это обеспечивает модуляцию до весьма высоких частот, так как в основном ширина полосы частот по входу управляемого генератора 1 может быть высокой (до нескольких МГц).

На частотах в пределах ширины полосы системы импульсно-фазовой автоподстройки частоты система пытается устранить этот непосредственно подаваемый в управляемый генератор 1 сигнал модуляции, так как ее он рассматривает как частотную или фазовую погрешность. Практически на нижних частотах модуляции процесс модуляции устраняется. Чтобы обеспечить частотную или фазовую модуляцию с постоянной составляющей сигнала модуляции, используют дополнительный второй канал модуляции от формирователя 8 модулирующего сигнала через дельта-сигма модулятор 9 на делитель 2 частоты с дробным переменным коэффициентом деления, в котором изменяется коэффициент деления по закону модулирующего воздействия. При этом система устроена так, что два канала модуляции согласованы с точки зрения усиления фазы. В результате того, что коэффициент деления делителя 2 частоты с дробным переменным коэффициентом деления изменяется в соответствии с законом модуляции, погрешность в системе импульсно-фазовой автоподстройки частоты на выходе частотно-фазового детектора 3 отсутствует, и частотная характеристика модуляции снижается до уровня постоянного тока, т.е. до нулевой частоты модуляции fмод. Коэффициент деления частоты делителя 2 частоты с дробным переменным коэффициентом деления устанавливается на выбранную дробную величину по закону модуляции с помощью дельта-сигма модулятора 9.

Описанная система имеет несколько существенных недостатков. В обоих каналах прохождения модулирующего сигнала возникают задержки по фазе, а также из-за того, что требуемый коэффициент деления делителя 2 частоты с дробным переменным коэффициентом деления устанавливается не мгновенно, а с некоторой задержкой после поступления сигнала управления от дельта-сигма модулятора 9. Эффект этой фазо-временной ошибки заключается в том, что оба канала модуляции не могут быть точно согласованы по усилению. Поэтому существуют сигналы ошибки по фазе на выходе частотно-фазового детектора 3. Эти сигналы через фильтр 6 нижних частот и сумматор 7 проходят на управляющий вход управляемого генератора 1, и, в конечном итоге, это приводит к искажению закона модулирующего воздействия и, как следствие, - к ухудшению качества модуляции.

Существенным недостатком такой схемы реализации частотной или фазовой модуляции в синтезаторе частот является также наличие в спектре выходного сигнала комбинационных составляющих с частотой сравнения и помех дробности, что также ухудшает качество модуляции.

Задачей, которую решает предлагаемое изобретение, является повышение качества частотной или фазовой модуляции наряду с высоким быстродействием устройства.

Для решения этой задачи в синтезатор частот с частотной или фазовой модуляцией, содержащий управляемый генератор, делитель частоты с дробным переменным коэффициентом деления, частотно-фазовый детектор, опорный генератор, делитель частоты с фиксированным коэффициентом деления, фильтр нижних частот, первый сумматор, формирователь модулирующего сигнала, дельта-сигма модулятор, блок установки выходной частоты, причем выход управляемого генератора является выходом высокой частоты и соединен с первым входом делителя частоты с дробным переменным коэффициентом деления, второй вход делителя частоты с дробным переменным коэффициентом деления является входом сигнала управления коэффициентом деления и соединен с первым выходом дельта-сигма модулятора, третий вход делителя частоты с дробным переменным коэффициентом деления соединен с выходом блока установки выходной частоты, формирующим сигнал выбора коэффициента деления для новой выходной частоты, выход делителя частоты с дробным переменным коэффициентом деления соединен с синхронизируемым входом частотно-фазового детектора и тактовым входом дельта-сигма модулятора, вход синхронизации частотно-фазового детектора соединен с выходом делителя частоты с фиксированным коэффициентом деления, вход делителя частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора, формирующего опорный сигнал, выход фильтра нижних частот соединен с первым входом первого сумматора, который является входом сигнала коррекции, выход формирователя модулирующего сигнала, являющийся выходом модулирующего сигнала, соединен со входом дельта-сигма модулятора и вторым входом первого сумматора, выход первого сумматора, который является выходом суммарного управляющего сигнала, соединен со входом управляемого генератора, вход блока установления выходной частоты является входом сигнала установки выходной частоты, вход формирователя модулирующего сигнала 8 является входом сигнала управления модуляцией,

согласно изобретению в синтезатор введен второй сумматор, причем выход частотно-фазового детектора, на котором формируется сигнал рассогласования, соединен с первым входом второго сумматора, второй вход второго сумматора является входом сигнала компенсации и соединен со вторым выходом дельта-сигма модулятора, выход второго сумматора является выходом нулевой ошибки и соединен со входом фильтра нижних частот.

Сопоставительный анализ синтезатора частот с частотной или фазовой модуляцией с прототипом показывает, что предлагаемое изобретение существенно отличаются от известных решений, так как позволяет повысить качество частотной или фазовой модуляции наряду с высоким быстродействием.

Сопоставительный анализ заявляемого решения с другими техническими решениями в данной области техники не позволил выявить признаки, заявленные в отличительной части формулы изобретения. Следовательно, заявляемое решение отвечает критериям "новизна", "техническое решение задачи", "существенные отличия" и обладает неочевидностью решения.

Графические материалы, представленные в материалах заявки:

Фиг.1 - структурная схема устройства прототипа.

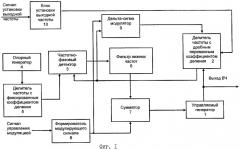

Фиг.2 - структурная схема предлагаемого устройства.

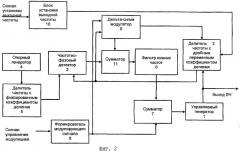

Фиг.3 - вариант выполнения дельта-сигма модулятора.

Фиг.4 - модуляционные характеристики, реализуемые в синтезаторе при различных вариантах подачи сигнала модуляции.

Фиг.4а - модуляционная характеристика при подаче сигнала модуляции только на сумматор 7.

Фиг.4б - модуляционная характеристика при подаче сигнала модуляции только на дельта-сигма модулятор 9.

Фиг.4с - модуляционная характеристика устройства-прототипа.

Фиг.4д - модуляционная характеристика предлагаемого изобретения.

Для решения задачи повышения качества частотной или фазовой модуляции наряду с высоким быстродействием предлагается синтезатор частот с частотной или фазовой модуляцией, в котором предусматривается компенсация возникающих комбинационных составляющих и помех дробности в результате дискретного действия системы импульсно-фазовой автоподстройки частоты.

На Фиг.2 приведена структурная схема предлагаемого устройства. Предлагаемый синтезатор частот с частотной или фазовой модуляцией содержит управляемый генератор 1, делитель 2 частоты с дробным переменным коэффициентом деления, частотно-фазовый детектор 3, опорный генератор 4, делитель 5 частоты с фиксированным коэффициентом деления, фильтр 6 нижних частот, первый сумматор 7, формирователь 8 модулирующего сигнала, дельта-сигма модулятор 9, блок 10 установки выходной частоты, второй сумматор 11.

Выход управляемого генератора 1 синтезатора является выходом высокой частоты и соединен с первым входом делителя 2 частоты с дробным переменным коэффициентом деления. Второй вход делителя 2 частоты с дробным переменным коэффициентом деления является входом сигнала управления коэффициентом деления и соединен с первым выходом дельта-сигма модулятора 9. Третий вход делителя 2 частоты с дробным переменным коэффициентом деления соединен с выходом блока 10 установки выходной частоты, формирующим сигнал выбора коэффициента деления для новой выходной частоты. Выход делителя 2 частоты с дробным переменным коэффициентом деления соединен с синхронизируемым входом частотно-фазового детектора 3 и тактовым входом дельта-сигма модулятора 9. Вход синхронизации частотно-фазового детектора 3 соединен с выходом делителя 5 частоты с фиксированным коэффициентом деления. Вход делителя 5 частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора 4, формирующего опорный сигнал. Выход частотно-фазового детектора 3, на котором формируется сигнал рассогласования или сигнал ошибки, соединен с первым входом второго сумматора 11, второй вход которого является входом сигнала компенсации и соединен со вторым выходом дельта-сигма модулятора 9. Выход второго сумматора 11 является выходом нулевой ошибки и соединен с входом фильтра 6 нижних частот. Выход фильтра 6 нижних частот соединен с первым входом первого сумматора 7, который является входом сигнала коррекции. Выход формирователя 8 модулирующего сигнала, являющийся выходом модулирующего сигнала, соединен с входом дельта-сигма модулятора 9 и вторым входом первого сумматора 7. Выход первого сумматора 7, который является выходом суммарного управляющего сигнала, соединен с входом управляемого генератора 1. Вход блока 10 установления выходной частоты является входом сигнала установки выходной частоты. Вход формирователя 8 модулирующего сигнала является входом сигнала управления модуляцией.

Схема работает следующим образом.

После установления синхронизма в кольце импульсно-фазовой автоподстройки частоты на выходе делителя 5 частоты с фиксированным коэффициентом деления и на выходе делителя 2 с дробным переменным коэффициентом деления частоты становятся равными. Благодаря наличию в кольце импульсно-фазовой автоподстройки частоты интегрирующего фильтра 6 нижних частот разность фаз сравниваемых сигналов на частотно-фазовом детекторе 3 стремится к нулю. При подаче модулирующего сигнала от формирователя 8 модулирующего сигнала на управляемый генератор 1 через сумматор 7 происходит частотная или фазовая модуляция выходного сигнала синтезатора и сигнала на выходе 2 делителя с дробным переменным коэффициентом деления, в результате чего на выходе частотно-фазового детектора 3 появляется сигнал ошибки. Для его устранения производится модуляция коэффициента деления делителя 2 с дробным переменным коэффициентом деления, для чего модулирующий сигнал подается на дельта-сигма модулятор 9. Дельта-сигма модулятор 9 управляет коэффициентом деления делителя 2 с дробным переменным коэффициентом деления, чтобы скомпенсировать появляющийся сигнал ошибки. В предлагаемую схему дополнительно введен второй сумматор 11 между выходом частотно-фазового детектора 3 и фильтром 6 нижних частот. От дельта-сигма модулятора 9 на сумматор 11 подается компенсирующий сигнал. Компенсирующий сигнал призван устранить влияние на качество модуляции изменений коэффициентов деления делителя 2 с дробным переменным коэффициентом деления при смене выходных несущих частот синтезатора. Кроме того, учитывается влияние неравномерности крутизны перестройки управляемого генератора 1 в рабочем диапазоне выходных частот, которые приводят к возникновению нелинейных и комбинационных искажений выходного модулированного сигнала. Предлагаемая схема позволяет существенным образом улучшить качество частотной или фазовой модуляции со стабильными параметрами, так как в этой схеме происходит полное устранение сигнала ошибки по фазе на выходе частотно-фазового детектора 3 в результате действия компенсирующего сигнала на входе фильтра 6 нижних частот. В предлагаемой схеме модуляция осуществляется по двум каналам: каналу управляемого генератора 1 и каналу цепи обратной связи делителя 2 с дробным переменным коэффициентом деления. В результате действия компенсирующего сигнала на входе фильтра 6 нижних частот обеспечивается идентичность усиления модулирующего сигнала по этим двум каналам модуляции в широком диапазоне изменения как модулирующих, так и выходных частот. В результате осуществляется широкополосная модуляция практически от постоянного тока до частоты среза по входу управляемого генератора 1 (порядка 1-2 МГц). Следует отметить, что в предлагаемой схеме построения системы импульсно-фазовой автоподстройки частоты с частотной или фазовой модуляцией не существует ограничений по выбору полосы ее пропускания для обеспечения высокого быстродействия, которое необходимо наряду с высоким качеством модуляции в различных системах связи.

На Фиг.3 представлен вариант выполнения дельта-сигма модулятора 9.

Сигнал модуляции поступает в цепь дельта-сигма модулятора 9, который квантует входной сигнал модуляции на поток двоичных символов со скоростью, определяемой входным для данного случая тактовым сигналом с выхода делителя 2 с дробным переменным коэффициентом деления. Двоичные символы изменяют коэффициент деления делителя 2 с дробным переменным коэффициентом деления между двумя соседними коэффициентами деления по закону изменения модулирующего сигнала. Дельта-сигма модулятор 9 содержит интегратор 12 ошибки, который интегрирует разность между входным сигналом модуляции и квантованным сигналом модуляции для получения интегрированного сигнала ошибки, используемого в качестве компенсации в цепи частотно-фазового детектора 3 и фильтра 6 нижних частот.

Дельта-сигма модулятор 9 вырабатывает последовательность управляющих сигналов, поступающих на модуляционный вход делителя 2 с дробным переменным коэффициентом деления. Эта последовательность имеет коэффициент заполнения, представляющий на входе дельта-сигма модулятора 9 мгновенный сигнал модуляции. Это достигается с помощью интегратора 12 ошибки, формирующего среднее значение разности выходного управляющего потока данных от триггера 15 и входного сигнала модуляции от формирователя 8 модулирующего сигнала. Если в среднем коэффициент заполнения слишком велик, то интегратор 12 ошибки, обладая способностью обратного преобразования, формирует падающее выходное напряжение до тех пор, пока напряжение интегрированной ошибки не опустится ниже порога квантования компаратора 14, задаваемого формирователем 13 опорного напряжения. На выходе компаратора 14 устанавливается уровень ЛОГ 0, который перемещается на следующий тактовый импульс с выхода делителя 2 с дробным переменным коэффициентом деления на выход триггера 15. Так как сигнал модуляции с выхода триггера 15 находится между уровнями ЛОГ 1 и ЛОГ 0, то знак ошибки меняется, и сигнал на выходе интегратора 12 ошибки начинает возрастать до тех пор, пока он еще раз не достигает порога квантования компаратора 14, формируя сигнал ЛОГ 1. Затем цикл работы дельта-сигма модулятора 9 повторяется.

Интегрированный сигнал ошибки, поступающий на сумматор 11 от интегратора 12 ошибки, является компенсирующим сигналом, аналогичным, но с противоположным знаком, сигналу совокупной фазовой ошибки на выходе частотно фазового детектора 3. Следовательно, в предлагаемой схеме вырабатывается сигнал компенсации фазовой ошибки, затем этот сигнал объединяется с сигналом с выхода частотно-фазового детектора 3 для формирования точного сигнала управления управляемым генератором 1 в системе импульсно-фазовой автоподстройки частоты синтезатора частот. Таким образом, обеспечивается точная работа синтезатора частот, модулированного по частоте или фазе вплоть до уровня постоянного тока.

На Фиг.4 представлены модуляционные характеристики, показанные относительно частоты среза fc системы ИФАПЧ синтезатора в диапазоне частот fмод модулирующего сигнала.

На Фиг.4а представлена модуляционная характеристика при подаче сигнала модуляции только на сумматор 7, на Фиг.4б - только на дельта-сигма модулятор 9.

Модуляционная характеристика на Фиг.4с получается при реализации частотной или фазовой модуляции в синтезаторе, выполненном по схеме устройства-прототипа. Эта модуляционная характеристика имеет протяженность от постоянного тока до частоты среза fp по входу УГ 1, но имеет неравномерность на частотах fмод, лежащих ниже частоты среза fc системы ИФАПЧ. Реализация схемы предлагаемого изобретения с введением компенсирующего сигнала с помощью сумматора 11 позволяет получить равномерную модуляционную характеристику в широком диапазоне частот от постоянного тока до частоты среза fp управляемого генератора 1.

Представленная на Фиг.4д модуляционная характеристика показывает преимущество реализации предлагаемого изобретения по сравнению с ранее известными схемами построения синтезаторов частот с частотной или фазовой модуляцией.

Предлагаемый синтезатор частот на основе импульсно-фазовой автоподстройки частоты имеет равномерные модуляционные характеристики в широком диапазоне выходных частот, что наблюдается как при частотной, так и при фазовой модуляции в пределах и вне ширины полосы системы импульсно-фазовой автоподстройки частоты.

Предлагаемая схема позволяет существенным образом улучшить качество частотной или фазовой модуляции со стабильными параметрами, так как в этой схеме происходит полное устранение сигнала ошибки по фазе на выходе частотно-фазового детектора 3 в результате действия компенсирующего сигнала на входе фильтра 6 нижних частот.

Синтезатор частот с частотной или фазовой модуляцией, содержащий управляемый генератор, делитель частоты с дробным переменным коэффициентом деления, частотно-фазовый детектор, опорный генератор, делитель частоты с фиксированным коэффициентом деления, фильтр нижних частот, первый сумматор, формирователь модулирующего сигнала, дельта-сигма модулятор, блок установки выходной частоты, причем выход управляемого генератора является выходом высокой частоты и соединен с первым входом делителя частоты с дробным переменным коэффициентом деления, второй вход делителя частоты с дробным переменным коэффициентом деления является входом сигнала управления коэффициентом деления и соединен с первым выходом дельта-сигма модулятора, третий вход делителя частоты с дробным переменным коэффициентом деления соединен с выходом блока установки выходной частоты, формирующим сигнал выбора коэффициента деления для новой выходной частоты, выход делителя частоты с дробным переменным коэффициентом деления соединен с синхронизируемым входом частотно-фазового детектора и тактовым входом дельта-сигма модулятора, вход синхронизации частотно-фазового детектора соединен с выходом делителя частоты с фиксированным коэффициентом деления, вход делителя частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора, формирующего опорный сигнал, выход фильтра нижних частот соединен с первым входом первого сумматора, который является входом сигнала коррекции, выход формирователя модулирующего сигнала, являющийся выходом модулирующего сигнала, соединен с входом дельта-сигма модулятора и вторым входом первого сумматора, выход первого сумматора, который является выходом суммарного управляющего сигнала, соединен с входом управляемого генератора, вход блока установления выходной частоты является входом сигнала установки выходной частоты, вход формирователя модулирующего сигнала является входом сигнала управления модуляцией, отличающийся тем, что введен второй сумматор, причем выход частотно-фазового детектора, на котором формируется сигнал рассогласования, соединен с первым входом второго сумматора, второй вход второго сумматора является входом сигнала компенсации и соединен со вторым выходом дельта-сигма модулятора, выход второго сумматора является выходом нулевой ошибки и соединен с входом фильтра нижних частот.