Устройство для синхронизации по циклам

Иллюстрации

Показать всеИзобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений. Технический результат - повышение надежности работы устройства для синхронизации по циклам. Устройство содержит опознаватель синхросигнала, элемент запрета, первый элемент И, сумматор, блок регистров сдвига, формирователь цикловых импульсов, элемент ИЛИ, счетчик циклов, счетчик искаженных синхросигналов, блок выбора допустимого числа неискаженных синхросимволов, блок выбора порога, блок выбора коэффициента счета, счетчик по выходу из синхронизма, а также решающий узел, содержащий первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения, второй элемент И, третий элемент И, второй элемент ИЛИ. Технический результат достигается благодаря устранению возможности переполнения блока регистров сдвига в синхронном режиме работы. 1 ил.

Реферат

Изобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений.

Известно устройство для синхронизации по циклам по а.с. СССР 436393 класса G 11 С 19/00, опубл. 15.07.1974, Бюл. №46, содержащее, как и предлагаемое устройство, опознаватель синхросигнала, сумматор, блок регистров сдвига, решающий узел, причем выход опознавателя синхросигнала подключен к первому входу сумматора, выход которого соединен с сигнальным входом блока регистров сдвига, основной выход которого подключен ко второму входу сумматора. Кроме того, в известном устройстве основной выход блока регистров сдвига соединен и с сигнальным входом решающего узла. При этом сумматор выполнен в виде n-разрядного реверсивного счетчика, который выполняет функцию счета откликов опознавателя синхросигнала на каждой из импульсных позиций циклов интервала наблюдения, а n регистров сдвига блока регистров сдвига осуществляют запоминание результатов счета в течение длительности цикла. В тактовых интервалах, задаваемых тактовыми импульсами с генератора тактовых импульсов, осуществляется списывание значений разрядов n-разрядного счетчика в первые ячейки соответствующих регистров сдвига и запись в этот же счетчик значений последних ячеек регистров сдвига. Если в тактовом интервале имеет место отклик опознавателя синхросигнала, то в n-разрядный счетчик добавляется единица, и таким образом значение двоичного числа, соответствующего числу откликов, накопленных ранее на данной позиции цикла, увеличивается на единицу. Если же на позиции цикла нет отклика опознавателя, то число, записанное в параллельном двоичном коде в n-разрядный счетчик с последних ячеек регистров, уменьшается на единицу. По истечении цикла в ячейках регистров в параллельном двоичном коде оказываются записанными результаты счета откликов опознавателя на всех N импульсных позициях. На основе анализа этих результатов решающий узел определяет номер позиции, которой соответствует наибольшее двоичное число откликов опознавателя синхросигнала, и таким образом принимает решение о положении синхронизма. Выход решающего узла является выходом устройства. Недостатком известного устройства является низкая надежность работы, обусловленная возможностью переполнения блока регистров сдвига, приводящее к нарушению правильной работы решающего узла и всего устройства в целом. Это обусловливается тем, что сигнал синхронизации с выхода решающего узла не обнуляет блок регистров сдвига. При этом блок регистров сдвига продолжает накапливать отклики опознавателя синхросигнала. Поэтому через определенное количество циклов поиска во многих ячейках блока регистров сдвига (не только на позиции истинного синхросигнала) будет наблюдаться установка максимально возможных значений накопления, что приведет к нарушению правильной работы решающего узла и всего устройства в целом, т.к. решающий узел после переполнения не может определить позицию синхросигнала.

Наиболее близким к предлагаемому является устройство для синхронизации по циклам по патенту РФ № 2231228 класса Н 04 L 7/08, опубл. 20.06.2004, Бюл. № 17, прототип, содержащее, как и предлагаемое устройство, опознаватель синхросигнала, элемент запрета, первый элемент И, сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, элемент ИЛИ, счетчик циклов, счетчик искаженных синхросигналов, блок выбора допустимого числа неискаженных синхросигналов, блок выбора порога, блок выбора коэффициента счета, счетчик по выходу из синхронизма. Причем решающий узел содержит первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения и второй элемент И. Выход опознавателя синхросигнала совместно соединен со вторым входом элемента запрета, вторым входом первого элемента И, а также с первым входом сумматора, выход которого подключен к сигнальному входу блока регистров сдвига. Основной выход блока регистров сдвига подключен ко второму входу сумматора, а дополнительный выход - к сигнальному входу решающего узла. Сигнальным входом решающего узла является первый вход первого блока сравнения. При этом выход первого блока сравнения подключен к входу управления блока памяти, выход которого подключен ко второму входу первого блока сравнения и первому входу блока вычитания. Второй вход блока вычитания объединен с входом данных блока памяти, первым входом первого блока сравнения и является сигнальным входом решающего узла. Выход блока вычитания подключен ко второму входу второго блока сравнения, выход которого соединен с входом сброса счетчика сравнения, выход которого соединен с вторым входом второго элемента И. При этом управляющим и тактовым входами решающего узла являются соответственно первый вход второго блока сравнения и тактовый вход счетчика сравнения. Дополнительным управляющим входом решающего узла является первый вход второго элемента И. При этом выход решающего узла совместно подключен к входам сброса формирователя цикловых импульсов, блока регистров сдвига, а также ко второму входу элемента ИЛИ. Выход формирователя цикловых импульсов совместно подключен к первому входу первого элемента И, первому входу элемента запрета и входу счетчика циклов. Выход счетчика циклов подключен к входу управления счетчика искаженных синхросигналов. Выход счетчика искаженных синхросигналов совместно подключен к адресным входам блока выбора допустимого числа неискаженных синхросимволов, блока выбора порога и блока выбора коэффициента счета. Выход блока выбора допустимого числа неискаженных синхросимволов подключен к входу управления опознавателя синхросигнала. Выход элемента запрета совместно подключен к счетным входам счетчика по выходу из синхронизма и счетчика искаженных синхросигналов. Выход первого элемента И подключен к первому входу элемента ИЛИ, выход которого подключен к входу сброса счетчика по выходу из синхронизма. К входу данных счетчика по выходу из синхронизма подключен выход блока выбора коэффициента счета. Тактовый вход формирователя цикловых импульсов объединен с тактовыми входами опознавателя синхросигнала, блока регистров сдвига и решающего узла. Управляющий вход решающего узла соединен с выходом блока выбора порога, а дополнительный управляющий вход решающего узла соединен с выходом счетчика по выходу из синхронизма. При этом сигнальный вход опознавателя синхросигнала, тактовый вход формирователя цикловых импульсов и выход формирователя цикловых импульсов являются соответственно сигнальным входом, тактовым входом и выходом устройства. Кроме того, в известном устройстве выходом решающего узла является выход второго элемента И, который соединен с входом сброса блока памяти. Недостатком прототипа является низкая надежность работы, обусловленная возможностью переполнения блока регистров сдвига в синхронном режиме, приводящего к нарушению правильной работы решающего узла и всего устройства в целом. Это обусловливается тем, что сигнал синхронизации решающего узла, обнуляющий блок регистров сдвига может быть сформирован только при условии обнаружения счетчиком по выходу из синхронизма сбоя синхронизма и обнаружении решающим узлом синхросигнала. В синхронном режиме счетчик по выходу из синхронизма обнулен. Поэтому даже при обнаружении решающим узлом истинного синхросигнала на его выходе сигнал синхронизации не формируется. При этом блок регистров сдвига не обнуляется, а продолжает накапливать отклики. Поэтому через определенное количество циклов поиска во многих ячейках блока регистров сдвига (не только на позиции истинного синхросигнала) будет наблюдаться установка максимально возможных значений накопления, что приведет к нарушению правильной работы решающего узла и всего устройства в целом, т.к. решающий узел после переполнения не может определить позицию истинного синхросигнала, как в синхронном режиме, так и после сбоя синхронизма.

Особенностью передачи детерминированного циклового синхросигнала является периодичность его повторения на одних и тех же позициях цикла передачи группового сигнала. При этом опознаватель синхросигнала может распознавать в принимаемом групповом сигнале не только истинные синхрогруппы, но и ложные, случайно сформированные на информационных позициях цикла. При формировании на выходе опознавателя синхросигнала откликов в виде единиц (на опознанную синхрогруппу) и нулей (на неопознанную синхрогруппу) требуемая достоверность принятия решения решающим узлом достигается за счет накопления откликов в блоке регистров сдвига. Распознание опознавателем синхросигнала кодовых групп на позиции синхросигнала приводит к накоплению откликов в ячейке блока регистров сдвига, соответствующей истинной синхрогруппе. При этом распознание опознавателем синхросигнала кодовых групп на информационных позициях цикла приводит к накоплению откликов в ячейках блока регистров сдвига, соответствующих ложным синхрогруппам. Решающий узел определяет ячейку с максимальным накоплением откликов. Этой ячейке соответствует позиция в цикле, которая принимается решающим узлом за позицию синхросигнала с наибольшей вероятностью. Решающий узел может определить позицию истинного циклового синхросигнала только при условии превышения накопления на определенную величину в одной из ячеек блока регистров сдвига над накоплениями во всех остальных ячейках. Для правильной работы решающего узла необходимо, чтобы при определении истинного синхросигнала блок регистров сдвига сбрасывался (обнулялся), а процесс накопления откликов опознавателя начинался заново. При этом при сбое синхронизма сброс блока регистров сдвига может произойти только после обнаружения выхода устройства из синхронизма. Необходимо отметить, что для надежной работы устройства сброс блока регистров сдвига в синхронном режиме работы также должен осуществляться. Невыполнение этой процедуры может привести к переполнению ячеек блока регистров сдвига, что приведет к нарушению правильной работы решающего узла и всего устройства в целом. Указанные факторы предъявляют повышенные требования к надежному функционированию блока регистров сдвига и недопущению его переполнения в синхронном режиме работы, что, в конечном счете, способствует надежной работе всего устройства для синхронизации по циклам.

Устройство для синхронизации по циклам содержит опознаватель синхросигнала, элемент запрета, первый элемент И, сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, элемент ИЛИ, счетчик циклов, счетчик искаженных синхросигналов, блок выбора допустимого числа неискаженных синхросимволов, блок выбора порога, блок выбора коэффициента счета, счетчик по выходу из синхронизма. Причем решающий узел содержит первый блок сравнения, блок памяти, блок вычитания, второй блок сравнения, счетчик сравнения и второй элемент И. Выход опознавателя синхросигнала совместно соединен со вторым входом элемента запрета, вторым входом первого элемента И, а также с первым входом сумматора, выход которого подключен к сигнальному входу блока регистров сдвига. Основной выход блока регистров сдвига подключен ко второму входу сумматора, а дополнительный выход - к сигнальному входу решающего узла. Сигнальным входом решающего узла является первый вход первого блока сравнения. При этом выход первого блока сравнения подключен к входу управления блока памяти, выход которого подключен ко второму входу первого блока сравнения и первому входу блока вычитания. Второй вход блока вычитания объединен с входом данных блока памяти, первым входом первого блока сравнения и является сигнальным входом решающего узла. Выход блока вычитания подключен ко второму входу второго блока сравнения, выход которого соединен с входом сброса счетчика сравнения, выход которого соединен с вторым входом второго элемента И. При этом управляющим и тактовым входами решающего узла являются соответственно первый вход второго блока сравнения и тактовый вход счетчика сравнения. Дополнительным управляющим входом решающего узла является первый вход второго элемента И. При этом выход решающего узла совместно подключен к входам сброса формирователя цикловых импульсов, блока регистров сдвига, а также ко второму входу элемента ИЛИ. Выход формирователя цикловых импульсов совместно подключен к первому входу первого элемента И, первому входу элемента запрета, и входу счетчика циклов. Выход счетчика циклов подключен к входу управления счетчика искаженных синхросигналов. Выход счетчика искаженных синхросигналов совместно подключен к адресным входам блока выбора допустимого числа неискаженных синхросимволов, блока выбора порога и блока выбора коэффициента счета. Выход блока выбора допустимого числа неискаженных синхросимволов подключен к входу управления опознавателя синхросигнала. Выход элемента запрета совместно подключен к счетным входам счетчика по выходу из синхронизма и счетчика искаженных синхросигналов. Выход первого элемента И подключен к первому входу элемента ИЛИ, выход которого подключен к входу сброса счетчика по выходу из синхронизма. К входу данных счетчика по выходу из синхронизма подключен выход блока выбора коэффициента счета. Тактовый вход формирователя цикловых импульсов объединен с тактовыми входами опознавателя синхросигнала, блока регистров сдвига и решающего узла. Управляющий вход решающего узла соединен с выходом блока выбора порога, а дополнительный вход управления решающего узла соединен с выходом счетчика по выходу из синхронизма. При этом сигнальный вход опознавателя синхросигнала, тактовый вход формирователя цикловых импульсов и выход формирователя цикловых импульсов являются соответственно сигнальным входом, тактовым входом и выходом устройства.

Технический результат при осуществлении изобретения - повышение надежности работы устройства для синхронизации по циклам - достигается введением в решающий узел третьего элемента И, а также второго элемента ИЛИ. При этом выход счетчика сравнения подключен также к первому входу третьего элемента И, а второй вход третьего элемента И подключен к выходу устройства. Выход третьего элемента И подключен ко второму входу второго элемента ИЛИ, к первому входу которого подключен выход второго элемента И. Выход второго элемента ИЛИ подключен ко входу сброса блока памяти. Выход второго элемента ИЛИ является выходом решающего узла. Благодаря введению в решающий узел третьего элемента И, а также второго элемента ИЛИ повышается надежность работы устройства для синхронизации по циклам, т.к. в синхронном режиме работы при обнаружении истинного синхросигнала не происходит переполнения блока регистров сдвига. Сброс блока регистров сдвига осуществляется сигналом синхронизации, сформированным на выходе второго элемента ИЛИ. Факт обнаружения решающим узлом в режиме синхронизма именно истинного синхросигнала определяется с помощью третьего элемента И. При одновременном поступлении сигналов с выхода счетчика сравнения и с выхода устройства синхронизации по циклам на входы третьего элемента И на его выходе формируется сигнал синхронизации. При этом с помощью второго элемента ИЛИ осуществляется операция проключения на выход решающего узла сигнала синхронизации, сформированного или в режиме сбоя синхронизма (с выхода второго элемента И), или в синхронном режиме работы (с выхода третьего элемента И).

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволили установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Выбор из перечня выявленных аналогов прототипа, как наиболее близкого по совокупности существенных признаков аналога, позволил выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявленное изобретение соответствует критерию "новизна".

Для проверки соответствия заявленного изобретения критерию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, определенного заявителем. Не выявлено влияние преобразований, предусматриваемых существенными признаками заявленного изобретения, на достижение технического результата. В частности, заявленным изобретением не предусматриваются следующие преобразования: дополнение известного средства какой-либо известной частью, присоединяемой к нему по известным правилам, для достижения технического результата, в отношении которого установлено влияние именно таких дополнений; замену какой-либо части известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены; исключение какой-либо части средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата; увеличение однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов; выполнение известного средства или его части из известного материала для достижения технического результата, обусловленного известными свойствами материала; создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций и достигаемый при этом технический результат обусловлен только известными свойствами частей этого объекта и связей между ними; изменение количественных признаков или взаимосвязи признаков, если известен факт влияния каждого из них на технический результат и новые значения признаков или их взаимосвязь могли быть получены из известных зависимостей. Следовательно, заявленное изобретение соответствует критерию "изобретательский уровень".

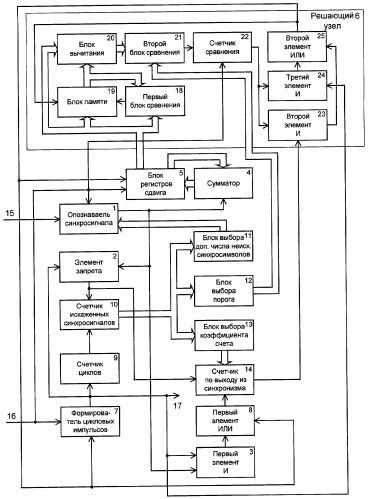

Изобретение поясняется чертежом, на котором представлена структурная схема устройства для синхронизации по циклам. Сведения, подтверждающие возможность осуществления изобретения с получением вышеуказанного технического результата, заключаются в следующем.

Устройство для синхронизации по циклам содержит опознаватель 1 синхросигнала, элемент 2 запрета, элемент 3 И, сумматор 4, блок 5 регистров сдвига, решающий узел 6, формирователь 7 цикловых импульсов, элемент 8 ИЛИ, счетчик 9 циклов, счетчик 10 искаженных синхросигналов, блок 11 выбора допустимого числа неискаженных синхросимволов, блок 12 выбора порога, блок 13 выбора коэффициента счета, счетчик 14 по выходу из синхронизма, вход 15 сигнальный, вход 16 тактовый, выход 17 устройства. Решающий узел 6 содержит блок 18 сравнения, блок 19 памяти, блок 20 вычитания, блок 21 сравнения, счетчик 22 сравнения, элемент 23 И, элемент 24 И, а также элемент 25 ИЛИ. Выход опознавателя 1 синхросигнала совместно соединен со вторым входом элемента 2 запрета, вторым входом элемента 3 И, а также с первым входом сумматора 4, выход которого подключен к сигнальному входу блока 5 регистров сдвига. Основной выход блока 5 регистров сдвига подключен ко второму входу сумматора 4, а дополнительный выход - к сигнальному входу решающего узла 6. Сигнальным входом решающего узла 6 является первый вход блока 18 сравнения. При этом выход блока 18 сравнения подключен к входу управления блока 19 памяти, выход которого подключен ко второму входу блока 18 сравнения и первому входу блока 20 вычитания. Второй вход блока 20 вычитания объединен с входом данных блока 19 памяти, первым входом блока 18 сравнения и является сигнальным входом решающего узла 6. Выход блока 20 вычитания подключен ко второму входу блока 21 сравнения, выход которого соединен с входом сброса счетчика 22 сравнения. Выход счетчика 22 сравнения совместно подключен ко второму входу элемента 23 И, а также к первому входу элемента 24 И. Выход элемента 23 И подключен к первому входу элемента 25 ИЛИ, ко второму входу которого подключен выход элемента 24 И. Выход элемента 25 ИЛИ подключен к входу сброса блока 19 памяти. При этом управляющим и тактовым входами решающего узла 6 являются соответственно первый вход блока 21 сравнения и тактовый вход счетчика 22 сравнения. Первым дополнительным входом управления решающего узла 6 является первый вход элемента 23 И. Вторым дополнительным входом управления решающего узла 6 является второй вход элемента 24 И. Выходом решающего узла 6 является выход элемента ИЛИ, который подключен к входам сброса формирователя 7 цикловых импульсов, блока 5 регистров сдвига, а также ко второму входу элемента 8 ИЛИ. Выход формирователя 7 цикловых импульсов совместно подключен к первому входу элемента 3 И, первому входу элемента 2 запрета, входу счетчика 9 циклов, и второму дополнительному входу управления решающего узла 6. Выход счетчика 9 циклов подключен к входу управления счетчика 10 искаженных синхросигналов. Выход счетчика 10 искаженных синхросигналов совместно подключен к адресным входам блока 11 выбора допустимого числа неискаженных синхросимволов, блока 12 выбора порога и блока 13 выбора коэффициента счета. Выход блока 11 выбора допустимого числа неискаженных синхросимволов подключен к входу управления опознавателя 1 синхросигнала. Выход элемента 2 запрета совместно подключен к счетным входам счетчика 14 по выходу из синхронизма и счетчика 10 искаженных синхросигналов. Выход элемента 3 И подключен к первому входу элемента 8 ИЛИ, выход которого подключен к входу сброса счетчика 14 по выходу из синхронизма. К входу данных счетчика 14 по выходу из синхронизма подключен выход блока 13 выбора коэффициента счета. Тактовый вход формирователя 7 цикловых импульсов объединен с тактовыми входами опознавателя 1 синхросигнала, блока 5 регистров сдвига и решающего узла 6. Управляющий вход решающего узла 6 соединен с выходом блока 12 выбора порога, а первый дополнительный управляющий вход решающего узла 6 соединен с выходом счетчика 14 по выходу из синхронизма. При этом сигнальный вход опознавателя 1 синхросигнала, тактовый вход формирователя 7 цикловых импульсов и выход формирователя 7 цикловых импульсов являются соответственно сигнальным входом 15, тактовым входом 16 и выходом 17 устройства.

Устройство синхронизации по циклам работает следующим образом. На сигнальный вход опознавателя 1 синхросигнала поступает групповой цифровой сигнал, содержащий детерминированные группы синхросигнала, повторяющиеся с частотой следования циклов. На информационных позициях группового сигнала кодовые группы информационных символов, идентичные синхрогруппе, формируются случайно. При поступлении на вход опознавателя 1 синхросигнала комбинации со структурой синхрогруппы на его выходе формируется отклик в виде "единичного" импульса, поступающего далее на первый вход сумматора 4, второй вход элемента 2 запрета и второй вход элемента 3 И. На вход управления опознавателя 1 синхросигнала с выхода блока 11 подается допустимое число k неискаженных синхросимволов. Опознаватель 1 синхросигнала состоит из регистра сдвига, дешифратора синхросигнала, кодера и устройства сравнения. Регистр сдвига осуществляет операцию преобразования группового цифрового сигнала, поступающего на информационный вход регистра сдвига, из последовательности в параллельный код. В течение каждого тактового интервала в регистр сдвига записывается один символ принимаемого сигнала, причем с приходом очередного символа предыдущий продвигается в следующую ячейку регистра сдвига. Таким образом, за m тактовых интервалов в регистр записывается m-символьная кодовая комбинация (где m - количество символов в синхрогруппе). С выхода регистра сдвига групповой сигнал в параллельном коде подается на вход дешифратора синхросигнала. Дешифратор настроен на распознание синхросигнала. К выходу дешифратора подключен кодер. Кодер предназначен для формирования двоичного кода числа безошибочно обнаруженных синхросимволов. Сравнивающее устройство осуществляет операцию сравнения числа безошибочно обнаруженных синхросимволов в синхрогруппе с допустимым числом k неискаженных синхросимволов. Если число безошибочно обнаруженных синхросимволов больше или равно допустимого числа k неискаженных синхросимволов, то на выходе опознавателя 1 синхросигнала формируется "единичный" сигнал (отклик). В противном случае на выходе опознавателя 1 формируется "нулевой" сигнал. Опознаватель 1 синхросигнала может быть реализован, например, как описано в описании изобретения к патенту РФ № 2231228 класса Н 04 L 7/08, опубл. 20.06.2004, Бюл. № 17, фиг.2.

Сумматор 4 представляет собой параллельный комбинационный сумматор, у которого младший разрядный вход первого слагаемого (младшие разряды n-разрядного входа) и n-разрядных входов второго слагаемого являются соответственно первым и вторым входом сумматора, при этом другие (n-1)-разрядные входы первого слагаемого подключены к источнику "нулевого" уровня.

Блок 5 регистров сдвига включает в себя n N-разрядных (n=[log2N]+1, N - число позиций в одном цикле) регистров сдвига. При этом объединенные тактовые входы и объединенные входы сброса регистров сдвига являются соответственно тактовым входом и входом сброса блока 5 регистров сдвига, а сигнальные входы, выходы последних разрядов и выходы первых разрядов всех регистров сдвига являются соответственно сигнальным входом, основным выходом и дополнительным выходом бока 5 регистров сдвига. Таким образом, отклик опознавателя 1 синхросигнала, имеющий место в i-м тактовом интервале, складывается в сумматоре 4 с результатом предыдущего счета откликов на i-й позиции цикла, поступающим с основного выхода блока 5 регистров сдвига. Новый результат счета откликов, больший на единицу прежнего, записывается в виде n-разрядного двоичного числа в соответствующие первые ячейки (разряды) регистров сдвига блока 5 регистров сдвига. При этом двоичное число, записанное до этого в первые ячейки блока 5 регистров сдвига, а также все остальные числа, хранящиеся в последующих однотипных ячейках, параллельно сдвигаются на один разряд, и с основного выхода блока 5 регистров сдвига на второй вход сумматора 4 поступает результат счета откликов - на (i+1)-м тактовом интервале. Если отклик опознавателя 1 синхросигнала на (i+1)-м тактовом интервале отсутствует, то прежний результат счета откликов на (i+1)-й позиции цикла переписывается в первые ячейки блока 5 регистров сдвига, а остальные числа, хранящиеся в однотипных ячейках блока 5 регистров сдвига, сдвигаются на один разряд и т.д. Блок 5 регистров сдвига обеспечивает запоминание результатов счета откликов на каждой позиции цикла в течение длительности цикла. При этом величина n определяет емкость памяти результатов счета. Одновременно результаты счета откликов на каждой из позиций цикла с дополнительного выхода блока 5 регистров сдвига последовательно поступают на сигнальный вход решающего узла 6. В решающем узле 6, например в i-м тактовом интервале, входное двоичное число в параллельном коде, представляющее текущий результат счета откликов на i-й позиции цикла, одновременно подается на первый вход блока 18 сравнения, вход данных блока 19 памяти и второй вход блока 20 вычитания. В блоке 18 сравнения входное число сравнивается с двоичным числом, хранящимся в блоке 19 памяти, и если оно превышает число блока 19 памяти, то на выходе блока 18 сравнения формируется импульс, который, поступая на вход управления блока 19 памяти, обеспечивает стирание прежнего и запись нового (входного) числа. После этого на входах блока 18 сравнения оказываются равные двоичные числа. Если же входное число равно или меньше числа, хранящегося в блоке 19 памяти, то содержимое последнего не изменяется. Таким образом, в блок 19 памяти переписывается наибольший текущий результат счета откликов на какой-либо позиции цикла, который далее сравнивается с результатами счета на последующих позициях цикла. Получающаяся разность (между числом блока 19 памяти и входным числом) на выходе блока 20 вычитания в виде двоичного числа в параллельном коде сравнивается в блоке 21 сравнения с пороговым числом d, поступающим на первый его вход (являющийся управляющим входом решающего узла 6) с выхода блока 12 выбора порога. При этом если число с выхода блока 20 вычитания меньше порогового числа d, то с выхода второго блока 21 сравнения на вход сброса счетчика 22 сравнения подается "единичный" (запрещающий) потенциал, который устанавливает и удерживает его в "нулевом" состоянии. Когда в i-м тактовом интервале число с выхода блока 20 вычитания равно или больше числа d, с выхода второго блока 21 сравнения поступает "нулевой" (разрешающий) потенциал, и счетчик 22 сравнения производит счет одного тактового импульса, поступающего на его тактовый вход, являющийся тактовым входом решающего узла 6. Если наибольшее двоичное число, записанное в блок 19 памяти, будет превышать каждое из N-1 последующих чисел, поступающих друг за другом с дополнительного выхода блока 5 регистров сдвига, на величину, равную или большую порогового числа d, то счетчик 22 сравнения произведет счет следующих подряд N тактовых импульсов. После чего на его выходе формируется "единичный" импульсный сигнал, который поступает на второй вход элемента 23 И, а также на первый вход элемента 24 И. При этом, если счетчик 14 по выходу из синхронизма произвел подсчет α раз подряд "неопознание" истинной синхрогруппы, то на его выходе формируется сигнал логической "единицы", который поступает на первый вход элемента 23 И, разрешая прохождение "единичного" импульсного сигнала с выхода счетчика сравнения на выход элемента 23 И. Прохождение "единичного" импульсного сигнала с выхода счетчика сравнения на выход элемента 24 И осуществляется при поступлении с выхода формирователя 7 цикловых импульсов сигнала цикловой синхронизации. Элемент 25 ИЛИ осуществляет проключение "единичного" импульсного сигнала на выход решающего узла 6 или с выхода элемента 23 И, или с выхода элемента 24 И. Сигнал на выходе решающего узла 6 является выходным сигналом синхронизации. При этом в первом случае сигнал синхронизации на выходе решающего узла 6 формируется при потере состояния синхронизма (потеря состояния синхронизма определяется счетчиком 14 по выходу из синхронизма). Во втором случае выходной сигнал синхронизации формируется в синхронном режиме работы. Сигнал синхронизации с выхода решающего узла 6 поступает на входы сброса блока 19 памяти, блока 5 регистров сдвига и формирователя 7 цикловых импульсов, а также на второй вход элемента 8 ИЛИ. В результате блок 19 памяти, блок 5 регистров сдвига и счетчик 14 по выходу из синхронизма сбрасываются в "нуль". После чего с выхода блока 21 сравнения начинает поступать запрещающий "единичный" потенциал и счетчик 22 сравнения также сбрасывается в "нуль". Выходным сигналом синхронизации решающего узла 6 производится фазирование формирователя 7 цикловых импульсов таким образом, что на выход 17 устройства начинают поступать регулярно следующие цикловые импульсы, по времени совпадающие с откликами опознавателя 1 синхросигнала на истинные синхрогруппы. Далее процесс поиска временного положения циклового синхросигнала в двоичном потоке группового сигнала начинается заново. При этом следующий сигнал синхронизации решающего узла 6 будет сформирован при условии обнаружения синхросигнала после потери состояния синхронизма ("единичный" импульс на выходе элемента 23 И) или в синхронном состоянии ("единичный" импульс на выходе элемента 24 И). В первом случае сигналы синхронизации решающего узла 6 будут изменять фазу начальной установки формирователя 7 цикловых импульсов. Во втором случае фаза начальной установки формирователя 7 цикловых импульсов изменяться не будет. Сбой состояния синхронизма может произойти если временное положение циклового синхросигнала изменилось или синхросигнал α раз подряд искажен (более чем на k синхросимволов). Таким образом, счетчик 14 по выходу из синхронизма подсчитывает количество следующих подряд импульсов сбоя синхросигнала, формируемых элементом 2 запрета. При достижении состояния счета α на выходе счетчика 14 по выходу из синхронизма появляется сигнал разрешения формирования решающим узлом 6 сигнала синхронизации. При этом при обнаружении истинного синхросигнала или формировании на выходе решающего узла 6 сигнала синхронизации счетчик 14 по выходу из синхронизма сбрасывается в "нуль". Блоки 18 и 21 сравнения могут быть выполнены, например, в виде n-разрядных компараторов двоичных кодов, формирующих признак "больше", "меньше" при соответствующем знаке разницы значений входных операндов, а также признак их равенства, подаваемых на первый и второй входы блоков. Блок 19 памяти может быть выполнен в виде n-разрядного регистра с параллельным входом. При этом входом данных, входом управления, входом сброса и выходом блока 19 памяти является соответственно вход данных, тактовый вход, вход сброса и выход данных n-разрядного регистра. Блок 20 вычитания может быть выполнен в виде полного n-разрядного параллельного сумматора. Разрядность сумматора обеспечивается последовательным соединением выхода переноса сумматора младших разрядов с входом переноса сумматора старших разрядов. Для выполнения сумматором операции вычитания число с блока 20 памяти, поступающее на первый вход блока вычитания, подвергается инверсии, а число, поступающее с дополнительного выхода блока 3 регистров сдвига на второй вход блока вычитания, инверсии не подвергается. Формирователь 7 цикловых импульсов и счетчик 22 сравнения и могут быть выполнены в виде последовательно соединенных двоично-десятичного синхронного счетчика и дешифратора (см., например, как описано в описании изобретения к патенту РФ № 2231228 класса Н 04 L 7/08, опубл. 20.06.2004, Бюл. № 17, фиг.3).

Счетчик 14 по выходу из синхронизма представляет собой двоично-десятичный синхронный счетчик импульсов, к выходу которого подключен первый вход компаратора двоичных чисел. Счетчик предназначен для подсчета следующих подряд импульсов сбоя синхросигнала, которые поступают с выхода элемента 2 запрета на тактовый вход счетчика. Компаратор предназначен для распознания достижения счетчиком состояния максимального счета, равного коэффициенту счета α, который с блока 13 выбора коэффициента счета подается в двоичном коде на второй вход компаратора. На вход сброса счетчика с выхода элемента 8 ИЛИ поступают импульсы опознания истинного синхросигнала или импульс синхронизации. Для запоминания сигнала состояния максимального накопления счетчиком 14 по выходу из синхронизма к выходу компаратора установочным входом должен быть подключен триггер. Сброс счетчика и триггера в "нулевое" состояние осуществляется при поступлении на вход сброса счетчика 14 по выходу из синхронизма сигнала "сброс". Выход триггера является выходом счетчика 14 по выходу из синхронизма. Счетчик 14 по выходу из синхронизма может быть реализован, например, как описано в описании изобретения к патенту РФ № 2231228 класса Н 04 L 7/08, опубл. 20.06.2004, Бюл. № 17, фиг.4.

Процесс формирования пороговых чисел d для решающего узла 6, допустимого числа k неискаженных синхросимволов для опознавателя 1 синхросигнала и коэффициента счета α для счетчика 14 по выходу из синхронизма производится следующим образом. На первый вход элемента 3 запрета поступают импульсы формирователя 7 цикловых импульсов, а на второй его вход - импульсы (отклики) опознавателя 1 синхросигнала. В результате на выход элемента 2 запрета пройдут только те импульсы формирователя 7 цикловых импульсов, которые соответствуют искаженным синхросигналам принимаемой двоичной информационной последовательности. Подсчитывая число R искаженных синхросимволов в течение времени счета довольно большого числа цикловых импульсов, можно с определенной степенью точности периодически определять вероятность (частость) ошибочн