Устройство для параметрической оценки закона распределения потоков сообщений

Иллюстрации

Показать всеИзобретение относится к радиотехнике и вычислительной технике. Технический результат заключается в повышении достоверности параметрической оценки закона распределения потоков сообщений. Устройство для параметрической оценки закона распределения потоков сообщений содержит входной усилитель, блок вычисления параметров, блок вычисления средних арифметических значений, блок определения типа распределения, вычислитель распределения, блок управления, блок анализа интенсивности, блок анализа признака пакета, блок преобразования вида признака пакета и позволяет с высокой достоверностью оценивать параметры распределения однородных и неоднородных (смешанных) потоков многопакетных сообщений, опознавательные признаки пакетов которых (признаки начала и окончания информационной части пакетов) могут идентифицироваться как количественно, так и качественно - неоднозначно, нечетко, с привлечением лингвистической переменной, за счет сравнительного анализа в блоке поступающих в двоичном коде битовых последовательностей с точки зрения их соответствия признакам пакетов, соответствующих использующемуся протоколу обмена и принятия решения о логико-математической природе их идентификационных атрибутов, математически корректного, на основе методов теории нечетких множеств, преобразования в блоке исходных данных, характеризующих признаки пакетов и идентифицированных в нечеткой форме к виду, пригодному для параметрического оценивания закона распределения потоков сообщений. 2 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к радиотехнике и вычислительной технике и предназначено для параметрической оценки закона распределения потоков многопакетных сообщений в средствах многоканальной (спутниковой, радиорелейной, тропосферной) радиосвязи и в средствах обработки и передачи данных локальных вычислительных сетей (ЛВС), объединенных в цифровую телекоммуникационную сеть (ТКС).

Известно устройство для параметрической оценки закона распределения, содержащее входной усилитель, блок памяти, блок проверки согласия, блок управления и синтезатор функции распределения (см. авт. св. СССР №1024935, G 06 F 15/36, G 06 G 7/52, 1983, бюл.23).

Недостатком данного устройства является низкий уровень быстродействия при его использовании для оценки распределения потоков многопакетных сообщений (МПС) в ТКС с интеграцией служб, обусловленный необходимостью перебора множества М сочетаний параметров распределения потока сообщений, состоящих из множества пакетов.

Известно устройство для параметрической оценки закона распределения потоков сообщений, содержащее входной усилитель, блок вычисления параметров, блок вычисления средних арифметических значений, блок определения типа распределения, вычислитель распределения и блок управления (см. патент РФ №2094844, G 06 F 17/18, 1997, бюл.30).

Однако данное устройство имеет узкую область применения, поскольку с его помощью невозможно производить оценку закона распределения неоднородных (смешанных) потоков МПС, имеющих место в ТКС с интеграцией служб и обусловленных наличием в ней источника информации, выдающего как явно выраженные независимые одиночные информационные сообщения пользователя (ИСП), так и пачки ИСП, длины которых распределены по геометрическому закону. В этом случае при аппроксимации реальной статистики входящих потоков ИСП невозможно свести их к трем классическим модификациям потоков сообщений.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство для параметрической оценки закона распределения потоков сообщений (см. патент РФ №2165100, 7 G 06 F 17/18, 2001, бюл.10), содержащее входной усилитель, на вход которого подана бинарная импульсная последовательность, блок вычисления параметров, блок вычисления средних арифметических значений, блок определения типа распределения, вычислитель распределения, блок управления и блок анализа интенсивности, причем тактовый выход блока управления подключен к тактовому входу вычислителя распределения, обнуляющий и управляющий выходы блока управления соединены соответственно с обнуляющим и управляющим входами блока вычисления параметров, информационный вход которого соединен с выходом входного усилителя, первый и второй информационные выходы блока вычисления параметров подключены соответственно к первому и второму информационным входам блока вычисления средних арифметических значений, первый информационный выход которого соединен с первым информационным входом вычислителя распределения и с входом блока определения типа распределения, первый, второй и третий модификационные выходы которого подключены соответственно к первому, второму и третьему модификационным входам вычислителя распределения, второй информационный вход которого соединен со вторым информационным выходом блока вычисления средних арифметических значений, выход вычислителя распределения является выходом устройства, вход блока анализа интенсивности подключен ко второму информационному выходу блока вычисления параметров, первый и второй параметрические выходы блока анализа интенсивности соединены соответственно с первым и вторым параметрическими входами вычислителя распределения, управляющий выход блока анализа интенсивности подключен к управляющему входу блока вычисления средних арифметических значений.

В прототипе реализуется возможность оценки параметров распределения (интенсивности сообщений - λс и соотношения информационных длин пакетов и сообщений - ξ) как однородных, так и неоднородных (смешанных) потоков МПС - потоков, периодически меняющих свою интенсивность в ходе функционирования ТКС с интеграцией служб, тем самым осуществляется расширение области применения устройства.

Однако прототип имеет недостаток - относительно низкую достоверность оценивания в условиях, присущих реальному процессу функционирования ТКС с интеграцией служб - в условиях неоднозначности (нечеткости) параметров циркулирующих потоков многопакетных сообщений. Данное устройство позволяет с высокой достоверностью оценивать параметры распределения лишь тех однородных и неоднородных (смешанных) потоков МПС, исходные признаки пакетов которых (начала и окончания информационной части пакетов) заданы количественно, идентифицируются четко и однозначно, в то время как признаки начала и окончания информационной части пакетов МПС для большого количества высокоскоростных потоков сообщений, реально циркулирующих в вычислительных и иных телекоммуникационных сетях могут быть идентифицированы лишь качественно - неоднозначно, нечетко, с привлечением лингвистической переменной.

Под «признаками» пакетов потока сообщений понимается установленные и традиционные для конкретного протокола обмена в ТКС с интеграцией служб атрибуты заголовка пакета - количество бит флага начала и окончания информационной части пакета, очередность и интенсивность их следования в рамках заголовков.

Анализ работ [1-6] и результаты исследований реальных потоков сообщений [7-9] показывают, что входной поток пакетов МПС пользователей, присущий существующим ТКС с интеграцией служб, характеризуется как количественными, так и качественными признаками. Ему присуща недостоверность, нечеткая (размытая) априорная неопределенность, обуславливающая отсутствие четких границ признаков начала информационной части пакета и окончания информационной части пакета. Особенно это характерно для МПС, когда разнородный групповой поток передается по сети такого класса с высокой скоростью. В этих условиях достаточно трудно однозначно (четко) идентифицировать принадлежность ключевых признаков, таких как интенсивность появления флага начала пакета - признака заголовка пакета, количества бит символов начала и окончания информационной части пакета, к пространству признаков.

При анализе параметров λс и ξ, в рамках оценки закона распределения потоков сообщений, все ярко выраженные и четко идентифицируемые признаки пакетов могут быть однозначно зафиксированы и численно описаны с использованием количественной меры, тогда как неоднозначно идентифицируемые признаки требуют, во избежание ошибок оценивания, верификации, дополнительной проверки истинности, которая возможна на качественном уровне. Это подразумевает верификацию неоднозначно (нечетко) идентифицируемых признаков пакетов, опираясь на математический аппарат теории нечетких множеств, с привлечением идентификационных критериев для верификации признаков пакетов, сформулированных в виде лингвистической переменной типа: «признак явно не принадлежит к пространству признаков» - «очень слабая степень принадлежности данного признака к пространству признаков» - «слабая степень принадлежности к пространству признаков» - «принадлежность и непринадлежность к пространству признаков равновозможны» - «высокая степень принадлежности к пространству признаков» - «очень высокая степень принадлежности к пространству признаков» - «данный признак пакета явно принадлежит к пространству признаков» и т.п. Математическим аналогом таких лингвистических переменных является функция принадлежности нечетких множеств, записываемая, как и имеющая физический смысл степени (уровня) уверенности в принадлежности признака к пространству признаков. Вместе с тем исходные данные с нечетко идентифицируемыми признаками, используемые для оценивания закона распределения потоков сообщений, по мнению авторов работ [1-6], составляют 40...50% от общего перечня всех исходных данных, необходимых для осуществления оценивания реальных потоков с высокой степенью достоверности. Иными словами, не учет параметров потока пакетов, идентифицируемых нечетко, облегчает задачу оценивания, однако резко снижает уровень достоверности результатов и, как следствие, снижает обоснованность принимаемых решений по управлению информационными потоками в ТКС с интеграцией служб.

Целью предлагаемого изобретения является создание устройства для параметрической оценки закона распределения потоков сообщений, обеспечивающего повышение достоверности оценивания в условиях, присущих реальному процессу функционирования ТКС с интеграцией служб - в условиях неоднозначности (нечеткости) параметров циркулирующих потоков многопакетных сообщений, устройства, способного с высокой достоверностью оценивать параметры распределения однородных и неоднородных (смешанных) потоков МПС, опознавательные признаки пакетов которых (признаки начала и окончания информационной части пакетов) могут идентифицироваться как количественно, так и качественно - неоднозначно, нечетко, с привлечением лингвистической переменной.

Указанная цель достигается тем, что в известное устройство для параметрической оценки закона распределения потоков сообщений, содержащее входной усилитель, вход которого является входом устройства, блок вычисления параметров для определения текущих значений интенсивности сообщений и соотношения информационных длин пакетов и сообщений, блок вычисления средних арифметических значений для получения численных значений усредненных за интервал наблюдения параметров потока, блок определения типа распределения, вычислитель распределения, блок анализа интенсивности для текущего оценивания и сравнения значений отсчетов параметра интенсивности входного потока и блок управления для регулировки интервала наблюдения, длины пакета и количества пакетов, тактовый выход которого подключен к тактовому входу вычислителя распределения, обнуляющий и управляющий выходы блока управления соединены соответственно с обнуляющим и управляющим входами блока вычисления параметров, первый и второй информационные выходы которого подключены соответственно к первому и второму информационным входам блока вычисления средних арифметических значений, первый информационный выход которого соединен с первым информационным входом вычислителя распределения и с входом блока определения типа распределения, первый, второй и третий модификационные выходы которого подключены соответственно к первому, второму и третьему модификационным входам вычислителя распределения, второй информационный вход которого соединен со вторым информационным выходом блока вычисления средних арифметических значений, выход вычислителя распределения является выходом устройства, вход блока анализа интенсивности подключен к второму информационному выходу блока вычисления параметров, первый и второй параметрические выходы блока анализа интенсивности соединены соответственно с первым и вторым параметрическими входами вычислителя распределения, управляющий выход блока анализа интенсивности подключен к управляющему входу блока вычисления средних арифметических значений, дополнительно введены блок анализа признака пакета и блок преобразования вида признака пакета, причем выход входного усилителя соединен с информационным входом блока анализа признака пакета, нечеткий признаковый выход которого подключен к входу блока преобразования вида признака пакета, выход которого соединен с возвратным признаковым входом блока анализа признака пакета, четкий признаковый выход которого подключен к информационному входу блока вычисления параметров.

Блок анализа признака пакета состоит из анализатора количества бит заголовка пакета, анализатора очередности бит заголовка пакета, анализатора интенсивности бит заголовка пакета, анализатора совпадений признаков и верификатора, причем вход анализатора количества бит заголовка пакета является информационным входом блока и соединен с входом анализатора очередности бит заголовка пакета и с входом анализатора интенсивности бит заголовка пакета, выходы анализатора количества бит заголовка пакета, анализатора очередности бит заголовка пакета и анализатора интенсивности бит заголовка пакета подключены соответственно к первому, второму и третьему признаковым входам анализатора совпадений признаков, нечеткий выход которого соединен с главным входом верификатора и является нечетким признаковым выходом блока, четкий выход анализатора совпадений признаков соединен с выходом верификатора и является четким признаковым выходом блока анализа признака пакета, а второстепенный вход верификатора является возвратным признаковым входом блока анализа признака пакета.

Блок преобразования вида признака пакета состоит из счетчика, вычислителя дополнения, основного и вспомогательного запоминающих элементов, основного и вспомогательного вычислителей пересечения, вычислителя объединения и анализатора функции α-уровня, выход которого является выходом блока, а вход счетчика является входом блока, первый и второй выходы счетчика соединены соответственно с входом основного запоминающего элемента и прямым входом вспомогательного запоминающего элемента, а также соответственно с первым и вторым входами вычислителя дополнения, выходы основного и вспомогательного запоминающих элементов подключены соответственно к главным входам основного и вспомогательного вычислителей пересечения, к дополнительным входам основного и вспомогательного вычислителей пересечения подключены соответственно первый и второй выходы вычислителя дополнения, выходы основного и вспомогательного вычислителей пересечения подключены соответственно к первому и второму входам вычислителя объединения, выход которого соединен с дополнительным входом вычислителя дополнения, дополнительным входом вспомогательного запоминающего элемента и входом анализатора функции α-уровня.

Благодаря новой совокупности существенных признаков за счет введения блоков анализа признака пакета и преобразования вида признака пакета, обеспечивающих сравнительный анализ поступающих в двоичном коде битовых последовательностей с точки зрения их соответствия признакам пакетов, использующихся протоколом обмена, и преобразование нечетко идентифицированных признаков пакетов, в заявленном устройстве достигается возможность верификации признаков пакетов и приведения признаков пакетов, идентифицированных в нечеткой форме к виду, пригодному для параметрического оценивания закона распределения потоков сообщений, что обуславливает повышение достоверности оценивания в условиях, присущих реальному процессу функционирования ТКС с интеграцией служб - в условиях неоднозначности (нечеткости) параметров циркулирующих потоков многопакетных сообщений.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявленное устройство поясняется чертежами, на которых представлены:

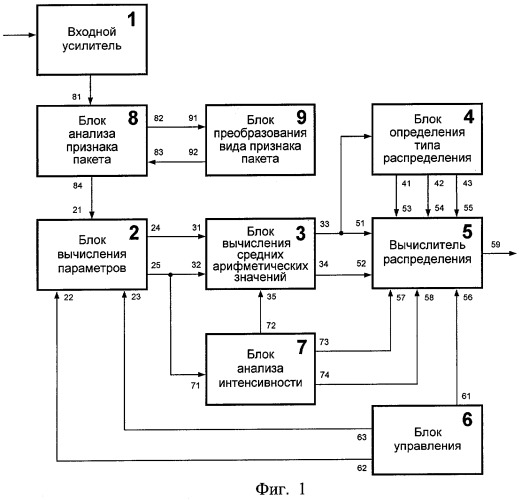

на фиг.1 - структурная схема устройства для параметрической оценки закона распределения потоков сообщений;

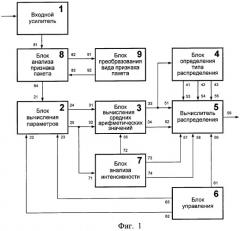

на фиг.2 - структурная схема блока анализа признака пакета;

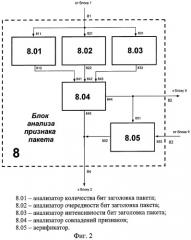

на фиг.3 - структурная схема верификатора;

на фиг.4 - структурная схема блока преобразования вида признака пакета;

на фиг.5 - структурная схема блока вычисления параметров;

на фиг.6 - структурная схема блока вычисления средних арифметических значений;

на фиг.7 - структурная схема блока определения типа распределения;

на фиг.8 - структурная схема вычислителя распределения;

на фиг.9 - структурная схема блока управления;

на фиг.10 - структурная схема блока анализа интенсивности.

Устройство для параметрической оценки закона распределения потоков сообщений, изображенное на фиг.1, состоит из входного усилителя 1, вход которого является входом устройства, блока вычисления параметров 2, блока вычисления средних арифметических значений 3, блока определения типа распределения 4, вычислителя распределения 5, блока управления 6, блока анализа интенсивности 7, блока анализа признака пакета 8 и блока преобразования вида признака пакета 9. Тактовый выход 61 блока управления 6 подключен к тактовому входу 56 вычислителя распределения 5, обнуляющий 62 и управляющий 63 выходы блока управления 6 соединены соответственно с обнуляющим 22 и управляющим 23 входами блока вычисления параметров 2, первый 24 и второй 25 информационные выходы которого подключены соответственно к первому 31 и второму 32 информационным входам блока вычисления средних арифметических значений 3, первый информационный выход 33 которого соединен с первым информационным входом 51 вычислителя распределения 5 и с входом блока определения типа распределения 4, первый 41, второй 42 и третий 43 модификационные выходы которого подключены соответственно к первому 53, второму 54 и третьему 55 модификационным входам вычислителя распределения 5, второй информационный вход 52 которого соединен со вторым информационным выходом 34 блока вычисления средних арифметических значений 3. Выход 59 вычислителя распределения 5 является выходом устройства, вход 71 блока анализа интенсивности 7 подключен к второму информационному выходу 25 блока вычисления параметров 2, первый 73 и второй 74 параметрические выходы блока анализа интенсивности 7 соединены соответственно с первым 57 и вторым 58 параметрическими входами вычислителя распределения 5. Управляющий выход 72 блока анализа интенсивности 7 подключен к управляющему входу 35 блока вычисления средних арифметических значений 3. Выход входного усилителя 1 соединен с информационным входом 81 блока анализа признака пакета 8, нечеткий признаковый выход 82 которого подключен к входу 91 блока преобразования вида признака пакета 9, выход 92 которого соединен с возвратным признаковым входом 83 блока анализа признака пакета 8, четкий признаковый выход 84 которого подключен к информационному входу 21 блока вычисления параметров 2.

Блок анализа признака пакета 8 (фиг.2) предназначен для осуществления процедуры последовательного сравнения поступающих в двоичном коде битовых последовательностей с точки зрения их соответствия признакам пакетов (количество бит, очередность и интенсивность следования бит флага начала (окончания) информационной части пакета), соответствующих использующемуся и заранее известному для данной ТКС протоколу обмена и принятия решения о логико-математической природе их идентификационных атрибутов - признаки пакета в данной битовой последовательности идентифицируются однозначно и соответствуют исходным (эталонным) признакам, либо признаки пакета идентифицируются неоднозначно (нечетко, могут быть описаны с привлечением лингвистической переменной) и требуется дополнительная верификация, математически корректная обработка и проверка их однозначной принадлежности к эталонному множеству идентификационных признаков.

Блок анализа признака пакета 8 состоит из анализатора количества бит заголовка пакета 8.01, анализатора очередности бит заголовка пакета 8.02, анализатора интенсивности бит заголовка пакета 8.03, анализатора совпадений признаков 8.04 и верификатора 8.05. Вход 811 анализатора количества бит заголовка пакета 8.01 является информационным входом 81 блока 8 и соединен с входом 821 анализатора очередности бит заголовка пакета 8.02 и с входом 831 анализатора интенсивности бит заголовка пакета 8.03. Выходы 812, 822 и 832 анализатора количества бит заголовка пакета 8.01, анализатора очередности бит заголовка пакета 8.02 и анализатора интенсивности бит заголовка пакета 8.03 подключены соответственно к первому 841, второму 842 и третьему 843 признаковым входам анализатора совпадений признаков 8.04, нечеткий выход 844 которого соединен с главным входом 851 верификатора 8.05 и является нечетким признаковым выходом 82 анализа признака пакета 8. Четкий выход 845 анализатора совпадений признаков 8.04 соединен с выходом 852 верификатора 8.05 и является четким признаковым выходом 84 блока анализа признака пакета 8, а второстепенный вход 853 верификатора 8.05 является возвратным признаковым входом 83 блока анализа признака пакета 8.

Анализатор количества бит заголовка пакета 8.01 блока анализа признака пакета 8 предназначен для сравнения количества бит поступающей бинарной импульсной последовательности с эталонным количеством бит флага начала (окончания) информационной части пакета, соответствующего использующемуся и заранее известному для данной ТКС протоколу обмена. Анализатор количества бит заголовка пакета 8.01 может быть технически реализован в виде двоичного суммирующего счетчика с последовательным переносом на Т-триггерах, как описано в литературе [Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987. С.138-141, рис.9.1].

Анализатор очередности бит заголовка пакета 8.02 блока анализа признака пакета 8 предназначен для сравнения очередности следования бит поступающей бинарной импульсной последовательности с принятой, для использующегося и заранее известного для данной ТКС протокола обмена, очередностью следования бит флага начала (окончания) информационной части пакета. Анализатор очередности бит заголовка пакета 8.02 может быть реализован на базе динамического сдвигового регистра, как показано в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С.82-87, рис.5.13 (б)],

Анализатор интенсивности бит заголовка пакета 8.03 блока анализа признака пакета 8 предназначен для сравнения интенсивности следования бит поступающей бинарной импульсной последовательности с традиционной для данного протокола интенсивностью следования бит флага начала (окончания) информационной части пакета. Анализатор интенсивности бит заголовка пакета 8.03 может быть технически реализован в виде счетчика-делителя с переменным коэффициентом деления, работающего как суммирующий двоичный, как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.181-182, рис.5.47].

Анализатор совпадений признаков 8.04 блока анализа признака пакета 8 предназначен для анализа (сравнения) дополнительных бинарных символов (1 либо 0), поступающих на его входы наряду с исходной бинарной кодовой последовательностью и принятия решения о логико-математической природе идентифицируемых признаков пакетов (четкие либо нечеткие). Анализатор совпадений признаков 8.04 представляет собой цифровой узел сравнения и может быть технически реализован в виде узла сравнения (цифрового компаратора), как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Верификатор 8.05 (фиг.3) блока анализа признака пакета 8 предназначен для окончательной реализации принятого в блоке преобразования вида признака пакета 9 решения о принадлежности (либо не принадлежности) анализируемого и математически корректно преобразованного признака пакета к пространству признаков и передачи информации в блок вычисления параметров 2. Верификатор 8.05 блока анализа признака пакета 8 состоит из сдвигающего регистра 8.05-1 и контроллера 8.05-2. Главный вход 8051 сдвигающего регистра 8.05-1 является главным входом 851 верификатора 8.05, выход сдвигающего регистра 8.05-1 является выходом 852 верификатора 8.05, дополнительный вход 8052 сдвигающего регистра 8.05-1 соединен с выходом контроллера 8.05-2, вход которого является второстепенным входом 853 верификатора 8.05.

Сдвигающий регистр 8.05-1 верификатора 8.05 выполняет функции хранения битовой последовательности и инверсии первого бита из идентифицированной как «не заголовок» битовой последовательности на противоположный («нуль» на «единицу» или наоборот) и может быть технически реализован на базе сдвигающего регистра для сдвига влево с инверсией, как показано в литературе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.158-160, рис.5.28 (б)].

Контроллер 8.05-2 верификатора 8.05 предназначен для приема из блока 9 контрольных сигналов и выработки соответствующих бинарных импульсных сигналов 0 или 1 («нуль» или «единица»), являющихся инверсионными командами для сдвигающего регистра 8.05-1. Контроллер 8.05-2 может быть технически реализован в виде серийно выпускаемой схемы контроля счетчика, как показано в [Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987, с.173-178, рис.10.21].

Блок преобразования вида признака пакета 9 (фиг.4) предназначен для математически корректного преобразования исходных данных, характеризующих признаки пакетов и идентифицированных в нечеткой форме (не параметрически) к виду, пригодному для параметрического оценивания закона распределения потоков сообщений. Блок преобразования вида признака пакета 9 состоит из счетчика 9.01, вычислителя дополнения 9.02, основного 9.03 и вспомогательного 9.04 запоминающих элементов, основного 9.05 и вспомогательного 9.06 вычислителей пересечения, вычислителя объединения 9.07 и анализатора функции α-уровня 9.08, выход которого 982 является выходом 92 блока преобразования вида признака пакета 9. Вход 911 счетчика 9.01 является входом 91 блока преобразования вида признака пакета 9, первый 912 и второй 913 выходы счетчика 9.01 соединены соответственно с входом 931 основного запоминающего элемента 9.03 и прямым входом 941 вспомогательного запоминающего элемента 9.04, а также соответственно с первым 921 и вторым 922 входами вычислителя дополнения 9.02, выходы основного 9.03 и вспомогательного 9.04 запоминающих элементов подключены соответственно к главным входам 951 и 961 основного 9.05 и вспомогательного 9.06 вычислителей пересечения, к дополнительным входам 952 и 962 основного 9.05 и вспомогательного 9.06 вычислителей пересечения подключены соответственно первый 923 и второй 924 выходы вычислителя дополнения 9.02, выходы 953 и 963 основного 9.05 и вспомогательного 9.06 вычислителей пересечения подключены соответственно к первому 971 и второму 972 входам вычислителя объединения 9.07, выход 973 которого соединен с дополнительным входом 925 вычислителя дополнения 9.02, дополнительным входом 943 вспомогательного запоминающего элемента 9.04 и входом 981 анализатора функции α-уровня 9.08.

Счетчик 9.01 блока преобразования вида признака пакета 9 предназначен для регистрации и сортировки в двоичном коде информации на две составляющие - по начальному количеству мнений экспертов (количество экспертов равно двум) о степени принадлежности конкретного идентифицируемого признака пакета в рамках данного сообщения к пространству признаков. Счетчик 9.01 может быть технически реализован на базе цифрового счетчика, как описано в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981, с.96-100].

Вычислитель дополнения 9.02 блока преобразования вида признака пакета 9 предназначен для осуществления в двоичном коде операции арифметического вычитания из единицы значений функций принадлежности нечетких множеств. Вычислитель дополнения 9.02 представляет собой типовое арифметико-логическое устройство и технически реализуется в виде серийно выпускаемого арифметико-логического устройства (АЛУ), описанного в [Дроздов Е.А., Комарницкий В.А., Пятибратов А.П. Электронно-вычислительные машины Единой системы. - М.: Машиностроение, 1981, с.158-170].

Основной запоминающий элемент 9.03 блока преобразования вида признака пакета 9 предназначен для хранения нечеткой информации от первого эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на главный вход 951 основного вычислителя пересечения 9.05. Основной запоминающий элемент 9.03 технически реализуется в виде типового программируемого запоминающего устройства в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996, с.197-199, рис.6.10].

Вспомогательный запоминающий элемент 9.04 блока преобразования вида признака пакета 9 предназначен для хранения нечеткой информации от второго эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на главный вход 961 вспомогательного вычислителя пересечения 9.06. Вспомогательный запоминающий элемент 9.04 отличается от основного запоминающего элемента 9.03 лишь наличием дополнительного входа, который технически может быть легко объединен с прямым входом, что позволяет осуществить реализацию вспомогательного запоминающего элемента 9.04 аналогично основному запоминающему элементу 9.03, в виде программируемого постоянного запоминающего устройства, как описано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.197-199, рис.6.10].

Основной вычислитель пересечения 9.05 блока преобразования вида признака пакета 9 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого первым экспертом с дополнением нечеткого множества, формулируемого вторым экспертом. Основной вычислитель пересечения 9.05 представляет собой цифровой узел сравнения, описанный в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Вспомогательный вычислитель пересечения 9.06 блока преобразования вида признака пакета 9 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого вторым экспертом с дополнением нечеткого множества, формулируемого первым экспертом. Вспомогательный вычислитель пересечения 9.06 идентичен основному вычислителю пересечения 9.05 и также может быть технически реализован на базе цифрового узла сравнения, описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Вычислитель объединения 9.07 блока преобразования вида признака пакета 9 предназначен для реализации завершающего цикл дизъюнктивного суммирования нечетких множеств - выполнения математической операции объединения нечетких множеств, являющихся результатом соответственно пересечения нечеткого множества, формулируемого первым экспертом с дополнением нечеткого множества, формулируемого вторым экспертом и пересечения нечеткого множества, формулируемого вторым экспертом с дополнением нечеткого множества, формулируемого первым экспертом. Вычислитель объединения 9.07 может быть технически реализован на базе цифрового узла сравнения, описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Анализатор функции α-уровня 9.08 блока преобразования вида признака пакета 9 предназначен для однозначного выбора (присвоения) количественных значений анализируемых нечетких параметров потока (признаков пакетов). Анализатор функции α-уровня 9.08 представляет собой цифровую программируемую пороговую схему сравнения, описанную в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.152-156, рис.5.22].

Входной усилитель 1, входящий в общую структурную схему, предназначен для осуществления процедуры усиления, нормировки по амплитуде и длительности входного потока - бинарной импульсной последовательности. Входной усилитель 1 может быть технически реализован в виде триггера Шмитта, как показано в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.117-119, рис.4.12 (а)].

Блок вычисления параметров 2, входящий в общую структурную схему, предназначен для определения текущих значений параметров λс и ξ. Его схема известна, описана (например, в патенте РФ №2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.5 данного описания. Блок вычисления параметров 2 содержит дешифратор заголовков пакетов 2.01, обнаружитель пауз 2.02, счетчик информационной длины многопакетных сообщений 2.03, счетчик сообщений 2.04 и вычислитель соотношения информационных длин пакетов и сообщений 2.05. Вход дешифратора заголовков пакетов 2.01, являющийся информационным входом 21 блока 2, параллельно подключен к первому входу 231 счетчика информационной длины многопакетных сообщений 2.03 и к входу обнаружителя пауз 2.02, выход дешифратора заголовков пакетов 2.01 соединен со вторым входом 232 счетчика информационной длины многопакетных сообщений 2.03. Выход обнаружителя пауз 2.02 подключен к третьему входу 233 счетчика информационной длины многопакетных сообщений 2.03 и к первому входу 241 счетчика сообщений 2.04, выход счетчика информационной длины многопакетных сообщений 2.03 подключен к первому входу 251 вычислителя соотношения информационных длин пакетов и сообщений 2.05, второй управляющий вход 252 которого является управляющим входом 23 блока вычисления параметров 2. Второй обнуляющий вход 242 счетчика сообщений 2.04 является обнуляющим входом 22 блока вычисления параметров 2. Выходы вычислителя соотношения информационных длин пакетов и сообщений 2.05 и счетчика сообщений 2.04 являются соответственно первым 24 и вторым 25 информационными выходами блока вычисления параметров 2.

Блок вычисления средних арифметических значений 3, входящий в общую структурную схему, предназначен для получения численных значений усредненных за интервал наблюдения параметров потока ( и ). Его структурная схема известна, описана, например, в прототипе (см. патент РФ №2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.6 данного описания. Блок вычисления средних арифметических значений 3 состоит из счетчика-делителя значений длительности 3.01, счетчика-делителя значений интенсивности 3.02 и элемента ЗАПРЕТ 3.03. Вход счетчика-делителя значений длительности 3.01 является первым информационным входом 31 блока вычисления средних арифметических значений 3, выход счетчика-делителя значений длительности 3.01 является первым информационным выходом 33 блока 3. Вход счетчика-делителя значений интенсивности 3.02 является вторым информационным входом 32 блока вычисления средних арифметических значений 3, выход счетчика-делителя значений интенсивности 3.02 подключен к разрешающему входу 331 элемента ЗАПРЕТ 3.03. Запрещающий вход 332 элемента ЗАПРЕТ 3.03 является управляющим входом 35 блока вычисления средних арифметических значений 3, выход элемента ЗАПРЕТ 3.03 является вторым информационным выходом 34 блока 3.

Блок определения типа распределения 4, входящий в общую структурную схему, предназначен для осуществления процедуры сравнения значений параметра соотношения длительности с единичным порогом и принятия решения о принадлежности однородного входного потока к одной из трех известных модификаций потоков многопакетных сообщений. Схема блока определения типа распределения 4 известна, описана в прототипе (см. патент РФ №2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.7 данного описания. Блок определения типа распределения 4 содержит: цифроаналоговый преобразователь (ЦАП) 4.01, два компаратора 4.02, 4.03, генератор порогового напряжения 4.04 и элемент ИЛИ-НЕ 4.05. Вход цифроаналогового преобразователя 4.01 является входом блока определения типа распределения 4 и соединен с первым информационным выходом 33 блока вычисления средних арифметических значений 3, выход цифроаналогового преобразователя 4.01 соединен с первым входом 421 компаратора 4.02 и с первым входом 431 компаратора 4.03. Второй вход 422 компаратора 4.02 и второй вход 432 компаратора 4.03 под