Устройство для обучения операторов

Иллюстрации

Показать всеИзобретение относится к техническим средствам подготовки операторов систем управления и может быть использовано для практического обучения операторов на тренажерах. Целью изобретения является создание устройства для обучения операторов, обеспечивающего повышение достоверности управленческих решений, принимаемых оператором при обучении в условиях, присущих реальному процессу функционирования автоматизированных систем управления. Устройство для обучения операторов содержит блок задания программы обучения 1, блок ответных действий оператора 2, стартовый 7, главный 13 и установочный 18 элементы ИЛИ, табло 4, элемент задержки 21, главный 3 и ответный 19 блоки сравнения, блоки стартовых 8 и опросных 10 элементов И, регистр числа 20, стартовый 6 и главный 11 счетчики, дешифратор 12, триггер 9, элемент И 5, блок анализа решения 22, блок поддержки принятия достоверного решения 23, соответствующим образом соединенные между собой. 3 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к техническим средствам подготовки операторов систем управления и может быть использовано для практического обучения операторов на тренажерах.

Известно устройство для обучения операторов по авт. св. СССР №1320833, G 09 В 9/00, 1986, содержащее регистр адреса, блок памяти, регистр микрокоманды, блок сравнения, пульт оператора, счетчик, элемент И, элементы ИЛИ, блок давления, регистр числа и блок памяти.

Недостатком данного устройства является узкий перечень решаемых задач обучения, направленных лишь на обучение устранению неисправностей, что обуславливает относительно невысокую дидактическую способность устройства.

Известно устройство для обучения операторов, содержащее регистр адреса (микрокоманды), блок памяти, регистр микрокоманды, панель органов индикации, выполненную в виде информационного табло, панель органов управления, выполненную в виде блока ввода ответных действий оператора, два блока сравнения, трех элементов ИЛИ, генератор, элементы задержки, счетчик, триггер и блок звуковой сигнализации (см. авт. св. СССР №1437897, G 09 В 9/00, 1988).

Однако данное устройство имеет узкую область применения, поскольку на этапе отработки навыков пооперационной своевременной деятельности частое включение звуковой сигнализации не позволяет закрепить навыки при отработке оператором сложных алгоритмов управления, имеющих место в современных автоматизированных системах управления (АСУ).

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство для обучения операторов (см. патент РФ №2011229, 5 G 09 В 9/00, 1994, бюл.7), содержащее блок задания программы обучения, блок ответных действий оператора, стартовый, главный и установочный элементы ИЛИ, элемент задержки, главный и ответный блоки сравнения, блоки стартовых и опросных элементов И, регистр числа, стартовый и главный счетчики, дешифратор, триггер, элемент И и табло, m≥2 информационных входов которого соединены с соответствующими m выходами дешифратора, m входов которого подключены к соответствующим m выходам блока опросных элементов И, m счетных входов которого соединены с соответствующими m выходами главного счетчика, установочный вход «Уст.«0» которого соединен с первым входом стартового элемента ИЛИ, вторым входом установочного элемента ИЛИ, первым входом главного элемента ИЛИ и является входом «Запуск» устройства, выход главного элемента ИЛИ подключен к счетному входу «Уст.«1» главного счетчика и первому управляющему входу блока задания программы обучения, m индикаторных выходов которого соединены с соответствующими m индикаторными входами табло, первый контрольный вход которого подключен к прямому выходу триггера, инверсный выход которого соединен с первым входом элемента И и вторым контрольным входом табло, m информационных выходов блока задания программы обучения соединены с соответствующими m информационными входами главного блока сравнения, m ответных входов которого подключены к соответствующим m выходам блока ответных действий оператора, первый выход главного блока сравнения соединен с вторым входом стартового элемента ИЛИ и вторым управляющим входом блока задания программы обучения, второй выход главного блока сравнения подключен к второму входу главного элемента ИЛИ, входу элемента задержки и второму входу элемента И, выход которого соединен с счетным входом «Уст.«1» стартового счетчика, установочный вход «Уст.«0» которого подключен к выходу стартового элемента ИЛИ, выход элемента задержки соединен с управляющим входом регистра числа и с m информационными входами блока стартовых элементов И, m счетных входов которого соединены с соответствующими m выходами стартового счетчика, m выходов блока стартовых элементов И подключены к соответствующим m информационным входам ответного блока сравнения, m ответных входов которого соединены с соответствующими m выходами регистра числа, выход ответного блока сравнения подключен к первому входу установочного элемента ИЛИ, выход которого соединен с установочным входом триггера, сбрасывающий вход которого подключен к контрольному выходу блока задания программы обучения и к m информационным входам блока опросных элементов И.

В прототипе реализуется возможность более обоснованного принятия решения о переводе обучаемого с этапа «Упражнение» к этапу «Тренировка», тем самым осуществляется расширение дидактических возможностей и области применения устройства.

Однако прототип имеет недостаток - относительно низкую достоверность множества решений, предлагаемых для принятия оператору (обучаемому) в ходе отработки сложных алгоритмов управления в различных условиях априорной неопределенности, в частности в условиях недостоверности (недостаточности, неполноты и противоречивости) исходных данных, т.е. относительно низкую достоверность решений в управленческих ситуациях с недостоверно (недостаточно, неполно) идентифицируемыми состояниями. Данное устройство позволяет обучать оператора принимать решения с высокой достоверностью в ситуациях, состояния которых количественно заданы, непротиворечивы и полно идентифицируются, в то время как большое количество ситуаций (состояний системы управления), реально возникающих и требующих принятия эффективных решений в современных АСУ могут быть идентифицированы лишь качественно (на качественном уровне - недостоверно, недостаточно, неполно), и достоверные решения в таких ситуациях традиционно принимаются опираясь на мнения экспертов.

Под «состоянием» управленческой ситуации (состоянием АСУ) понимается n-мерный вектор переменных состояния АСУ в конкретный момент времени в пространстве состояний. Это множество значений характеристик свойств АСУ (как правило, существенных) в данный момент времени (точка в N-мерном пространстве) или, иными словами, вектор (вектор параметров) в параметрическом пространстве состояний, численно описывающих характеристики (свойства) АСУ.

Целью предлагаемого изобретения является создание устройства для обучения операторов, обеспечивающего повышение достоверности управленческих решений, принимаемых оператором при обучении в условиях, присущих реальному процессу функционирования АСУ, т.е. при недостоверности (недостаточности, неполноты и противоречивости) идентификации состояний системы управления, устройства, способного помочь обучить и закрепить навыки оператора по принятию достоверных (эффективных) решений при отработке сложных алгоритмов управления в АСУ, текущие состояния которых могут быть идентифицированы как количественно, так и качественно - недостоверно, неполно.

Указанная цель достигается тем, что в известное устройство для обучения операторов, содержащее блок задания программы обучения, блок ответных действий оператора, стартовый, главный и установочный элементы ИЛИ, элемент задержки, главный и ответный блоки сравнения, блоки стартовых и опросных элементов И, регистр числа, стартовый и главный счетчики, дешифратор, триггер, элемент И и табло, m≥2 информационных входов которого соединены с соответствующими m выходами дешифратора, m входов которого подключены к соответствующим m выходам блока опросных элементов И, m счетных входов которого соединены с соответствующими m выходами главного счетчика, установочный вход «Уст.«0» которого соединен с первым входом стартового элемента ИЛИ, вторым входом установочного элемента ИЛИ, первым входом главного элемента ИЛИ и является входом «Запуск» устройства, выход главного элемента ИЛИ подключен к счетному входу «Уст.«1» главного счетчика и первому управляющему входу блока задания программы обучения, m индикаторных выходов которого соединены с соответствующими m индикаторными входами табло, первый контрольный вход которого подключен к прямому выходу триггера, инверсный выход которого соединен с первым входом элемента И и вторым контрольным входом табло, m информационных выходов блока задания программы обучения соединены с соответствующими m информационными входами главного блока сравнения, первый выход которого сравнения соединен с вторым входом стартового элемента ИЛИ и вторым управляющим входом блока задания программы обучения, второй выход главного блока сравнения подключен к второму входу главного элемента ИЛИ, входу элемента задержки и второму входу элемента И, выход которого соединен с счетным входом «Уст.«1» стартового счетчика, установочный вход «Уст.«0» которого подключен к выходу стартового элемента ИЛИ, выход элемента задержки соединен с управляющим входом регистра числа и с m информационными входами блока стартовых элементов И, m счетных входов которого соединены с соответствующими m выходами стартового счетчика, m выходов блока стартовых элементов И подключены к соответствующим m информационным входам ответного блока сравнения, m ответных входов которого соединены с соответствующими m выходами регистра числа, выход ответного блока сравнения подключен к первому входу установочного элемента ИЛИ, выход которого соединен с установочным входом триггера, сбрасывающий вход которого подключен к контрольному выходу блока задания программы обучения и к m информационным входам блока опросных элементов И, дополнительно введены блок анализа решения и блок поддержки принятия достоверного решения, причем m выходов блока ответных действий оператора подключены к соответствующим m входам блока анализа решения, m проверочных выходов которого соединены с соответствующими m входами блока поддержки принятия достоверного решения, m выходов которого объединены с соответствующими m подтверждающими выходами блока анализа решения и подключены к соответствующим m регистровым входам блока задания программы обучения и к соответствующим m ответным входам главного блока сравнения.

Блок анализа решения состоит из регистра сдвига и регистра хранения, m входов которого подключены к соответствующим m выходам регистра сдвига, m входов которого являются соответствующими m входами блока анализа решения, m подтверждающих выходов регистра хранения являются соответствующими m подтверждающими выходами блока анализа решения, m проверочных выходов регистра хранения являются соответствующими m проверочными выходами блока анализа решения.

Блок поддержки принятия достоверного решения состоит из регистра и вычислителя решения оператора, m выходов которого являются соответствующими m выходами блока, m информационных входов вычислителя решения оператора подключены к соответствующим m информационным выходам регистра, разрешающий выход которого соединен с разрешающим входом вычислителя решения оператора, запрещающий вход которого подключен к запрещающему выходу регистра, m входов которого являются соответствующими m входами блока поддержки принятия достоверного решения.

Блок задания программы обучения состоит из регистра адреса микрокоманды, элемента памяти микропрограммы, регистра микрокоманды и регистра верифицированной микрокоманды, m входов которого являются соответствующими m регистровыми входами блока, m выходов регистра верифицированной микрокоманды объединены с соответствующими m выходами регистра адреса микрокоманды и подключены к соответствующим m входам элемента памяти микропрограммы, m выходов которого соединены с соответствующими m входами регистра микрокоманды, m индикаторных выходов которого являются соответствующими m индикаторными выходами блока, m информационных выходов регистра микрокоманды являются соответствующими m информационными выходами блока. Первый и второй входы регистра адреса микрокоманды являются соответственно первым управляющим и вторым управляющим входами блока, а контрольный выход регистра адреса микрокоманды является контрольным выходом блока задания программы обучения.

Благодаря новой совокупности существенных признаков за счет введения блока анализа решения и блока поддержки принятия достоверного решения, обеспечивающих, соответственно, анализ поступающих в двоичном коде управленческих решений, принимаемых оператором, с точки зрения их достоверности относительно полноты идентификации состояний системы управления и математически корректной поддержки принятия достоверного решения в заявленном устройстве в рамках обучения и закрепления навыков достигается возможность предварительного анализа и преобразования (верификации) решений оператора, обуславливающая повышение достоверности принимаемых обучаемым управленческих решений в условиях, присущих реальному процессу функционирования и управления АСУ - в условиях недостоверности (недостаточности, неполноты, а зачастую и противоречивости) исходных данных для принятия решения.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявленное устройство поясняется чертежами, на которых представлены:

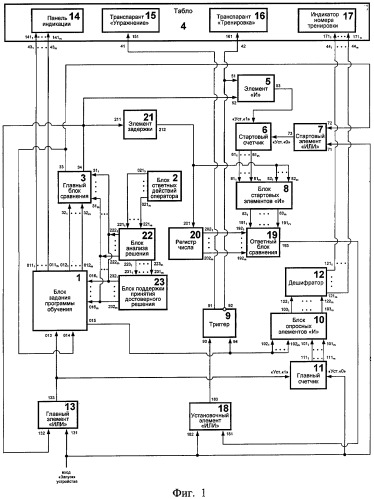

на фиг.1 - структурная схема устройства для обучения операторов;

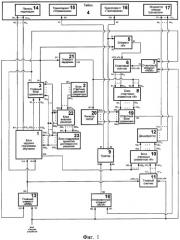

на фиг.2 - структурная схема блока анализа решения;

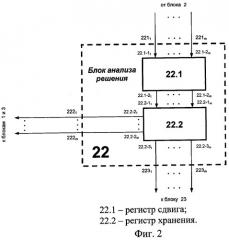

на фиг.3 - структурная схема блока поддержки принятия достоверного решения;

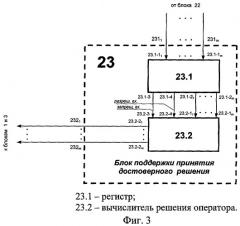

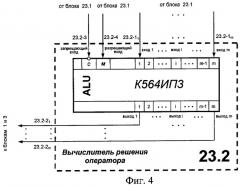

на фиг.4 - структурная схема вычислителя решения оператора;

на фиг.5 - структурная схема блока задания программы обучения;

на фиг.6 - структурная схема блока стартовых элементов И;

на фиг.7 - структурная схема блока опросных элементов И.

Устройство для обучения операторов, изображенное на фиг.1, состоит из блока задания программы обучения 1, блока ответных действий оператора 2, стартового 7, главного 13 и установочного 18 элементов ИЛИ, элемента задержки 21, главного 3 и ответного 19 блоков сравнения, блоков стартовых 8 и опросных 10 элементов И, регистра числа 20, стартового 6 и главного 11 счетчиков, дешифратора 12, триггера 9, элемента И 5, блока анализа решения 22, блока поддержки принятия достоверного решения 23 и табло 4, m≥2 информационных входов 441-44m которого соединены с соответствующими m выходами 1211-121m дешифратора 12, m входов 1221-122m которого подключены к соответствующим m выходам 1031-103m блока опросных элементов И 10, m счетных входов 1011-101m которого соединены с соответствующими m выходами 1111-111m главного счетчика 11. Установочный вход «Уст.«0» главного счетчика 11 соединен с первым входом 71 стартового элемента ИЛИ 7, вторым входом 181 установочного элемента ИЛИ 18, первым входом 131 главного элемента ИЛИ 13 и является входом «Запуск» устройства. Выход 133 главного элемента ИЛИ 13 подключен к счетному входу «Уст.«1» главного счетчика 11 и первому управляющему входу 013 блока задания программы обучения 1, m индикаторных выходов 0111-011m которого соединены с соответствующими m индикаторными входами 431-43m табло 4, первый контрольный вход 41 которого подключен к прямому выходу 91 триггера 9, инверсный выход 92 которого соединен с первым входом 51 элемента И 5 и вторым контрольным входом 42 табло 4, m информационных выходов 0121-012m блока задания программы обучения 1 соединены с соответствующими m информационными входами 321-32m главного блока сравнения 3. Первый выход 33 главного блока сравнения 3 соединен с вторым входом 72 стартового элемента ИЛИ 7 и вторым управляющим входом 014 блока задания программы обучения 1. Второй выход 34 главного блока сравнения 3 подключен к второму входу 132 главного элемента ИЛИ 13, входу 211 элемента задержки 21 и второму входу 52 элемента И 5, выход 53 которого соединен с счетным входом «Уст.«1» стартового счетчика 6, установочный вход «Уст.«0» которого подключен к выходу 73 стартового элемента ИЛИ 7. Выход 212 элемента задержки 21 соединен с управляющим входом 201 регистра числа 20 и с m информационными входами 821-82m блока стартовых элементов И 8, m счетных входов 811-81m которого соединены с соответствующими m выходами 611-61m стартового счетчика 6, m выходов 831-83m блока стартовых элементов И 8 подключены к соответствующим m информационным входам 1911-191m ответного блока сравнения 19, m ответных входов 1921-192m которого соединены с соответствующими m выходами 2021-202m регистра числа 20. Выход 193 ответного блока сравнения 19 подключен к первому входу 181 установочного элемента ИЛИ 18, выход 183 которого соединен с установочным входом 93 триггера 9, сбрасывающий вход 94 которого подключен к контрольному выходу 015 блока задания программы обучения 1 и к m информационным входам 1021-102m блока опросных элементов И 10, m выходов 0211-021m блока ответных действий оператора 2 подключены к соответствующим m входам 2211-221m блока анализа решения 22, m проверочных выходов 2231-223m которого соединены с соответствующими m входами 2311-231m блока поддержки принятия достоверного решения 23, m выходов 2321-232m которого объединены с соответствующими m подтверждающими выходами 2221-222m блока анализа решения 2 и подключены к соответствующим m регистровым входам 0161-016m блока задания программы обучения 1 и к соответствующим m ответным входам 311-31m главного блока сравнения 3.

Число «m, (m≥2)» (входов, выходов, элементов И, счетчиков и т.п.) определяется в соответствии с необходимой и достаточной для обучения операторов степенью детализации (полноты) идентификации состояний системы управления и, как правило, составляет от 2 (двух) до 20 (двадцати).

Блок анализа решения 22 (фиг.2) предназначен для осуществления процедур регистрации (хранения), анализа поступающих в двоичном коде управленческих решений, принимаемых оператором, с точки зрения их достоверности относительно полноты идентификации состояний системы управления и принятия решения о математической природе исходных данных, зафиксированных в рамках обучающих микрокоманд и использовавшихся для принятия конкретного управленческого решения - исходные данные идентифицированы количественно (параметрически) или качественно (недостоверно, неполно) и принятое обучаемым управленческое решение нуждаются в верификации с привлечением аналитически сформулированных субъективных мнений (ассоциаций) экспертов.

Блок анализа решения 22 состоит из регистра сдвига 22.1 и регистра хранения 22.2, m входов 22.2-11-22.2-1m которого подключены к соответствующим m выходам 22.1-21-22.1-2m регистра сдвига 22.1, m входов 22.1-11-22.1-1m которого являются соответствующими m входами 2211-221m блока анализа решения 22, m подтверждающих выходов 22.2-21-22.2-2m регистра хранения 22.2 являются соответствующими m подтверждающими выходами 2221-222m блока анализа решения 22, m проверочных выходов 22.2-31-22.2-3m регистра хранения 22.2 являются соответствующими m проверочными выходами 2231-223m блока анализа решения 22.

Регистр сдвига 22.1 блока анализа решения 22 предназначен для фиксирования (регистрации в двоичном коде) управленческого решения, принимаемого обучаемым. Регистр сдвига 22.1 может быть технически реализован в виде запоминающего устройства на базе типового регистра сдвига с последовательным вводом и выводом информации, описанного в [Быстров Ю.А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга/ Под ред. Быстрова Ю.А. - СПб.: Энергоатомиздат, 1996. С.291-292, рис.6.7].

Регистр хранения 22.2 блока анализа решения 22 предназначен для осуществления процедуры последовательного сравнения поступающих управленческих решений, принимаемых оператором, и принятия решения о математической природе исходных данных, зафиксированных в рамках обучающих микрокоманд и использовавшихся для принятия конкретного управленческого решения - исходные данные идентифицированы количественно (параметрически) или качественно (недостоверно, неполно) и принятое обучаемым управленческое решение недостоверно и нуждаются в верификации с привлечением аналитически сформулированных субъективных мнений (ассоциаций) экспертов. Регистр хранения 22.2 может быть технически реализован в виде серийно выпускаемого сдвигающего регистра для сдвига влево, как показано в литературе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.158-160, рис.5.28(б)].

Блок поддержки принятия достоверного решения 23 (фиг.3) предназначен для математически корректной поддержки принятия достоверного решения путем преобразования идентифицированных недостоверно (неполно) исходных данных, зафиксированных в рамках обучающих микрокоманд, к виду, пригодному для принятия обучаемым достоверного управленческого решения.

Блок поддержки принятия достоверного решения 23 состоит из регистра 23.1 и вычислителя решения оператора 23.2, m выходов 23.2-21-23.2-2m которого являются соответствующими m выходами 2321-232m блока 23, m информационных входов 23.2-11-23.2-1m вычислителя решения оператора 23.2 подключены к соответствующим m информационным выходам 23.1-21-23.1-2m регистра 23.1, разрешающий выход 23.1-4 которого соединен с разрешающим входом 23.2-4 вычислителя решения оператора 23.2, запрещающий вход 23.2-3 которого подключен к запрещающему выходу 23.1-3 регистра 23.1, m входов 23.1-11-23.1-1m которого являются соответствующими m входами 2311-231m блока поддержки принятия достоверного решения 23.

Регистр 23.1 блока поддержки принятия достоверного решения 23 предназначен для регистрации (записи) и хранения в двоичном коде принятого обучаемым управленческого решения. Регистр 23.1 может быть технически реализован на базе серийно выпускаемого программируемого запоминающего устройства в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.197-199, рис.6.10].

Вычислитель решения оператора 23.2 блока поддержки принятия достоверного решения 23 (фиг.4) предназначен для осуществления процедуры преобразования идентифицированных недостоверно (неполно) исходных данных, используемых для принятия конкретного решения и зафиксированных в рамках обучающих микрокоманд, к виду, пригодному для принятия обучаемым достоверного управленческого решения.

Вычислитель решения оператора 23.2 представляет собой программируемый параллельный арифметико-логический вычислитель (АЛВ) с одним разрешающим и одним запрещающим входом, m информационными входами и выходами, где m может принимать значения от 2 до 23. Разрешающий вход М АЛВ является разрешающим входом 23.2-4 вычислителя решения оператора 23.2, запрещающий вход С АЛВ является запрещающим входом 23.2-3 вычислителя решения оператора 23.2, m информационных входов АЛВ являются соответствующими m информационными входами 23.2-11-23.2-1m вычислителя решения оператора 23.2, m информационных выходов АЛВ являются соответствующими m выходами 23.2-21-23.2-2m вычислителя решения оператора 23.2. Вычислитель решения оператора 23.2 может быть технически реализован в виде параллельного арифметико-логического устройства на базе серийно выпускаемой программируемой комплиментарной металл-окисел-полупроводниковой (КМОП) микросхемы серии 564 (например, ALU К564ИП3), как показано в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - M.: Радио и связь, 1987. С.273-275, рис.2.70].

Блок задания программы обучения 1 (фиг.5) предназначен для записи и хранения параметров алгоритма управления, отрабатываемого человеком-оператором.

Блок задания программы обучения 1 состоит из регистра адреса микрокоманды 1.1, элемента памяти микропрограммы 1.2, регистра микрокоманды 1.3 и регистра верифицированной микрокоманды 1.4, m входов 1.4-11-1.4-1m которого являются соответствующими m регистровыми входами 0161-016m блока 1, m выходов 1.4-21-1.4-2m регистра верифицированной микрокоманды 1.4 объединены с соответствующими m выходами 1.1-31-1.1-3m регистра адреса микрокоманды 1.1 и подключены к соответствующим m входам 1.2-11-1.2-1m элемента памяти микропрограммы 1.2, m выходов 1.2-21-1.2-2m которого соединены с соответствующими m входами 1.3-31-1.3-3m регистра микрокоманды 1.3, m индикаторных выходов 1.3-11-1.3-1m которого являются соответствующими m индикаторными выходами 0111-011m блока 1, m информационных выходов 1.3-21-1.3-2m регистра микрокоманды 1.3 являются соответствующими m информационными выходами 0121-012m блока 1. Первый 1.1-1 и второй 1.1-2 входы регистра адреса микрокоманды 1.1 являются соответственно первым управляющим 013 и вторым управляющим 014 входами блока 1, а контрольный выход 1.1-4 регистра адреса микрокоманды 1.1 является контрольным выходом 015 блока задания программы обучения 1.

Регистр адреса микрокоманды 1.1 блока задания программы обучения 1 предназначен для записи и хранения адреса всех микрокоманд, используемых при обучении операторов. Регистр адреса микрокоманды 1.1 может быть технически реализован в виде серийно выпускаемого сдвигающего регистра для сдвига влево, как описано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.158-160, рис.5.28(б)].

Элемент памяти микропрограммы 1.2 блока задания программы обучения 1 предназначен для выбора и хранения адресов микрокоманд, соответствующих очередной операции алгоритма управления. Элемент памяти микропрограммы 1.2 технически реализуется в виде типового программируемого запоминающего устройства в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.197-199, рис.6.10].

Регистр микрокоманды 1.3 блока задания программы обучения 1 предназначен для записи, хранения и считывания в двоичном коде содержания очередной микрокоманды (микрооперации), соответствующей конкретному алгоритму управления. Регистр микрокоманды 1.3 может быть реализован на базе динамического сдвигового регистра, как показано в работе [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981, С.82-87, рис.5.13(б)],

Регистр верифицированной микрокоманды 1.4 блока задания программы обучения 1 предназначен для записи, хранения и считывания в двоичном коде содержания верифицированной команды (управляющего воздействия), инициированного обучаемым (оператором). Техническая реализация регистра верифицированной микрокоманды 1.4 возможна по аналогии с типовым, серийно выпускаемым динамическим оперативным запоминающим устройством, описанным в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.194-196, рис.6.9].

Табло 4, входящее в общую структурную схему, предназначено для индикации (визуализации в интересах обучаемого) состояния алгоритма управления, режима обучения (упражнение либо тренировка) и номера тренировки, на которой обучаемому удается завершить алгоритм управления без ошибок. Табло 4 состоит из объединенных в едином корпусе панели индикации 14, транспаранта «Упражнение» 15, транспаранта «Тренировка» 16 и индикатора номера тренировки 17. Состав элементов табло 4, их взаимосвязь и принцип их действия известны и подробно описаны в прототипе (см. патент РФ №2011229, 5 G 09 В 9/00, 1994, бюл.7).

Блок ответных действий оператора 2, входящий в общую структурную схему, предназначен для набора (формирования) оператором кода очередного управляющего воздействия (кода управленческой микрокоманды) и передачи сформированного сигнала для проверки в соответствии с алгоритмом обучения. Блок ответных действий оператора 2 представляет собой типовую клавиатуру, которая в традиционном сочетании с панелью индикации 14 табло 4 (экраном, монитором) является физической моделью пульта оператора реальной АСУ. Структурная схема и принцип действия блока ответных действий оператора 2 известны и описаны, например, в прототипе (см. патент РФ №2011229, 5 G 09 В 9/00, 1994, бюл.7).

Главный блок сравнения 3, входящий в общую структурную схему, предназначен для оценки безошибочности сформированного оператором управляющего воздействия. Главный блок сравнения 3 представляет собой цифровой узел сравнения и может быть технически реализован в виде серийно выпускаемого узла сравнения (цифрового компаратора), как показано в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.149-152, рис.5.19].

Элемент И 5, входящий в общую структурную схему, предназначен для регистрации ошибок оператора и коммутации счетного входа «Уст.«1» стартового счетчика 6 в интересах их подсчета. Элемент И 5 может быть технически реализован на основе серийно выпускаемого элемента И, описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.13-14, рис.1.2].

Стартовый счетчик 6, входящий в общую структурную схему, предназначен для подсчета числа ошибок, допущенных подряд на этапе тренировки оператора. Частный случай технической реализации стартового счетчика 6 описан в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С.96-100].

Стартовый элемент ИЛИ 7, входящий в общую структурную схему, предназначен для объединения сигналов на установочный вход «Уст.«0» стартового счетчика 6 для его обнуления с началом обучения - с внешнего входа «Запуск» устройства и в случае безошибочного выполнения текущей операции - с первого выхода 33 главного блока сравнения 3. Стартовый элемент ИЛИ 7 может быть технически реализован на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.24-26, рис.1.7].

Блоки стартовых 8 и опросных 10 элементов И (фиг.6 и 7 соответственно), входящие в общую структурную схему, идентичны, a m однотипных элементов И (8.11-8.1m и 10.11-10.1m соответственно), входящих в состав блоков стартовых 8 и опросных 10 элементов И, выполняют функции коммутирующих элементов при опросе содержимого соответственно стартового 6 и главного 11 счетчиков. Структура блоков стартовых 8 и опросных 10 элементов И известна, описана в прототипе (см. патент РФ №2011229, 5 G 09 В 9/00, 1994, бюл.7) и проиллюстрирована на фиг.6 и 7, а элементы И (8.11-8.1m и 10.11-10.1m), входящие в состав этих блоков, реализуются в виде известных и описанных в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.13-14, рис.1.2].

Триггер 9, входящий в общую структурную схему, предназначен для управления засветкой транспаранта «Упражнение» 15 или транспаранта «Тренировка» 16 табло 4 в соответствующем режиме обучения. Триггер 9 может быть технически реализован в виде серийно выпускаемого одноступенчатого триггера с коллекторно-базовыми связями, как показано в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.72-73, рис.3.2(б)].

Главный счетчик 11, входящий в общую структурную схему, предназначен для подсчета числа попыток, затраченных обучаемым до первого безошибочного выполнения алгоритма управления. Главный счетчик 11 может быть технически реализован в виде двоичного счетчика с последовательным переносом на Т-триггерах, как описано в литературе [Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987. С.138-141, рис.9.1.].

Дешифратор 12, входящий в общую структурную схему, предназначен для преобразования двоичного кода содержимого главного счетчика 11 в десятичный код в интересах представления (визуализации, показа) обучаемому номера попытки с помощью индикатора номера тренировки 17 табло 4. Дешифратор 12 может быть технически реализован в виде серийно выпускаемого дешифратора, описанного в книге [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С.432-436, рис.4.46].

Главный элемент ИЛИ 13, входящий в общую структурную схему, предназначен для объединения первого управляющего входа 013 блока задания программы обучения 1 с внешним входом «Запуск» устройства и вторым выходом 34 главного блока сравнения 3 для инициализации начала новой тренировки после включения устройства или совершения обучаемым ошибки. Главный элемент ИЛИ 13 может быть технически реализован на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.24-26, рис.1.7].

Установочный элемент ИЛИ 18, входящий в общую структурную схему, предназначен для объединения внешнего входа «Запуск» устройства с выходом 193 ответного блока сравнения 19 в интересах перевода триггера 9 в единичное состояние и введения режима «Упражнение». Установочный элемент ИЛИ 18 реализуется в виде типового элемента ИЛИ, описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.24-26, рис.1.7].

Ответный блок сравнения 19, входящий в общую структурную схему, предназначен для сравнения числа ошибок, которые сделал обучаемый, с допустимым числом ошибок. Ответный блок сравнения 19 может быть технически реализован в виде серийно выпускаемого узла сравнения (цифрового компаратора), описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.149-152, рис.5.19].

Регистр числа 20, входящий в общую структурную схему, предназначен для записи и хранения допустимого числа ошибок. Регистр числа 20 может быть технически реализован в виде серийно выпускаемого регистра хранения на D-триггерах, описанного в литературе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.156-158, рис.5.27].

Элемент задержки 21, входящий в общую структурную схему, предназначен для синхронизации моментов считывания информации с элементов И, входящих в состав блока стартовых элементов И 8, и из регистра числа 20 в ответный блок сравнения 19. Частным случаем технической реализации элемента задержки 21 может служить синхронный триггер задержки (D-триггер), структурная схема и принцип действия которого описаны в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.89-91, рис.3.14].

Устройство для обучения операторов функционирует следующим образом. Известно [1-5], что с точки зрения верификации и логико-аналитической поддержки принятия обучаемым управленческих решений, существует возможность идентификации заданных как количественно, так и качественно (недостоверно, неполно, противоречиво) исходных данных, используемых для принятия оператором конкретного решения в рамках обучения. Эта возможность реализуется путем последовательных преобразований с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих осуществить переход от недостоверно (недостаточно, неполно) поставленной задачи принятия обучаемым решения к параметрической задаче.

При этом принятое оператором в процессе упражнения или тренировки управленческое решение может быть верифицировано с помощью экспертов в рамках простейших, аппаратно реализуемых нейросетевых вычислительных методов и алгоритмов. Данная трактовка модели поддержки принятия решения позволяет в рамках программы обучения ввести алгоритм последовательного преобразования идентифицированных недостоверно (неполно) исходных данных, используемых для принятия конкретного решения и зафиксированных в рамках обучающих микрокоманд, к виду, пригодному для принятия обучаемым достоверного управленческого решения.

В рамках традиционной экспертной системы для решения задачи объединения мнений экспертов, знания которых используются для поддержки принятия решения в виде заранее сформированных данных о возможном состоянии системы управления, используется один