Блокирование исходных регистров в устройстве обработки данных

Иллюстрации

Показать всеИзобретение относится к блокированию исходных регистров в устройстве обработки данных. Техническим результатом является повышение эффективности конвейерной обработки данных. Устройство содержит процессор, имеющий конвейер для выполнения последовательности команд, и набор исходных регистров для сохранения исходных данных, запрашиваемых процессором при выполнении команд в последовательности. Механизм блокировки используют для блокирования исходных регистров, зависящих от настраиваемого критерия. Процессор работает в двух режимах работы. В первом режиме работы процессор после определения одного или нескольких исключительных состояний во время выполнения команды запускает процесс, внешний по отношению к конвейеру. Во втором режиме процессор завершает выполнение команды в конвейере, даже если определено наличие одного или нескольких исключительных состояний. 2 н. и 14 з.п. ф-лы, 9 ил., 2 табл.

Реферат

Область изобретения

Данное изобретение относится к блокированию исходных регистров в устройстве обработки данных.

Описание известного уровня техники

Известно обеспечение процессоров, которые включают в себя один или несколько конвейеров для выполнения команд. Из-за конвейерной природы таких процессоров, множественные команды могут находиться в процессе выполнения в любой момент времени, и это привело к необходимости обеспечения соответствующих функций проверки риска и ресурсов для конвейерного процессора. Следовательно, каждая команда обычно оценивается прежде, чем выдать ее в конвейер выполнения для определения того, возникнет ли условие риска или конфликт ресурса, если она будет выдана в конвейер выполнения. Условие риска будет обнаружено, если эта команда запрашивает элемент данных, который еще не является доступным из-за того, что он все еще вычисляется (например, командой, уже выполняемой в конвейере), или если эта команда требует доступа к регистру, который все еще запрашивается другой командой, уже находящейся в конвейере, и который не должен быть переписан, пока он не считывается другой командой уже в конвейере. Конфликт ресурса будет обнаружен, если есть требование для процессора, который не является доступным из-за того, что он уже используется для другой выполняющейся команды.

Можно не выполнять проверку риска и ресурса, а вместо этого оставить работу по избежанию условий риска и конфликтов ресурсов устройству записи компилятора/кода. Однако это обычно приводит к очень сложному коду, и соответственно, обычно такие процедуры проверки риска и ресурса реализуются.

Функции проверки риска и ресурса требуют способности останавливать соответствующий процессор и все зависимые процессоры. Например, сопроцессор, который детектирует условие риска, должен сигнализировать обнаружение этого условия риска главному процессору, и главный процессор в большинстве случаев остановится для поддержания координации потока команд с сопроцессором. Подобным же образом главный процессор, детектирующий условие риска или конфликт ресурса, должен сообщать всем сопроцессорам остановить их конвейеры соответственно. Понятно, что остановка вводит неопределенность в определение времени для запуска раздела кода.

Известные процессоры используют разнообразные сложные способы для детектирования условий риска и конфликтов ресурсов и для уменьшения воздействия таких условий риска и конфликтов ресурсов на производительность. Переименование регистров является одним из таких способов, которые могут использоваться, причем этот способ включает в себя использование дополнительных регистров для устранения условий риска, относящихся к записи рассматриваемого регистра как исходного регистра для уже выполняемой команды. В высокопроизводительных процессорах команды могут вызываться не по порядку программы, что дает возможность командам, которые не имеют риска или конфликтов ресурсов, выполняться перед командами с риском или конфликтами ресурсов. Обычным способом, используемым с таким подходом, является поддержание таблиц команд, находящихся в данный момент в некотором состоянии выполнения, и затем, для конкретной команды, проведение определения как доступности функционального блока для обработки команды, так и доступности операндов, запрашиваемых командой. Это может быть выполнено в известном способе путем использования, например, позиций резервирования, или в централизованном способе путем использования, например, способа буфера переупорядочения.

Оба вышеупомянутых способа хорошо известны в технике. Как понятно специалистам в данной области техники, стоимость таких способов, в терминах пространства и мощности, и в сложности, относительно высока.

Другие известные способы, которые снижают бульшую часть стоимости и уменьшают сложность вышеописанных способов, включают в себя использование табло. Табло отслеживает доступность регистров либо как исходные операнды, либо как пункты назначения для операций сохранения. Табло может быть разделено на отдельные части: одна - для исходных операндов и одна - для целевых операндов, или единое табло может поддерживаться как для исходных, так и для целевых операндов. Запись в табло очищается, когда регистр, связанный с этим входом, доступен для использования последующей командой. Следовательно, команды, подлежащие выдаче в конвейер выполнения, который потребует регистры, которые показаны как блокированные в табло, заставляют ждать или остановиться, пока регистры не станут доступными. Табло обычно проще и дешевле в смысле пространства, мощности и стоимости разработки, чем ранее описанные способы, но обычно предлагают более низкую производительность.

Соответственно, область приложения для устройства обработки данных обычно диктует то, какие из вышеупомянутых подходов используются. Для высокопроизводительных приложений, таких как приложение для настольной системы или научное приложение, или бизнес-приложение, более сложные способы часто требуются для распространения необходимой производительности. Машины, такие как CDC6600, IBM360/91, и недавние процессоры IBM, Intel x86 и Sun SPARC используют эти более сложные способы. Однако для встроенных приложений производительность обычно не является столь критической, а вместо этого участок кристалла процессора и потребляемая мощность имеют большую важность, с производительностью, просто необходимой, чтобы быть достаточной для выполнения цели приложения. В таких случаях, использование выдачи команды в порядке следования в программе и вышеописанного способа табло обычно является наиболее подходящим способом для проверки условий риска, в то время как использование ограниченного количества конвейеров, обычно одного или двух, помогает уменьшить сложность управления ресурсами.

Во многих приложениях выполняемые арифметические действия могут быть охарактеризованы таким образом, что диапазон операндов и результатов хорошо известен. Однако, когда это невозможно, арифметический блок должен быть способным обрабатывать непротиворечивым и разумным способом условия, в которых результат операции находится вне границ диапазона поддерживаемого типа данных, или операция включает в себя операнды, для которых результат не определен (например, сложение положительной бесконечности с отрицательной бесконечностью).

Рассматривая пример арифметики с плавающей точкой, «IEEE Standard for Binary Floating-Point Arithmetic», ANSI/IEE Std 754-1985, The Institute of Electrical and Electronic Engineers, Inc., New York, 10017 (далее называемый стандартом IEEE 754) определяет поведение команд, когда результаты находятся вне диапазона поддерживаемого типа данных или когда результат операции не определен. Для полной реализации технических условий IEEE 754 охват всех возможных случаев, которых может потребовать арифметика, приводит к дополнительному использованию аппаратного обеспечения/пространства и мощности, и/или сниженной тактовой частоте. Технические условия IEEE 754 определяют количество исключений, причем такие исключения являются случаями, в которых результат не является тем, что было бы возвращено, если бы арифметические действия выполнялись с неограниченной точностью, или если результат не определен. Пять типов исключения определены в технических условиях IEEE 754, а именно, недопустимость, переполнение, антипереполнение (потеря значимости), деление на ноль и неточность.

В наиболее встроенных приложениях арифметические действия могут характеризоваться как хорошо известные, и полные особенности технических условий IEEE 754 обычно не требуются. Например, такие особенности, как субнормальная поддержка и поддержка для обработки Nan (не является числом) может не требоваться. Однако способность обрабатывать условия переполнения и операции, включающие в себя бесконечности, обычно являются преимущественными.

При детектировании таких исключительных ситуаций во время выполнения команды в конвейерном процессоре, механизмы обработки исключительных ситуаций часто запускаются для обработки этих исключительных ситуаций. Такие механизмы обработки исключительных ситуаций при запуске могут нуждаться в доступе к исходным операндам для исключительной команды для того, чтобы иметь дело с исключительной ситуацией. Соответственно, при блокировании регистров для избежания условий риска, как это делается при использовании описанного ранее способа табло, в таких случаях необходимо блокировать эти исходные регистры, пока команда не дойдет до точки в конвейере выполнения, в которой исключительная ситуация будет детектирована.

В одном процессоре известного уровня техники, описанном более подробно в GB-A-2339312, процессор приспособлен для детектирования и обработки некоторых из исключительных случаев пессимистично, что означает, что определение наличия исключительного состояния основывается на информации, доступной прежде, чем команда обработана полностью. Для обеспечения того, что все возможные исключительные случаи обработаны, некоторые случаи, которые могут не привести к исключительному состоянию, рассматриваются как таковые, пока операция не обработана полностью и окончательное определение не сделано. В процессоре, описанном в GB-A-2339312, детектирование выполняется в первой стадии (каскаде) выполнения в конвейере процессора для минимизации количества информации, требуемой для сохранения текущего состояния процессора. Так как детектирование исключительной ситуации выполняется без завершения команды, требуется, чтобы исходные операнды были предварительно сохранены для механизма обработки исключительной ситуации, и не могут быть разблокированы в табло, пока связанная команда не пройдет точку детектирования исключительной ситуации (здесь стадия 1 выполнения конвейера). Системная программа затем используется для определения точного положения команды, генерирования правильного ответа, включая специальную обработку для исключительных случаев IEEE 754, и либо возврата к программе, либо запуска заданного пользователем обработчика исключительных ситуаций.

Следовательно, в заключение, системная программа, используемая для обработки исключительных ситуаций, требует доступа к исходным регистрам команды. Кроме того, она не будет выполняться, пока не пройдет некоторое количество циклов (тактов) после исключительной команды. Соответственно, команда, которая может нуждаться в доступе к исходным регистрам исключительной команды, может быть вызвана между выполнением исключительной команды и выполнением системной программы для того, чтобы иметь дело с идентифицированным исключительным состоянием.

Таким образом, любая команда, которая нуждается в доступе к исходным регистрам выполняющейся команды, для считывания их как операндов, сохранения их в памяти или загрузки их с новым значением, обычно должна ожидать, пока выполняемая команда не пройдет точку определения исключительной ситуации, и исходные регистры затем разблокируются в табло (либо потому, что не детектировано никакой исключительной ситуации, либо после того, как соответствующая системная программа выполнила необходимую обработку исключительной ситуации).

Следовательно, можно видеть, что это требование блокирования регистров в то время, когда осуществляется определение наличия исключительного состояния в соответствующей команде, может значительно повлиять на эффективность конвейерной схемы обработки посредством остановки последовательных команд, если они нуждаются в доступе к таким блокированным регистрам.

Краткое изложение существа изобретения

Согласно первому аспекту данное изобретение обеспечивает устройство обработки данных, содержащее: процессор, содержащий конвейер для выполнения последовательности команд; множество исходных регистров для сохранения исходных данных, запрашиваемых процессором при выполнении команд в последовательности; механизм блокировки для блокирования исходных регистров в зависимости от настраиваемых критериев, причем эти настраиваемые критерии выбираются для обеспечения того, что исходные регистры, все еще запрашиваемые для завершения выполнения команды в конвейере, были блокированы для предотвращения заданных типов доступа последующей командой, причем последующая команда способна только войти в конвейер, если исходные регистры, уместные для этой инструкции, могут быть доступны, как требуется этой командой; причем процессор имеет первый и второй режимы работы; в первом режиме работы процессор приспособлен, после определения одного или нескольких исключительных состояний во время выполнения команды, для запуска процесса, внешнего по отношению к блоку конвейерного выполнения, для того, чтобы сделать возможным выполнение команды, подлежащей завершению; во втором режиме работы процессор приспособлен для завершения выполнения команды в конвейере, даже если наличие указанного одного или нескольких исключительных состояний определено; причем механизм блокировки приспособлен для изменения настраиваемых критериев в зависимости от режима работы процессора таким образом, что уменьшение в количестве блокируемых исходных регистров может быть достигнуто во втором режиме работы.

В соответствии с данным изобретением процессор имеет два режима работы, причем первый режим работы является режимом, в котором процесс, внешний по отношению к конвейерному блоку выполнения, запускается после определения одного или нескольких исключительных состояний для того, чтобы сделать возможным выполнение команды, подлежащей завершению, тогда как во втором режиме работы процессор приспособлен для завершения выполнения команды в конвейере, даже если присутствуют одно или несколько исключительных состояний. Механизм блокировки используется для блокирования исходных регистров в зависимости от настраиваемых критериев, и механизм блокировки приспособлен для изменения настраиваемых критериев в зависимости от режима работы процессора, для того, чтобы сделать возможным уменьшение количества исходных регистров, блокируемых во втором режиме работы.

Поскольку вероятно, что процесс, внешний по отношению к блоку конвейерного выполнения, нуждается в доступе к исходным регистрам команды, для которой было детектировано исключительное состояние, ясно, что в первом режиме работы эти исходные регистры должны быть блокированы механизмом блокировки, пока не будет определено, что для этой команды не существует исключительных состояний, или пока эти исходные регистры не будут считаны процессом, внешним по отношению к блоку конвейерного выполнения, следующим за детектированием одного из этих исключительных условий. Во втором режиме работы процессор приспособлен таким образом, что он не нуждается в запуске какого-либо процесса, внешнего по отношению к блоку конвейерного выполнения, при рассмотрении любого из этих исключительных состояний, и соответственно, это позволяет избежать необходимости блокировать исходные регистры, пока не детектировано наличие этих одного или нескольких исключительных состояний.

Авторы данного изобретения понимают, что имеется два основных требования для защиты значения исходного регистра от перезаписи. Во-первых, это должно быть сделано, если в данных в исходном регистре нуждается команда, которая еще не считала регистр. Во-вторых, это должно быть сделано, если в данных в исходном регистре может нуждаться программа, которая еще не выполнялась, например, внешний процесс, используемый для обработки исключительных состояний. Во многих случаях наблюдалось, что первое требование было значительно менее затруднительным, чем второе требование. Исходные регистры, блокируемые для их сохранения для использования внешними процессами в случае детектируемого исключительного состояния, вызвали остановку последовательных команд вне того, что требуется для защиты исходных регистров, в то время как они еще не были считаны командой, определяющей их.

Данное изобретение значительно смягчает эту проблему посредством обеспечения второго режима работы, который устраняет необходимость в запуске процессов, внешних по отношению к блоку конвейерного выполнения для рассмотрения одного или нескольких исключительных состояний, и затем дает возможность механизму блокировки изменять настраиваемый критерий таким образом, что он просто больше не блокирует исходный регистр, так что они могут быть доступны таким внешним процессам.

В предпочтительных вариантах устройство обработки данных дополнительно содержит множество целевых регистров для сохранения целевых данных, являющихся результатом выполнения команд в последовательности, причем механизм блокировки дополнительно приспособлен для блокировки целевых регистров, зависящих от заданных критериев.

Когда команда определяет целевой регистр, ясно, что важно обеспечить то, что этот регистр блокирован, пока результат, генерируемый выполнением этой команды, не записан обратно в целевой регистр, для обеспечения того, что этот целевой регистр не считан или не записан, пока результат не будет сохранен в целевом регистре. Такое требование необходимо как в первом, так и во втором режиме работы, и соответственно, в предпочтительных вариантах заданные критерии, используемые для определения блокировки целевых регистров, являются одинаковыми как для первого, так и для второго режимов работы.

В предпочтительных вариантах механизм блокировки содержит: запись блокированных регистров; логические схемы проверки для определения со ссылкой на запись блокированных регистров, может ли последующая команда войти в конвейер; и логические схемы определения для определения для последующей команды, должны ли какие-либо из исходных регистров этой команды быть блокированы в записи, причем логические схемы определения чувствительны к настраиваемым критериям.

Соответственно, проверочные логические схемы определяют, указаны ли уже исходные и, необязательно, целевые регистры, определенные последующей командой, как блокированные в записи блокированных регистров, причем обычно последующей команде не разрешено войти в конвейер, если какой-либо из его исходных и целевых регистров указан как уже блокированный. Логические схемы определения определяют, должны ли какие-либо из исходных регистров и, необязательно, целевых регистров, определенных последующей командой, быть блокированными в записи, и поскольку логические схемы определения чувствительны к настраиваемым критериям, они обычно потребуют блокирования меньшего количества исходных регистров, когда схема обработки работает во втором режиме работы.

Понятно, что настраиваемые критерии могут быть определены большим количеством способов. Однако в предпочтительных вариантах настраиваемый критерий приспособлен в первом режиме работы таким образом, что, когда команда должна выполняться конвейером, механизм блокировки блокирует исходные регистры, требуемые этой командой, тогда как эти исходные регистры могут быть все еще перезаписаны перед тем, как они были считаны этой командой в конвейере или пока они могут быть все еще затребованы процессом, внешним по отношению к конвейеру, тогда как во втором режиме работы настраиваемый критерий приспособлен таким образом, что механизм блокировки блокирует исходные регистры, требуемые этой командой, только пока эти исходные регистры могут все еще быть перезаписаны перед тем, как они были считаны этой командой в конвейере.

Следовательно, во втором режиме работы исходные регистры блокированы для предотвращения возможности состояния риска «запись после считывания». Следовательно, желаемой ситуацией является такая, когда запись в исходный регистр должна происходить только после того, как считывание этого исходного регистра имеет место («запись после считывания»), и риск записи после считывания имеет место, когда эта ситуация нарушается. Соответственно, во втором режиме работы исходный регистр блокирован в течение любого периода времени, когда возможно, что этот исходный регистр может быть перезаписан перед тем, как он будет считан командой, определяющей этот исходный регистр. В первом режиме работы исходные регистры также блокированы для предотвращения таких рисков записи после считывания, но они дополнительно блокированы, тогда как они могут быть запрошены процессом, внешним по отношению к конвейеру.

С учетом вышеприведенного требования во втором режиме работы настраиваемый критерий обеспечен в предпочтительных вариантах данного изобретения таким образом, что механизм блокировки не блокирует какие-либо исходные регистры для скалярных команд или для векторных команд, имеющих количество итераций, меньшее или равное заданной величине. В реализациях в соответствии с предпочтительными вариантами осуществления данного изобретения было понятно, что нет возможности риска записи после считывания в связи с исходными регистрами скалярных команд или относительно коротких векторных команд (то есть векторных команд, имеющих количество итераций, меньшее или равное заданной величине).

В предпочтительных вариантах осуществления заданной величиной является четыре для векторных команд одинарной точности или для векторных команд двойной точности с производительностью в один такт и два для векторных команд двойной точности с производительностью в два такта.

Для простоты в предпочтительных вариантах данного изобретения настраиваемый критерий таков, что во втором режиме работы механизм блокировки рассматривает любую векторную команду двойной точности как имеющую производительность в два такта.

Процесс, внешний к конвейеру, который запускается в первом режиме работы после детектирования одной или нескольких исключительных ситуаций, может принимать разнообразные формы. Однако, предпочтительно, чтобы процессом, внешним к конвейеру, была либо служебная программа, либо запускаемая пользователем программа обработки исключительных ситуаций (ошибок).

Служебная программа выполняет три основных функции в предпочтительных вариантах данного изобретения. Во-первых, служебная программа может использоваться для обработки команд и типов данных, не поддерживаемых аппаратным обеспечением. Например, в предпочтительных вариантах осуществления оставшаяся команда не обеспечена в технических условиях архитектуры процессора, а требуется стандартом IEEE 754. Подобным же образом тип десятичных данных также не включен в технические условия архитектуры процессора, но требуется стандартом IEEE 754. В предпочтительных вариантах осуществления обработка, требуемая для обоих, существует в виде библиотечных функций, доступных для прикладной программы, выполняемой процессором.

Второй функцией, выполняемой служебной программой предпочтительных вариантов осуществления, является обработка команд со специфическими данными, для которых аппаратное обеспечение не способно полностью обрабатывать инструкцию, задавшей эти специфические данные, например, потенциальные состояния потери значимости или неправильные операнды. Некоторые из этих случаев могут также приводить к исключительным ситуациям, тогда как другие могут приводить к неисключительным результатам. Если команда приводит к исключительным ситуациям, для этой команды запускается запускаемая пользователем программа обработки исключительных ситуаций, затем служебная программа выполняет некоторую предварительную обработку, описанную ниже как третья основная функция служебной программы. Если команда не генерирует исключительное состояние или если все генерируемые исключительные состояния не имеют соответствующего набора битов, разрешающего исключительные ситуации, то служебная программа приспособлена для записи вычисленного результата в целевой регистр команды, а затем для возврата к прикладной программе, выполняемой процессором.

Третьей основной функцией служебной программы предпочтительных вариантов осуществления является предварительная обработка исключительных ситуаций, для которых установлен бит разрешения исключительной ситуации. Служебная программа является затем первой точкой входа для возвращенной команды. Команды могут быть возвращены для разрешения выполнения второй основной функции служебной программы, описанной выше, или из-за того, что истинное исключительное состояние было детектировано и установлен бит разрешения исключительной ситуации для этой исключительной ситуации. Если данные требуют проверки предусловия для запускаемой пользователем программы обработки исключительных ситуаций, служебная программа выполнит эту проверку предусловия. Запускаемая пользователем программа обработки исключительных ситуаций, если она выбирает возврат к прикладной программе, сделает это через служебную программу.

Вышеприведенные три функции служебной программы соответствуют первому режиму работы предпочтительных вариантов осуществления. Во втором режиме работы необходимость в использовании служебной программы устраняется посредством разрешения завершения выполнения команд в конвейере, даже если определено наличие одного или нескольких исключительных состояний.

Ясно, что первый и второй режимы работы процессора могут быть выполнены разнообразными способами в зависимости от реализации. Однако в предпочтительных вариантах осуществления первым режимом работы является соответствующий IEEE 754 режим работы, а вторым режимом работы является не соответствующий IEEE 754 режим работы, который избегает необходимости в системных программах для обработки указанного одного или нескольких исключительных состояний. В предпочтительных вариантах осуществления первым режимом работы процессора является соответствующий IEEE 754 режим работы посредством обеспечения служебной программы, причем служебная программа вызывается, когда аппаратное обеспечение процессора не способно обработать команду со специфическими операндами. Во втором режиме работы некоторые из особенностей стандарта IEEE 754, которые не требуются в некоторых приложениях, не обрабатываются согласно техническим условиям IEEE 754, а вместо этого обрабатываются не соответствующим способом для того, чтобы устранить необходимость в использовании процесса, внешнего к блоку конвейерного выполнения.

Специалистам в данной области техники понятно, что при поддержании записи как исходных, так и целевых регистров, существуют разнообразные способы, которыми может быть скомпонован механизм блокировки. В предпочтительных вариантах осуществления, для простоты, механизм блокировки поддерживает единственную запись как для исходных, так и для целевых регистров, и следовательно, не делает различия между этими двумя типами регистров. Однако в альтернативном варианте осуществления механизм блокировки содержит первую запись для записи блокированных целевых регистров и вторую запись для записи блокированных исходных регистров.

Хотя этот альтернативный подход некоторым образом повышает сложность, он разрешает некоторую вариацию в заданных типах доступа, которые ограничены блокированным регистром, в зависимости от того, является ли этот регистр целевым регистром или исходным регистром. Более конкретно, с этой альтернативной реализацией, если последующей команде необходимо выполнить какой-либо тип доступа к целевому регистру, указанному как блокированный в первой записи, она будет остановлена от входа в конвейер, пока блокировка не будет очищена из первой записи, тогда как если последующей команде только необходимо выполнить доступ считывания одного или нескольких исходных ресурсов, блокированных во второй записи, ей будет разрешено войти в конвейер без необходимости ожидать очищения соответствующих блокировок из второй записи. Если конкретный регистр не определен как целевой регистр, то ясно, что данные, сохраняемые в этом регистре, не будут изменяться любой из команд, уже находящихся в конвейере. Соответственно, безопасно позволить последующей команде считать такой регистр, и так как акт считывания регистра не изменяет значение, сохраняемое в регистре, допустимо считывать исходный регистр, даже когда он был блокирован командой, уже находящейся в конвейере.

Специалистам в данной области техники понятно, что существует разнообразие способов, в которых процессор может быть скомпонован для завершения выполнения команды в конвейере даже в присутствии одного или нескольких исключительных состояний. В предпочтительных вариантах осуществления во втором режиме работы процессор приспособлен для применения режима сброса на нуль для замены любых исходных данных или результирующих данных в неправильном (ненормальном) диапазоне с положительным нулем. Было обнаружено, что этот режим работы устраняет сложность и аппаратное обеспечение, которое в ином случае потребовалось бы для обработки неправильных значений данных, с никаким или очень небольшим арифметическим влиянием на хорошо понятные алгоритмы.

Кроме того, во втором режиме работы предпочтительных вариантов осуществления процессор приспособлен для применения режима по умолчанию Nan (не является числом) для получения в качестве результирующих данных Nan по умолчанию, если какое-либо из исходных данных является Nan. Этот подход обрабатывает Nan согласно техническим условиям IEEE 754, но не совместим с обычной практикой. Тем не менее, он все еще обеспечивает обработку Nan как указания неопределенной арифметической операции.

Кроме того, во втором режиме работы предпочтительных вариантов осуществления процессор приспособлен обрабатывать в аппаратном обеспечении процессора любые исключительные состояния переполнения, неточности, деления на ноль или недопустимости. Более конкретно, в предпочтительных вариантах осуществления полная обработка по умолчанию обеспечена для исключительных ситуаций переполнения, неточности и деления на ноль в аппаратном обеспечении, и почти полная обработка по умолчанию обеспечена для исключительных ситуаций недопустимости в аппаратном обеспечении. Было обнаружено, что этот подход обеспечивает близкое соответствие IEEE 754 и является подходящим для большинства встроенных приложений, которые используют переполнение для насыщения и бесконечность для особых ситуаций обработки.

С точки зрения второго аспекта, данное изобретение обеспечивает способ управления устройством обработки данных, имеющим процессор, содержащий конвейер для выполнения последовательности команд, и набор исходных регистров для сохранения исходных данных, требуемых процессором при выполнении команд в этой последовательности, причем этот способ предусматривает стадии: (i) использования механизма блокировки для блокирования исходных регистров в зависимости от настраиваемого критерия, причем настраиваемый критерий выбирается для того, чтобы гарантировать то, что исходные регистры, все еще требуемые для завершения выполнения команды в конвейере, блокированы для того, чтобы воспрепятствовать заданным типам доступа последующей командой, причем последующая команда способна только войти в конвейер, если исходные регистры, соответствующие для этой команды, могут быть доступны по требованию команды; (ii) выбора первого или второго режима работы для процессора, причем в первом режиме работы конвейерный процессор приспособлен, после определения одного или нескольких исключительных состояний во время выполнения команды, запускать процесс, внешний по отношению к блоку конвейерного выполнения, для того, чтобы дать возможность завершиться выполнению команды, во втором режиме работы конвейерный процессор приспособлен для завершения выполнения команды в конвейере, даже если определено наличие указанного одного или нескольких исключительных состояний; и (iii) изменения механизмом блокировки настраиваемого критерия в зависимости от режима работы процессора таким образом, что уменьшение в количестве блокированных исходных регистров может быть достигнуто во втором режиме работы.

Краткое описание чертежей

Данное изобретение будет описано далее только посредством примера со ссылкой на его предпочтительный вариант осуществления, проиллюстрированный на сопроводительных чертежах, в которых:

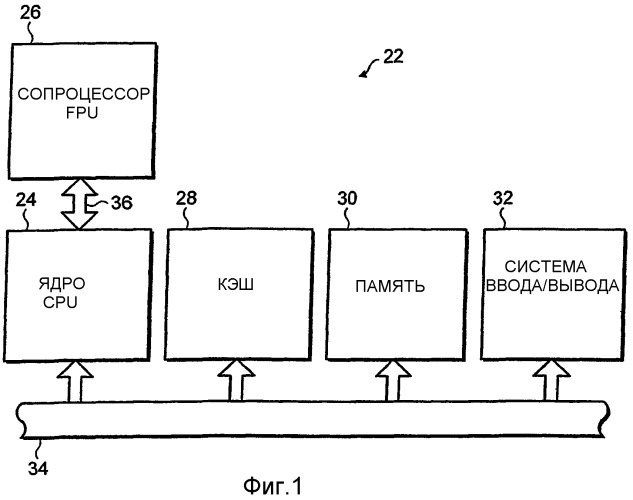

фиг.1 является блок-схемой, показывающей элементы устройства обработки данных в соответствии с предпочтительными вариантами осуществления данного изобретения;

фиг.2А является блок-схемой, показывающей элементы сопроцессора согласно фиг.1, в соответствии с предпочтительными вариантами осуществления данного изобретения;

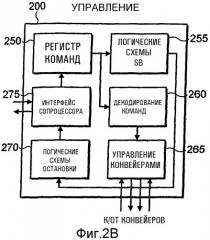

фиг.2В является блок-схемой, показывающей более подробно элементы, обеспеченные в управляющих логических схемах сопроцессора в соответствии с предпочтительными вариантами осуществления данного изобретения;

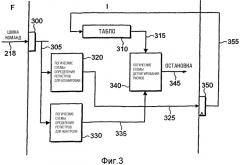

фиг.3 является схемой, схематически показывающей работу логических схем табло в соответствии с предпочтительными вариантами осуществления данного изобретения;

фиг.4 является блок-схемой, показывающей основной поток конвейеров в пределах ядра процессора и сопроцессора в соответствии с предпочтительными вариантами осуществления данного изобретения;

фиг.5А и 5В являются схемами, показывающими последовательность выполнения каскадных арифметических операций в первом режиме работы и втором режиме работы, соответственно, где вторая команда имеет в качестве целевого регистра исходный регистр первой команды;

фиг.6А и 6В являются диаграммами, показывающими последовательность выполнения арифметической команды, за которой следует команда загрузки в первом режиме работы и втором режиме работы, соответственно, в которой команда загрузки осуществляет запись в один или несколько исходных регистров арифметической команды;

фиг.7А - 7С показывают последовательность выполнения векторной команды, за которой следует команда загрузки, причем первый режим работы показан на фиг.7А, а второй режим работы показан на фиг.7В и 7С;

фиг.8А и 8В показывают последовательность выполнения векторной команды одинарной точности и векторной команды удвоенной точности, соответственно, в обоих случаях за командой следует команда загрузки, и показывают условия, которые делают необходимым блокирование исходных регистров; и

фиг.9А - 9F являются таблицами, показывающими, как исходные регистры блокируются и очищаются как для команд одинарной точности, так и для команд двойной точности как для первого режима работы, так и для второго режима работы.

Описание предпочтительного варианта осуществления

Фиг.1 показывает систему 22 обработки данных, содержащую основной процессор 24, сопроцессор 26 с плавающей точкой (FPU), кэш-память 28, основную память 30 и систему 32 ввода/вывода. Основной процессор 24, кэш-память 28, основная память 30 и система 32 ввода/вывода соединены через основную шину 34. Шина 36 сопроцессора связывает основной процессор 24 с сопроцессором 26 с плавающей точкой.

При работе основной процессор 24 (также называемый ядром ARM) выполняет поток команд обработки данных, которые управляют операциями обработки данных общего типа, включая взаимодействия с кэш-памятью 28, основной памятью 30 и системой 32 ввода/вывода. Команды сопроцессора встроены в поток команд обработки данных. Основной процессор 24 распознает эти команды сопроцессора как имеющие тип, который должен выполняться присоединенным сопроцессором. Соответственно, основной процессор 24 выдает эти команды сопроцессора на шину сопроцессора 36, откуда они принимаются любыми присоединенными сопроцессорами. В этом случае сопроцессор 26 FPU будет принимать и выполнять любые принятые команды сопроцессора, которые, как он обнаруживает, предназначены для него. Это обнаружение происходит через поле номера сопроцессора в команде сопроцессора.

Фиг.2А является блок-схемой, показывающей более подробно элементы, обеспеченные в сопроцессоре 26 в соответствии с предпочтительными вариантами осуществления данного изобретения. Сопроцессор 26 включает в себя арифметический конвейерный блок 230 для выполнения арифметических операций. Регистровый файл 220 обеспечен состоящим из нескольких регистров, которые могут быть определены либо как исходные, либо как ц