Функциональный аналого-цифровой преобразователь

Иллюстрации

Показать всеУстройство относится к области автоматики и вычислительной технике и может быть использовано для преобразования функционально связанных аналоговых сигналов в цифровой код (например, угла поворота вала в цифровой код). Техническим результатом является возможность изменения функциональных настроек блоков, входящих в состав функционального аналого-цифрового преобразователя, а также унификация конструкции и настройки соответствующих блоков устройства. Технический результат достигается тем, что в функциональный аналого-цифровой преобразователь дополнительно введены входной и выходной мультиплексоры, буферный регистр, первый и второй повторители, первый и второй компараторы, фазовращатель, первая, вторая, третья и четвертая цепи демодуляции. Причем используемые в составе блоков повторители, компараторы, инверторы, релейные ключи и фильтры низких частот имеют соответственно одинаковую конструкцию и настройки. 3 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике, а именно к преобразователям функционально связанных аналоговых сигналов в цифровой код.

Известен функциональный аналого-цифровой преобразователь [1], содержащий цифроаналоговый преобразователь, интегратор, компараторы, фазовращатель, реверсивный счетчик, блок памяти, блок управления, триггеры, логические устройства ИЛИ-НЕ и И.

Наиболее близким по технической сущности является функциональный аналого-цифровой преобразователь [2], содержащий первый и второй умножающие цифроаналоговые преобразователи (УЦАП), преобразователь кодов, интегратор, блок определения знака, контроллер, реверсивный счетчик, причем параллельный выход преобразователя кодов подключен к входу первого УЦАП.

Недостатком такого функционального аналого-цифрового преобразователя является вызванная большой номенклатурой элементов и связей между ними сложность устройства функционального аналого-цифрового преобразователя, а также неполное использование возможностей примененных элементов.

Техническим результатом изобретения является расширение функциональных возможностей и упрощение устройства функционального аналого-цифрового преобразователя.

Данный технический результат достигается в функциональном аналого-цифровом преобразователе, содержащем первый и второй умножающие цифроаналоговые преобразователи (УЦАП), преобразователь кодов, интегратор, блок определения знака, контроллер, реверсивный счетчик, причем параллельный выход преобразователя кодов подключен к входу первого УЦАП, тем, что его первым входом является выход синусной обмотки первого канала синусно-косинусного вращающегося трансформатора (СКВТ), вторым входом является выход косинусной обмотки первого канала СКВТ, третьим входом является выход синусной обмотки второго канала СКВТ, четвертым входом является выход косинусной обмотки второго канала СКВТ, пятым входом является выход электронного генератора, имеет шину связи с процессором, в него введены входной мультиплексор, выходной мультиплексор, буферный регистр, первый и второй повторители, первый и второй инверторы, первый и второй релейные ключи, первый и второй компараторы, фазовращатель, выполнены первая, вторая, третья и четвертая цепи демодуляции, каждая из которых содержит третий и четвертый повторители, третий инвертор, третий релейный ключ, фильтр низких частот (ФНЧ), причем к выходу третьего повторителя подключены входы четвертого повторителя и третьего инвертора, выход четвертого повторителя соединен с размыкающим контактом третьего релейного ключа, выход третьего инвертора соединен с замыкающим контактом третьего релейного ключа, выход которого подключен к входу ФНЧ; входы третьего повторителя в первой, второй, третьей и четвертой цепях демодуляции являются соответственно первым, вторым, третьим и четвертым входами функционального аналого-цифрового преобразователя; вход первого компаратора является пятым входом функционального аналого-цифрового преобразователя, выход первого компаратора подсоединен к входу фазовращателя и к управляющим входам третьего релейного ключа в первой и второй цепях демодуляции, выход фазовращателя подключен к входу второго компаратора, к выходу которого подсоединены управляющие входы третьего релейного ключа в третьей и четвертой цепях демодуляции, блок определения знака образован в составе третьего компаратора и интегратора, выполненного как разностный интегрирующий каскад, преобразователь кодов имеет прошивку синуса угла от 0 до 180°, выходы ФНЧ первой, второй, третьей и четвертой цепей демодуляции подключены к входам входного мультиплексора, первый выход входного мультиплексора подключен к входам первого повторителя и первого инвертора, выход первого повторителя соединен с размыкающим контактом первого релейного ключа, к замыкающему контакту которого подключен выход первого инвертора, выход первого релейного ключа соединен с умножающим входом первого УЦАП, второй выход входного мультиплексора подключен к входам второго повторителя и второго инвертора, выход второго повторителя подключен к размыкающему контакту второго релейного ключа, к замыкающему контакту которого подсоединен выход второго инвертора, выход второго релейного ключа подключен к умножающему входу второго УЦАП, параллельный выход преобразователя кодов подсоединен к входу второго УЦАП, выход первого УЦАП подключен к первому входу разностного интегрирующего каскада, к второму входу которого подключен выход второго УЦАП, выход разностного интегрирующего каскада подсоединен к входу третьего компаратора, выход которого соединен с контроллером, выходы выходного мультиплексора соединены первой шиной с входом преобразователя кодов, второй шиной - с входами буферного регистра, выходы реверсивного счетчика подключены к входам выходного мультиплексора, шина связи с процессором соединена с буферным регистром, первый выход контроллера соединен с входом записи первого УЦАП, второй выход соединен с входом записи второго УЦАП, третий выход соединен со старшим адресным входом преобразователя кодов, четвертый выход соединен с управляющим входом первого релейного ключа, пятый выход соединен с управляющим входом второго релейного ключа, шестой выход соединен с тактовым входом реверсивного счетчика, седьмой выход соединен с входом разрешения записи реверсивного счетчика, восьмой выход соединен с входом выбора знака счета реверсивного счетчика, выходы контроллера также соединены шинами с входами управления входного мультиплексора и выходного мультиплексора.

Выполнение четырех идентичных цепей демодуляции, введение идентичных повторителей, инверторов, компараторов, релейных ключей позволяют уменьшить номенклатуру элементов функционального аналого-цифрового преобразователя, что приводит к более простому его выполнению.

Выполнением одного преобразователя кодов с прошивкой синуса угла от 0 до 180° достигается упрощение устройства функционального аналого-цифрового преобразователя.

Введение входного и выходного мультиплексоров, выполнение четырех цепей демодуляции с двумя повторителями, инвертором, ФНЧ и релейным ключом позволяют расширить функциональные возможности функционального аналого-цифрового преобразователя при ограниченном количестве его элементов за счет более полного использования их возможностей, так как производится преобразование сигналов синусных и косинусных обмоток СКВТ, имеющего первый канал (например, грубый) и второй канал (точный).

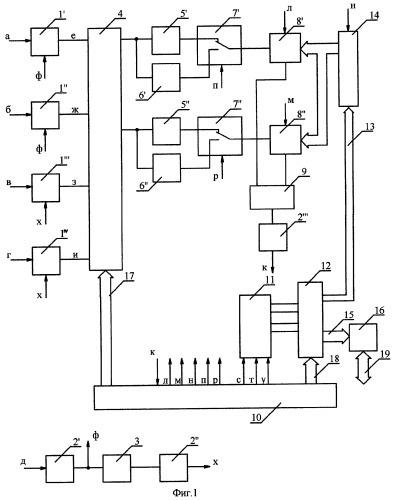

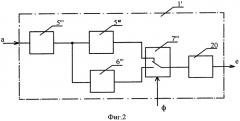

На фиг.1 представлена схема функционального аналого-цифрового преобразователя, на фиг.2 - схема одной из цепей демодуляции функционального аналого-цифрового преобразователя, на фиг.3 - циклограммы сигналов в функциональном аналого-цифровом преобразователе.

В функциональном аналого-цифровом преобразователе (фиг.1) выполнены подключенный к входу первой цепи демодуляции 1' первый вход "а" от синусной обмотки первого (например, грубого) канала СКВТ, подключенный к входу второй цепи демодуляции 1" второй вход "б" от косинусной обмотки первого канала СКВТ, подключенный к входу третьей цепи демодуляции 1''' третий вход "в" от синусной обмотки второго (точного) канала СКВТ, подключенный к входу четвертой цепи демодуляции 1IV четвертый вход "г" от косинусной обмотки второго канала СКВТ, подключенный к входу первого компаратора 2' пятый входа "д" от электронного генератора. Выход первого компаратора 2' подсоединен к входу фазовращателя 3, выход которого подключен к входу второго компаратора 2''.

Выходы "е" первой цепи демодуляции 1', "ж" второй цепи демодуляции 1'', "з" третьей цепи демодуляции 1''', "и" четвертой цепи демодуляции 1IV подключены к входам входного мультиплексора 4, первый выход которого подсоединен к входам первого повторителя 5' и первого инвертора 6'. Второй выход входного мультиплексора 4 подключен к входам второго повторителя 5'' и второго инвертора 6''.

Выход первого повторителя 5' подключен к размыкающему контакту первого релейного ключа 7', к замыкающему контакту которого подсоединен выход первого инвертора 6'. Выход первого релейного ключа 7' подсоединен к умножающему входу первого УЦАП 8'. Выход второго повторителя 5'' подключен к размыкающему контакту второго релейного ключа 7'', к замыкающему контакту которого подсоединен выход второго инвертора 6''. Выход второго релейного ключа 7'' подключен к умножающему входу второго УЦАП 8''. Блок определения знака образован в составе третьего компаратора 2''' и интегратора, выполненного как разностный интегрирующий каскад 9. Выход первого УЦАП 8' подключен к первому входу разностного интегрирующего каскада 9, к второму входу которого подсоединен выход второго УЦАП 8''. Выход разностного интегрирующего каскада 9 подключен к входу третьего компаратора 2''', выход "к" которого подсоединен к входу контроллера 10.

Выходы реверсивного счетчика 11 подсоединены к входам выходного мультиплексора 12, выходы которого соединены первой шиной 13 с входом преобразователя кодов 14, а второй шиной 15 - с входами буферного регистра 16.

Преобразователь кодов 14 имеет прошивку синуса угла от 0 до 180°, и его параллельный выход подключен к входам первого УЦАП 8' и второго УЦАП 8''.

Первый выход "л" контроллера 10 соединен с входом записи первого УЦАП 8', второй выход "м" - с входом записи второго УЦАП 8'', третий выход "н" - со старшим адресным входом преобразователя кодов 14, четвертый выход "п" - с управляющим входом первого релейного ключа 7', пятый выход "р" - с управляющим входом второго релейного ключа 7'', шестой выход "с" - с тактовым входом реверсивного счетчика 11, седьмой выход "т" - с входом разрешения записи реверсивного счетчика 11, восьмой выход "у" - с входом выбора знака счета реверсивного счетчика 11. Выходы контроллера 10 также соединены шинами 17, 18 с входами управления входного мультиплексора 4 и выходного мультиплексора 12. В контроллере 10 выполнены генератор тактовой частоты, делители частоты и распределитель.

Шина 19 связи функционального аналого-цифрового преобразователя с процессором соединена с буферным регистром 16.

В первой цепи демодуляции 1' (фиг.2) первый вход "а" функционального аналого-цифрового преобразователя соединен с входом третьего повторителя 5''', к выходу которого подключены входы четвертого повторителя 5IV и третьего инвертора 6'''. Выход четвертого повторителя 5IV соединен с размыкающим контактом третьего релейного ключа 7''', замыкающий контакт которого подключен к выходу третьего инвертора 6'''. Выход третьего релейного ключа 7''' подключен к входу ФНЧ 20, выход "е" которого соединен с входом входного мультиплексора 4. Управляющий вход третьего электронного ключа 7''' соединен с выходом "ф" первого коммутатора 2'.

Вторая 1", третья 1''' и четвертая 1IV цепи демодуляции выполнены идентично с первой цепью демодуляции 1' (фиг.1). К управляющему входу третьего релейного ключа 7''' во второй цепи демодуляции 1" подключен выход "ф" первого компаратора 4'. К управляющим входам третьих электронных ключей 7''' в третьей 1''' и четвертой 1IV цепях демодуляции подключен выход "х" второго компаратора 2".

Функциональный аналого-цифровой преобразователь работает следующим образом. На входы "а", "б", "в", "г" функционального аналого-цифрового преобразователя подаются сигналы от синусных и косинусных обмоток первого (грубого) и второго (точного) каналов СКВТ. Угол поворота второго канала СКВТ в 2n раз (n - коэффициент редукции между грубым и точным каналами СКВТ) больше угла поворота первого канала. На первый вход "а" и третий вход "в" поступает напряжение

где Um - амплитуда напряжения возбуждения СКВТ,

ω - круговая частота напряжения возбуждения СКВТ от электронного генератора,

ϕ - угол поворота первого канала СКВТ или второго канала СКВТ.

На второй вход "б" и четвертый вход "г" подается напряжение

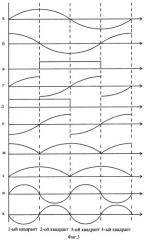

При подаче на управляющий вход третьего релейного ключа 7''' первой цепи демодуляции 1' импульсов с выхода "ф" первого компаратора 2' на выходе "е" первой цепи демодуляции 1' образуется напряжение, пропорциональное синусу угла поворота первого канала (фиг.3, а)

Фазовращатель 3 компенсирует сдвиг фазы между первым и вторым каналами СКВТ. Поэтому при подаче импульсов с выхода "х" второго компаратора 2'' на выходе третьей цепи демодуляции 1''' образуется напряжение, пропорциональное синусу угла поворота второго канала.

При подаче импульсов с выходов "ф", "х" первого компаратора 2' и второго компаратора 2'' соответственно на выходах "ж", "и" второй 1'' и четвертой 1IV цепей демодуляции образуется напряжение (фиг.3, б), пропорциональное косинусу угла поворота первого и второго каналов,

Входной мультиплексор 4 подает на свой первый выход напряжение U3 сначала от первого канала СКВТ, а затем от второго канала СКВТ.

По сигналу с четвертого выхода "п" контроллера 10 (фиг.3, в) с выхода первого релейного ключа 7' на умножающий вход первого УЦАП 8' идет сигнал, имеющий положительную фазу в первом и третьем квадрантах (фиг.3, г).

Входной мультиплексор 4 подает на свой второй выход напряжение U4 сначала от первого канала СКВТ, а затем от второго канала СКВТ.

По сигналу с пятого выхода "р" контроллера 10 (фиг.3, д) с выхода второго релейного ключа 7'' на умножающий вход второго УЦАП 8'' идет сигнал, имеющий положительную фазу во втором и четвертом квадрантах (фиг.3, е).

Путем подачи с шестого выхода "с" контроллера 10 на тактовый вход реверсивного счетчика 11 импульсов от генератора тактовой частоты контроллера 10 в реверсивном счетчике 11 формируется цифровой код, пропорциональный выходному углу θ. Параллельный двоичный код с выхода реверсивного счетчика 11 поступает на вход выходного мультиплексора 12, который по сигналам по шине 18 от контроллера 10 подключает посредством первой шины 13 к преобразователю кодов 14 k-разрядный код или от старших разрядов (грубый канал) реверсивного счетчика 11, или от его младших разрядов (точный канал).

Далее от преобразователя кодов 14 на цифровой вход первого УЦАП 8' поступает код, изменяющийся по времени как cosθ (фиг.3, ж), а на цифровой вход второго УЦАП 8'' - код, изменяющийся по времени как sinθ (фиг.3, з).

При получении сигнала с первого выхода "л" контроллера 10 на вход записи первого УЦАП 8' на его выходе образуется напряжение (фиг.3, и)

По сигналу с второго выхода "м" контроллера 10 на выходе второго УЦАП 8'' образуется напряжение (фиг.3, к)

После преобразования напряжений U5, U6 в разностном интегрирующем каскаде 9 на его выходе формируется напряжение рассогласования

В третьем компараторе 2''' формируется сигнал знака напряжения рассогласования U7, который подается с его выхода "к" в контроллер 10, а контроллер 10 выдает сигнал с восьмого выхода "у" на вход выбора знака счета реверсивного счетчика 11. В зависимости от знака напряжения рассогласования U7 реверсивный счетчик 11 изменяет код выходного угла θ, приводящий к обнулению напряжения рассогласования U7. В момент равенства напряжения рассогласования U7 нулю выходной угол θ равен входному углу ϕ. После того как напряжения рассогласования сравняются с нулем в грубом и точном каналах, откорректированный выходной код угла θ по второй шине 15 переписывается в буферный регистр 16, откуда по шине 19 он поступает в процессор.

Контроллер 10 синхронизирует сигналы от третьего компаратора 2''' с определенным временным циклом преобразования и формирует сигналы управления по шине 17 входного мультиплексора 4, по шине 18 выходного мультиплексора 12, с седьмого выхода "т" на вход разрешения записи реверсивного счетчика 11 и с третьего выхода "н" на старший адресный вход преобразователя кодов 14.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Авторское свидетельство СССР №1329570 А1, кл. Н 03 М 1/48. Преобразователь угла поворота вала в код. 1985 г.

2. Авторское свидетельство СССР №1424124 А1, кл. Н 03 М 1/48. Преобразователь угла поворота вала в код. 1987 г.

Функциональный аналогово-цифровой преобразователь, содержащий первый и второй умножающие цифроаналоговые преобразователи (УЦАП), преобразователь кодов, интегратор, блок определения знака, контроллер, реверсивный счетчик, причем параллельный выход преобразователя кодов подключен к входу первого УЦАП, отличающийся тем, что его первым входом является выход синусной обмотки первого канала синусно-косинусного вращающегося трансформатора (СКВТ), вторым входом является выход косинусной обмотки первого канала СКВТ, третьим входом является выход синусной обмотки второго канала СКВТ, четвертым входом является выход косинусной обмотки второго канала СКВТ, пятым входом является выход электронного генератора, с шиной связи с процессором, в него введены входной мультиплексор, выходной мультиплексор, буферный регистр, первый и второй повторители, первый и второй инверторы, первый и второй релейные ключи, первый и второй компараторы, фазовращатель, выполнены первая, вторая, третья и четвертая цепи демодуляции, каждая из которых содержит третий и четвертый повторители, третий инвертор, третий релейный ключ, фильтр низких частот (ФНЧ), причем к выходу третьего повторителя подключены входы четвертого повторителя и третьего инвертора, выход четвертого повторителя соединен с размыкающим контактом третьего релейного ключа, выход третьего инвертора соединен с замыкающим контактом третьего релейного ключа, выход которого подключен к входу ФНЧ, входы третьего повторителя в первой, второй, третьей и четвертой цепях демодуляции являются соответственно первым, вторым, третьим и четвертым входами функционального аналого-цифрового преобразователя; вход первого компаратора является пятым входом функционального аналого-цифрового преобразователя, выход первого компаратора подсоединен к входу фазовращателя и к управляющим входам третьего релейного ключа в первой и второй цепях демодуляции, выход фазовращателя подключен к входу второго компаратора, к выходу которого подсоединены управляющие входы третьего релейного ключа в третьей и четвертой цепях демодуляции, блок определения знака образован в составе третьего компаратора и интегратора, выполненного как разностный интегрирующий каскад, преобразователь кодов имеет прошивку синуса угла от 0-180°, выходы ФНЧ первой, второй, третьей и четвертой цепей демодуляции подключены к входам входного мультиплексора, первый выход входного мультиплексора подключен к входам первого повторителя и первого инвертора, выход первого повторителя соединен с размыкающим контактом первого релейного ключа, к замыкающему контакту которого подключен выход первого инвертора, выход первого релейного ключа соединен с умножающим входом первого УЦАП, второй выход входного мультиплексора подключен к входам второго повторителя и второго инвертора, выход второго повторителя подключен к размыкающему контакту второго релейного ключа, к замыкающему контакту которого подсоединен выход второго инвертора, выход второго релейного ключа подключен к умножающему входу второго УЦАП, параллельный выход преобразователя кодов подсоединен к входу второго УЦАП, выход первого УЦАП подключен к первому входу разностного интегрирующего каскада, к второму входу которого подключен выход второго УЦАП, выход разностного интегрирующего каскада подсоединен к входу третьего компаратора, выход которого соединен с контроллером, выходы выходного мультиплексора соединены первой шиной с входом преобразователя кодов, второй шиной с входами буферного регистра, выходы реверсивного счетчика подключены к входам выходного мультиплексора, шина связи с процессором соединена с буферным регистром, первый выход контроллера соединен с входом записи первого УЦАП, второй выход соединен с входом записи второго УЦАП, третий выход соединен с управляющим входом второго релейного ключа, пятый выход соединен с управляющим входом второго релейного ключа, шестой выход соединен с тактовым входом реверсивного счетчика, седьмой выход соединен с входом разрешения записи реверсивного счетчика, восьмой выход соединен с входом выбора знака счета реверсивного счетчика, выходы контроллера также соединены шинами с входами управления входного мультиплексора.