Дифференциальный усилитель

Иллюстрации

Показать всеУстройство относится к области радиотехники. Техническим результатом при изобретения является повышение выходного сопротивления и, как следствие, увеличение коэффициента усиления по напряжению в режиме холостого хода. Устройство содержит входной дифференциальный каскад, первое, второе, третье и четвертое токовые зеркала, кроме того, в него введены р-n-р и n-р-n дополнительные транзисторы, причем базы этих дополнительных транзисторов соединены с основным выходом дифференциального усилителя, эмиттер р-n-р дополнительного транзистора соединен с выходом первого токового зеркала, а его коллектор связан со входом четвертого токового зеркала, эмиттер n-р-n дополнительного транзистора соединен с выходом второго токового зеркала, а его коллектор подключен ко входу третьего токового зеркала. 6 з.п. ф-лы, 16 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны дифференциальные усилители (ДУ) на базе нескольких токовых зеркал, которые стали основой построения многих современных операционных усилителей [1-21]. Однако они имеют недостаточно высокое собственное выходное сопротивление и, как следствие, небольшой коэффициент усиления по напряжению в режиме холостого хода на выходе (т.е. при бесконечно большом сопротивлении нагрузки). Проблема повышения выходного сопротивления ДУ данного класса, которые широко используются в операционных усилителях с «минимальной электрической длиной», относящихся к числу наиболее широкополосных двухтактных структур, является одной из актуальных проблем современной аналоговой микросхемотехники.

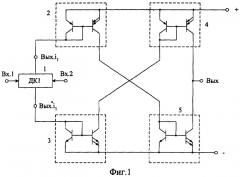

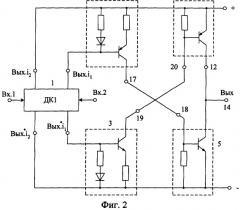

Ближайшим прототипом (фиг.1, фиг.2) заявляемого устройства является дифференциальный усилитель [Патент США №4404528, H 03 f 3/26, Патент Японии 53-25232, 98(5) А33, H 03 f 3/26], содержащий входной дифференциальный каскад, первое, второе, третье и четвертое токовые зеркала, причем вход первого токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной положительного источника питания, вход второго токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной отрицательного источника питания, а выходы третьего и четвертого токовых зеркал соединены с основным выходом дифференциального усилителя.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокое собственное выходное сопротивление в разомкнутом состоянии (Rвых), которое определяется величинами выходных сопротивлений применяемых токовых зеркал. Для современных интегральных транзисторов, например, ФГУП «Пульсар», выходное сопротивление типовых токовых зеркал лежит в диапазоне единиц-десятков килом, что не позволяет получить на базе известного ДУ большие коэффициенты усиления по напряжению:

где S - крутизна преобразования входного напряжения ДУ в его выходной ток.

Так, при типовых S=0,01 Ом-1 входного дифференциального каскада можно получить Ку.max=100÷200.

Основная цель предлагаемого изобретения состоит в повышении выходного сопротивления ДУ на один-два порядка, что позволяет (при малой проводимости нагрузки) получить существенное улучшение коэффициента усиления по напряжению.

Поставленная цель достигается тем, что в дифференциальный усилитель, содержащий входной дифференциальный каскад, первое, второе, третье и четвертое токовые зеркала, причем вход первого токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной положительного источника питания, вход второго токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной отрицательного источника питания, а выходы третьего и четвертого токовых зеркал соединены с основным выходом дифференциального усилителя, вводятся новые элементы и связи между ними - р-n-р и n-р-n дополнительные транзисторы, причем базы этих дополнительных транзисторов соединены с основным выходом дифференциального усилителя, эмиттер р-n-р дополнительного транзистора соединен с выходом первого токового зеркала, а его коллектор связан со входом четвертого токового зеркала, эмиттер n-р-n дополнительного транзистора соединен с выходом второго токового зеркала, а его коллектор подключен ко входу третьего токового зеркала.

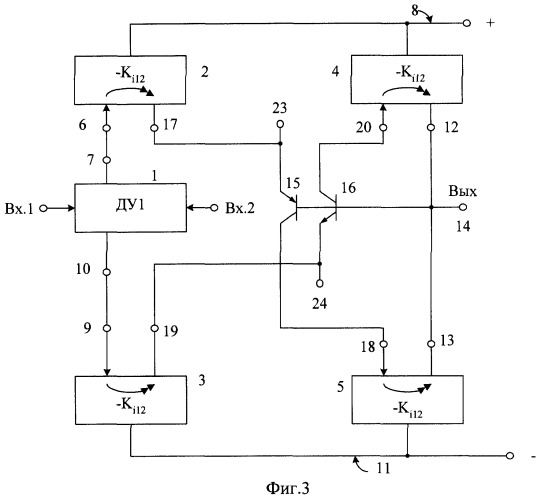

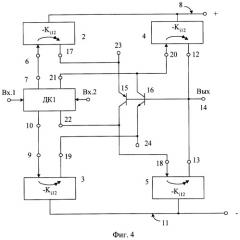

Схема заявляемого устройства показана на фиг.3. На фиг.4 показана схема ДУ в соответствии с п.2 формулы изобретения. На фиг.5-6 приведены варианты выполнения входного дифференциального каскада в соответствии с п.3 (фиг.5) и п.4 (фиг.6) формулы изобретения.

В соответствии с п.5 формулы изобретения на фиг.4 показаны вспомогательные выходы дифференциального усилителя (23, 24), к которым для для улучшения качественных показателей может подключаться вспомогательная нагрузка.

Частный случай выполнения ДУ фиг.1 по п.6 показан на фиг.7.

Варианты выполнения ДУ фиг.4 для случая, когда коэффициенты передачи со входа входного дифференциального каскада к первому и второму вспомогательным выходам значительно превышают коэффициенты передачи к выходам 7 и 10, приведены на фиг.8.

Фиг.9, на которой показаны переменные токи и напряжения, поясняет работу заявляемого устройства фиг.1.

На фиг.10 показана схема ДУ-прототипа, которая исследовалась авторами в среде PSpice на моделях интегральных транзисторах ФГУП «Пульсар» (г.Москва), а на фиг.11 - результаты расчета ее выходного сопротивления. Аналогично на фиг.12 показана схема заявляемого ДУ, а на фиг.13 - результаты ее компьютерного моделирования.

На фиг.14 приведена схема ДУ-прототипа в составе типового операционного усилителя, а на фиг.15 - схема ОУ на основе заявляемого ДУ. Результаты расчета АЧХ коэффициента усиления данных устройств при емкости коррекции Ск=10 пф, показаны на фиг.16.

Дифференциальный усилитель (фиг.3) содержит входной дифференциальный каскад 1, первое 2, второе 3, третье 4 и четвертое 5 токовые зеркала, причем вход 6 первого токового зеркала 2 соединен с основным выходом 7 входного дифференциального каскада 1, согласованным с шиной положительного источника питания 8, вход 9 второго токового зеркала 3 соединен с основным выходом 10 входного дифференциального каскада 1, согласованным с шиной отрицательного источника питания 11, а выходы 12 третьего (4) и 13 четвертого (5) токовых зеркал соединены друг с другом и основным выходом дифференциального усилителя 14. В схему в соответствии с п.1 формулы изобретения введены р-n-р (15) и n-р-n (16) дополнительные транзисторы, причем базы этих дополнительных транзисторов соединены с основным выходом 14 дифференциального усилителя, эмиттер р-n-р дополнительного транзистора 15 соединен с выходом 17 первого токового зеркала 2, а его коллектор связан со входом 18 четвертого токового зеркала 5, эмиттер n-р-n дополнительного транзистора 16 соединен с выходом 19 второго токового зеркала 3, а его коллектор подключен ко входу 20 третьего токового зеркала 4.

В соответствии с п.2 формулы изобретения в качестве входного дифференциального каскада 1, так же, как и в ДУ-прототипе (Японский патент), может использоваться (фиг.4) дифференциальный каскад, содержащий, кроме основного выхода 7, согласованного с шиной положительного источника питания 8, первый противофазный ему вспомогательный выход 21, согласованный с шиной положительного источника питания, а также второй вспомогательный выход 22, согласованный с шиной отрицательного источника питания, противофазный основному выходу входного дифференциального каскада, согласованному с шиной отрицательного источника питания, причем первый вспомогательный выход, согласованный с шиной положительного источника питания, соединен со входом третьего токового зеркала, а второй вспомогательный выход, согласованный с шиной отрицательного источника питания, подключен ко входу четвертого токового зеркала. В качестве вспомогательных выходов 23 и 24 используются эмиттеры транзисторов 15 и 16.

На фиг.7 выходы токовых зеркал 2 и 3 связаны друг с другом. Это переводит транзисторы 15 и 16 в режим отсечки (при малых сигналах и идентичных элементах схемы). В то же время при больших уровнях входного сигнала «открывается» либо транзистор 15, либо транзистор 16, что обеспечивает передачу сигнала на выход ДУ.

Схема фиг.8 соответствует схеме фиг.4. Однако в ней коэффициенты передачи по переменному току ко входам 21 и 22 выбраны значительно больше, чем ко входам 7 и 10.

На фиг.9 элементы у22.2, y22.3, y22.4, y22.5 представляют собой эквивалентные выходные проводимости токовых зеркал 2, 3, 4, 5.

Для расчета выходного сопротивления ДУ-прототипа фиг.10 и заявляемого ДУ на выход включен источник переменного напряжения Vin1, а выходное сопротивление определяется как отношение Vin1/iвых.

В операционных усилителях фиг.14 и фиг.15 в качестве буферного усилителя с коэффициентом передачи по напряжению, близким к единице, использовался типовой двухтактный выходной каскад на «бриллиантовых» транзисторах с верхней граничной частотой 800-900 МГц. Устойчивость ОУ обеспечивалась корректирующей емкостью Ск=10 пФ.

Работу заявляемого устройства рассмотрим на примере анализа фиг.9.

Для определения выходного сопротивления необходимо найти отношение

Если учесть, что сопротивление коллекторных переходов транзисторов 15 и 16 (Гк) значительно превышает выходное сопротивление токовых зеркал 2-4 (фиг.11), то из рассмотрения схемы фиг.9 можно найти составляющие токов, обусловленные конечными значениями выходных проводимостей токовых зеркал у22.2÷y22.5:

Токи i22.2 и i22.3 передаются транзисторами 15 и 16 и токовыми зеркалами 4 и 5 на выход ДУ 14. Поэтому суммарный выходной ток

где Ki12,5≈Ki12.4≈1 - коэффициенты передачи по току токовых зеркал 4 и 5;

α15≈α16≈1 - коэффициенты передачи по току эмиттера транзисторов 15 и 16 в схеме с общей базой.

В результате выходной ток ДУ можно представить в виде

где у22.35=у22.3=у22.5, у22.42=у22.4=у22.2 - средние значения соответствующих выходных проводимостей.

Так как в качестве токовых зеркал 5 и 3, 4 и 2 используются идентичные устройства, то их выходные проводимости при интегральном исполнении незначительно отличаются друг от друга, кроме этого коэффициенты α15Кi12.5≈1, α16Ki12.4≈1. Поэтому эквивалентная входная проводимость ДУ оказывается значительно меньше абсолютных значений у22.i. Как следствие, выходное сопротивление ДУ существенно повышается. Сравнение графиков фиг.11 и фиг.13 показывает, что этот параметр улучшается в 40-50 раз, что позволяет во столько же раз увеличить коэффициент усиления по напряжению ДУ (фиг.16).

В соответствии с п.2-п.7 формулы изобретения в устройствах фиг.7, фиг.8 создаются дополнительные условия, обеспечивающие дальнейшее повышение качественных показателей заявляемого ДУ в различных режимах его работы (более высокий выигрыш по Rвых(Ку), более высокая температурная стабильность статических параметров, большая независимость выигрыша по Квых в широком диапазоне изменения статических токов и питающих напряжений, более широкий частотный диапазон и т.д.).

1. Дифференциальный усилитель, содержащий входной дифференциальный каскад, первое, второе, третье и четвертое токовые зеркала, причем вход первого токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной положительного источника питания, вход второго токового зеркала соединен с основным выходом входного дифференциального каскада, согласованным с шиной отрицательного источника питания, а выходы третьего и четвертого токовых зеркал связаны с основным выходом дифференциального усилителя, отличающийся тем, что в схему введены р-n-р и n-р-n дополнительные транзисторы, причем базы этих дополнительных транзисторов соединены с основным выходом дифференциального усилителя, эмиттер р-n-р дополнительного транзистора соединен с выходом первого токового зеркала, а его коллектор связан со входом четвертого токового зеркала, эмиттер n-р-n дополнительного транзистора соединен с выходом второго токового зеркала, а его коллектор подключен ко входу третьего токового зеркала.

2. Устройство по п.1, отличающееся тем, что в качестве входного дифференциального каскада используется усилитель, содержащий кроме основного выхода, согласованного с шиной положительного источника питания, первый противофазный ему вспомогательный выход, согласованный с шиной положительного источника питания, а также второй вспомогательный выход, согласованный с шиной отрицательного источника питания, противофазный основному выходу входного дифференциального каскада, согласованному с шиной отрицательного источника питания, причем первый вспомогательный выход, согласованный с шиной положительного источника питания, соединен со входом третьего токового зеркала, а второй вспомогательный выход, согласованный с шиной отрицательного источника питания, подключен ко входу четвертого токового зеркала.

3. Устройство по п.1, отличающееся тем, что в качестве входного дифференциального каскада используется мостовой дифференциальный каскад на n-р-n и р-n-р транзисторах, имеющий основной и противофазный ему первый вспомогательный выход, согласованные с шиной положительного источника питания, а также основной и противофазный ему второй вспомогательный выходы, согласованные с шинами отрицательного источника питания.

4. Устройство по п.1, отличающееся тем, что в качестве входного дифференциального каскада используется два параллельно-балансных каскада на n-р-n и р-n-р транзисторах, эмиттеры которых объединены и подключены к шине положительного и отрицательного источников питания через соответствующие токостабилизирующие двухполюсники, причем коллекторы n-р-n транзисторов являются основным и первым вспомогательным выходами, согласованными с шиной положительного источника питания, а коллекторы р-n-р транзисторов являются соответственно основным и вспомогательным выходами, согласованными с шинами отрицательного источника питания.

5. Устройство по п.1, отличающееся тем, что эмиттеры дополнительных транзисторов являются вспомогательными выходами дифференциального усилителя, к которым подключается вспомогательная нагрузка.

6. Устройство по п.2, отличающееся тем, что выходы первого и второго токовых зеркал соединены друг с другом.

7. Устройство по п.2, отличающееся тем, что коэффициент передачи по переменному току со входа входного дифференциального каскада к основным выходам, согласованным с шинами положительного и отрицательного источников питания, выбираются значительно меньше, чем коэффициенты передачи по переменному току со входа входного дифференциального каскада к первому и второму вспомогательным выходам.