Схемное устройство и способ для формирования сигнала двойной шины

Иллюстрации

Показать всеИзобретение относится к схемному устройству и способу формирования выходного сигнала двойной шины с устройством (12) обработки сигнала с переключателями, управляемыми в зависимости от входного сигнала <а, aq>, а также с двумя выходами (х, xq), причем посредством одного из переключателей (s, sq) первый выход (х), а посредством другого переключателя (sq, s) второй выход (xq) могут соединяться с опорной точкой (v) управляющего устройства, находящейся на первом потенциале (0). Устройство обработки сигнала через переключающее устройство (13) соединено с выходами схемного устройства для выдачи выходного сигнала двойной шины <z, zq>. При этом выходы (E1, E2) переключающего устройства (13) в зависимости от управляющего сигнала (7), могут соединяться соответственно с одним или обоими входами (D1, D2). Также предусмотрено устройство контроля потенциала для установления потенциалов выходов (F1, F2) схемного устройства, когда они не связаны через переключающее устройство (13) и устройство (12) обработки сигнала с опорной точкой (v) устройства обработки сигнала. 2 с. и 4 з.п. ф-лы, 8 ил.

Реферат

Обычно переключательные схемы выполняются в микроэлектронике таким образом, что каждый бит подлежащей обработке информации физически представляется точно одним электрическим узлом (узловой точкой). Такое построение также называется "одношинной" схемотехникой. Однако такие переключательные схемы относительно ненадежны по отношению к так называемому дифференциальному анализу профиля тока, который применяется противоправными третьими лицами при попытке доступа к секретной информации. Дифференциальный анализ профиля тока (в англоязычной литературе называемый дифференциальным анализом мощности - DPA) является одним из важнейших методов атаки неправомерного доступа), например, на чип-карты в приложениях, связанных с защитой. При этом осуществляется целенаправленная атака на конфиденциальную информацию, такую как пароли или криптографические ключи. Для заданной программы или заданного алгоритма статистическими методами оцениваются измеренные профили тока чип-карты или интеграл ее заряда, вычисленный на одного или нескольких тактах, причем - для множества реализаций на основе программного обеспечения - из корреляции систематических изменений данных с соответствующим интегралом заряда можно сделать выводы относительно защищаемой информации.

В противоположность обычной одношинной схемотехнике, при которой каждый бит в тракте данных или сигнала физически представляется посредством точно одного электрического узла k, при реализации в варианте двухшинной схемотехники каждый бит представляется двумя узлами k и kq, причем этот бит имеет действительное логическое значение, если k соответствует истинному логическому значению b этого бита, а kq - значению с отрицанием bn=not (b).

Таким образом, если должно передаваться значение b=1, то это происходит посредством "1" в узле k. Однако одновременно также передается значение "0" в узле kq, так что в целом передается как "1", так и "0". Если должно передаваться значение b=0, то одновременно происходит передача значения "1" в узле kq. В обоих случаях, таким образом, передается "1" и "0". Исходя из физической равноправности узлов k и kq, посредством дифференциального анализа профиля тока теперь уже невозможно различить, передаются ли данные "1" или "0". Однако это справедливо только в том случае, если действительно при передаче данных происходит смена сигнала, то есть информация "1" сменяется информацией "0". Если последовательно друг за другом передаются множество одинаковых данных, то свойства защиты от атак на основе дифференциального анализа тока ухудшаются.

Желательная инвариантность интеграла заряда достигается тем, что между каждыми двумя состояниями с действительными логическими значениями (b,bn)=(1,0) или (0,1) добавляется так называемое состояние предзаряда, для которого как k, так и kq заряжаются до одного и того же электрического потенциала, таким образом, принимают логически недействительные значения (1,1) или (0,0). Для состояния предзаряда (1,1) последовательность состояний может выглядеть следующим образом:

(1,1)→(0,1)→(1,1)→(1,0)→(1,1)→(1,0)→(1,1)→(0,1)→...

Для любой такой последовательности символов справедливо, что для каждого перехода (1,1)→(b,bn) точно один узел перезаряжается с "1" на "0", а для всех (b,bn)→(1,1) точно один узел перезаряжается с "0" на "1", независимо от логического действительного значения b конкретного битового состояния. Аналогичное положение справедливо для последовательности состояний в случае состояния предзаряда (0,0).

Отсюда следует, что соответствующие этим последовательностям интегралы заряда независимы от последовательности (b,bn) логически действительных значений, если обеспечивается, что узлы k и kq имеют одинаковые электрические емкости. Профиль тока реализованного таким образом пути (тракта) данных не зависит от временных изменений подлежащих обработке данных и тем самым является устойчивым по отношению к дифференциальному анализу профиля тока.

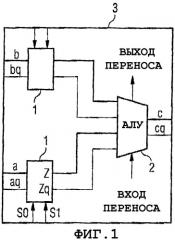

Схемные устройства для формирования сигнала двойной шины используются, например, в устройстве обработки данных, как показано на фиг.1, где представлено устройство 3 обработки данных, которое имеет вычислительный блок 2, часто называемый арифметико-логическим устройством (АЛУ). Такое АЛУ предназначается для того, чтобы связывать между собой два входных значения, например, таким образом, чтобы осуществлялось их сложение. Два входных значения а и b связываются, таким образом, в одно выходное значение с. Вычитание может осуществляться таким образом, что одно из обоих связываемых друг с другом значений подается на АЛУ инвертированным и одновременно устанавливается бит переноса на входе переноса АЛУ. Вместо сигнала а в примере, показанном на фиг.1, необходим сигнал not(а). Для этого устройство 3 обработки данных содержит входные схемы 1 предварительной обработки, которые обеспечивают реализацию функции not(а).

Входная схема 1 выдает выходной сигнал z, который поступает на АЛУ. В других случаях в качестве входного сигнала для АЛУ необходимо значение "0" или "1", поэтому входная схема 1 должна также иметь возможность реализации этих обоих значений. Таким образом, требуемые функции формирования выходного сигнала z входной схемы 1 имеют вид

z=f(a),

z=not(f(а)),

z=0 и

z=1

При этом функция f указывает, что может осуществляться дополнительная обработка входных данных а, например, когда данные а зашифрованы и сначала должны быть расшифрованы, чтобы стала возможной дальнейшая обработка в АЛУ. То, какая из этих четырех функций должна быть использована, определяется управляющими сигналами S0, S1, которые подаются на входную схему 1.

Наряду с сигнальными путями для сигналов a, b, z и с, обозначенными на фиг.1 жирными линиями, также показаны сигнальные пути для сигналов aq, bq, zq и cq, обозначенные тонкими линиями. Эти сигнальные пути или эти сигналы присутствуют тогда, когда речь идет об устройстве 3 обработки данных, которое пригодно для обработки сигналов двойной шины. Наряду с собственно сигналом данных всегда имеется еще дополнительный сигнал, если речь идет о действительных данных. В вышеназванном состоянии предзаряда на оба сигнальных проводника подаются одинаковые сигналы, то есть справедливы соотношения а=aq, b=bq, z=zq и c=cq.

Реализуемая входной схемой 1 функция, связанная с обоими битами управления S0 и S1, имеет вид

z=not(s1·not(f(a<n:1>)+s0·f(a<n:1>)).

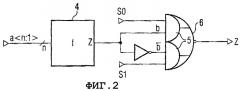

Согласно уровню техники такая функция реализуется схемным устройством, показанным на фиг.2. Слово данных а<n:1> длиной n битов подается на первый блок 4 схемы. Этот блок образует функцию f(a). Этот сигнал дополнительно инвертируется, так что для дальнейшей обработки в распоряжение предоставляются как f(а), так и not(f(a)). Функция f(a) связывается затем с битом управления S0 в логической схеме "И". Так же значение not(f(a)) связывается в логической схеме "И" с битом управления 31. В логической схеме "ИЛИ" оба выходных значения обеих логических схем "И" связываются в выходное значение z.

Таким образом, используется множество последовательно включенных обычных логических схем. Такое схемное устройство, воплощающее логическую систематику, оказывается относительно дорогостоящим в связи с числом применяемых транзисторов, в частности, когда вместо одношинного сигнала должен применяться двухшинный сигнал. Кроме того, время обработки в таких схемных устройствах, которые к тому же имеют высокое потребление тока, относительно велико.

Как следует из случая применения, проиллюстрированного на фиг.1, подобная схема не просто вводится в устройство обработки данных, а должна выполняться отдельно для каждого параллельно обрабатываемого бита. В случае процессора, работающего с 32-битовой шиной, эта схема, следовательно, должна быть повторена 2·32=64 раз.

Задачей изобретения является создание схемного устройства для формирования выходного сигнала двойной шины, которое является более простым по конструкции и может быть реализовано с меньшим числом транзисторов. Кроме того, задачей изобретения является создание соответствующего способа.

Указанная задача решается схемным устройством для формирования выходного сигнала двойной шины, содержащим первый вход, по меньшей мере, с двумя выводами для приема входного сигнала двойной шины, второй вход для приема управляющего сигнала, устройство обработки сигнала с первым и вторым переключателями, управляемыми соответственно в зависимости от входного сигнала, а также с двумя выходами, причем посредством одного из переключателей первый выход, а посредством другого переключателя второй выход могут соединяться с опорной точкой управляющего устройства, находящейся на первом потенциале, переключающее устройство, имеющее два входа, которые соединены с выходами устройства обработки сигнала, и два выхода, которые соединены с двумя выходами схемного устройства для выдачи выходного сигнала двойной шины, причем выходы, в зависимости от управляющего сигнала, могут соединяться соответственно с одним или обоими входами, и устройство контроля потенциала для установления потенциалов выходов схемного устройства, когда они не связаны через переключающее устройство и устройство обработки сигнала с опорной точкой устройства обработки сигнала.

Кроме того, поставленная задача решается способом согласно пункту 6 формулы изобретения.

Преимущество соответствующего изобретению схемного устройства состоит в том, что выходной сигнал может принимать не только значения f(a) и fq=not(f(а)), но и оба значения "0" и "1". При этом схема весьма проста по построению и содержит небольшое количество транзисторов. Наряду с транзисторами, которые в устройстве обработки сигнала обеспечивают реализацию функций f(a,aq) и fq(a,aq), необходимы только четыре транзистора для переключающего устройства, а также транзисторы для устройства контроля потенциала. В предпочтительном варианте осуществления устройство контроля потенциала может содержать всего два транзистора.

Особенно предпочтительным является то, что почти вся схема может быть реализована с использованием только одного типа транзисторов. Это положительно влияет на потребление тока схемы, так как для процессов перезаряда в этом случае потребляется меньше тока.

Особенно предпочтительным является вариант выполнения схемного устройства, когда обеспечена возможность следующих рабочих условий, причем Е1 и Е2 являются выходами, a D1 и D2 являются входами переключающего устройства

E1 связан с D1, a E2 связан с D2: z=not(f(а)),

E1 связан с D2, а E2 связан с D1: z=f(a),

E1 связан с D1 и D2, а E2 разомкнут: z=0,

E1 связан с D1 и D2, а Е1 разомкнут: z=1.

В этом случае схемное устройство обладает функциональными возможностями, которые необходимы для использования входной схемы, как в случае устройства обработки данных, показанного на фиг.1.

Кроме того, предпочтительно, если предусмотрено дополнительное устройство предзаряда, посредством которого перед каждыми передаваемыми данными на всех выводах выхода, через которые передаются данные, формируется одинаковый потенциал. Тем самым в особенности обеспечивается защита от дифференциального анализа профиля тока.

В возможном предпочтительном варианте осуществления устройство обработки сигнала реализует логическую функцию "исключающее ИЛИ".

Изобретение поясняется ниже более подробно на примере его осуществления. На чертежах показано:

Фиг.1 - устройство обработки данных, в котором может быть использовано схемное устройство согласно изобретению;

Фиг.2 - схемное устройство, соответствующее уровню техники;

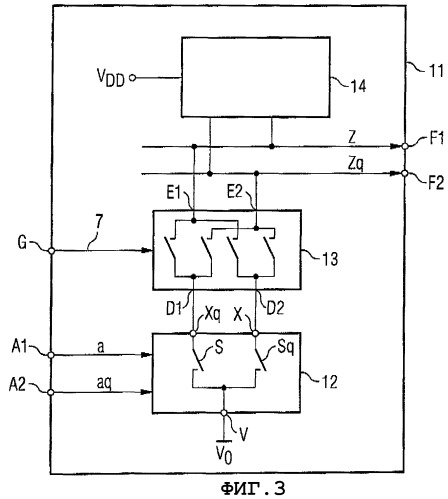

Фиг.3 - схематичное изображение устройства, соответствующего изобретению;

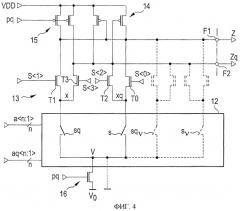

Фиг.4 - конкретная реализация схемного устройства по фиг.2;

Фиг.5 - временная диаграмма, иллюстрирующая сигналы схемного устройства по фиг.4;

Фиг.6 - первый пример выполнения устройства обработки сигнала;

Фиг.7 - второй пример выполнения устройства обработки сигнала;

Фиг.8 - пример выполнения соответствующего изобретению схемного устройства по фиг.3 с р-канальными транзисторами.

Фиг.1 изображает описанное выше устройство обработки данных, в котором может быть использовано схемное устройство согласно изобретению.

Фиг.2 иллюстрирует схемное устройство, соответствующее уровню техники, которое также было описано выше.

На Фиг.3 приведено схематичное изображение устройства, соответствующего изобретению. Схемное устройство 11 содержит вход А1 и А2, на который подается сигнал двойной шины. При этом на вход А1 поступает сигнал данных а, а на вход А2 дополнительный сигнал данных aq. Оба сигнала подаются на устройство 12 обработки сигнала. Устройство 12 обработки сигнала предназначено для схемотехнической реализации двух булевых функций переключения, причем является так называемым "двухшинным" представлением f

и

,

причем справедливы соотношения:

если aq〈j〉=not(а〈j〉)∀j, а также

sq=not(s), если aq〈j〉=not(а〈j〉)∀j.

При этом s=0 или sq=0 означает, что соответствующий переключатель разомкнут, и, отсутствует проводящее соединение между опорной точкой v устройства 12 обработки сигналов и выходами х и xq устройства 12 обработки сигналов. Напротив, s=1 или sq=1 означает, что опорная точка v связана проводящим образом с выходами х и xq.

Выходы х и xq устройства 12 обработки сигналов связаны с входами D1 и D2 переключающего устройства 13. Выходы Е1 и Е2 связаны с выходами F1 и F2 всего схемного устройства, так что там формируется выходной сигнал z и zq, который является сигналом двойной шины. При действительных данных zq является, таким образом, сигналом, дополнительным к сигналу z.

Кроме того, предусмотрен управляющий вход G, на который может подаваться управляющий сигнал 7, который передается далее на переключающее устройство 13. Управляющий сигнал 7 определяет, каким образом входы D1 и D2 соединяются с выходами Е1 и Е2 переключающего устройства 13.

Для пояснения способа работы устройства сначала предполагается, что устройство 14 контроля потенциала обеспечивает на обоих выходах F1 и F2 второй потенциал VDD. За счет замыкания соответствующих переключателей в устройстве 12 обработки сигнала и переключающем устройстве 13 каждый из выходов F1 и F2 может соединяться с опорной точкой v устройства обработки сигнала, которая в состоянии, представленном на фиг.3, находится под первым потенциалом V0.

Теперь следует исходить из того, что приложен действительный сигнал данных a, aq. Это обуславливает то, что либо соединение между х и v, либо соединение между xq и v замыкается, в то время как другое соединение разомкнуто. Это следует из того, что сигналы а и aq двойной шины при действительных данных являются дополнительными друг к другу, как описано выше. Это справедливо также для переключающих функций s и sq. За счет управляющего сигнала 7 может теперь быть обеспечено то, что входы D1 и D2 и выходы Е1 и Е2 переключающего устройства 13 могут любым образом соединяться друг с другом. Если вначале предположить, что посредством переключателя s опорная точка v устройства 12 обработки сигнала соединена с xq, и помимо этого D1 соединено с Е1, то F1 переводится на первый потенциал V0, так как выход F1 проводящим образом соединен с V. Поэтому выходной сигнал z равен "0".

Отсюда в соответствии с логикой систематики двойной шины, следует, что другой выход должен находиться под дополнительным уровнем напряжения, а именно под потенциалом VDD. Соответственно устройство 14 контроля потенциала в описанном примере соединяет выход F2 с вторым потенциалом VDD.

Если дополнительно D2 соединено с Е2, то сигнал z, zq зависит еще только от установки положений переключателей в устройстве 12 обработка сигнала. Тем самым реализуется функция z=not(f(a)).

Если должна быть реализована функция z=f(a), то это может бытъ обеспечено тем, что D1 соединяется с Е2, а D2 - с Е1.

Третья подлежащая реализации функция соответствует z=0. Это реализуется тем, что как Е1 соединяется как с D1, так и с D2, в то время как соединение с Е2 остается разомкнутым. Один из выходов х или xq устройства 12 обработки сигнала всегда соединен с опорной точкой v. За счет соединения Е1 как с D1, так и с D2, тем самым выход Е1 переключающего устройства 13 независимо от приложенных данных a, aq и полученных отсюда положений установки переключателей s, sq всегда связан с первым потенциалом 0 либо через переключатель s, либо через переключатель sq устройства 12 обработки сигнала.

Функция z=1 может быть реализована за счет того, что выход E1 переключающего устройствам 13 остается разомкнутым. Без дополнительного управления потенциал на выходе F1 остается на второй величине потенциала VDD. Чтобы выработать действительный сигнал двойной шины, выход F2 для выдачи сигнала zq должен быть переведен на первый потенциал 0. Для этого выход Е2 должен соединяться как с входом D1, так и с входом D2 переключающего устройства 13. Таким образом, описанным способом гарантируется, что выход F2 соединяется с опорной точкой v независимо от приложенных данных а, aq.

В простом варианте осуществления устройство контроля потенциала состоит из двух нагрузочных резисторов (резисторов установки рабочей точки), через которые выходы F1 и F2 соединены с вторым потенциалом VDD. Недостаток подобного решения состоит в том, что при соединении одного выхода с первым потенциалом V0 через резистор протекает поперечный (уравнительный) ток, который приводит к нежелательному потреблению тока. Этот нежелательный поперечный ток проявляется и тогда, когда применяется один транзистор, включенный в качестве сопротивления.

В предпочтительном варианте осуществления поэтому предусматриваются два транзистора, причем каждый транзистор соединяет один выход с вторым потенциалом VDD через свой промежуток сток-исток. Вывод затвора управляется соответственно от другого выхода. Если используются р-канальные транзисторы, то транзистор регулируется автоматически, как только потенциал на выходе, который соединен с затвором, становится равным 0. Таким путем можно предотвратить возникновение поперечных токов.

На фиг.4 представлен детальный пример выполнения соответствующего изобретению схемного устройства. Управляющий сигнал 7 образуется посредством четырех отдельных сигналов s<3>, s<2>, s<1> и s<0>. Дополнительно к описанной схеме транзисторов устройства 14 контроля потенциала показаны два транзистора 15 предзаряда. Они соединяют второй потенциал VDD с обоими выходами F1 и F2. Транзисторы 15 управляются посредством общего сигнала pq предзаряда. Если pq=0, то транзисторы переключаются и оба выхода F1 и F2 соединяются со вторым потенциалом VDD.

Это, однако, может привести к проблемам, если одновременно переключается переключающее устройство 13 и устройство 12 обработки сигнала устанавливает соединение с опорной точкой v, которая непосредственно связана с первым потенциалом 0. В этом случае между VDD и потенциалом 0 имеет место короткое замыкание. Чтобы воспрепятствовать этому, имеются две возможности. Одна возможность состоит в том, чтобы соединить опорную точку v через дополнительный транзистор 16 с потенциалом 0, причем этот транзистор 16 также управляется сигналом pq предзаряда. Одновременно с запиранием транзисторов 15 предзаряда отпирается транзистор 16 опорной точки, так что путь тока между VDD и первым потенциалом V0 прерывается, даже если переключающее устройство 13 и устройство 12 обработки сигнала переключены. Другая возможность состоит в том, чтобы управляющий сигнал 7 и сигнал предзаряда согласовать друг с другом таким образом, чтобы гарантировалось, что при запертых транзисторах 15 предзаряда переключающие транзисторы переключающего устройства 13 отпираются.

Помимо этого, естественно, существует возможность, что прикладываемые данные a, aq подаются таким образом, что справедливо соотношение s=sq=0, когда один из переключателей переключающего устройства 13 замкнут, и одновременно pq=0. Для пояснения на фиг.5 приведена диаграмма сигналов, из которой понятна временная последовательность сигналов в схеме по фиг.4. Например, там показан временной интервал Z1. В начале интервала Z1 pq=0, так что транзисторы 15 предзаряда на фиг.4 являются низкоомными. Однако одновременно транзисторы Т1 и Т2 в соответствии с управляющим сигналом s<3:0>=(0110) также являются низкоомными. Однако короткое замыкание между VDD и V0 предотвращается тем, что a=aq=0 и тем самым s=sq=0, до тех пор, пока pq вновь не станет равным 1 и транзисторы предзаряда не станут высокоомными. Две подходящие схемы представлены для примера на фиг.6 и 7 и ниже описаны более подробно.

Кроме того, на фиг.5 показаны остальные последовательности сигналов, которые уже были описаны с помощью схем на фиг.3 и 4, так что это представление может быть использовано для пояснения этих схем.

Переключающее устройство 13 на фиг.3 и 4 реализует желательное выходное состояние с четырьмя управляющими битами. Хотя необходимо выбрать только четыре различных рабочих состояния, так как предусмотрены четыре транзистора, предпочтительным является прибегнуть к использованию четырех управляющих битов. Альтернативно можно было бы осуществлять управление с помощью двух управляющих битов, которые посредством дополнительной схемы должны были раздваиваться для управления четырьмя транзисторами. Получается следующее распределение состояний:

| pq | S<3:0> | z | zq |

| 1 | 0011 | 0 | 1 |

| 1 | 1100 | 1 | 0 |

| 1 | 0110 | f | not(f) |

| 1 | 1001 | not(f) | f |

He считая состояние предзаряда, здесь могут предполагаться четыре вышеназванных значения s. Это может быть обеспечено схемой, находящейся вне описываемого пути передачи данных.

Устройство 12 обработки сигнала может реализовывать любую функцию. Простейший случай соответствует следующему: f(a)=a и fq(a)=aq. В зависимости от того, являются ли принимаемые данные зашифрованными или нет, или должны ли применяться какие-либо иные функции, в устройстве 12 обработки сигнала может быть использована любая такая схема. Два примера показаны на фиг.6 и 7. Схема на фиг.6 представляет мультиплексор, а схема на фиг.7 реализует логическую схему "исключающее ИЛИ". Другие схемы также очевидны для специалиста, и информация о них может быть получена из специальной литературы.

Посредством схемы на фиг.6 реализуется функция

с помощью функций

и

Посредством схемы на фиг.7 реализуется функция

f(a〈2:1〉)=а(1)⊕а(2)

с помощью функций

и

На фиг.8 показан вариант схемного устройства по фиг.4. В то время как схема по фиг.4 по существу построена на n-канальных транзисторах, вариант схемного устройства по фиг.8 выполнен главным образом на р-канальных транзисторах. В остальном построение схемы по фиг.8 симметрично представленному на фиг.4. Следует, однако, отметить, что для транзисторов 25 предзаряда применяются n-канальные транзисторы, которые управляются сигналом р предзаряда вместо сигнала pq. Предусматриваемый в соответствии с управлением транзистор 16 опорной точки также должен управляться сигналом р предзаряда.

Перечень ссылочных позиций

a, aq входной сигнал данных

z, zq выходной сигнал данных

s, sq переключатель (функция)

р, pq сигнал предзаряда

A1, A2 вход схемного устройства

F1, F2 выход схемного устройства

D1, D2 вход переключающего устройства

E1, E2 выход переключающего устройства

х, xq выход устройства обработки данных

G управляющий вход

V0 первый потенциал

VDD второй потенциал

1 входная схема

2 вычислительный блок

3 устройство обработки данных

4 переключающий блок

5 логическая схема "И"

6 логическая схема "ИЛИ"

7 управляющий сигнал

11 схемное устройство

12 устройство обработки сигнала

13 переключающее устройство

14 устройство контроля потенциала

15 транзисторы предзаряда

16 транзистор опорной точки

1. Схемное устройство для формирования выходного сигнала (z, zq) двойной шины, содержащее первый вход, по меньшей мере, с двумя выводами (A1, A2) для приема входного сигнала (a, aq) двойной шины, второй вход (G) для приема сигнала (7) управления, устройство (12) обработки сигнала с первым (s) и вторым (sq) переключателями, управляемыми соответственно в зависимости от входного сигнала (а, aq), а также с двумя выходами (х, xq), причем посредством одного из переключателей (s, sq) первый выход (х), а посредством другого переключателя (sq, s) второй выход (xq) могут соединяться с опорной точкой (v) управляющего устройства, находящейся на первом потенциале (0), переключающее устройство (13), имеющее два входа (D1, D2), которые соединены с выходами (х, xq) устройства обработки сигнала, и два выхода (E1, E2), которые соединены с двумя выходами (F1, F2) схемного устройства для выдачи выходного сигнала (z, zq) двойной шины, причем выходы (E1, E2), в зависимости от управляющего сигнала (7), могут соединяться соответственно с одним или обоими входами (D1, D2), и устройство контроля потенциала (14), которое устанавливает второй потенциал (VDD) на выходах (F1, F2) схемного устройства, когда они не связаны через переключающее устройство (13) и устройство (12) обработки сигнала с опорной точкой (v) устройства обработки сигнала.

2. Схемное устройство по п.1, отличающееся тем, что переключающее устройство выполнено с возможностью обеспечения следующих рабочих условий:

Е1 связан с D1, а Е2 связан с D2: z=not(f(a)),

E1 связан с D2, а Е2 связан с D1: z=f(a),

E1 связан с D1 и D2, а Е2 разомкнут: z=0,

Е2 связан с D1 и D2, а Е1 разомкнут: z=1.

3. Схемное устройство по п.1 или 2, отличающееся тем, что предусмотрено устройство (15) предзаряда, управляемое сигналом (pq, p) предзаряда, посредством которого перед каждыми передаваемыми данными на всех выводах (F1, F2) выхода, через которые передаются данные, формируется предварительно определенный одинаковый потенциал.

4. Схемное устройство по п.3, отличающееся тем, что последовательно с устройством (12) обработки сигнала и переключающим устройством (13) включен переключатель, управляемый сигналом (pq, p) предзаряда, для предотвращения непосредственного соединения между первым потенциалом (V0) и вторым потенциалом (VDD) через переключатели устройства (12) обработки сигнала и переключающего устройства (13).

5. Схемное устройство по любому из пп.1, 2 или 4, отличающееся тем, что указанные переключатели (s, sq) в устройстве (12) обработки сигнала реализуют переключательную схему, посредством которой осуществляется логическая функция "Исключающее ИЛИ".

6. Способ формирования выходного сигнала z, zq двойной шины в двух образующих одну пару проводниках данных, включающий в себя этапы обеспечения первого переключателя (s), управляемого сигналом и второго переключателя (sq), управляемого сигналом где а, aq являются входным сигналом данных двойной шины, причем при действительном сигнале данных aq=not(a) справедливо соотношение , соединения проводников данных с переключателями (s, sq) в следующих комбинациях: первый проводник данных с первым переключателем (s), а второй проводник данных с вторым переключателем (sq), или первый проводник данных с вторым переключателем (sq), а второй проводник данных с первым переключателем (s), или первый проводник данных с первым и вторым переключателем (s, sq), а второй проводник данных ни с первым переключателем (s), ни со вторым переключателем (sq), или второй проводник данных с первым переключателем (s) и со вторым переключателем (sq), а первый проводник данных ни с первым переключателем (s), ни со вторым переключателем (sq), причем при замкнутом переключателе (s, sq) связанный с ним проводник данных приводится на первый потенциал, а с другим проводником данных может быть соотнесен второй потенциал.