Способ передачи и приема сигналов квадратурной амплитудной модуляции, система для его осуществления, машиночитаемый носитель и применение способа для синхронизации приема сигналов квадратурной амплитудной модуляции

Иллюстрации

Показать всеИзобретение относится к технике передачи сигналов. Технический результат - снижение порога демодуляции. Использование данного способа в системах передачи и приема сигналов квадратурной амплитудной модуляции (КАМ) с низким порогом синхронизации по несущей частоте позволяет снизить порог демодуляции за счет обеспечения низкого порога синхронизации по несущей частоте. Этот результат достигается дополнением пачки из М m-уровневых символов КАМ заранее заданными символами, часть которых не изменяется от пачки к пачке, а другая часть периодически инвертируется в некоторых из пачек. Благодаря этому на приемной стороне выделяются составляющие сигнала КАМ, соответствующие дополнительным заранее заданным символам (частоты которых известны). По этим составляющим определяется частота инвертирования, что и обеспечивает устранение неоднозначности в подстройке частоты синхронизации приема. Это дает возможность вплотную приблизиться к порогу Шеннона. 4 н. и 16 з.п. ф-лы, 1 табл., 8 ил.

Реферат

Область техники, к которой относится изобретение

Данное изобретение относится к технике передачи сигналов. Конкретно данное изобретение относится к способу и системе для передачи и приема сигналов квадратурной амплитудной модуляции с низким порогом синхронизации по несущей частоте.

Уровень техники

При передаче и приеме сигналов, модулированных тем или иным образом, очень важной характеристикой является порог демодуляции, т.е. то отношение мощности сигнала к мощности шума (С/Ш), при котором перестает выделяться несущее колебание принимаемого сигнала, что ведет к срыву приема. Порог демодуляции существенно зависит от вида модуляции, примененного на передающей стороне, и вида помехоустойчивого кодирования.

Из теории известно, что эффективность любой системы связи определяется ее частотным и энергетическим ресурсом, т.е. полосой частот, занимаемой сигналом, и его мощностью для обеспечения требуемых скоростей передачи и приема информации. В общем случае эта зависимость скорости передачи и приема информации от ширины спектра частот и энергетики сигнала определяется формулой Шеннона:

где С - скорость передачи и приема информации, В - ширина спектра частот передаваемого сигнала в канале связи, РС - мощность сигнала на входе приемника, РШ - мощность шумов, приведенных к входу приемника, в полосе В частот.

Современные системы связи представляют собой модемные технологии, построенные под конкретные скорости передачи информации. Наиболее часто используются следующие виды модуляции:

- в спутниковой связи: QPSK, 8PSK, 16QAM, 32QAM;

- в радиорелейных линиях связи: BPSK, QPSK, 8PSK, 16QAM, 32QAM, 64QAM, 128QAM, 256QAM;

- в кабельных линиях связи: QPSK, 16QAM, 64QAM, 256QAM;

- в телефонии: от 16QAM до 16384QAM.

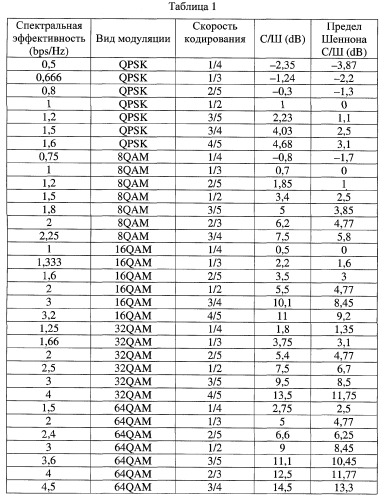

Наиболее часто используемыми видами помехоустойчивого кодирования, применяемыми в современных модемах, являются кодирование Витерби (сверточное), кодирование кодами Рида-Соломона, решетчатое кодирование (ТСМ - Trellis Code Modulation), турбокодирование [1] и LDPC (Low Density Parity Check Codes - коды с проверкой на четность низкой плотности) [3, 4]. Последнее является наиболее эффективным видом помехоустойчивого кодирования, позволяющим с потерями всего лишь в 0,8-1,5 дБ достигать предельных скоростей передачи информации, определенных формулой (1). В Таблице 1 приведены характеристики кодирования LDPC для различных скоростей кодирования и видов модуляции.

Препятствием для реализации достигнутых характеристик кодирования LDPC в современных системах связи являются слишком высокие пороги демодуляции (пороги восстановления несущей) в существующих демодуляторах. Так для демодуляции вида QPSK существующие демодуляторы начинают синхронизироваться по несущей частоте при соотношении С/Ш в 0 дБ, а для модуляции вида 16КАМ (16QAM) - при соотношении С/Ш около +8,9 дБ, для модуляции 32КАМ (32QAM) - при +12,7 дБ [2].

Из Таблицы 1 видно, что для реализации полной возможности кодирования LDPC сигнала QPSK при скорости кодирования 1/4 демодулятор должен работать при соотношении

тогда как он срывается уже при 0 дБ. Для сигнала 16QAM при той же скорости кодирования 1/4 демодулятор должен работать устойчиво при соотношении

а он срывается уже при +8,9 дБ и т.д.

Основной причиной этого является тот факт, что система восстановления несущей частоты в современных демодуляторах QPSK (4ФМ) и QAM (КАМ) является нелинейной. В спектрах сигналов, использующих такие виды модуляции, как QPSK (4ФМ), 8PSK (8ФМ), 16QAM (16КАМ) и т.п., не содержится остатка несущей частоты, поэтому когерентное ей колебание выделяют из принимаемого сигнала посредством некоторого нелинейного преобразования и последующей фильтрации. Но любая нелинейность ограничивает порог восстановления несущей. Если бы система выделения несущей была линейной, то порог демодуляции был бы меньше -3 дБ, что позволило бы демодулятору сохранять свои характеристики вплоть до соотношения

Итак, известные в настоящее время системы помехоустойчивого кодирования, к примеру кодирование LDPC и турбокодирование, позволяют довольно близко подойти к порогу Шеннона. Однако его достижение сдерживается отсутствием демодуляторов, способных работать при таких низких отношениях С/Ш из-за отсутствия синхронизации, что требует выделения несущего колебания из сигналов, использующих такие виды модуляции, как 4ФМ, 8ФМ, 16КАМ и т.п., с помощью нелинейного преобразования с последующей фильтрацией. Таким преобразованием является метод умножения частоты, который можно реализовать возведением в М-ю степень входного сигнала (в четвертую - для 4ФМ, восьмую - для 8ФМ и т.д.). Но при этом в ту же степень возводится и шум, который и ограничивает возможности восстановления несущей. Кроме того, возникает еще и фазовая неоднозначность, устранение которой требует введения в передаваемый сигнал относительного кодирования, вносящего дополнительные энергетические потери.

Сложности, связанные с использованием модуляции типа 2ФМ, 4ФМ и 8ФМ, наглядно демонстрируют патент США №6697440 (24.02.2004) и выложенная заявка Японии №2000-032072 (28.01.2000).

Как уже отмечено, в современных системах связи среди прочих методов модуляции используется и квадратурная амплитудная модуляция (КАМ или QAM).

Так, в выложенной заявке Японии №2001-237908 (31.08.2001) описана система выделения синхросигнала из сигнала КАМ, обеспечивающая квазисинхронное детектирование. В патентах США №№6717462 (06.04.2004) и 6727772 (27.04.2204) описаны способы и системы передачи и приема сигналов КАМ с подстройкой несущей частоты. Однако оба этих патента обеспечивают лишь простую обработку обычного сигнала КАМ. Недостатком этих аналогов является невозможность снизить порог демодуляции для приближения к порогу Шеннона.

Сущность изобретения

Задачей настоящего изобретения является создание таких способа и системы для передачи и приема сигналов КАМ, которые позволили бы снизить порог демодуляции за счет обеспечения низкого порога синхронизации по несущей частоте.

Для достижения такого результата предлагается способ и реализующая его система для передачи и приема сигналов КАМ по настоящему изобретению. Основным принципом этого изобретения является дополнение пачки из М m-уровневых символов КАМ заранее заданными символами, часть которых не изменяется от пачки к пачке, а другая часть периодически инвертируется в некоторых из пачек. Благодаря этому на приемной стороне выделяются составляющие сигнала КАМ, соответствующие дополнительным заранее заданным символам (частоты которых известны). По этим составляющим определяется частота инвертирования, что и обеспечивает устранение неоднозначности в подстройке частоты синхронизации приема. Это и дает возможность вплотную приблизиться к порогу Шеннона.

Подробно объекты и признаки настоящего изобретения указаны в прилагаемой формуле изобретения. Для лучшего понимания заявленной группы изобретений служит подробное описание.

Краткое описание чертежей

Нижеследующее подробное описание иллюстрируется прилагаемыми чертежами, на которых одинаковые или сходные элементы имеют одни и те ссылочные позиции.

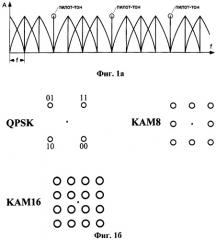

Фиг.1 представляет условную диаграмму, иллюстрирующую возможный сигнал, используемый в системе по настоящему изобретению.

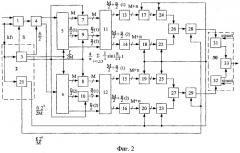

Фиг.2 является блок-схемой передающей стороны системы для передачи и приема сигналов КАМ по настоящему изобретению.

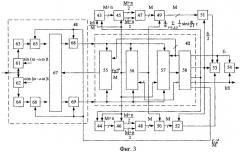

Фиг.3 является блок-схемой приемной стороны системы для передачи и приема сигналов КАМ по настоящему изобретению.

Фиг.4 иллюстрирует выполнение цифрового квадратурного демодулятора в блоке квадратурного преобразования приемной стороны системы по настоящему изобретению.

Фиг.5-7 иллюстрируют выполнение, соответственно, первого-третьего блоков фазовой автоподстройки частоты в выделителе тактовых частот приемной стороны системы по настоящему изобретению.

Фиг.8 иллюстрирует выполнение блока формирования частотных компонентов в выделителе тактовых частот приемной стороны системы по настоящему изобретению.

Подробное описание изобретения

Вид сигнала, используемого в системе передачи и приема сигналов КАМ по настоящему изобретению, показан на фиг.1. Спектр этого сигнала в канале I представляет собой набор частотных составляющих, разнесенных на заранее заданное значение частоты, чередующихся с пилотными сигналами (фиг.1а). С учетом сигнала в канале Q возможные сигнальные созвездия для разных видов модуляции имеют вид, показанный на фиг.1б.

Система передачи и приема сигналов КАМ по настоящему изобретению в общем случае состоит из передающей стороны и приемной стороны, соединенных каналом связи.

На фиг.2 представлена блок-схема передающей стороны системы передачи и приема сигналов КАМ по настоящему изобретению.

Передающая сторона содержит формирователь 1 m-уровневых символов, предназначенный для преобразования исходной информационной последовательности битовых символов, следующих с частотой kf1, в последовательность m-уровневых символов, где m=2k, k=2, 3, ..., следующих с первой тактовой частотой f1. Эта первая тактовая частота вырабатывается в формирователе 2 тактовых частот передающей стороны на первом выходе входящего в него блока 3 деления частоты из поступающего на его вход сигнала тактовой частоты kf1, которой сопровождается исходная последовательность битовых символов.

Разделитель 4 каналов предназначен для разделения информационной последовательности m-уровневых символов с формирователя 1 на канал I передающей стороны с четными m-уровневыми символами и канал Q передающей стороны с нечетными m-уровневыми символами. Частота следования m-уровневых символов в каждом из каналов I и Q передающей стороны, равная f1/2, формируется на втором выходе блока 3 деления частоты.

Первый и второй формирователи 5 и 6 пачек предназначены каждый для запоминания пачек из М m-уровневых символов на интервале

где 2L-1<M<2L, L=5, 6, 7, ..., в соответствующем из каналов I и Q передающей стороны и для дополнения каждой пачки из М m-уровневых символов n заранее заданными символами до общего числа М+n=2L. На формирователи 5, 6 подается сигнал с частотой 1/Гс третьего выхода блока 3 деления частоты.

В каждом из каналов I и Q передающей стороны имеется по два перемножителя. Первый и второй перемножители 7 и 8 предназначены каждый для инвертирования значений m-уровневых символов в нечетных парах пачек в каналах I и Q передающей стороны соответственно. Третий и четвертый перемножители 9 и 10 предназначены каждый для инвертирования значений половины добавленных в каждую нечетную пару пачек заранее заданных символов в каналах I и Q передающей стороны соответственно. Сигнал, обеспечивающий такое инвертирование и подающийся с четвертого выхода блока 3 деления частоты, имеет вид

т.е. представляет собой меандр со значениями +1 и -1 и с частотой 1/4T.

Третий и четвертый формирователи 11 и 12 пачек предназначены каждый для разделения каждой пачки из М+n символов пополам в соответствующем из каналов I и Q передающей стороны.

Первый-четвертый блоки 13-16 обратного преобразования Фурье (ОПФ) предназначены для замены каждой пачки из символов набором из М+n временных отсчетов с помощью ОПФ.

Первый-четвертый параллельно-последовательные преобразователи 17-20 предназначены для преобразования в каждом из каналов I и Q передающей стороны каждого из наборов из М+n временных отсчетов, полученных из блоков 13-16 ОПФ, соответственно, в соответствующую последовательность из М+n временных отсчетов со второй тактовой частотой

Сигнал этой частоты получается в формирователе 2 тактовых частот с первого выхода блока 21 умножения частоты, на вход которого подается тактовая частота kf1 исходной последовательности битовых символов.

Первый и второй блоки 22, 23 преобразования Гильберта предназначены каждый для поворота по фазе на π/2 всех частот спектра соответствующей последовательности из М+n временных отсчетов в канале I или Q передающей стороны соответственно. Первый и второй блоки 24, 25 задержки предназначены каждый для задержки другой из последовательностей из М+n временных отсчетов в соответствующем канале I или Q передающей стороны на время обработки в соответствующем блоке 22, 23 преобразования Гильберта.

Первый и второй поотсчетные сумматоры 26 и 27 предназначены каждый для объединения в соответствующем из каналов I и Q передающей стороны обеих полученных последовательностей из М+n временных отсчетов из одноименного блока 22, 23 преобразования Гильберта и одноименного блока 24, 25 задержки в одну последовательность той же длины.

Первый и второй блоки 28 и 29 фильтрации предназначены каждый для фильтрации объединенной последовательности с одноименных поотсчетных сумматоров 26 и 27 соответственно. Эта фильтрация осуществляется со второй тактовой частотой f2 с блока 21 умножения частоты в диапазоне от 0 до f2/2 в соответствующем из каналов I и Q передающей стороны.

Формирователь 30 сигнала на передачу предназначен для формирования сигнала на передачу из отфильтрованных последовательностей из блоков 28, 29 в каналах I и Q передающей стороны. В формирователе 30 в первом и втором перемножителях 31, 32 осуществляется перемножение отфильтрованных последовательностей с косинусным и синусным сигналами несущей частоты и сложение результатов этого перемножения в блоке 33 сложения. Сигнал с выхода блока 33 сложения в формирователе 30 подается в канал связи (не показано).

На фиг.3 представлена блок-схема приемной стороны системы передачи и приема сигналов КАМ по настоящему изобретению.

Приемная сторона, вход которой подключен к каналу связи, содержит обычные для любого приемника средства усиления, фильтрации и преобразования на промежуточную частоту, которые не показаны на фиг.3, но предполагаются в наличии. Далее, приемная сторона содержит блок 41 квадратурного преобразования, предназначенный для разделения принимаемого сигнала на последовательности цифровых отсчетов канала I приемной стороны и канала Q приемной стороны. В состав приемной стороны входит выделитель 42 тактовых частот, предназначенный для выделения тактовых частот с помощью сигналов в каналах I и Q приемной стороны. Выполнение выделителя 42 тактовых частот будет дано ниже.

Первый и второй буферные блоки 43 и 44 предназначены каждый для разделения последовательности цифровых отсчетов в соответствующем из каналов I и Q приемной стороны на пачки по М+n отсчетов и для запоминания этих пачек.

Первый и второй блоки 45 и 46 прямого преобразования Фурье (ППФ) предназначены каждый для осуществления в соответствующем из каналов I и Q приемной стороны ППФ над пачками по М+n отсчетов и для получения пар по m-уровневых отсчетов.

Первый и второй выделители 47 и 48 отсчетов предназначены каждый для выделения М m-уровневых отсчетов из каждой пары m-уровневых отсчетов в соответствующем из каналов I и Q приемной стороны. Эти М отсчетов соответствуют тем отсчетам, которые поступали на вход передающей стороны.

Первый и второй блоки 49 и 50 устранения фазовой неоднозначности предназначены каждый для устранения фазовой неоднозначности в сигнале соответствующего канала из каналов I и Q приемной стороны. Первый и второй преобразователи 51 и 52 в m-уровневую последовательность предназначены каждый для формирования последовательности m-уровневых отсчетов в соответствующем канале из каналов I и Q приемной стороны из сигналов с выхода одноименного блока 49 и 50 устранения фазовой неоднозначности. Блок 53 объединения последовательностей предназначен для объединения последовательностей m-уровневых отсчетов из одноименных преобразователей 51 и 52 каналов I и Q приемной стороны в одну последовательность m-уровневых отсчетов, следующих с первой тактовой частотой f1.

Преобразователь 54 в двоичную последовательность предназначен для преобразования объединенной последовательности m-уровневых отсчетов из блока 53 объединения последовательностей в информационную последовательность битовых символов с тактовой частотой kf1.

Выделитель 42 тактовых частот содержит (фиг.3) первый-третий блоки 55-57 фазовой автоподстройки частоты (ФАПЧ), первые и вторые входы которых предназначены для приема сигналов соответственно канала I и канала Q приемной стороны, выход первого блока 55 ФАПЧ предназначен для выдачи сигнала подстройки промежуточной частоты, подаваемого в блок 41 квадратурного преобразования. Первый и второй выходы второго блока 56 ФАПЧ предназначены, соответственно, для выдачи сигнала частоты подаваемого в первый и третий блоки 55, 57 ФАПЧ, в первый и второй буферные блоки 43, 44 и в первый и второй блоки 45, 46 ППФ, и меандрового сигнала интервальной частоты, подаваемого в первый и второй блоки 49 и 50 устранения фазовой неоднозначности. Выход третьего блока 57 ФАПЧ предназначен для выдачи сигнала подстройки тактовой частоты в блок 58 формирования частотных компонентов, выходы первой группы выходов которого подключены к соответствующим входам группы входов первого и третьего блоков 55-57 ФАПЧ, а выходы второй группы выходов подключены к соответствующим входам группы входов второго блока 56 ФАПЧ. Первый выход блока 58 формирования частотных компонентов предназначен для выдачи сигналов с частотой на блок 41 квадратурного преобразования, второй выход блока 58 формирования частотных компонентов предназначен для выдачи сигналов с второй тактовой частотой на первый и второй буферные блоки 43, 44, третий выход блока 58 формирования частотных компонентов предназначен для выдачи сигналов с частотой kf1 на преобразователь 54 в двоичную последовательность, четвертый выход блока 58 формирования частотных компонентов предназначен для выдачи сигналов с первой тактовой частотой f1 на блок 53 объединения последовательностей и преобразователь 54 в двоичную последовательность, пятый выход блока 58 формирования частотных компонентов предназначен для выдачи сигналов с частотой f1/2 на первый и второй преобразователи 51 и 52 в m-уровневую последовательность и на блок 53 объединения последовательностей.

Блок 41 квадратурного преобразования на приемной стороне содержит (фиг.3): седьмой и восьмой перемножители 61 и 62, предназначенные каждый для перемножения входного сигнала с соответствующей квадратурной составляющей частоты , где является частотой приблизительной расстройки от промежуточной частоты ; первый и второй фильтры 63 и 64, предназначенные каждый для выделения соответственно синусной и косинусной компонент принимаемого сигнала; первый и второй аналого-цифровые преобразователи (АЦП) 65 и 66, предназначенные каждый для преобразования соответствующей компоненты принимаемого сигнала в цифровые отсчеты с частотой ; цифровой квадратурный демодулятор 67, предназначенный для демодуляции сигналов синфазного и квадратурного каналов с помощью сигнала подстройки промежуточной частоты из первого блока 55 ФАПЧ в выделителе 42 тактовых частот; первый и второй оптимальные цифровые фильтры 68 и 69, предназначенные для оптимальной цифровой фильтрации с частотой демодулированных сигналов соответственно синфазного и квадратурного каналов. Выходы первого и второго цифровых фильтров 68 и 69 являются, соответственно, выходами канала I и канала Q приемной стороны.

Входящий в блок 41 квадратурного преобразования на приемной стороне цифровой квадратурный демодулятор 67 содержит (фиг.4): девятый и десятый перемножители 71 и 72, предназначенные каждый для перемножения синусной компоненты входного сигнала с соответствующей квадратурной составляющей частоты ; одиннадцатый и двенадцатый перемножители 74 и 74, предназначенные каждый для перемножения косинусной компоненты входного сигнала с соответствующей квадратурной составляющей частоты ; первый управляемый синтезатор 75 частоты, формирующий из сигнала подстройки промежуточной частоты (с выхода первого блока 55 ФАПЧ) синусную составляющую сигнала частоты для подачи на девятый и одиннадцатый перемножители 71, 73 и косинусную составляющую сигнала частоты для подачи на десятый и двенадцатый перемножители 72 и 74; первый вычитатель 76, предназначенный для нахождения разности сигналов десятого и одиннадцатого перемножителей 72, 73; первый сумматор 77, предназначенный для суммирования сигналов девятого и двенадцатого перемножителей 71, 74. Выходы первого вычитателя 76 и первого сумматора 77 являются, соответственно, выходами канала I и канала Q блока 41 квадратурного преобразования.

На фиг.5-7 показаны возможные выполнения соответственно первого - третьего блоков фазовой автоподстройки частоты (ФАПЧ), входящих в состав выделителя 42 тактовых частот приемной стороны.

Первый блок 55 ФАПЧ содержит (фиг. 5): второй вычитатель 101, предназначенный для нахождения разности сигналов синфазного и квадратурного каналов с соответствующих выходов блока 41 квадратурного преобразования; первую группу перемножителей 102-104, предназначенных для перемножения разностного сигнала с второго вычитателя 101 с соответствующими косинусными составляющими cos Ω1t, cos Ω2t, ...cos Ωn/2t, описанными далее; второй сумматор 105, предназначенный для суммирования результатов перемножения с выходов перемножителей 102-104; первый фильтр 106 нижних частот (ФНЧ), предназначенный для выделения низкочастотных составляющих суммарного сигнала с второго сумматора 105; тринадцатый перемножитель 107, предназначенный для перемножения отфильтрованного в ФНЧ 106 сигнала с сигналом частоты ; первый петлевой фильтр 108, предназначенный для фильтрации сигнала с выхода тринадцатого перемножителя 107 и выделения сигнала подстройки промежуточной частоты. (Название "петлевой" подчеркивает тот факт, что этот фильтр установлен в петле ФАПЧ). Выход первого петлевого фильтра 108 является выходом первого блока 55 ФАПЧ.

Второй блок 56 ФАПЧ содержит (фиг.6): третий сумматор 111, предназначенный для нахождения суммы сигналов синфазного и квадратурного каналов с соответствующих выходов блока 41 квадратурного преобразования; вторую группу перемножителей 112-114, предназначенных для перемножения суммарного сигнала с третьего сумматора 111 с соответствующими синусными составляющими sin Ω1t, sin Ω2t, ...sin Ωn/2t, описанными далее; четвертый сумматор 115, предназначенный для суммирования результатов перемножения с выходов перемножителей 112-114 второй группы; второй ФНЧ 116, предназначенный для выделения низкочастотных составляющих суммарного сигнала с четвертого сумматора 115; четырнадцатый перемножитель 117, предназначенный для перемножения отфильтрованного во втором ФНЧ 116 сигнала с сигналом, описанным далее; второй петлевой фильтр 118, предназначенный для фильтрации сигнала с выхода четырнадцатого перемножителя 117; второй управляемый синтезатор 119 частот, предназначенный для формирования на своем первом выходе сигнала на четырнадцатый перемножитель 117, а на своем втором выходе - меандрового сигнала вида

первый формирователь 120 частоты, предназначенный для формирования сигнала частоты из упомянутого меандрового сигнала с второго выхода второго управляемого синтезатора 119 частот. Выход первого формирователя 120 частоты и второй выход второго управляемого синтезатора 119 частот являются, соответственно, первым и вторым выходами второго блока 56 ФАПЧ.

Третий блок 57 ФАПЧ содержит (фиг. 7): пятый сумматор 121, предназначенный для нахождения суммы сигналов синфазного и квадратурного каналов с соответствующих выходов блока 41 квадратурного преобразования; третью группу перемножителей 122-124, предназначенных для перемножения суммарного сигнала с пятого сумматора 121 с соответствующими косинусными составляющими cos Ω1t, cos Ω2t, ...cos Ωn/2t, описанными далее; шестой сумматор 125, предназначенный для суммирования результатов перемножения с выходов перемножителей 122-124 третьей группы; третий ФНЧ 126, предназначенный для выделения низкочастотных составляющих суммарного сигнала с шестого сумматора 125; пятнадцатый перемножитель 127, предназначенный для перемножения отфильтрованного в третьем ФНЧ 126 сигнала с сигналом частоты ; третий петлевой фильтр 128, предназначенный для фильтрации сигнала с выхода пятнадцатого перемножителя 127 и выделения сигнала подстройки тактовой частоты. Выход третьего петлевого фильтра 128 является выходом третьего блока 56 ФАПЧ.

Блок 58 формирования частотных компонентов содержит (фиг.8): третий управляемый синтезатор 131 частот, предназначенный для приема с третьего блока 57 ФАПЧ сигнала подстройки тактовой частоты и для формирования сигнала тактовой частоты приемной стороны; второй формирователь 132 частоты, предназначенный для формирования сигнала с частотой из сигнала третьего управляемого синтезатора 131 частот; группу формирователей 133-135 косинусных составляющих, предназначенных каждый для формирования соответствующей из косинусных составляющих cos Ω1t, cos Ω2t, ...cos Ωn/2t, описанных далее; группу формирователей 136-138 синусных составляющих, предназначенных каждый для формирования соответствующей из синусных составляющих sin Ω1t, sin Ω2t, ...sin Ωn/2t, описанных далее; цепь 139 фазовой автоподстройки частоты (ФАПЧ), предназначенную для подстройки частоты описанного далее сигнала по сигналу со второго формирователя 132 частоты; четвертый управляемый синтезатор 140 частот, предназначенный для формирования сигнала с частотой, подстраиваемой цепью 139 ФАПЧ; третий формирователь 141 частоты, предназначенный для формирования сигнала с частотой из сигнала второго формирователя 132 частот; четвертый формирователь 142 частоты, предназначенный для формирования сигнала с частотой kf1 из сигнала четвертого управляемого синтезатора 140 частот; пятый формирователь 143 частоты, предназначенный для формирования сигнала с частотой f1 из сигнала четвертого управляемого синтезатора 140 частот; шестой формирователь 144 частоты, предназначенный для формирования сигнала с частотой f1/2 из сигнала четвертого управляемого синтезатора 140 частот. Выходы группы формирователей 133-135 косинусных составляющих и выходы группы формирователей 136-138 синусных составляющих являются, соответственно, первой группой выходов и второй группой выходов четвертого блока 58 формирования частотных компонентов. Выходы второго-шестого формирователей 132, 141-144 частоты являются, соответственно, первым-пятым выходами блока 58 формирования частотных компонентов.

Способ передачи и приема сигналов КАМ по настоящему изобретению реализуется в показанной системе следующим образом.

Исходная битовая последовательность с частотой kf1 поступает на информационный вход формирователя 1 m-уровневых символов (фиг.2), который преобразует эту битовую (т.е. двоичную) последовательность в последовательность m-уровневых символов, где m=2k, k=2, 3, ..., следующих с первой тактовой частотой f1. В принципе, формирователь 1 не потребуется, если исходной последовательностью будет именно последовательность m-уровневых символов. Первая тактовая частота вырабатывается в формирователе 2 тактовых частот передающей стороны на первом выходе входящего в него блока 3 деления частоты из поступающего на его вход сигнала тактовой частоты kf1. В случае, когда исходной является последовательность m-уровневых символов, первая тактовая частота f1 поступает непосредственно с входа. Тогда в формирователе 2 тактовых частот необходимо будет предусмотреть дополнительное умножение частоты в блоке 21 умножения частоты, либо добавить соответствующий умножитель частоты перед блоком 21.

Полученная последовательность m-уровневых символов с формирователя 1 поступает на разделитель 4 каналов, где эта последовательность разделяется на канал I передающей стороны с четными m-уровневыми символами и канал Q передающей стороны с нечетными m-уровневыми символами. Частота следования m-уровневых символов в каждом из каналов I и Q передающей стороны равна f1/2. Соответствующий тактовый сигнал формируется на втором выходе блока 3 деления частоты в формирователе 2 тактовых частот.

В канале I передающей стороны четные m-уровневые символы поступают в первый формирователь 5 пачек, где четные m-уровневые символы с одного выхода разделителя 4 запоминаются в виде пачек из М m-уровневых символов на интервале

где 2L-1<M<2L, L=5, 6, 7.... Аналогично, в канале Q передающей стороны нечетные m-уровневые символы поступают во второй формирователь 6 пачек, где нечетные m-уровневые символы с другого выхода разделителя 4 запоминаются в виде аналогичных пачек из М m-уровневых символов на том же самом интервале Т. Кроме того, в каждом из формирователей 5 и 6 пачек каждая формируемая пачка из М m-уровневых символов дополняется n заранее заданными символами до общего числа М+n=2L. Отметим, что на формирователи 5, 6 пачек подается сигнал с частотой 1/T, т.е., с третьего выхода блока 3 деления частоты в формирователе 2 тактовых частот.

В каждом из каналов I и Q передающей стороны все значения m-уровневых символов в нечетных парах пачек инвертируются, соответственно, в первом и втором перемножителях 7 и 8. Одна половина значений заранее заданных символов, добавленных в каждую нечетную пару пачек в каждом из формирователей 5 и 6 пачек в каналах I и Q передающей стороны, тоже инвертируется, соответственно, в третьем и четвертом перемножителях 9 и 10. Это инвертирование обеспечивается путем перемножения всех поступающих на перемножители 7-10 значений на меандровый сигнал вида

со значениями +1 и -1 и с частотой 1/4T, подаваемый с четвертого выхода блока 3 деления частоты в формирователе 2 тактовых частот. Отметим, что вторая половина значений заранее заданных символов, добавленных в каждую пачку в каждом из формирователей 5 и 6 пачек в каналах I и Q передающей стороны, инвертированию не подвергается.

Каждая пачка из М m-уровневых символов, инвертированная или нет, вместе со всеми n добавленными к ней заранее заданными значениями, одна половина которых может быть инвертирована, а другая половина без инвертирования, поступает в соответствующем из каналов I и Q передающей стороны на третий или четвертый формирователи 11 и 12 пачек. Каждый из этих формирователей 11 и 12 предназначен для разделения каждой пачки из М+n символов пополам и параллельной выдачи обеих половин на соответствующем своем выходе.

Каждая "полупачка" из m-уровневых символов поступает на один из первого-четвертого блоков 13-16 обратного преобразования Фурье (ОПФ), где с помощью ОПФ происходит замена каждой пачки из символов набором из М+n временных отсчетов.

Наборы из М+n временных отсчетов с выходов первого-четвертого блоков 13-16 ОПФ параллельно поступают на входы одноименных параллельно-последовательных преобразователей 17-20. Каждый из этих преобразователей 17-20 предназначен для преобразования в каждом из каналов I и Q передающей стороны параллельного набора из М+n временных отсчетов в соответствующую последовательность из М+n временных отсчетов с второй тактовой частотой

Сигнал этой частоты выдается с пятого выхода формирователя 2 тактовых частот, где этот сигнал получается с первого выхода блока 21 умножения частоты, на вход которого подается тактовая частота kf1 исходной последовательности битовых символов.

Далее обеспечивается поворот по фазе на π/2 всех частот спектра одной из двух последовательностей из М+n временных отсчетов в каждом из каналов I и Q передающей стороны (что и представляет собой преобразование Гильберта в данном случае). Эту операцию выполняют в каналах I и Q передающей стороны первый и второй блоки 22, 23 преобразования Гильберта, соответственно. Другая последовательность из М+n временных отсчетов в каждом из каналов I и Q передающей стороны задерживается, соответственно, первым или вторым блоком 24, 25 задержки на время обработки в соответствующем блоке 22, 23 преобразования Гильберта.

Обе полученные после этих преобразований последовательности из М+n временных отсчетов - с повернутыми фазами и задержанная - в каждом из каналов I и Q передающей стороны поступают на соответствующие входы первого (в канале I) и второго (в канале Q) поотсчетного сумматора 26 и 27, где производится поотсчетное объединение этих последовательностей из М+n временных отсчетов из одноименного блока 22, 23 преобразования Гильберта и одноименного блока 24, 25 задержки в одну последовательность той же длины.

Полученные объединенные последовательности в каждом из каналов I и Q передающей стороны фильтруются, соответственно, первым и вторым блоками 28 и 29 фильтрации. Эта фильтрация осуществляется с второй тактовой частотой f2, подаваемой с шестого выхода формирователя 2 тактовых частот (с второго выхода блока 21 умножения частоты) в диапазоне от 0 до f2/2 в соответствующем из каналов I и Q передающей стороны.

Наконец, полученный отфильтрованный сигнал в каждом из каналов I и Q передающей стороны поступает на формирователь 30 сигнала на передачу. В формирователе 30 в пятом и шестом перемножителях 31, 32 осуществляется перемножение отфильтрованных последовательностей на косинусный и синусный сигналы несущей частоты и сложение результатов этого перемножения в блоке 33 сложения. Сигнал с выхода блока 33 сложения в формирователе 30 поступает в канал связи (не показано на фиг.2).

После прохождения канала связи передаваемый сигнал поступает на приемную сторону (фиг.3). После прохождения обычных для любого приемника средств усиления, фильтрации и преобразования на промежуточную частоту (не показаны на фиг.3) принятый сигнал поступает в блок 41 квадратурного преобразования. В этом блоке 41 принятый сигнал промежуточной частоты попадает на входы седьмого и восьмого перемножителей 61 и 62, в каждом из которых входной сигнал перемножается с косинусной или синусной составляющей частоты , где является частотой приблизительной расстройки от промежуточной частоты . Полученные при таком перемножении сигналы фильтруются, соответственно, в первом и втором фильтрах 63 и 64, выделяющих каждый соответственно синусную и косинусную компоненты принимаемого сигнала.

Эти выделенные компоненты представляют собой аналоговые сигналы, которые подаются, соответственно, на