Устройство моделирования непрерывной случайной величины по гистограмме

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в имитаторах случайных процессов, а также в специализированных и универсальных вычислительных машинах. Техническим результатом является расширение функциональных возможностей устройства. Устройство содержит датчик случайных чисел, генератор тактовых импульсов, генератор ступенчатого напряжения, блок сравнения, счетчик, дешифратор, триггер, формирователь импульсов, блоки памяти, элементы задержки, элементы И, умножитель, сумматор, блок задания исходных данных, блок сумматоров, блок вычитателей, блок амплитудных дискриминаторов, преобразователь ″код-амплитуда″, блоки элементов И, элементы ИЛИ. 1 ил.

Реферат

Предлагаемое изобретение относится к вычислительной технике, предназначено для генерирования непрерывной случайной величины (НСВ) с неизвестным законом распределения по гистограмме и может быть использовано в имитаторах случайных процессов, а также в специализированных и универсальных вычислительных машинах при проведении имитационных экспериментов.

Известен генератор случайных чисел с произвольным законом распределения [1], содержащий датчик случайных чисел с равномерным законом распределения, три регистра, блок управления, схему сравнения, два счетчика, блок памяти, блок умножения, сумматор и блок элементов ИЛИ.

Недостатком генератора является использование кусочно-полиномиальной аппроксимации заданной функции распределения СВ, что снижает точность воспроизведения случайной величины.

По техническому решению наиболее близким к предлагаемому изобретению является генератор случайных чисел с произвольным законом распределения [2], который и выбран в качестве прототипа.

Генератор содержит генератор тактовых импульсов, выход которого соединен со входом датчика случайных чисел, равномерно распределенных в интервале (0, 1), через первый элемент задержки со счетным входом триггера и с первым входом первого элемента И. Выход датчика случайных чисел соединен с первыми входами второго и третьего элементов И. Единичный выход триггера соединен со вторыми входами первого и второго элементов И. Нулевой выход триггера соединен со вторым входом третьего элемента И. Выход первого элемента И соединен с первым входом генератора ступенчатого напряжения. Выход второго элемента И через первый блок памяти соединен с первым входом блока сравнения, второй вход которого подключен к выходу генератора ступенчатого напряжения и через формирователь импульсов к счетному входу счетчика, вход «установка» которого через второй элемент задержки соединен со вторым входом генератора ступенчатого напряжения, с управляющим входом дешифратора и с выходом блока сравнения. Выход счетчика через дешифратор соединен со входами второго и третьего блоков памяти, выходы которых соединены с первыми входами умножителя и сумматора. Выход третьего элемента И через умножитель соединен со входом сумматора, выход которого является выходом устройства.

Генератор работает следующим образом. В исходном положении триггера первый и второй элементы И открыты, а третий элемент И закрыт. Импульс, вырабатываемый генератором тактовых импульсов при пуске, проходит через первый элемент И и запускает генератор ступенчатого напряжения, а также побуждает датчик случайных чисел выдать случайное число R, которое проходит через второй элемент И на вход первого блока памяти и на блок сравнения. Этот же импульс через первый элемент задержки поступает на триггер и переключает его. При этом закрываются первый и второй элементы И и открывается третий элемент И. С выхода генератора ступенчатого напряжения на второй вход блока сравнения последовательно поступают скачки напряжения, значения которых пропорциональны величинам В блоке сравнения эти величины в той же последовательности сравниваются с числом R. Блок сравнения выдает сигнал только в том случае, когда удовлетворяется одно из неравенств

где i - номер интервала

Ступенчато возрастающее выходное напряжение генератора ступенчатого напряжения подается на вход формирователя импульсов. При каждом скачке напряжения формирователь выдает импульс, поступающий на счетчик. Число накопленных в счетчике импульсов является адресом, по которому во втором и третьем блоках памяти записаны величины xi-1 и xi-xi-1 соответственно. Содержимое счетчика подается во второй и третий блоки памяти через дешифратор. Из второго блока памяти величина xi-1 поступает в сумматор, а из третьего блока памяти величина xi- xi-1=Δxi - в блок умножения. В момент, когда выполняется неравенство (1), число импульсов в счетчике равно i. В этот момент выходной сигнал блока сравнения поступает на второй вход дешифратора, разрешая выдачу адреса из счетчика во второй и третий блоки памяти. Одновременно выходной сигнал блока сравнения поступает на вход генератора ступенчатого напряжения и через второй элемент задержки на вход ″установка″ счетчика. Под действием этого сигнала генератор ступенчатого напряжения возвращается в исходное положение и очищается счетчик. Второй импульс генератора тактовых импульсов побуждает датчик случайных чисел выдать второе случайное число R, которое через открытый третий элемент И (первый и второй элементы И закрыты) поступает на вход блока умножения. Величина, равная произведению ΔXi·R2, поступает в сумматор, где складывается с величиной Хi-1 и формируется случайное число X. Одновременно второй импульс генератора тактовых импульсов через первый элемент задержки поступает на счетный вход триггера и переключает его. Вследствие этого третий элемент И закрывается, первый и второй элементы И открываются, и устройство готово к циклу выработки очередного случайного числа.

К недостаткам генератора относится его нечувствительность к изменению границ интервалов значений НСВ и частот попадания НСВ в эти интервалы, что сужает его функциональные возможности.

Целью изобретения является расширение функциональных возможностей генератора путем устранения указанных недостатков.

Цель изобретения достигается тем, что в известное устройство, содержащее генератор тактовых импульсов, выход которого соединен со входом датчика случайных чисел и через элемент задержки со счетным входом триггера, единичный выход которого соединен с первым входом первого элемента И, а нулевой - с первым входом второго элемента И, выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом первого блока памяти, а выход умножителя подключен к первому входу сумматора, выход которого является выходом устройства, а второй вход соединен с выходом второго блока памяти; выход датчика случайных чисел подключен ко вторым входам первого и второго элементов И, дополнительно введены блок задания исходных данных, блок сумматоров, блок вычитателей, блок амплитудных дискриминаторов, преобразователь ″код-амплитуда″, первый и второй блоки элементов И, первый и второй элементы ИЛИ, выходы которых соединены со входами первого и второго блоков памяти соответственно; входы первого элемента ИЛИ соединены с выходами первого блока элементов И, а входы второго элемента ИЛИ - с выходами второго блока элементов И, управляющие входы которого подключены к выходам блока амплитудных дискриминаторов и соответствующим управляющим входам первого блока элементов И, информационные входы которого соединены с выходами блока вычитателей, входы которого соединены с соответствующими информационными входами второго блока элементов И и граничными выходами блока задания исходных данных, первый, второй и последний частотные выходы которого подключены к соответствующим пороговым входам блока амплитудных дискриминаторов, остальные частотные выходы блока задания исходных данных подключены ко входам блока сумматоров, выходы которого соединены с соответствующими остальными пороговыми входами блока амплитудных дискриминаторов, информационный вход которого подключен к выходу преобразователя ″код-амплитуда″, вход которого соединен с выходом первого элемента И.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается тем, что содержит дополнительно введенные блоки: блок задания исходных данных, блок сумматоров, блок вычитателей, блок амплитудных дискриминаторов, преобразователь ″код-амплитуда″, первый и второй блоки элементов И, первый и второй элементы ИЛИ, а также связи между ними. Кроме того, введение указанных блоков позволило упростить структуру блоков памяти и исключить из предлагаемого устройства такие имеющиеся в прототипе блоки, как генератор ступенчатого напряжения, блок сравнения, формирователь импульсов, счетчик, дешифратор, блок памяти, элемент задержки, элемент И, а также связи между ними.

Таким образом, заявляемое устройство соответствует критерию изобретения ″новизна″.

Сравнение заявляемого решения с другими техническими решениями показывает, что вновь введенные блоки известны [3].

Однако при их введении в указанной связи с остальными элементами схемы в заявляемое устройство оно проявляет новые свойства, что приводит к расширению функциональных возможностей устройства. Это позволяет сделать вывод о соответствии технического решения критерию ″существенные отличия″.

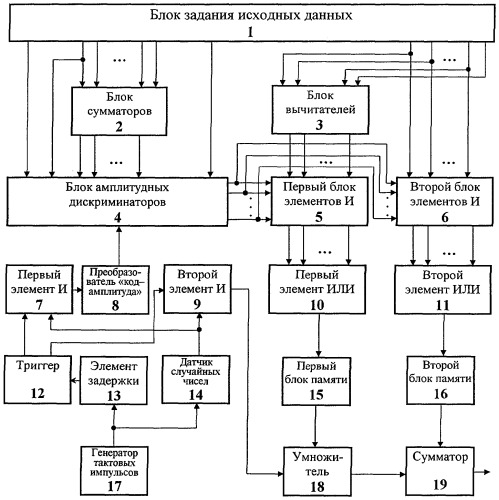

Блок-схема устройства представлена на чертеже.

Устройство содержит:

1 - блок задания исходных данных, с ″частотных″ выходов которого поступает информация о частотах попадания случайной величины (СВ) в каждый из К интервалов, на которые разбит весь диапазон возможных значений СВ, а с ″граничных″ выходов - информация о границах этих интервалов. Первый, второй и последний ″частотные″ выходы подключены к соответствующим пороговым входам блока 4 амплитудных дискриминаторов. Остальные ″частотные″ выходы блока 1 подключены ко входам блока 2 сумматоров, а ″граничные″ выходы - ко входам блока 3 вычитателей и информационным входам второго блока 6 элементов И;

2 - блок сумматоров на К-1 входов и К-2 выходов (в составе К-2 сумматоров на два входа каждый). Входы блока сумматоров подключены к соответствующим ″частотным″ выходам блока 1 задания исходных данных, а выходы - к соответствующим пороговым входам блока 4 амплитудных дискриминаторов;

3 - блок вычитателей на К+1 входов и К выходов (в составе К вычитателей на два входа каждый), входы которого соединены с ″граничными″ выходами блока 1 задания исходных данных, а выходы - с соответствующими информационными входами первого блока 5 элементов И;

4 - блок амплитудных дискриминаторов на К+1 пороговых входов, один информационный вход и К выходов (в составе К амплитудных дискриминаторов на один информационный и два пороговых входа каждый), информационный вход которого подключен к выходу преобразователя 8 ″код-амплитуда″, а соответствующие пороговые входы соединены с первым, вторым и последним ″граничными″ выходами блока 1 задания исходных данных и выходами блока 2 сумматоров. Выходы блока 4 соединены с соответствующими управляющими входами первого 5 и второго 6 блоков элементов И;

5 - первый блок элементов И на К информационных входов, К управляющих входов и К выходов (в составе К элементов И на два входа каждый), информационные входы которого подключены к выходам блока 3 вычитателей, управляющие входы - к выходам блока 4 амплитудных дискриминаторов, а выходы соединены со входами первого элемента ИЛИ 10;

6 - второй блок элементов И на К информационных входов, К управляющих входов и К выходов (в составе К элементов И на два входа каждый), информационные входы которого подключены к соответствующим ″граничным″ выходам блока 1 задания исходных данных, управляющие входы - к выходам блока 4 амплитудных дискриминаторов, а выходы соединены со входами второго элемента ИЛИ 11;

7 - первый элемент И, первый (управляющий) вход которого подключен к единичному выходу триггера 12, второй (информационный) вход соединен с выходом датчика 14 случайных чисел, а выход подключен ко входу преобразователя 8 ″код-амплитуда″;

8 - преобразователь ″код-амплитуда″, вход которого подключен к выходу первого элемента И 7, а выход - к информационному входу блока 4 амплитудных дискриминаторов;

9 - второй элемент И, первый (управляющий) вход которого подключен к нулевому выходу триггера 12, второй (информационный) вход соединен с выходом датчика 14 случайных чисел, а выход подключен к первому входу умножителя 18;

10 - первый элемент ИЛИ, входы которого подключены к выходам первого блока 5 элементов И, а выход - ко входу первого блока 15 памяти;

11 - второй элемент ИЛИ, входы которого подключены к выходам второго блока 6 элементов И, а выход - ко входу второго блока 16 памяти;

12 - триггер, единичный выход которого соединен с первым входом первого элемента И 7, нулевой выход - с первым входом второго элемента И 9, а вход подключен к выходу элемента 13 задержки;

13 - элемент задержки, вход которого подключен к выходу генератора 17 тактовых импульсов, а выход - ко входу триггера 12;

14 - датчик случайных чисел с равномерным распределением на интервале [0, 1), вход которого соединен с выходом генератора 17 тактовых импульсов, а выход - со вторыми входами первого 7 и второго 9 элементов И;

15 - первый блок памяти, вход которого подключен к выходу первого элемента ИЛИ 10, а выход - ко второму входу умножителя 18;

16 - второй блок памяти, вход которого подключен к выходу второго элемента ИЛИ 11, а выход - ко второму входу сумматора 19;

17 - генератор тактовых импульсов, выход которого подключен ко входам элемента 13 задержки и датчика 14 случайных чисел;

18 - умножитель, первый вход которого соединен с выходом второго элемента И 9, второй вход - с выходом первого блока 15 памяти, а выход подключен к первому входу сумматора 19;

19 - сумматор, первый вход которого соединен с выходом умножителя 18, второй вход - с выходом второго блока 16 памяти, а выход является выходом устройства.

Устройство работает следующим образом. С ″частотных″ выходов блока 1 задания исходных данных снимаются сигналы, пропорциональные частотам Р1, Р2...,Рк-1 попадания СВХ в первые К-1 интервалов ее значений (из общего количества К интервалов, на которые разбит весь диапазон значений [Х0, Хк] этой случайной величины).

Поступая на блок 2 сумматоров, эти сигналы после их почленного суммирования формируют на выходах блока 2 ″сетку″ пороговых напряжений , которые вместе с сигналами 0, P1 и 1, снимаемыми с первого, второго и последнего частотных выходов блока 1 задания исходных данных, попарно поступают на пороговые входы амплитудных дискриминаторов блока 4.

С ″граничных″ выходов блока 1 сигналы, соответствующие границам x0, х1,...хк интервалов значений СВХ попарно (хо, х1; х1, х2;...; хк-1, хк) поступают на вычитатели блока 3, на выходах которого формируются значения длин соответствующих интервалов:

Значения х0, х1,...,хк-1 левых границ всех К интервалов с соответствующих ″граничных″ выходов блока 1 поступают на информационные входы элементов И второго блока 6 элементов И.

В исходном положении триггера 12 первый элемент И 7 открыт, а второй элемент И 9 закрыт. Импульс, вырабатываемый генератором 17 при пуске, побуждает датчик 14 выдать первое случайное число R1, которое через открытый первый элемент И 7 поступает на преобразователь 8. Этот же импульс через элемент задержки 13 поступает на триггер 12 и переключает его. При этом закрывается первый элемент И 7 и открывается второй элемент И 9. Информация о первом случайном числе, содержащаяся в амплитуде импульса на выходе преобразователя 8, поступает на информационный вход каждого амплитудного дискриминатора блока 4, на пороговые входы которых подаются соответствующие пороговые напряжения. В зависимости от того, между какими порогами лежит значение амплитуды импульса (какое из неравенств (1) выполняется), срабатывает соответствующий амплитудный дискриминатор блока 4, выдавая импульс на соответствующий выход блока 4 и связанные с ним управляющие входы соответствующих элементов И первого 5 и второго 6 блоков элементов И. На информационные входы соответствующих элементов И первого блока 5 подаются значения длин интервалов, а второго блока 6 элементов И - значения левых границ соответствующих интервалов. Таким образом, по первому случайному числу на выходе второго элемента ИЛИ 11 фиксируется левая граница xi-1 интервала, в который попало это случайное число, а на выходе первого элемента ИЛИ 10 - длина Δxi этого интервала. Эти значения запоминаются соответственно во втором 16 и первом 15 блоках памяти.

Второй импульс генератора 17 побуждает датчик 14 выдать второе случайное число R2, которое через открытый второй элемент И 9 (первый элемент И 7 закрыт) поступает на вход умножителя 18. Величина, равная произведению Δхi·R2, поступает в сумматор 19, где складывается с величиной Xi-1 и формируется случайное число X. Одновременно второй импульс генератора 17 через элемент 13 задержки поступает на счетный вход триггера 12 и переключает его. Вследствие этого первый элемент И 7 открывается, второй элемент И 9 закрывается, и устройство готово к циклу выработки очередного случайного числа.

Источники информации

1. Авторское свидетельство СССР №1509883, кл. G 06 F 7/58, 1989.

2. Авторское свидетельство СССР №877534, кл. G 06 F 7/58, 1981 (прототип).

3. Горошков Б.И. Элементы радиоэлектронных устройств: Справочник. - М.: Радио и связь, 1988.

Устройство моделирования непрерывной случайной величины по гистограмме, содержащее генератор тактовых импульсов, выход которого соединен со входом датчика случайных чисел и через элемент задержки со счетным входом триггера, единичный выход которого соединен с первым входом первого элемента И, а нулевой - с первым входом второго элемента И, выход которого подключен к первому входу умножителя, второй вход которого соединен с выходом первого блока памяти, а выход умножителя подключен к первому входу сумматора, выход которого является выходом устройства, а второй вход соединен с выходом второго блока памяти; выход датчика случайных чисел подключен ко вторым входам первого и второго элементов И, отличающееся тем, что в него дополнительно введены блок задания исходных данных, блок сумматоров, блок вычитателей, блок амплитудных дискриминаторов, преобразователь ″код-амплитуда″, первый и второй блоки элементов И, первый и второй элементы ИЛИ, выходы которых соединены со входами первого и второго блоков памяти соответственно; входы первого элемента ИЛИ соединены с выходами первого блока элементов И, а входы второго элемента ИЛИ - с выходами второго блока элементов И, управляющие входы которого подключены к выходам блока амплитудных дискриминаторов и соответствующим управляющим входам первого блока элементов И, информационные входы которого соединены с выходами блока вычитателей, входы которого соединены с соответствующими информационными входами второго блока элементов И и граничными выходами блока задания исходных данных, первый, второй и последний частотные выходы которого подключены к соответствующим пороговым входам блока амплитудных дискриминаторов, остальные частотные выходы блока задания исходных данных подключены ко входам блока сумматоров, выходы которого соединены с соответствующими остальными пороговыми входами блока амплитудных дискриминаторов, информационный вход которого подключен к выходу преобразователя ″код-амплитуда″, вход которого соединен с выходом первого элемента И.