Расширение набора команд с использованием 3-байтового кода операции перехода

Иллюстрации

Показать всеИзобретение относится к микропроцессорным системам, в частности к расширению набора команд с использованием 3-байтовых значений кода операции перехода в поле кода операции. Техническим результатом является расширение набора команд без увеличения сложности аппаратных средств. Устройство для декодирования длины команды расширенного набора команд, использующего 3-байтовые коды операции перехода, содержит детектор операции перехода и декодер длины команды. Система расширения набора команд с использованием 3-байтовых кодов операции перехода содержит память для хранения кода команды, логику выборки кода команды из памяти и блок декодирования для генерации одного или более сигналов управления. Один из вариантов устройства для выполнения набора команд, использующего 3-байтовые коды операции перехода, содержит декодер для генерации сигнала управления и исполнительный блок, а другой вариант содержит средство для выборки из памяти кода команды в формате команды переменной длины и средство для инициирования операции, соответствующей значению специфического для команды кода операции. Способы описывают работу указанных устройств и системы. 7 н. и 69 з.п. ф-лы, 7 ил., 1 табл.

Реферат

Область техники

Настоящее изобретение относится к микропроцессорным системам. В частности, изобретение относится к расширению набора команд с использованием 3-байтовых значений кода операции перехода в поле кода операции.

Предшествующий уровень техники

Микропроцессорная технология развивается уже многие годы с высокой скоростью. Достижения в компьютерной архитектуре и полупроводниковой технике создали множество возможностей для проектирования новых процессоров. Имеются два типовых варианта проектирования новых процессоров: (1)определение полностью новой архитектуры и (2) расширение существующей архитектуры для включения новых функций. Каждый вариант имеет как преимущества, так и недостатки. Однако когда процессор захватывает значительный сегмент рынка, то вариант (2) предоставляет множество существенных выгод. Основное преимущество наращивания существующей архитектуры состоит в совместимости с современными и более ранними моделями. Недостатки включают в себя проблемы выхода за пределы ограничений, налагавшихся более ранними моделями.

Новые процессоры связаны с реализацией новых функций как в аппаратных средствах, так и в программном обеспечении. Новый процессор, основанный на существующей модели, в типовом случае имеет дополнительный набор команд, который может получить выгоды от новой структуры аппаратных средств. Однако наращивание набора команд путем добавления нового набора команд является серьезной проблемой ввиду ограничений в кодировании этих команд. Поэтому имеется потребность в технологии для обеспечения эффективного способа для расширения набора команд без увеличения сложности аппаратных средств.

Краткое описание чертежей

Признаки и преимущества изобретения поясняются в последующем детальном описании со ссылками на чертежи, на которых представлено следующее:

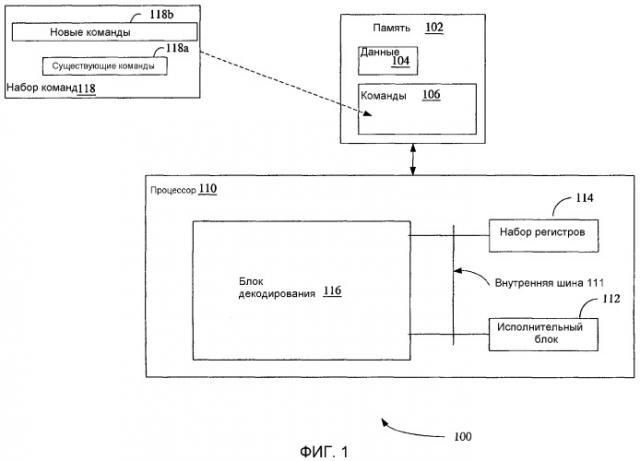

Фиг.1 - блок-схема, иллюстрирующая, по меньшей мере, один вариант осуществления системы обработки, который может использовать раскрытые методы.

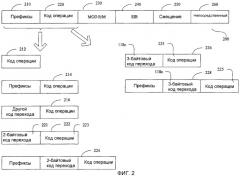

Фиг.2 - блок-схема, иллюстрирующая, по меньшей мере, один вариант осуществления формата для команды.

Фиг.3 - блок-схема, иллюстрирующая, по меньшей мере, один вариант осуществления логики для декодирования команды.

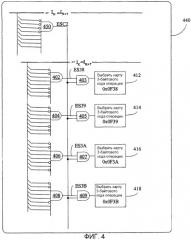

Фиг.4 - блок-схема, иллюстрирующая, по меньшей мере, один вариант осуществления схемы для декодирования команды нового типа 1.

Фиг.5 - блок-схема детектора префикса и перехода, схемы деблокирования декодера и декодера кода операции в соответствии с, по меньшей мере, одним вариантом осуществления изобретения.

Фиг.6 - блок-схема алгоритма, иллюстрирующая процесс выполнения декодирования команды с использованием префиксов, в соответствии с, по меньшей мере, одним вариантом осуществления изобретения.

Фиг.7 - блок-схема алгоритма, иллюстрирующая, по меньшей мере, один вариант осуществления способа декодирования длины команды.

Описание настоящего изобретения

Ниже раскрыты варианты осуществления способа, устройства и системы для расширения набора команд, использующего 3-байтовые коды операции перехода. Раскрытые варианты осуществления обеспечивают расширение набора команд, который использует 3-байтовые коды операций перехода, путем использования префикса для определения команды, которая включает в себя трехбайтовый код операции перехода. Раскрытые способы используют набор существующих полей команд для определения нового набора команд и обеспечения эффективного механизма для декодирования нового набора команд.

Термин «трехбайтовый код операции», как он используется в настоящем описании, относится к двухбайтовому значению, которое указывает логике декодера, что код операции для команды, представляющей интерес, включает в себя три байта: два байта трехбайтового кода операции перехода плюс однобайтовый код операции, специфический для команды. По меньшей мере, для одного варианта осуществления двухбайтовое значение в трехбайтовом коде операции перехода имеет одно из следующих значений: 0х0F38, 0x0F39, 0x0F3A или 0x0F3B.

В последующем описании, в целях пояснения, изложены различные конкретные детали, касающиеся типов процессоров, форматов команд, типов логических схем и значений кода операции перехода, чтобы обеспечить глубокое понимание настоящего изобретения. Однако специалистам в данной области техники должно быть понятно, что эти конкретные детали не требуются для реализации настоящего изобретения. В других случаях хорошо известные электрические структуры и схемы показаны в форме блок-схемы, чтобы не загромождать описание изобретения несущественными деталями. В последующем описании предполагается, что запись 0х указывает, что следующее число записано в шестнадцатеричном формате.

На фиг.1 представлен, по меньшей мере, один вариант осуществления системы 100 обработки, которая может использовать раскрытые методы. Система 100 может быть использована, например, для декодирования и исполнения команд нового типа 0 и команд нового типа 1. В целях настоящего раскрытия система обработки включает в себя любую систему, которая имеет процессор 110, например цифровой процессор сигналов (DSP), микроконтроллер, специализированную интегральную схему (ASIC) или микропроцессор. Процессор 110 может иметь любой тип архитектуры, например, такой как архитектура компьютера с полным набором команд (CISC), архитектура компьютера с сокращенным набором команд (RISC), архитектура компьютера с командными словами сверхбольшой длины (VLIW), многопоточная или гибридная архитектура. Система 100 является представителем систем обработки на базе микропроцессоров Itanium® и Itanium®II, а также Pentium®, Pentium®Pro, Pentium®II, Pentium®III, Pentium®4, разработанных компанией Intel Corporation. Также могут использоваться и другие системы (включая персональные компьютеры (РС), имеющие другие микропроцессоры, рабочие станции, персональные цифровые помощники и другие портативные устройства, приставки и т.п.). В одном варианте осуществления система 100 может исполнять версию операционной системы WindowsTM компании Microsoft Corporation, хотя также могут использоваться и другие операционные системы и графические пользовательские интерфейсы.

На фиг.1 показано, что процессор 110 включает в себя блок 116 декодирования, набор 114 регистров, по меньшей мере, один исполнительный блок 112 и, по меньшей мере, одну внутреннюю шину 111 для команд исполнения. Разумеется, процессор 110 содержит дополнительные схемы, которые не являются необходимыми для понимания изобретения. Блок 116 декодирования, регистры 114 и исполнительный блок 112 связаны между собой одной или несколькими внутренними шинами 111. Блок 116 декодирования используется для декодирования команд, принятых процессором 110, для получения сигналов управления и/или точек входа микрокода. Команды могут выдаваться в блок 116 декодирования посредством буфера команд (например, 310 на фиг.3). В ответ на эти сигналы управления и/или точки входа микрокода исполнительный блок 112 выполняет соответствующие операции. Блок 116 декодирования может быть реализован с использованием любого количества различных механизмов (например, таблицы перекодировки, аппаратной реализации, программируемой логической матрицы (ПЛМ) и т.д.).

Блок 116 декодирования имеет возможность декодирования команд 106, которые следуют формату, определенному расширенным набором 118 команд. Набор 118 команд включает в себя существующий набор 118а команд и новый набор 118b команд. Набор 118 команд включает в себя команды для выполнения операций над скалярными и упакованными данными. Числовой формат для этих операций может быть любым удобным форматом, включая числа с обычной точностью, с удвоенной точностью, расширенные числа с плавающей запятой, числа со знаком и без знака и нечисловые данные. По меньшей мере, в одном варианте осуществления команды, определенные в наборе 118 команд, могут изменяться по длине одна относительно другой.

Команды 106 в формате, установленном набором 118 команд, могут сохраняться в системе 102 памяти. Под системой 102 памяти понимается обобщенное представление памяти или иерархий памяти, и она может включать в себя множество форм памяти, таких как накопитель на жестких дисках, ПЗУ на компакт-дисках (CD-ROM), ОЗУ (RAM), динамическая память с произвольным доступом (DRAM), статическая память с произвольным доступом (SRAM), флэш-память и связанные с ними схемы. Система 102 памяти может хранить, помимо команд 106, данные 104, представленные сигналами данных, которые могут исполняться процессором 110.

Формат команд

На фиг.2 представлена диаграмма, иллюстрирующая формат команды 200 соответственно варианту осуществления изобретения. Формат 200 команды включает в себя поле 210 префикса, поле 220 кода операции и поля спецификатора операнда (например, modR/M, система счисления-индекс-основание (SIB), смещение, непосредственный и т.д.). Поля спецификатора операнда являются факультативными и включают поле 230 «modR/M», поле 240 «SIB», поле 250 «смещение», поле 260 «непосредственный».

Содержимое поля 230 «modR/M» указывает форму адресации. Поле 230 «modR/M» может определять регистры и режимы адресации.

Определенное кодирование информации в поле 230 «modR/M» может указывать, что второй байт информации адресации присутствует в поле 240 «SIB» для полного определения формы адресации кода команды. Например, форма адресации «основание-плюс-индекс» и форма адресации «система счисления-плюс-индекс» могут каждая включать в себя в поле 240 «SIB» информацию, такую как масштабный коэффициент, номер регистра для индекса и/или номер регистра для индексного регистра.

Специалистам в данной области техники должно быть понятно, что формат 200, показанный на фиг.2, является иллюстративным и что в раскрытых вариантах осуществления могут использоваться другие структуры данных в коде команды. Например, нет необходимости упорядочивать поля 210, 220, 230, 240, 250, 260 в том порядке, как показано, они могут быть переупорядочены в другие местоположения по отношению друг к другу и не обязательно должны следовать непрерывно. Также длины описываемых полей не следует трактовать ограничивающим образом. Поле, описываемое как конкретное число байтов, в альтернативных вариантах осуществления может быть реализовано как поле большей или меньшей длины. Также термин «байт», используемый здесь как ссылающийся на группу из 8 битов, в других вариантах осуществления может быть реализован как группа любого другого размера, например, 4 бита, 16 битов и 32 бита.

Команда, используемая в настоящем описании, такая как команды 106, показанные на фиг.1, включает в себя определенные значения в полях формата 200 команды, показанного на фиг.2. Такая команда иногда называется «действующая (рабочая) команда». Битовые значения для действительной команды иногда здесь упоминаются как «код команды».

Допустимые байтовые значения для действительной команды определены в наборе 118 команд (фиг.1). Допустимые байтовые значения для каждого из полей формата 200 команды представляют собой те значения, которые логика декодирования, такая как декодер 306 длины команды (фиг.3) и блок 116 декодирования (фиг.1) распознают и обрабатывают для генерации декодированного кода операции. Для каждого кода команды соответствующий декодированный код команды уникальным образом представляет операцию, выполняемую исполнительным блоком 112 (фиг.1) в ответ на код команды. Декодированный код команды может включать в себя одну или более микроопераций.

Поле 210 префикса, показанное на фиг.2, может включать в себя ряд префиксов. В одном варианте осуществления поле 210 префикса включает в себя до четырех префиксов, причем каждый префикс содержит один байт. Поле 210 префикса является факультативным. Для описываемого расширенного нового набора команд поле префикса используется для расширения трехбайтового пространства команды кода операции перехода.

Содержимое поля 220 кода операции определяет операцию. Для, по меньшей мере, одного варианта осуществления, как отмечено выше, поле кода операции для нового набора 118b команд, описываемого здесь, имеет длину три байта. По меньшей мере, в одном варианте осуществления поле 20 кода операции для расширенного нового набора 118b команд может включать в себя один, два или три байта информации. Для некоторых из новых команд в описываемом расширенном новом наборе команд (команды типа 0) трехбайтовое значение кода операции перехода в двухбайтовом поле 118с поля 220 кода операции комбинируется с содержимым третьего байта 225 поля 220 кода операции для определения операции. Третий байт 225 упоминается здесь как специфический для команды код операции. Для других из новых команд в описываемом расширенном новом наборе команд (команды типа 1) трехбайтовое значение кода операции перехода в двухбайтовом поле 118с поля 220 кода операции комбинируется с содержимым поля 210 префикса и содержимым поля 225 специфического для команды кода операции для определения операции.

В принципе, комбинация поля 210 префикса и поля 220 кода операции создает ряд различных типов команд. Для иллюстрации на фиг.2 показано только семь типов команд: регулярная (обыкновенная) однобайтовая команда 212, регулярная команда с префиксом в качестве спецификатора 214, регулярная команда 216 перехода, расширенная команда 222 первого типа, расширенная команда 224 второго типа, новая команда 226 первого типа, новая команда 228 второго типа. Как известно специалистам в данной области техники, можно определить аналогичным образом другие типы команд.

Регулярная однобайтовая команда 212 включает в себя регулярные команды с однобайтовым специфическим для команды кодом операции в поле 220 кода операции. Регулярная команда с префиксом в качестве спецификатора 214 включает в себя регулярные команды, которые используют префикс в качестве спецификатора для кода операции. Например, строковая команда может использовать значение префикса REPEAT (повторить) для повторения строковой команды число раз, определенное в счетном регистре или до тех пор, порка не будет удовлетворено определенное условие. Значение префикса, используемое в команде 214, не добавляет полностью нового смысла значению кода операции, которое следует в поле 220 кода операции. Напротив, значение префикса используется просто как спецификатор для определения кода операции с дополнительными условиями. Как пояснено ниже, использование префикса в команде 214 существенно отличается от использования его в расширенной команде второго типа 224 и в новой команде второго типа 228.

Регулярная команда 216 перехода является регулярной командой, которая использует код операции перехода в первом поле 215 поля 220 кода операции для указания аппаратным средствам декодера, что специфический для команды код операции во втором поле 217 поля 220 кода операции используется для определения команды. Например, в одном варианте осуществления значение кода операции перехода от 0ХD8 до 0xDF сопроцессора с плавающей запятой в первом байте 215 поля 220 кода операции указывает, что значение кода операции, которое следует во втором байте 217 поля 220 кода операции, должно интерпретироваться как команда сопроцессора и должно направляться в аппаратные средства сопроцессора для исполнения.

Расширенная команда первого типа 222 является командой перехода конкретного типа, которая определена как содержащая предварительно определенное значение кода операции перехода 0х0F в первом поле 221 поля 220 кода операции. Код операции перехода 0x0F указывает аппаратным средствам декодера, что специфическое для команды значение кода операции во втором поле 223 поля 220 кода операции используется для определения команды. Расширенные команды первого типа 222 могут, в зависимости от значения второго байта кода операции (и в некоторых случаях значения трех битов в поле 230 modR/M), иметь переменную длину. Например, две команды (логический сдвиг влево упакованных данных) расширенной команды типа 222 могут включать в себя следующие значения поля команды соответственно:

PSLLW(значение сдвига в регистре): 0F:F1:1b"11xxxyyy", где ххх определяет первый регистр, а ууу определяет второй регистр.

PSLLW (сдвиг на непосредственно получаемое значение): 0F:71:1b"11110xxx": непосредственно получаемые данные (8 битов), где ххх определяет регистр.

В каждой из указанных команд PSSLW первое слово поля 220 кода операции включает в себя значение перехода 0x0F. Первая команда имеет длину три байта, но вторая команда имеет длину четыре байта, так как она включает в себя байт непосредственно полученных данных.

Соответственно для расширенной команды типа 222 аппаратные средства декодера (такие, например, как декодер 306 длины команды, показанный на фиг.3) используют значение 0x0F кода операции перехода в первом поле 221 поля 220 кода операции, а также значение во втором байте 223 двухбайтового поля 220 кода операции и значение поля 230 modR/M для декодирования длины команды.

Новая команда первого типа 226 (также называемая «новой командой типа 0») является новым типом команды, которая является частью нового набора 118b команд (фиг.1), добавляемой к существующему регулярному набору 118а команд (фиг.1). Формат команды нового набора 118b команд включает в себя 3-байтовое поле 118с кода операции перехода и специфическое для команды поле 225 кода операции. 3-байтовое поле 118с кода операции перехода, по меньшей мере, в одном варианте осуществления имеет длину два байта. Новая команда типа 0 использует один из четырех специальных кодов операции перехода, называемых трехбайтовым кодами операции перехода. Трехбайтовые коды операции перехода имеют длину два байта и указывают аппаратным средствам декодера, что команда использует третий байт в поле 220 кода операции для определения команды. Поле 118с трехбайтового кода операции перехода может располагаться в любом месте в пределах кода операции команды и, необязательно, должно быть полем высшего порядка или низшего порядка в составе команды.

По меньшей мере в одном варианте осуществления четыре новых значения трехбайтового кода операции перехода определены как 0x0F3y, где у есть 0х8, 0х9, 0хА или 0хВ. Для команды 226 значение в специфическом для команды поле 225 кода операции поля 220 кода операции должно быть декодировано как новая команда.

Примеры префиксов команд и кодов операций

Как второй тип 224 расширенной команды и второй тип 228 новой команды (иногда называемой «типом 1 новой команды») используют значение в поле 210 префикса в качестве части кода операции. В отличие от регулярной инструкции со спецификатором, 214, где префикс просто определяет последующий код операции, второй тип 224 расширенной команды и тип 1 228 новой команды используют префикс для определения полностью новой команды.

Префиксы команд были первоначально разработаны для усовершенствования набора команд. Например, префикс «повторить» предназначен для повторения стоковой команды. Кодами префикса «повторить» являются 0xF3 (REP, REPE) и 0xF2 (REPNE). Префикс, используемый как таковой, не определяет новый смысл для кода операции, которая следует далее. Он просто определяет дополнительные операционные условия для кода операции.

Коды операции перехода обеспечивают расширение для набора команд. Например, коды операции от 0xD8 до 0xDF используются для индикации того, что второй байт 217 кода операции содержит значение, определяющее команду для блока с плавающей запятой. Декодер пропускает код операции к декодеру с плавающей запятой.

По меньшей мере, в одном варианте осуществления расширенного набора команд, как описано здесь, 3-байтовый код операции перехода представляет собой двухбайтовый объект, имеющий значение 0x0F3y, где у есть 0Х8, 0х9, 0хА или 0хВ. Значение 3-байтового кода операции перехода в поле 118с 3-байтового кода операции перехода показывает декодеру, что специфическое для команды значение кода операции в третьем байте 225 поля 200 кода операции указывает на команду в наборе новых команд.

В противоположность 2-байтовому коду операции перехода, описанному выше в связи с первым типом 222 расширенной команды, значение поля 118с 3-байтового кода операции перехода указывает декодеру метод, который должен быть использован для определения длины определяемой команды типа 0. То есть каждое значение для 3-байтового кода операции перехода связано с конкретным методом, который должен быть использован для определения длины команды для каждой команды в карте, соответствующей конкретному 3-байтовому коду операции перехода. Например, значение 0x0F38 в поле 118с 3-байтового кода операции перехода ассоциировано с соответствующей картой кода операции. Длина для каждой команды в карте кода операции 0x0F38 может быть вычислена с использованием одного и того же метода определения длины, используемого для определения длины других команд в карте кода операции 0x0F38.

Аналогично, длина каждой команды соответствующих карт кода операции, ассоциированных с остальными значениями 3-байтового кода операции перехода (0x0F39, 0x0F3А, 0x0F3В), может быть вычислена с использованием той же самой логики определения длины, используемой для определения длины других команд в соответствующей карте кода операции.

Логика определения длины, используемая для определения длины команд, для каждой команды в одной из новых карт кода операции упрощена тем, что одинаковый набор входных членов оценивается для определения длины каждой команды в карте кода операции. Такая логика определения длины называется здесь как логика или метод «с фиксированным входом». То есть каждый входной член, оцениваемый для определения длины одной команды в карте, также релевантен для определения длины каждой другой команды в карте. Фиксированный набор членов, подлежащих оцениванию, может отличаться для различных карт кода операции. Хотя набор входных членов, подлежащих оцениванию, может отличаться для различных карт кода операции, входные члены, оцениваемые для определения длины команды, являются одними и теми же по всем командам в заданной карте 3-байтового кода операции.

Комбинация префикса и кода операции перехода обеспечивает значительное расширение таблицы кодов операций процессора, допуская создание новых наборов команд. Такая комбинация использует существующие коды префиксов для определения нового набора команд, в дополнение к набору команд, созданному кодами операций перехода. Используя существующие коды префиксов, схемы декодирования для существующего набора команд могут оставаться относительно неизменными для поддержки декодирования новых команд 118с (фиг.1).

Специфические для команд значения кодов операции (в третьем байте 225 поля 220 кода операции) для некоторых или всех новых команд могут быть теми же самыми, что и коды операции для существующих команд. За счет использования тех же самых кодов операции с префиксом и кодами операции перехода для определения нового набора команд, схемы декодирования могут быть менее сложными, чем при использовании полностью нового набора кодов операции для нового набора команд.

В одном варианте осуществления значение префикса 0Х66 используется для определения новых команд. Могут использоваться и другие префиксы. Кроме того, префиксы могут продолжать использоваться в традиционной роли усовершенствования кода операции или определения кода операции при некотором операционном условии.

В Таблице 1 ниже приведены примеры нового набора команд с использованием префиксов и трехбайтовых кодов операции перехода.

| Таблица 1 | ||

| Команда | (Префикс)/Код операции перехода/специфический для команды код операции(в шестнадцатеричн.) | Определение |

| PHADDW | 0F 38 01/r | Суммировать горизонтально упакованные числа из 64-бит. регистра или памяти в 64-бит. регистр |

| PHADDW | (66)0F 38 01/r | Суммировать горизонтально упакованные числа из 128-бит. регистра или памяти в 128-бит. регистр |

| PHADDD | 0F 38 02/r | Суммировать горизонтально упакованные числа из 64-бит. регистра или памяти в 64-бит. регистр |

| PHADDD | (66)0F 38 02/r | Суммировать горизонтально упакованные числа из 128-бит. регистра или памяти в 128-бит. регистр |

| PHADDSW | 0F 38 03/r | Суммировать горизонтально упакованные числа с насыщением из 64-бит. регистра или памяти в 64-бит. регистр |

| PHADDSW | (66)0F 38 03/r | Суммировать горизонтально упакованные числа с насыщением из 128-бит. регистра или памяти в 128-бит. регистр |

| PHSUBW | 0F 38 05/r | Вычитать горизонтально упакованные слова со знаком в 64-бит. регистре или памяти в 64-бит. регистр |

| PHSUBW | (66)0F 38 05/r | Вычитать горизонтально упакованные слова со знаком в 128-бит. регистре или памяти в 128-бит. регистр |

| PHSUBD | 0F 38 06/r | Вычитать горизонтально упакованные двойные слова со знаком в 64-бит. регистре или памяти в 64-бит. регистр |

| PHSUBD | (66)0F 38 06/r | Вычитать горизонтально упакованные двойные слова со знаком в 128-бит. регистре или памяти в 128-бит. регистр |

| PHSUBSW | 0F 38 07/r | Вычитать горизонтально упакованные слова со знаком в 64-бит. регистре или памяти в 64-бит. регистр как результат с насыщением |

| PHSUBSW | (66)0F 38 07/r | Вычитать горизонтально упакованные слова со знаком в 128-бит. регистре или памяти в 128-бит. регистр как результат с насыщением |

| PMADDUBSW | 0F 38 04/r | Умножить и суммировать упакованные числа со знаком и без знака в 64-битовом регистре или памяти в 64-битовый регистр |

| PMADDUBSW | (66)0F 38 04/r | Умножить и суммировать упакованные числа со знаком и без знака в 128-битовом регистре или памяти в 128-битовый регистр |

| PMULHRSW | 0F 38 0B/r | Упакованное умножение верхнего порядка с округлением и масштабированием из 64-бит. регистра или памяти в 64-бит. регистр |

| PMULHRSW | (66)0F 38 0B/r | Упакованное умножение верхнего порядка с округлением и масштабированием из 128-бит. регистра или памяти в 128-бит. регистр |

| PSHUFB | 0F 38 050/r | Упакованные перемешанные байты в 64-бит. регистре или памяти в 64-бит. регистр |

| PSHUFB | (66)0F 38 00/r | Упакованные перемешанные байты в 128-бит. регистре или памяти в 128-бит. регистр |

| PSIGNB | 0F 38 08/r | 64-бит.регистр или память упакованного знакового байта в 64-бит. регистр |

| PSIGNB | (66)0F 38 08/r | 128-бит.регистр или память упакованного знакового байта в 128-бит. регистр |

| PSIGNW | 0F 38 09/r | 64-бит.регистр или память упакованного знакового слова в 64-бит. регистр |

| PSIGNW | (66)0F 38 09/r | 128-бит.регистр или память упакованного знакового слова в 128-бит. регистр |

| PSIGND | 0F 38 0A/r | 64-бит.регистр или память упакованного знакового двойного слова в 64-бит. регистр |

| PSIGND | (66)0F 38 0A/r | 128-бит.регистр или память упакованного знакового двойного слова в 128-бит. регистр |

| PSRMRG | 0F 3A 0F/r | Упаковать со сдвигом вправо и объединить содержимое 64-бит. регистра или памяти в 64-бит.регистр |

| PSRMRG | (66)0F 3A 0F/r | Упаковать со сдвигом вправо и объединить содержимое 128-бит. регистра или памяти в 128-бит.регистр |

| PABSB | 0F 38 1C/r | Абсолютное значение упакованного байта для значения в 64-бит. регистре или памяти в 64-бит. регистр как результат без знака |

| PABSB | (66)0F 38 1C/r | Абсолютное значение упакованного байта для значения в 128-бит. регистре или памяти в 128-бит. регистр как результат без знака |

| PABSW | 0F 38 1D/r | Абсолютное значение упакованного слова для значения в 64-бит. регистре или памяти в 64-бит. регистр как результат без знака |

| PABSW | (66)0F 38 1D/r | Абсолютное значение упакованного слова для значения в 128-бит. регистре или памяти в 128-бит. регистр как результат без знака |

| PASBSD | 0F 38 1E/r | Абсолютное значение упакованного двойного слова для значения в 64-бит. регистре или памяти в 64-бит. регистр как результат без знака |

| PABSD | (66)0F 38 1E/r | Абсолютное значение упакованного двойного слова для значения в 128-бит. регистре или памяти в 128-бит. регистр как результат без знака |

В приведенных выше примерах команды с префиксом 0х66 относятся к командам, которые используют один или более регистров расширенного размера (такого как размер 128-битового регистра), в то время как команды без префикса 0х66 относятся к командам, которые используют один или более регистров меньшего размера (такого как размер 64-битового регистра). Регистры меньшего размера упоминаются здесь как регистры «регулярной длины». Как известно специалистам в данной области техники, точные коды для префиксов являются зависящими от реализации и описанное выше значение префикса 0х66 приведено только для иллюстрации.

Декодирование команд с использованием 3-байтовых кодов операции перехода

На фиг.3 приведена диаграмма, иллюстрирующая логику 300 для декодирования команд переменной длины. Логика 300 декодирования может включать в себя декодер 306 длины команды, блок 308 циклического сдвига команд, буфер 310 команд, детектор 320 префикса и перехода, схему 330 запуска декодера и декодер 340 кода операции. Детектор 320 префикса и перехода, схема 330 запуска декодера и декодер 340 кода операции образуют весь или часть блока 116 декодирования, показанного на фиг.1. Хотя детектор 320 префикса и кода перехода показан как единый блок, он может быть реализован как состоящий из отдельных блоков детектора перехода и детектора префикса.

Декодер 306 длины команды определяет длину текущего кода команды, выборка которой была произведена из внешней памяти (например, из памяти 102 на фиг.2). Для целей иллюстрации код команды предполагается включающим в себя до пяти байтов: первый байт соответствует от IN до IN+7, второй байт соответствует от IК до IК+7, третий байт соответствует от IL до IL+7, четвертый байт соответствует от IМ до IМ+7 и пятый байт соответствует от IР до IР+7, где IN до IN+7, IК до IК+7, IL до IL+7, IМ до IМ+7 и IР до IР+7 относятся к позициям битов кода команды. На практике, однако, текущая команда может включать в себя более чем пять байтов в своем коде команды. Аналогичным образом, текущая команда может включать в себя менее пяти байтов в своем коде команды.

По меньшей мере, в одном варианте осуществления пять проиллюстрированных байтов кода команды являются непрерывными, такими как K=N+8, L=K+8 и L=N+16 и M=L+8, M=K+16 и M=K+24 и т.д. Однако, как описано выше в связи с фиг.2, поля формата 200 не обязательно должны занимать показанные позиции. Соответственно, проиллюстрированные пять байтов кода команды, которые описаны здесь, могут иметь любой порядок и необязательно должны быть непрерывными.

Специалисту в данной области должно быть понятно, что логика декодера 306 длины команды может реализовывать довольно сложные методы декодирования длины в системе, которая поддерживает команды переменной длины. Это особенно справедливо для систем, которые требуют различных методов, которые оценивают различные входные входы, для определения длины команды для команд в той же самой карте кода операции. Как описано ниже, варианты осуществления настоящего изобретения обеспечивают упрощенную обработку декодирования длины за счет обеспечения того, что длина каждой команды в карте кода операции определяется посредством логики определения длины одиночного фиксированного входного члена.

Блок 308 циклического сдвига команд циклически сдвигает байты команды так, чтобы первый байт, подлежащий декодированию, был в начальном положении. Блок 308 циклического сдвига команд, таким образом, идентифицирует начало байтов команды, подлежащих декодированию. Следует отметить, что хотя блок 308 циклического сдвига команд может идентифицировать первый байт команды, такой как байт префикса, первый байт не обязательно должен быть идентифицирован. По меньшей мере, в одном варианте осуществления, например, блок 308 циклического сдвига команд идентифицирует наименее значимый байт кода операции и циклически сдвигает его в начальное положение команды. По меньшей мере, еще в одном варианте осуществления блок 308 циклического сдвига команд идентифицирует наиболее значимый байт кода операции и циклически сдвигает его в начальное положение команды.

Буфер 310 команды получает и сохраняет команды, которые были извлечены из внешней памяти. По меньшей мере, в одном варианте осуществления команды декодируются по длине и циклически сдвигаются, прежде чем поступят в буфер 310 команд. По меньшей мере, в одном варианте осуществления буфер 310 команд реализован как кэш команд.

Детектор 320 префикса и перехода получает биты команд от IN до IN+7, от IК до IК+7, от IL до IL+7 и обнаруживает присутствие одного или более из набора предварительно определенных префиксов и/или кодов операции перехода, используемых в качестве части нового набора команд. Значение префикса может быть выбрано так, что оно является тем же, что и префикс, используемый для регулярного набора команд. Схема 330 запуска декодера использует результаты детектора 320 префикса и перехода для генерации сигналов запуска или выбора для отдельного декодера кода операции. Декодер 440 кода операции получает биты команд от IN до IN+7, IК до IК+7, IМ до IМ+7, IL до IL+7 и IР до IР+7 и преобразует отдельные коды команд в декодированные коды команд, которые определяют желательную команду.

На фиг.4 показана блок-схема, иллюстрирующая, по меньшей мере, один вариант осуществления схемы 440 декодера для декодирования новой команды типа 0. Схема 440 декодера может быть реализована как часть детектора префикса и перехода, такого как детектор 320 префикса и перехода, показанный на фиг.3. В целях иллюстрации при описании фиг.4 предполагается, что блок циклического сдвига команд (308 на фиг.3) указывает первый байт кода операции команды.

На фиг.4 показано, что декодер 440 включает в себя схему «И» 450, которая определяет, согласуется ли первый байт команды, то есть биты от IN до IN+7, со значением 0х0F двухбайтового кода операции перехода. Сигнал ESC2 выдается, если биты от IN до IN+7 представляют значение 0х0F двухбайтового кода операции перехода.

Декодер 440 также включает в себя схемы «И» 402, 404, 406, 408. Схема «И» 402 согласует биты от IК до IК+7 команды со значением 0х38 трехбайтового кода операции перехода и генерирует сигнал ES38. Сигнал ES38 выдается, если биты от IK до IK+7 команды представляют значение 0х38 трехбайтового кода операции перехода.

Если биты от IN до IN+7 представляют значение 0х0F двухбайтового кода операции перехода и если биты от IK до IK+7 команды представляют значение 0х38 трехбайтового кода операции перехода, то команда представляет собой новую команду 226 типа 0. Если выданы оба сигнала ESC2 и ES38, то схема «И» 403 выдает оценку «истинно», запуская логику 412. Логика 412 выбирает, для декодирования значения в специфическом для команды поле 225 кода операции (фиг.2), карту трехбайтового кода операции для команд, имеющих значение 0х38 трехбайтового кода перехода.

Схема «И» 404 согласует биты от IК до IК+7 команды со значением 0х39 трехбайтового кода операции перехода и генерирует сигнал ES39. Сигнал ES39 выдается, если биты от IK до IK+7 команды представляют значение 0х39 трехбайтового кода операции перехода. Если биты от IN до IN+7 команды представляют значение 0х0F двухбайтового кода операции перехода и если биты от IK до IK+7 команды представляют значение 0х39 трехбайтового кода операции перехода, то команда представляет собой новую команду 226 типа 0. Если выданы оба сигнала ESC2 и ES39, то схема «И» 405 выдает оценку «истинно», запуская логику 414. Логика 414 выбирает для декодирования значения в специфическом для команды поле 225 кода операции (фиг.2) карту трехбайтового кода операции для команд, имеющих значение 0х39 трехбайтового кода перехода.

Схема «И» 406 согласует биты от IК до IК+7 команды со значением 0х3А трехбайтового кода операции перехода и генерирует сигнал ES3А. Сигнал ES3А выдается, если биты от IK до IK+7 команды представляют значение 0хА трехбайтового кода операции перехода. Если биты от IN до IN+7 команды представляют значение 0х0F двухбайтового кода операции перехода, и если биты от IK до IK+7 команды представляют значение 0х3А трехбайтового кода операции перехода, то команда представляет собой новую команду 226 типа 0. Если выданы оба сигнала ESC2 и ES3А, то схема «И» 405 выдает оценку «истинно», запуская логику 416. Логика 416 выбирает для декодирования значения в специфическом для команды поле 225 кода операции (