Способы и устройства для осуществления канала связи переменной разрядности

Иллюстрации

Показать всеИзобретение относится к системам обработки данных и может использоваться в схемах межсоединения. Технический результат состоит в обеспечении алгоритма для деления канала связи на один или более каналов связи уменьшенной разрядности. Для одного из вариантов осуществления изобретения схема мультиплексирования используется для осуществления порядка передачи битов, требуемого конкретным контролем с помощью циклического избыточного кода. Порядок мультиплексированных выходных битов затем изменяют на кристалле для уменьшения перегрузки маршрутизации на плате. 4 н. и 23 з.п. ф-лы, 8 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления данного изобретения относятся в общем случае к области систем обработки данных, использующих схему межсоединения, основывающуюся на канале связи, а более конкретно к способам и устройствам для осуществления логического разделения интерфейса единого канала связи на квадранты таким образом, что обеспечивается поддержка таких функциональных возможностей, как переменная разрядность канала связи, реверсирование сигнальных линий и раздвоение порта.

Предшествующий уровень техники

В целях преодоления недостатков основывающихся на шинах схем межсоединения для мультипроцессорных систем (МПС) были разработаны двухточечные основывающиеся на канале связи схемы межсоединения. Каждый узел такой системы включает в себя абонента (например, процессор, контроллер памяти, компонент-концентратор ввода/вывода (I/O), наборы микросхем и т.д.) и маршрутизатор для передачи данных между соединенными узлами. Абоненты таких систем обмениваются данными через использование иерархической структуры межсоединения, что обычно включает в себя уровень протокола, необязательный уровень маршрутизации, канальный уровень и физический уровень.

Уровень протокола задает формат пакета передачи в соответствии с протоколом (ППП, PTP), который определяет модуль данных, передаваемый между узлами. Уровень маршрутизации определяет путь, по которому данные передаются между узлами. Канальный уровень принимает пакеты ППП от уровня протокола и передает их в виде последовательности блоков (частей). Размер каждой части определяется канальным уровнем и представляет часть ППП, перемещение которой должно быть синхронизировано, поэтому каждая часть известна как модуль управления потоком данных (МУПД, флит). ППП состоит из целого и переменного количества модулей МУПД. Физический уровень состоит из фактически существующей в каждом узле электроники и средств передачи сигналов. В двухточечных основывающихся на канале связи схемах межсоединения существуют только два абонента, подсоединенных к каждому каналу связи. Эта ограниченная нагрузка на электронику приводит к повышенному быстродействию. Быстродействие может дополнительно увеличиваться с помощью сокращения разрядности интерфейса физического уровня (ИФУ, PLI), и таким образом, дрожания синхроимпульсов. Поэтому ИФУ обычно предназначен для передачи некоторой части МУПД в каждом из нескольких тактовых циклов. Та часть МУПД, которая может передаваться по физическому интерфейсу за один тактовый цикл, известна как разряд управления физического уровня (РУФ, phit). В то время как модули МУПД представляют логические блоки данных, РУФ соответствует физическому количеству данных.

Иерархическую структуру межсоединения реализуют для достижения большего быстродействия системы на физическом уровне. Канальный уровень передает данные (принятые как ППП от уровня протокола) в виде модулей МУПД, которые затем разбивают на разряды РУФ на физическом уровне и передают через ИФУ на физический уровень принимающего абонента. Принятые РУФ объединяют в модули МУПД на физическом уровне принимающего абонента и направляют на канальный уровень принимающего абонента, на котором объединяют модули МУПД в пакеты ППП и направляют ППП на уровень протокола принимающего абонента.

Этот способ передачи данных по каналу связи приводит к нескольким трудностям в реализации канала связи переменной разрядности (например, канала связи уменьшенной разрядности).

Обычные схемы межсоединения предшествующего уровня техники (например, PCI Express) используют пакеты данных. Передающий абонент (Tx) передает один байт пакета данных в каждой сигнальной линии канала связи в течение каждого тактового цикла. Пакет имеет индикаторы «начало пакета» (НП, SOP) и «конец пакета» (КП, EOP). Во время инициализации принимающий абонент (Rx) использует обучающую последовательность для определения количества доступных сигнальных линий. Rx последовательно берет один байт из каждой доступной сигнальной линии и компонует байты до тех пор, пока не будет принят индикатор КП.

Эта схема, упоминаемая как «режим последовательной передачи байтов по сигнальным линиям», позволяет сократить канал связи до произвольного количества сигнальных линий. Однако реализация такой схемы в двухточечном основывающемся на канале связи ИФУ, предназначенном для передачи некоторой части МУПД в каждом из нескольких тактовых циклов, может привести к недопустимому времени ожидания. Например, такая система может использовать 80-битный МУПД и передавать этот МУПД по полноразрядному каналу связи, включающему 20 сигнальных линий, за четыре тактовых цикла. То есть, один бит передают по каждой из этих 20 сигнальных линий в течение каждого тактового цикла. Для такой системы, если байт должен передаваться последовательно по каждой из этих 20 сигнальных линий, требуется 8 тактовых циклов для передачи 160 битов, что будет эквивалентно увеличению размера МУПД. То есть, один 80-битный МУПД не может быть переслан до тех пор, пока все 160 битов не достигнут Rx. Это добавленное время ожидания может быть недопустимо для таких систем. Кроме того, для таких систем также не требуется включение индикаторов НП и КП, а они должны добавляться для реализации схемы режима последовательной передачи байтов по сигнальным линиям.

Дополнительное рассмотрение касается разработки способа реализации канала связи уменьшенной разрядности, который обеспечивает другие функциональные возможности, поддерживаемые ИФУ.

Перечень фигур чертежей

Данное изобретение может быть лучше всего понято на основе последующего описания и сопроводительных чертежей, которые используются для иллюстрации вариантов осуществления изобретения. На чертежах:

фиг.1 - формат МУПД и расположение восьми битов CRC в пределах 80-битного МУПД, разделенного на четыре блока в соответствии с одним из вариантов осуществления изобретения;

фиг.1A - формат МУПД для 80-битного МУПД на фиг.1, разделенного на четыре РУФ: РУФ0-РУФ3, для передачи по каналу связи полной разрядности в соответствии с одним из вариантов осуществления изобретения;

фиг.2 - формат МУПД для 80-битного МУПД, разделенного на восемь РУФ, для передачи по каналу связи половинной разрядности в соответствии с одним из вариантов осуществления изобретения;

фиг.3 - формат МУПД для 80-битного МУПД, разделенного на шестнадцать РУФ, для передачи по каналу связи четвертной разрядности в соответствии с одним из вариантов осуществления изобретения;

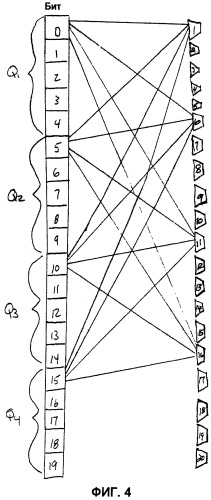

фиг.4 - перегрузка маршрутизации на кристалле и переменная задержка, характерные для схемы прямой маршрутизации, обеспечивающей каналы связи переменной разрядности, в соответствии с одним из вариантов осуществления изобретения;

фиг.5 - входная схема мультиплексора для осуществления требуемого порядка передачи РУФ и битов в соответствии с одним из вариантов осуществления изобретения;

фиг.6 - компоновка платы для системы, реализующей мультиплексирование полубайтов для осуществления требуемого порядка передачи битов при поддержке разветвляющегося порта, в соответствии с одним из вариантов осуществления изобретения; и

фиг.7 - реализация схемы изменения порядка битов в соответствии с одним из вариантов осуществления изобретения.

Подробное описание

В последующем описании сформулированы многочисленные конкретные подробности. Однако следует понимать, что варианты осуществления изобретения могут использоваться без этих конкретных подробностей. В других случаях известные схемы, структуры и методики не раскрыты подробно для того, чтобы не затенить понимание этого описания.

Ссылки по всему описанию к «одному из вариантов осуществления» или «варианту осуществления» означают, что конкретную функциональную возможность, структуру или характеристику, описанную в связи с данным вариантом осуществления, включает в себя по меньшей мере один из вариантов осуществления настоящего изобретения. Таким образом, появление фраз «в одном из вариантов осуществления» или «в варианте осуществления» в различных местах по всему описанию не обязательно относится все время к одному и тому же варианту осуществления. Кроме того, конкретные функциональные возможности, структуры или характеристики могут объединяться любым подходящим образом в одном или большем количестве вариантов осуществления.

Кроме того, аспекты изобретения заключаются не во всех признаках одного раскрытого варианта осуществления. Таким образом, формула изобретения, следующая за подробным описанием, непосредственно содержится в этом подробном описании, причем каждый пункт формулы изобретения фигурирует, как отдельный вариант осуществления этого изобретения.

Формат МУПД

Один из вариантов осуществления изобретения обеспечивает ИФУ, имеющий канал связи, содержащий 20 сигнальных линий (при полной разрядности), который передает 80-битный МУПД в качестве четырех 20-битных РУФ. Для одного из вариантов осуществления изобретения эти 20 сигнальных линий делят на квадранты по пять сигнальных линий в каждом. Для такого варианта осуществления канал связи уменьшенной разрядности может состоять из любой комбинации двух квадрантов для канала связи половинной разрядности или из любого из квадрантов для канала связи четвертной разрядности. Т.е. такой вариант осуществления не поддерживает произвольную разрядность канала связи, а только полную разрядность (20 сигнальных линий), половинную разрядность (10 сигнальных линий) и четвертную разрядность (5 сигнальных линий). При полной разрядности канал связи передает 80-битный МУПД как четыре 20-битных РУФ за четыре тактовых цикла; при половинной разрядности канал связи передает 80-битный МУПД как восемь 10-битных РУФ за восемь тактовых циклов; и при четвертной разрядности канал связи передает 80-битный МУПД как шестнадцать 5-битных РУФ за шестнадцать тактовых циклов.

80-битный МУПД содержит несколько (например, восемь) битов обнаружения ошибки для осуществления контроля с помощью циклического избыточного кода (CRC). CRC - это способ обнаружения ошибок в данных, которые были переданы по каналу связи. Как правило, Tx применяет полином к блоку данных и добавляет результирующий код CRC в конец блока. Rx применяет тот же самый полином и сравнивает результат применения с добавленным в конец результатом. Если они совпадают, то данные были приняты успешно, в противном случае Tx уведомляют, чтобы он повторно передал данные.

Биты CRC МУПД должны передаваться в определенном порядке, основанном на математике, используемой для реализации CRC. Для одного из вариантов осуществления передача РУФ и битов в пределах каждого РУФ должна выполняться в определенном порядке для эффективного использования возможности обнаружения пакета ошибок CRC канального уровня. Порядок передачи зависит от разрядности используемого канала связи. Фиг.1 показывает формат МУПД и расположение восьми битов CRC в пределах 80-битного МУПД, разделенного на четыре блока в соответствии с одним из вариантов осуществления изобретения. Как показано на фиг.1, иллюстрируемый МУПД содержит четыре 20-битных блока: блоки 0-3 с восьмью битами CRC: битами C0-C8. Для генерации CRC биты CRC передают в определенном порядке. Биты CRC C0 и C4 включены в блок 0, C1 и C5 включены в блок 1, C2 и C6 включены в блок 2, и C3 и C7 включены в блок 3.

Фиг.1A показывает формат 80-битного МУПД по фиг.1, разделенного на четыре РУФ: РУФ0-РУФ3, для передачи в канале связи полной разрядности в соответствии с одним из вариантов осуществления изобретения. Как показано на фиг.1, для канала связи полной разрядности, имеющего 20 сигнальных линий, каждый блок МУПД соответствует РУФ. Фиг.1A представляет каждый бит как упорядоченную пару <q, o>, где «q» определяет квадрант, которому принадлежит данный бит, и «o» определяет смещение бита в пределах квадранта. Как показано на фиг.1A, восемь битов CRC содержатся в столбцах (позициях битов) 0 и 1 каждого из четырех РУФ, РУФ0-РУФ3.

Канал связи половинной разрядности передает 80-битный МУПД как восемь 10-битных МУПД за восемь тактовых циклов, используя любую комбинацию двух квадрантов. Восемь РУФ не состоят просто из первой и второй половин каждого из четырех блоков МУПД. Для выполнения требований алгоритма CRC формат МУПД для канала связи половинной разрядности чередует биты МУПД так, чтобы восемь битов CRC находились в первой позиции бита каждого из восьми РУФ. Фиг.2 показывает формат МУПД для 80-битного МУПД, разделенного на восемь РУФ, для передачи в канале связи половинной разрядности в соответствии с одним из вариантов осуществления изобретения. Как показано на фиг.2, первый из восьми РУФ, а именно РУФ0 состоит из чередующихся битов первого блока МУПД; второй из восьми РУФ, а именно РУФ1 состоит из чередующихся битов второго блока; третий из восьми РУФ, а именно РУФ2 состоит из оставшихся чередующихся битов первого блока (не включенных в РУФ0) и т.д. То есть РУФ0 содержит четные столбцы блока 0, и РУФ1 содержит четные столбцы блока 1. Следующие два РУФ, а именно РУФ2 и РУФ3 содержат нечетные столбцы блока 0 и блока 1, соответственно. Таким образом, РУФ0-РУФ3 используются для полной передачи блока 0 и блока 1. Затем используются РУФ4-РУФ7 для передачи блока 2 и блока 3 с помощью повторения процесса. Такое упорядочение позволяет располагать восемь битов CRC в первую позицию бита каждого из восьми РУФ, как показано.

Для канала связи половинной разрядности используются только два из четырех квадрантов сигнальных линий. Эти два используемых квадранта могут быть любой комбинацией <x, y> четырех квадрантов, как показано на фиг.2. Для одного из вариантов осуществления изобретения квадрант с меньшим значением «q» из двух выбранных квадрантов передает бит с меньшим номером столбца (позицией бита в пределах РУФ). Например, для формата МУПД, показанного на фиг.2, y > x.

Канал связи четвертной разрядности передает 80-битный МУПД как шестнадцать 5-битных РУФ за шестнадцать тактовых циклов, используя любой из квадрантов сигнальных линий. Опять же биты в пределах МУПД нужно упорядочить определенным образом для удовлетворения требованиям CRC. Фиг.3 показывает формат МУПД для 80-битного МУПД, разделенного на шестнадцать РУФ, для передачи в канале связи четвертной разрядности в соответствии с одним из вариантов осуществления изобретения. Как показано на фиг.3, восемь битов CRC находятся в первой позиции бита чередующихся пар РУФ. Шестнадцать РУФ формируют посредством процесса, подобного описанному выше со ссылкой на фиг.2. То есть РУФ0 состоит из 5 битов блока 0, начиная со столбца 0, и включает в себя каждый четвертый бит. РУФ1 содержит 5 битов блока 1, начиная со столбца 0, и включает в себя каждый четвертый бит. РУФ2-РУФ7 чередуют биты блока 0 и блока 1, которые содержат по пять битов на блок, выбирая каждый четвертый бит, начиная со столбцов 2, 1 и 3, в таком конкретном порядке. Таким образом, РУФ0-РУФ7 используются для полной передачи блока 0 и блока 1. Затем используются РУФ8-РУФ15 для передачи блока 2 и блока 3 с помощью повторения процесса.

Мультиплексирование полубайтов

Прямая маршрутизация битов в порядке, требуемом для CRC, привела бы к большим длинам трасс, что вызвало бы перегрузку маршрутизации и переменную задержку. Фиг.4 показывает перегрузку маршрутизации на кристалле и переменную задержку, характерные для схемы прямой маршрутизации, обеспечивающей каналы связи переменной разрядности в соответствии с одним из вариантов осуществления изобретения. Как показано на фиг.4, биты 20 сигнальных линий разделены на квадранты по пять сигнальных линий в каждом. Один бит из каждого из квадрантов Q1-Q4 направляют к четырем из 20 мультиплексоров МП1-МП20. Например, как показано на фиг.4, каждый из битов 0, 5, 10 и 15 (первый бит каждого квадранта) направляют к каждому из мультиплексоров 1, 6, 11 и 16. Эту комбинацию продолжают для каждого из битов 1, 6, 11 и 16 (второй бит каждого квадранта), направляя их к каждому из мультиплексоров 2, 7, 12 и 17 и т.д. Каждый из мультиплексоров принимает четыре входных бита и обеспечивает выходную информацию, основываясь на разрядности канала связи, т.е. для канала связи полной разрядности (20 битов), каждый из 20 мультиплексоров обеспечивает вывод информации, причем МП1 обеспечивает вывод бита 0 и т.д. Для канала связи половинной разрядности только 10 из 20 мультиплексоров обеспечивают вывод информации в тактовом цикле для полного вывода 10 битов за тактовый цикл. Например, МП1 может обеспечивать вывод битов 0 и 10 в каждом из двух последовательных тактовых циклов, соответственно, и МП6 может обеспечивать вывод битов 5 и 15 в каждом из двух последовательных тактовых циклов, соответственно, когда используются квадранты Q1 и Q2. Когда используются квадранты Q3 и Q4, МП11 может обеспечивать вывод битов 0 и 10 в каждом из двух последовательных тактовых циклов соответственно, и МП16 может обеспечивать вывод битов 5 и 15 в каждом из двух последовательных тактовых циклов, соответственно. Для канала связи четвертной разрядности только 5 из 20 мультиплексоров обеспечивают вывод информации в тактовом цикле для полного вывода 5 битов за тактовый цикл. Например, МП1 может обеспечивать вывод битов 0, 5, 10 и 15 в каждом из четырех последовательных тактовых циклов, соответственно (когда используется квадрант Q1).

Сравнение длин трасс в соответствии с такой схемой показывает переменную задержку. Такая изменчивость в длине трассы может потребовать буферизацию.

Для осуществления порядка передачи битов, требуемого для CRC, и избегая при этом вышеупомянутых недостатков, интегрированный мультиплексор (МП) обеспечивают для каждой сигнальной линий ИФУ в соответствии с одним из вариантов осуществления изобретения. Для ИФУ с 20 сигнальными линиями интегрируют 20 мультиплексоров.

Фиг.5 показывает входную схему мультиплексора для осуществления требуемого порядка передачи РУФ и битов в соответствии с одним из вариантов осуществления изобретения. Входная схема 500 мультиплексора делит 20-битный блок на пять полубайтов, полубайт 0 - полубайт 4, состоящих из четырех битов каждый. Схема мультиплексирования для решения проблемы ограничения порядка передачи, наложенного CRC, обсуждается для полубайта 0.

Для канала связи полной разрядности выбор входа мультиплексора является прямым; 20 мультиплексоров реализованы для каждого из четных и нечетных блоков. Для канала связи полной разрядности каждый из 20 мультиплексоров (один мультиплексор связан с каждым входом) является активным, и каждый мультиплексор принимает соответствующие ему входные данные по полубайтно. Как показано на фиг.5, каждый из битов полубайта 0, а именно биты 0-3 вводят в четыре соответствующие мультиплексора МП0-МП3. Эти биты имеют смещение 0 в каждом квадранте. Все полубайты блока 0, как показано с помощью полубайта 0 блока 0, передаются как РУФ0, и все полубайты блока 1 (показано с помощью полубайта 0 блока 0) передаются как РУФ1. Передача блоков чередуется через мультиплексор 510 блоков.

Операцию повторяют для блоков 2 и 3 для следующих двух РУФ.

Для канала связи половинной разрядности используются два квадранта, обозначенные Qy и Qx, и поэтому только два из четырех мультиплексоров, связанных с каждым полубайтом, используются для общего количества десять активных мультиплексоров. Полубайт 0 блока 0 и блока 1 передают в первых четырех из восьми РУФ, используя биты <x, 0> и <y, 0>. В РУФ 0 Qx и Qy передают биты 0 и 2 блока 0 (а также биты 4, 8, 12 и 16 и биты 6, 10, 14 и 18), соответственно. В РУФ1 Qx и Qy переключаются к блоку 1 и передают биты 0 и 2 (а также биты 4, 8, 12 и 16 и биты 6, 10, 14 и 18), соответственно. Эту операцию повторяют для битов 1 и 3 (а также для битов 5, 9, 13 и 17 и битов 7, 11, 15 и 19) блока 0 и блока 1 для общего количества четыре РУФ. Следующие четыре РУФ повторяют операцию для блоков 2 и 3.

Как отмечено выше, для пары квадрантов Qy и Qx значение x меньше, чем y. Например, если квадранты 1 и 0 используются для формирования канала связи половинной разрядности, то квадрант 0 передает биты 0 и 1 каждого блока в последовательных РУФ, а квадрант 1 передает биты 2 и 3 в последовательных РУФ. С другой стороны, если используются квадранты 1 и 2, то квадрант 1 передает биты 0 и 1 каждого блока в последовательных РУФ, а квадрант 2 передает биты 2 и 3 в последовательных РУФ.

Для канала связи четвертной разрядности используется один из квадрантов Qx, и поэтому используется только один из мультиплексоров, связанных с каждым полубайтом, для общего количества пять активных мультиплексоров. Полубайт 0 блока 0 и блока 1 передают в первых восьми из шестнадцати РУФ, используя <x, 0>. Бит 0 блока 0 (а также биты 4, 8, 12 и 16) передают в РУФ0, и бит 0 блока 1 (а также биты 4, 8, 12 и 16) передают в РУФ1. Операцию повторяют три раза, используя биты 2, 1 и 3 полубайта 0 (и соответствующие биты каждого другого полубайта), соответственно, для каждой итерации при чередовании блоков 0 и 1 для общего количества восемь РУФ для этих двух блоков. Операцию повторяют для блоков 2 и 3, используя следующие восемь РУФ.

После передачи принятые биты демультиплексируют в порте Rx, используя схему, которая осуществляет обратную схему относительно описанной схемы мультиплексирования и обеспечивает демультиплексирование битов и РУФ.

Изменение порядка

Вариант осуществления изобретения, который осуществляет мультиплексирование полубайтов, как описано выше, уменьшает перегрузку маршрутизации на кристалле и переменную длину канала связи, обеспечивая мультиплексоры, которые тщательно расположены на кристалле относительно связанных с ними входов. Поддержание требуемого порядка передачи для РУФ и битов в пределах каждого РУФ может привести к относительным трудностям, потому что при работе канала связи уменьшенной разрядности (или канала связи половинной разрядности, или канала связи четвертной разрядности для одного из вариантов осуществления изобретения) РУФ не передают по каналу связи по смежным физическим сигнальным линиям. Т.е. реализация схемы мультиплексирования полубайтов направляет выход каждого из четырех мультиплексоров, соответствующих данному полубайту, в различные квадранты. Это может быть проблематичным в системе, которая поддерживает различные функциональные возможности.

Например, рассмотрим поддерживаемую функциональную возможность раздвоения порта. Раздвоение порта позволяет разделить абонент полной разрядности на два абонента, каждый с каналом связи половинной разрядности. Например, для некоторых системных платформ трафик ввода/вывода не настолько большой, как трафик между процессорами. Поэтому для системы с двумя процессорами вместо того, чтобы каждый процессор имел свой собственный специализированный компонент ввода/вывода, возможно, чтобы эти два процессора совместно использовали один компонент ввода/вывода в контексте межсоединения. В таком случае эти два процессора связываются друг с другом, используя межсоединение с разрядностью 20 битов (20 сигнальных линий), но абонент ввода/вывода выделяет 10 из своих 20 сигнальных линий для связи с одним процессором, а другие 10 сигнальных линий - для связи с другим процессором. Для одного из вариантов осуществления изобретения раздвоение порта осуществляется посредством перемычек штыревых выводов до инициализации канала связи, и конфигурация остается статической. Для одного из вариантов осуществления изобретения раздвоенный порт имеет две сигнальные линии синхроимпульсов (по одной для каждого канала связи половинной разрядности) в центре поля штыревых выводов. Для одного из вариантов осуществления изобретения порт, выполненный с возможностью раздвоения, также выполнен с возможностью работы в качестве одного канала связи полной разрядности. Для такого варианта осуществления дополнительный штыревой вывод синхроимпульсов может быть не отсоединен или может быть фиксировано присоединен или к Vcc, или к Vss.

Фиг.6 показывает схему компоновки платы для системы, которая реализует мультиплексирование полубайтов для осуществления требуемого порядка передачи битов при поддержке раздвоенного порта в соответствии с одним из вариантов осуществления изобретения. Система 600, показанная на фиг.6, включает в себя абонент 605 Tx, который осуществляет требуемый порядок передачи, являющийся результатом мультиплексирования полубайтов, как описано выше со ссылкой на фиг.5. Как показано, абонент 605 имеет раздвоенный порт. Система 600 также включает в себя два абонента 610A и 610B, каждый из них имеет порт половинной разрядности. Из 20 сигнальных линий, доступных каждому из абонентов 610A и 610B, половина неактивна. Для абонента 610A порт половинной разрядности использует сигнальные линии 0-9, в то время как для абонента 610B порт половинной разрядности использует сигнальные линии 10-19. Как показано на фиг.6, квадранты 0 и 1 абонента 605 направлены к абоненту 610A, в то время как квадранты 2 и 3 направлены к абоненту 610B. Такая компоновка привела бы к чрезмерному скрещиванию проводников на плате, как показано на фиг.6, или альтернативно, потребовала бы дополнительные уровни маршрутизации, причем и то, и другое нежелательно.

Чтобы справиться с этой ситуацией, для одного из вариантов осуществления изобретения между внутренними логическими средствами и физическими сигнальными линиями реализуют уровень изменения порядка битов.

Фиг.7 показывает реализацию схемы изменения порядка битов в соответствии с одним из вариантов осуществления изобретения. Система 700, показанная на фиг.7, включает в себя абонента 705, имеющего схему изменения порядка битов, реализованную между внутренними логическими средствами и физическими штыревыми выводами 706. Изменение порядка битов приводит к тому, что квадранты имеют все биты, передаваемые по смежным физическим сигнальным линиям. Для одного из вариантов осуществления изобретения изменение порядка битов реализуют через фиксированную разводку на кристалле, и поэтому не требуется дополнительных логических средств. Как показано на фиг.7, для одного из вариантов осуществления изобретения бит, представляющий использование упорядоченной пары <q, o>, отображают на физическую сигнальную линию «n», используя следующее уравнение изменения порядка.

| Сигнальная линия n = (NL/4) * (1 + q) - o -1 | для q < 2 |

| = (NL/4) * (5 - q) + o | для q >= 2 |

где, 'n' - номер сигнальной линии (от 0 до NL - 1), 'NL' - количество сигнальных линий для канала связи полной разрядности (например, 20 маршрутов), 'q' - номер квадранта (от 0 до 3), и 'о' - смещение бита (от 0 до 4) в пределах квадранта 'q'. С помощью изменения порядка битов внутренним образом, заставляя таким образом все биты квадранта передаваться по смежным физическим сигнальным линиям, смягчают перегрузку маршрутизации на плате для раздвоенного порта. Порт абонента 705 может быть раздвоен, как показано, причем квадранты 0 и 1 направлены к порту половинной разрядности абонента 710A, а квадранты 2 и 3 направлены к порту половинной разрядности абонента 710. Порядок квадрантов после реализации описанной схемы изменения порядка не является последовательным на физических штыревых выводах 706, но соединение с абонентами 710A и 710B может быть сделано напрямую без дополнительных уровней маршрутизации.

Общие вопросы

Варианты осуществления изобретения обеспечивают алгоритм для деления канала связи на один или более каналов связи уменьшенной разрядности. Хотя описанное выше относится к ИФУ, который имеет канал связи полной разрядности из 20 линий связи, МУПД размером 80 бит и каналы связи уменьшенной разрядности половинной разрядности и четвертной разрядности, альтернативные варианты осуществления изобретения одинаково применимы к интерфейсам ИФУ, которые имеют отличающиеся размеры каналов связи, МУПД и обеспечивают разнообразные каналы связи уменьшенной разрядности.

Для одного из вариантов осуществления тщательное расположение мультиплексоров, которое следует из процесса мультиплексирования полубайтов, описанного выше со ссылкой на фиг.5, уменьшает перегрузку на кристалле в сильно перегруженной области кристалла. Изменение порядка битов, описанное выше со ссылкой на фиг.6, увеличивает перегрузку на кристалле (в менее перегруженной области, где увеличенную перегрузку можно допустить), но уменьшает перегрузку на плате, позволяя системе лучше поддерживать функциональные возможности раздвоения порта и реверсирования сигнальных линий.

Реверсирование сигнальных линий

Реализация схемы мультиплексирования и изменения порядка, как описано выше, обеспечивает дополнительные преимущества в отношении реверсирования сигнальных линий.

В идеале штыревые выводы, подающие физические сигналы на каждый из двух соединенных между собой абонентов, соединены с соответствующими штыревыми выводами на другом абоненте. То есть, для пары абонентов с 20 штыревыми выводами штыревые выводы 0-19 одного абонента соединены со штыревыми выводами 0-19 другого абонента. Такое соединение может привести к чрезмерной перегрузке компоновки платы или сложности для некоторой топологии. Вариант осуществления изобретения позволяет располагать штыревые выводы одного порта в обратном порядке относительно штыревых выводов другого порта. Такое реверсирование сигнальных линий задается с помощью следующего уравнения соединения штыревых выводов между двумя портами A и B.

Штыревой вывод kкомпонент А=>штыревой вывод (NL-k-1)компонент B

Реверсирование сигнальных линий автоматически обнаруживается и компенсируется с помощью порта Rx. Никакие дополнительные этапы не требуются на плате, пока абоненты соединены через соответствующие штыревые выводы (прямое соединение) или через указанное выше уравнение соединения штыревых выводов при реверсировании сигнальных линий.

Для одного из вариантов осуществления изобретения, в котором функциональная возможность реверсирования сигнальных линий поддерживается вместе с раздвоением порта, сигнальные линии 0-9 раздвоенного порта с 20 сигнальными линиями соединены с сигнальными линиями 19-10 (в таком конкретном порядке) первого порта половинной разрядности, в то время как сигнальные линии 10-19 раздвоенного порта с 20 сигнальными линиями соединены с сигнальными линиями 9-0 (в таком конкретном порядке) второго порта половинной разрядности.

Для одного из вариантов осуществления изобретения, который использует описанную выше схему мультиплексирования и изменения порядка, идентификатор сигнальной линии для каждой сигнальной линии прямого соединения отличается только одним битом от идентификатора сигнальной линии соединения с обращенными сигнальными линиями. Т.е. так как сигнальные линии ограничены только одним из двух расположений, их идентификаторы могут быть одинаковыми, за исключением одного бита. В таком варианте осуществления реверсирование сигнальных линий может быть обнаружено с помощью сравнения этого одного бита. Это экономит время и место на кристалле, поскольку реверсирование сигнальных линий может быть указано с помощью ссылки на один бит идентификатора сигнальной линии, таким образом требуется реализация только однобитового компаратора на кристалле для поддержания реверсирования сигнальных линий. Напротив, схемы предшествующего уровня техники требовали сравнения всех пяти битов идентификатора сигнальной линии, и таким образом требовался компаратор на пять битов.

Варианты осуществления изобретения обеспечивают процесс мультиплексирования и изменения порядка для осуществления требуемого порядка передачи битов и содействия созданию канала связи уменьшенной разрядности при поддержке других необходимых функциональных возможностей. Эти процессы включают в себя различные операции и они описаны в своей самой основной форме, но эти операции можно добавить или удалить из любого из этих процессов, не отступая от основного объема изобретения. Операции различных вариантов осуществления изобретения могут осуществляться посредством аппаратных компонентов или могут быть воплощены в машиноисполняемых командах, как описано выше. Альтернативно, они могут выполняться с помощью комбинации аппаратных средств и программного обеспечения. Вариант осуществления изобретения может обеспечиваться в качестве компьютерного программного продукта, который может включать в себя машиночитаемый носитель, хранящий инструкции, которые могут использоваться для программирования компьютера (или других электронных устройств) для выполнения процесса согласно изобретению, как описано выше.

Машиночитаемый носитель включает в себя любое средство, которое обеспечивает (т.е. хранит и/или передает) информацию в форме, доступной машине (например, компьютеру, сетевому устройству, персональному цифровому информационному устройству, производственному прибору, любому устройству с набором из одного или более процессоров и т.д.). Например, машиночитаемый носитель включает в себя записываемый/незаписываемый носитель (например, постоянное запоминающее устройство (ПЗУ)); оперативное запоминающее устройство (ОП); запоминающее устройство в виде магнитного диска; оптические носители данных; устройства флэш-памяти; и т.д.), а также электрические, оптические, акустические или другой формы распространяющиеся сигналы (например, несущие волны, инфракрасные сигналы, цифровые сигналы и т.д.); и т.д.

Хотя данное изобретение было описано на основе нескольких вариантов осуществления, специалисты должны признать, что данное изобретение не ограничено описанными вариантами осуществления, а может быть реализовано на практике с модификацией и изменениями в пределах объема и сущности, определяемых прилагаемой формулой изобретения. Таким образом данное описание следует рассматривать как пояснительное, а не как ограничительное.

1. Способ мультиплексирования битов, содержащий этапы, на которых делят биты модуля управления потоком данных (МУПД) на группы, причем каждая группа имеет равное количество битов, и мультиплексируют биты каждой группы независимо для осуществления требуемого порядка передачи с помощью ввода каждого бита группы в один или более соответствующих мультиплексоров, и делят сигнальные линии передачи на некоторое количество разделов сигнальных линий передачи так, чтобы мультиплексированные биты из каждой группы формировали разряд управления физического уровня (РУФ), имеющий количество битов, соответствующее количеству сигнальных линий передачи в каждом разделе сигнальных линий передачи.

2. Способ по п.1, в котором каждый из упомянутых одного или более соответствующих мультиплексоров связан с разделом сигнальных линий, отличающимся от других разделов сигнальных линий передачи.

3. Способ по п.1, в котором каждая группа имеет четыре бита.

4. Способ по п.2, в котором каждый раздел сигнальных линий передачи представляет собой квадрант сигнальных линий передачи.

5. Способ по п.4, в котором каждый квадрант сигнальных линий передачи имеет пять сигнальных линий передачи.

6. Способ по п.5, в котором порядок мультиплексированных битов изменяют так, чтобы каждый выходной бит передавался из смежной физической сигнальной линии передачи.

7. Способ по п.1, в котором требуемый порядок передачи обеспечивает конкретный контроль с помощью циклического избыточного кода.

8. Система, предназначенная для обеспечения канала связи переменной разрядности, содержащая устройство деления порта, предназначенное для деления сигнальных линий передачи данных порта канала связи на квадранты, причем по меньшей мере один из этих квадрантов активный; и устройство передачи, предназначенное для передачи модуля управления потоком данных (МУПД) в виде совокупности разрядов управления физического уровня (РУФ), при этом каждый РУФ имеет количество битов, равное общему количеству сигнальных линий передачи данных в пределах всех активных квадрантов.

9. Система по п.8, в которой разряды РУФ из МУПД и биты РУФ передаются по каналу связи в заданном порядке передачи битов.

10. Система по п.9, в которой заданный порядок передачи битов выбирается для осуществления контроля с помощью циклического избыточного кода.

11. Система по п.10, дополнительно содержащая совокупность наборов мультиплексоров, причем каждый набор мультиплексоров связан с группой битов, при этом биты каждой группы вводятся в каждый из мультиплексоров, с