Способ и устройство для уменьшения фазовых скачков при переключении источников синхронизации

Иллюстрации

Показать всеИзобретение относится к области синхронизации в сетях связи и может быть использовано при переключении исходных опорных сигналов. Достигаемый технический результат - уменьшение фазовых скачков в сигнале синхронизации фрейма. Способ и устройство основаны на том, что генерируют первый и второй главные опорные сигналы, синхронизированные по фазе с первым и вторым исходными опорными сигналами соответственно, причем частота каждого из них в n раз выше, чем частота соответствующего исходного опорного сигнала, выбирают один из главных опорных сигналов с помощью сигнала выбора, делят частоту выбранного главного опорного сигнала до частоты соответствующего ему опорного сигнала и подают этот сигнал в схему фазовой подстройки частоты для генерирования сигнала синхронизации фрейма. 2 н. и 11 з.п. ф-лы, 4 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к синхронизации в сетях связи, в частности к уменьшению фазовых скачков в сигнале синхронизации фрейма при переключении между опорными источниками синхронизации.

Уровень техники

Нижний уровень сетей связи, такой как уровень соединения в базовой сети сотовой среды можно рассматривать как слой с распределенными ресурсами, предназначенными для управления потоками данных. Некоторые из основных узлов, входящих в состав таких сетей, выполняют коммутацию маршрутизации и направляют данные от входных в выходные линии. При такой коммутации очень важно обеспечить надежную внутреннюю синхронизацию, помимо прочего, для поддержания сдвига битов, возникающего при передаче через коммутаторы, на как можно более низком уровне.

Коммутаторы обычно оборудованы внутренними шинами мультиплексирования с временным разделением, заранее определенным образом передающими фреймы, состоящие из временных интервалов данных, от приемной до передающей стороны коммутатора. Для нормальной передачи фреймов их синхронизируют с главным синхронизирующим устройством, которое инициирует передачу каждого фрейма.

Стандарт H.110 определяет, что внутри узла, например коммутатора, находится два потенциальных источника главной синхронизации, первичное главное и вторичное главное синхронизирующие устройства. Два главных синхронизирующих устройства необходимы для того, чтобы в случае отказа первичного синхронизирующего устройства вторичное главное синхронизирующее устройство могло обеспечить синхронизацию узла. Причины такой ситуации могут состоять в отказе канала в некоторых из входных каналов, сигнал низкого качества, перерывы подачи питания и т.д.

Источники тактового сигнала первичного и вторичного главных синхронизирующих устройств представляют собой опорные сигналы, netref#1, и netref#2. Любой из последовательных входных портов узла можно использовать как источник для netref#1 и netref#2. Эти опорные сигналы синхронизированы с определенными опорными сигналами в сети.

Однако область проблем, в частности, не связана со стандартом H.110, но приведена здесь как пример. Для иллюстрации проблемы, из-за которой был составлен настоящий документ, рассмотрим дополнительный пример системы, а именно плезиохронную цифровую иерархию (ПЦИ, PDH). PDH представляет собой протокол передачи данных, обычно используемый для передачи данных со скоростью от 64 кбит/с до 139 264 Мбит/с.

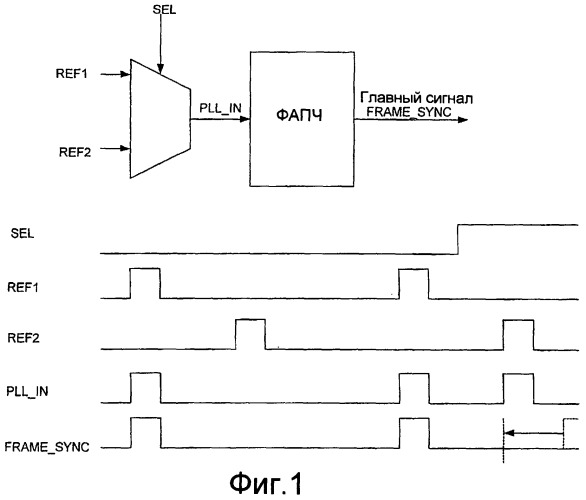

На фиг.1 показана упрощенная блок-схема и схема синхронизации в системе PDH. Одну из двух (или больше) опорных частот, которые обычно выделяют из последовательных каналов передачи данных, используют как опорный сигнал синхронизации для главного сигнала синхронизации фрейма. Опорные сигналы (REF1 и REF2) и сигнал синхронизации фрейма (FRAME_SYNC) обычно представляют собой сигналы частотой 8 кГц (125-е периоды), обозначающие один фрейм МВР (мультиплексирование с временным разделением, TDM).

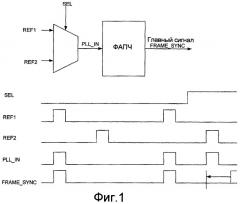

Опорные сигналы REF1 и REF2 могут находиться между собой в произвольном фазовом соотношении. Для снижения неустойчивости синхронизации обычно используют ФАПЧ (фазовая автоматическая подстройка частоты, PLL), которая предназначена для выравнивания изменений фазы при переходе от одного опорного сигнала к другому. Для выбора REF1 или REF2 в качестве опорного сигнала синхронизации используют внешний сигнал выбора (SEL). При переходе от одного опорного сигнала к другому (то есть, когда выбранный опорный сигнал пропадает, или качество опорного сигнала становится плохим), разница в фазах между опорными сигналами приводит к фазовому скачку на входе схемы ФАПЧ. Это постепенно приводит к изменению фазы сигнала синхронизации фрейма. Изменение фазы может достигать до одного периода опорного сигнала (худший случай). Два условия фазового скачка в худшем случае представлены на фиг.2 и на фиг.3.

Перед шиной TDM обычно размещают буфер ПППО (первым пришел - первым обслужен, FIFO), который предназначен для снижения влияния изменений скорости передачи данных и компенсации небольших нарушений фазы. Однако размеры таких буферов FIFO не позволяют компенсировать значительные скачки фазы, поскольку использование буферов FIFO большого объема приводит к значительным задержкам синхронизации и к необходимости использования большего количества логических схем. Таким образом, фазовый скачок в сигнале синхронизации фрейма, как описано выше, может привести к переполнению буфера FIFO, что, в свою очередь, приводит к сдвигу битов и ошибкам битов, в результате чего может потребоваться повторная синхронизация и повторная передача данных при переходе от одного опорного сигнала синхронизации к другому.

В WO 98/25367 и WO 98/25368 описаны варианты способа генерирования системного тактового сигнала, который периодически синхронизируется с выбранной одной из множества цепей фазовой синхронизации, в каждой из которых генерируют тактовый сигнал, синхронизированный по фазе с внешним опорным сигналом. Цифровой сигнал ошибки передают из выбранной цепи фазовой синхронизации в центральный генератор с цифровым управлением, и тактовую частоту системы синхронизируют с выходным сигналом центрального генератора с цифровым управлением.

В US 5909149 описана многополосная синхронизированная цепь, в которой используется множество переключаемых генераторов, управляемых напряжением. Здесь используется одна схема ФАПЧ, имеющая отдельный генератор с управлением напряжения для каждого требуемого частотного диапазона. Функция передачи фазового детектора в цепи синхронизации фазы переключается в зависимости от конкретного диапазона, выбранного для поддержания собственной частоты петли в одной точке, независимо от других изменений функции передачи петли, таких как изменение наклона частотной характеристики генераторов, управляемых напряжением, и изменений коэффициента деления схемы делителя частоты.

Один из недостатков WO 98/25367 и WO 98/25368 состоит в том, что в этих конструкциях необходимо применять значительное количество логических схем, поскольку требуется использовать несколько фазовых детекторов и генераторов с цифровым управлением. Это приводит к очень усложненному решению. Кроме того, цифровой сигнал ошибки должен быть интегрирован за период времени.

US 5909149 на самом деле направлен на решение проблем, связанных в переключением между двумя опорными частотами, но в нем описаны только проблемы переключения, которые возникают при переключении с одного частотного диапазона в другой, а не проблемы фазового скачка между двумя опорными частотами с одной частотой. Таким образом, в этой публикации не решается указанная проблема, поскольку в ней не предложено решение для уменьшения фазового скачка при переключении между опорными частотами.

Раскрытие изобретения

Настоящее изобретение направлено на способ и устройство, которые устраняют описанные выше недостатки. Свойства, описанные в предложенной формуле изобретения, характеризуют эти способ и устройство. В частности, в настоящем изобретении раскрыты способ и устройство, применяемые в сетях связи или передачи данных для уменьшения фазовых скачков в сигнале синхронизации фрейма при переключении с первого исходного опорного сигнала на второй опорный сигнал. Способ содержит этапы генерирования первого и второго главных опорных сигналов, синхронизированных по фазе с первым и вторым исходными опорными сигналами соответственно, частота каждого из которых в n раз выше, чем частота соответствующего исходного опорного сигнала, выбор одного из главных опорных сигналов с помощью сигнала выбора, деление частоты выбранного главного опорного сигнала обратно до частоты соответствующего ему опорного сигнала, подачу сигнала с разделенной частотой в схему фазовой подстройки частоты для генерирования сигнала синхронизации фрейма. Данный способ воплощен в устройстве.

Краткое описание чертежей

Для улучшения понимания настоящего изобретения в приведенном ниже описании делается ссылка на прилагаемые чертежи.

На фиг.1 показана блок-схема и временная характеристика, иллюстрирующие основную концепцию механизма синхронизации в системе PDH,

на фиг.2 показаны временные диаграммы, иллюстрирующие один из худших случаев фазового скачка в сигнале синхронизации фрейма в системе по фиг.1,

на фиг.3 показаны временные диаграммы, иллюстрирующие другой худший случай фазового скачка в сигнала синхронизации фрейма в системе по фиг.1,

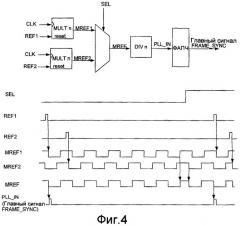

на фиг.4 показана блок-схема и временная диаграмма, иллюстрирующие пример механизма синхронизации в системе PDH, улучшенного в соответствии с настоящим изобретением.

Осуществление изобретения

В настоящем изобретении описан способ уменьшения фазовых скачков в сигнале синхронизации фрейма при переключении между источниками опорных сигналов синхронизации.

Настоящее изобретение основано на реализации того факта, что при генерировании главного сигнала синхронизации фрейма, необходимо обеспечить синхронизацию опорной частоты, но при этом фазовое соотношение с опорным сигналом не имеет значения.

Для уменьшения фазового скачка, при переходе с одного опорного сигнала на другой, в настоящем изобретении вводят "тактовые частоты" (MREF1 и MREF2), синхронизированные по фазе с опорными сигналами, с частотой, которая в n раз больше, чем частота опорных сигналов (n представляет собой целое число). Эти тактовые сигналы могут генерироваться с помощью счетчиков с высокой тактовой частотой (CLK), сброс которых выполняют по опорному сигналу, как показано на фиг.4.

После мультиплексирования выбранную "тактовую частоту" (MREF) делят обратно до исходной частоты. Таким образом, максимальные фазовые скачки уменьшают от одного периода опорного сигнала до одного периода сигнала MREF, как показано на фиг.4. Частоту "тактовых сигналов" MREF следует выбирать как можно более высокой для минимизации фазовых скачков при переходе, но она не должна быть настолько высокой, чтобы переменное количество периодов "тактовой частоты" MREF возникало между двумя импульсами REF. Это происходит, когда частота MREF настолько высока, что период MREF меньше, чем дельта-период максимально допустимого отклонения частоты сигнала REF (REF(номинальный период) - REF(минимальный период) или REF(максимальный период) - REF(номинальный период)). Следовательно, период MREF всегда должен быть не больше, чем эта максимальная вариация периода.

Пример варианта выполнения настоящего изобретения, вместе с временными диаграммами, иллюстрирующими сценарий сдвига опорного сигнала, показан на фиг.4. Этот сценарий иллюстрирует эффект настоящего изобретения.

На основе двух доступных опорных сигналов, REF1 и REF2, генерируют сигналы MREF1 и MREF2 путем фазовой синхронизации с самими опорными сигналами сигналов тактовой частоты, частота которых в n раз выше, чем частота соответствующих опорных сигналов. MULT n обозначает, что частоты MREF1 и MREF2 представляют собой соответственно частоты REF1 и REF2, умноженные на n, где n представляет собой целочисленную степень двух (2, 4, 8, 16 и т.д.). MREF1 и MREF2 мультиплексируют с сигналом выбора (SEL), при этом MREF1 выбирают, когда SEL имеет низкий уровень, и MREF2 выбирают, когда SEL имеет высокий уровень. Выбранный сигнал MREF затем делят на n (предпочтительно с помощью счетчика), в результате чего получают сигнал PLL_IN, который подают на вход схемы ФАПЧ, на выходе которой получают результирующий главный сигнал синхронизации фрейма. DIV n обозначает, что частота PLL_IN представляет собой частоту MREF, разделенную на n, где n представляет собой то же целое число, что и в MULT n.

В случае, представленном на фиг.4, сигнал PLL_IN переходит на высокой уровень сразу после REF1. Это показано только для представления того, что фаза PLL_IN не изменяется, даже если SEL изменяется при переходе от REF1 на REF2. PLL_IN переходит в высокое состояние, поскольку элемент DIV подсчитал n периодов. Сброс MREF выполняют при поступлении следующего REF2, но поскольку периоды MREF1 и MREF2 короче, чем максимальная вариация фазы между двумя импульсами REF, переменное количество периодов "тактовой частоты" MREF между двумя импульсами REF не получается. Следует отметить, что при этом больше не поддерживается корреляция между фазами REF1/REF2 и PLL_IN. Исходная схема ФАПЧ в этом случае становится цепью синхронизации частоты (АПЧ, FLL), которая подавляет фазовые скачки, превышающие один период MREF.

MULT n указывает, что частоты MREF1 и MREF2 представляют собой соответственно частоты REF1 и REF2, умноженные на n, где n представляет собой целочисленную степень двух (2, 4, 8, 16 и т.д.). DIV n указывает, что частота PLL_IN представляет собой частоту MREF, разделенную на n, где n представляет собой то же целое число, что и в MULT n.

Следует отметить, что можно выбирать различные логические уровни и конкретные логические устройства, применяемые в блок-схеме синхронизации, показанной на фиг.4. Назначение представленных временной диаграммы и блок-схемы состоит в иллюстрации вариантов выполнения и сценария событий, которые могут происходить при использовании настоящего изобретения, и не ограничивают его объем, определенный приложенными независимыми пунктами формулы изобретения.

Основное преимущество настоящего изобретения состоит в том, что максимальные фазовые скачки при переключении с одного опорного сигнала на другой опорный сигнал могут быть уменьшены от одного периода опорного сигнала до дельта-периода максимально допустимой девиации частоты сигнала REF (REF(номинальный период) - REF(минимальный период) или REF(максимальный период) - REF(номинальный период)).

Кроме того, при этом исключаются ошибки битов при переключении с одного опорного сигнала на другой, без использования буфера FIFO больших размеров, что обеспечивает снижение частоты ошибки битов. Возможность исключения буфера FIFO больших размеров также снижает задержки синхронизации и уменьшает количество используемых логических устройств.

Настоящее изобретение обеспечивает несложное решение и снижает необходимость повторной синхронизации и повторной передачи данных.

Сокращения:

FIFO - Буфер организации очереди по принципу первым пришел - первым обслужен.

АПЧ - Схема автоматической подстройки частоты.

PDH - Плезиохронная цифровая иерархия.

ФАПЧ - Фазовая автоматическая подстройка частоты.

Литература

1. WO 98/25367 и WO 98/25368; A method and a circuit for generating a system/central clock signal.

2. Патент США 5909149; Multiband phase-locked loop using a switched voltage controlled oscillator.

1. Способ, используемый в сети связи или передачи данных для уменьшения фазовых скачков в сигнале синхронизации фрейма при переключении с первого исходного опорного сигнала на второй исходный опорный сигнал, отличающийся тем, что генерируют первый и второй главный опорный сигнал, синхронизированные по фазе с первым и вторым исходными опорными сигналами, соответственно, причем частота каждого из которых в n раз выше, чем частота соответствующего исходного опорного сигнала, выбирают один из главных опорных сигналов с помощью сигнала выбора, делят частоту выбранного главного опорного сигнала до частоты соответствующего ему опорного сигнала, подают сигнал с разделенной частотой в схему фазовой подстройки частоты для генерирования сигнала синхронизации фрейма.

2. Способ по п.1, отличающийся тем, что первый главный опорный сигнал выбирают, когда сигнал выбора имеет низкий уровень, и второй главный опорный сигнал выбирают, когда сигнал выбора имеет высокий уровень, или наоборот.

3. Способ по п.1 или 2, отличающийся тем, что деление частоты выполняют путем подсчета количества периодов выбранного главного опорного сигнала и вывода такого же импульса, как и в соответствующем исходном опорном сигнале, для каждого n-ого периода выбранного главного опорного сигнала.

4. Способ по п.1 или 2, отличающийся тем, что периоды первого главного опорного сигнала и второго главного опорного сигнала больше, чем дельта-период максимально допустимой девиации частоты соответсвующего исходного опорного сигнала.

5. Способ по п.3, отличающийся тем, что периоды первого главного опорного сигнала и второго главного опорного сигнала больше, чем дельта-период максимально допустимой девиации частоты соответствующего исходного опорного сигнала.

6. Способ по п.1, отличающийся тем, что сигнал синхронизации фрейма представляет собой главный сигнал синхронизации фрейма в системе плезиохронной цифровой иерархии (ПЦИ).

7. Устройство, используемое в узле сети связи или передачи данных, предназначенное для уменьшения фазовых скачков сигнала синхронизации фрейма при переключении с первого исходного опорного сигнала на второй исходный опорный сигнал, отличающееся элементом для каждого исходного опорного сигнала, генерирующим первый и второй главный опорные сигналы, синхронизированные по фазе с первым и вторым исходными опорными сигналами, соответственно, частота каждого из которых в n раз выше, чем частота соответствующего исходного опорного сигнала, мультиплексором с первым и вторым главными опорными сигналами, используемыми в качестве входных сигналов, совместно с сигналом выбора, с помощью которого выбирают один из главных опорных сигналов в качестве выходного сигнала мультиплексора, делителем, выполняющим деление частоты выходного сигнала мультиплексора, до частоты соответствующего исходного опорного сигнала, схемой фазовой подстройки частоты, предназначенной для генерирования сигнала синхронизации фрейма, на вход которой поступает сигнал с выхода делителя.

8. Устройство по п.7, отличающееся тем, что мультиплексор выбирает первый главный опорный сигнал, когда сигнал выбора имеет низкий уровень, и второй главный опорный сигнал, когда сигнал выбора имеет высокий уровень, или наоборот.

9. Устройство по п.7 или 8, отличающееся тем, что делитель представляет собой счетчик, подсчитывающий количество периодов выходного сигнала мультиплексора, на выход которого поступает такой же импульс, как и в соответствующем исходном опорном сигнале, для каждого n-го периода выходного сигнала мультиплексора.

10. Устройство по п.7 или 8, отличающееся тем, что периоды главных опорных сигналов больше, чем дельта-период максимально допустимой девиации частоты соответствующего исходного опорного сигнала.

11. Устройство по п.9, отличающееся тем, что периоды главных опорных сигналов больше, чем дельта-период максимально допустимой девиации частоты соответствующего исходного опорного сигнала.

12. Устройство по п.7, отличающееся тем, что узел представляет собой коммутатор.

13. Устройство по п.7, отличающееся тем, что сигнал синхронизации фрейма представляет собой главный сигнал синхронизации фрейма в системе плезиохронной цифровой иерархии (ПЦИ).