Устройство для проведения игры

Иллюстрации

Показать всеИзобретение относится к устройству для проведения игры. Техническим результатом является повышение устойчивости в работе устройства для проведения игры в условиях внешних воздействий, достигаемой за счет того, что осуществляют контроль целостности игрового процесса, проверяют данные внешней памяти, тестируют генератор случайных чисел для получения возможности нормализации выходных данных генератора случайных чисел и работы микроконтроллера. Сущность изобретения заключается в том, что устройство содержит декодирующую микросхему с кварцевым резонатором для получения рабочей частоты в 6 МГц. 4 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к развлечениям и играм, в частности к устройствам для проведения игр.

Известно устройство для проведения игры, содержащее связанные между собой компьютер, управляющий узел, генератор случайных чисел и средство генерации, обработки данных игрового процесса и контроля целостности сохраняемых данных (см. патент РФ №2060756, кл. А 63 F 13/10, 27.05.1996 - аналог и прототип).

Недостатком известного устройства для проведения игры является низкая устойчивость в работе в условиях внешних воздействий.

Техническим результатом изобретения является повышение устойчивости в работе устройства для проведения игры в условиях внешних воздействий, повышение зрелищности и занимательности.

Достигается это устройством для проведения игры, содержащим декодирующую микросхему с кварцевым резонатором для получения рабочей частоты в 6 MHz и для преобразования ее в тактовую частоту в 16 MHz, два блока внешней памяти, средство генерации, обработки данных игрового процесса и контроля целостности сохраняемых данных, выполненное в виде микроконтроллера, связанного с таймером реального времени, имеющего источник резервного питания, а генератор случайных чисел совмещен с дешифратором адресов, причем декодирующая микросхема связана с микроконтроллером посредством тактовой частоты в 16 MHz, а блоки внешней памяти связаны с дешифратором адресов, при этом генератор случайных чисел содержит группу по меньшей мере из двух невзаимосвязанных генераторов периодического импульсного сигнала, источник управляющего сигнала, блок формирования случайной импульсной последовательности, выходной регистр, в котором выход каждого из генераторов группы связан с соответствующим информационным входом блока формирования случайной импульсной последовательности, информационный выход которого связан с информационным входом регистра, выход которого выполнен выходом генератора, а выход источника управляющего сигнала подключен к управляющему входу блока формирования случайной импульсной последовательности и к тактовому входу выходного регистра.

Каждый из генераторов периодического импульсного сигнала выполнен в виде инвертора, охваченного положительной обратной связью.

Блок формирования случайной импульсной последовательности содержит мультиплексор и счетчик, выходы которого подключены к адресному входу мультиплексора, прямые и инверсные информационные входы мультиплексора выполнены информационными входами блока, счетный вход счетчика выполнен управляющим входом блока формирования, а выход мультиплексора выполнен выходом блока.

Источник управляющего сигнала состоит из последовательно соединенных генератора периодического сигнала и делителя частоты, выход которого выполнен выходом источника управляющего сигнала.

Генератор выполнен на единичном базовом матричном кристалле.

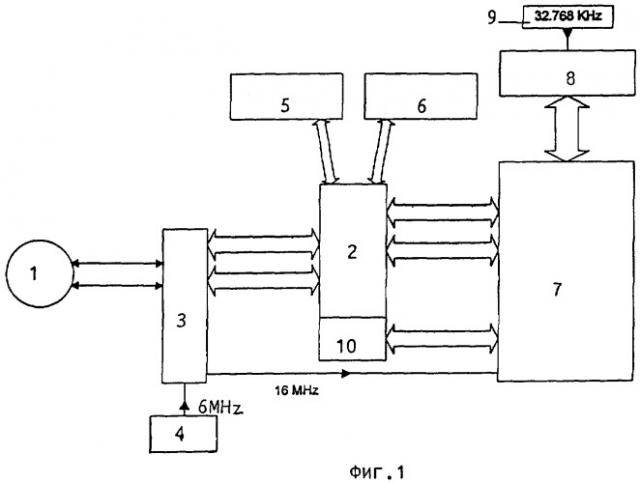

Сущность изобретения поясняется чертежами, где:

на фиг.1 изображена схема устройства для проведения игры;

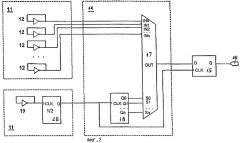

на фиг.2 - генератор случайных чисел.

Устройство для проведения игры содержит связанные между собой компьютер (не показан), управляющий узел 1, генератор 2 случайных чисел и средство генерации, обработки данных игрового процесса и контроля целостности сохраняемых данных.

Устройство содержит декодирующую микросхему 3 с кварцевым резонатором 4 для получения рабочей частоты в 6 MHz и для ее преобразования в тактовую частоту в 16 MHz, два блока 5, 6 внешней памяти, средство генерации, обработки данных игрового процесса и контроля целостности сохраняемых данных выполнено в виде микроконтроллера 7, связанного с таймером 8 реального времени, имеющего источник 9 резервного питания, а генератор 2 случайных чисел совмещен с дешифратором 10 адресов.

Декодирующая микросхема 3 связана с микроконтроллером 7 посредством подаваемой тактовой частоты в 16 MHz, а блоки 5, 6 внешней памяти связаны с дешифратором 10 адресов.

Генератор 2 случайных чисел содержит группу 11 по меньшей мере из двух невзаимосвязанных генераторов 12 периодического импульсного сигнала, источник 13 управляющего сигнала, блок 14 формирования случайной импульсной последовательности, выходной регистр 15, в котором выход каждого из генераторов группы связан с соответствующим информационным входом блока 14 формирования случайной импульсной последовательности, информационный выход которого связан с информационным входом регистра 15, выход которого выполнен выходом 16 генератора, а выход источника управляющего сигнала 13 подключен к управляющему входу блока 14 формирования случайной импульсной последовательности и к тактовому входу выходного регистра 15.

Каждый из генераторов 12 периодического импульсного сигнала выполнен в виде инвертора, охваченного положительной обратной связью.

Блок 14 формирования случайной импульсной последовательности содержит мультиплексор 17 и счетчик 18, выходы которого подключены к адресному входу мультиплексора 17, прямые и инверсные информационные входы мультиплексора 17 являются информационными входами 14 блока, счетный вход счетчика является управляющим входом блока 14 формирования, а выход мультиплексора 17 является выходом блока 14.

Источник 13 управляющего сигнала состоит из последовательно соединенных генератора 19 периодического сигнала и делителя 20 частоты, выход которого является выходом источника 13 управляющего сигнала.

Генератор 2 выполнен на единичном базовом матричном кристалле.

Функционирует устройство для проведения игр следующим образом.

В процессе работы выполняются следующие функции:

- выдача данных, описывающих этапы игрового процесса;

- генерация случайных чисел;

- генерация выигрышей из таблицы выигрышей;

- хранение текущего состояния игры;

- хранение статической информации;

- отсчет текущего времени;

- хранение информации о состоянии различных компонентов устройства;

- хранение информации о некритических ошибках устройства;

- хранение информации о критических ошибках устройства;

- хранение информации об активизации.

Микроконтроллер 7 осуществляет все операции по генерации и обработке данных для игрового процесса, а также по контролю целостности сохраняемых данных. В микроконтроллере 7 содержится программный код и данные, описывающие этапы игры, реализацию внутренних процедур и таблицы выигрышей. Эта информация содержится во внутренней flash-памяти микроконтроллера 7 и загружается в нее до начала работы.

В процессе работы микроконтроллер 7 осуществляет:

- выдачу данных, описывающих этапы игрового процесса;

- обработку полученных от генератора случайных чисел;

- генерацию выигрышей из таблиц;

- обработку команд и данных, полученных от внешних устройств;

- получение обработку и запись данных в памяти блоков 5, 6;

- диагностику состояния периферийных компонентов устройств;

В микроконтроллере 7 имеется 4 кб памяти EEPROM, в которой хранится информация о времени наработки математической платы и о ключе активизации. Первые 24 байт занимает служебная информация, после которой находятся два счетчика наработки (основной и резервный), размером по 32 бита каждый. Все остальное пространство памяти используется для контроля за временем наработки.

Счетчики наработки синхронизированы и работают следующим образом:

- После программирования микроконтроллера 7 адресное пространство EEPROM заполнено единицами. С самого начала работы платы математики, после того, как она была запрограммирована, адресное пространство, используемое для контроля времени наработки, начинает заполняться нулями со скоростью 1 бит в секунду. Когда адресное пространство заканчивается, то оно вновь начинает заполняться с нулевого адреса значением, инверсным предыдущему (при первом цикле единицы заполняются нулями, при втором - нули единицами и т.д.). Каждый раз, когда адресное пространство заканчивается, значение счетчиков наработки увеличивается на единицу. Это происходит примерно 1 раз за 8,5 часов.

- После изменения очередного бита в адресном пространстве EEPROM, в обоих блоках 5, 6 памяти сохраняются значения изменившегося байта и его адрес. При выключении аппарата эти значения сохраняются, и при следующем включении процесс заполнения адресного пространства продолжается с того места, на котором он был завершен.

- Соответствие значения байта в обоих блоках 5, 6 памяти EEPROM проверяется каждую секунду. В случае несовпадения значений возникает сообщение о критической ошибке.

Микроконтроллер 7 также оснащен 4 кб памяти SRAM, которая используется следующим образом:

- 2 кб для хранения локальных переменных;

- 1 кб для хранения адресов возврата из процедур;

- 1 кб для текущих вычислений.

Для работы микроконтроллера 7 требуется тактовая частота 16 MHz, подающаяся с внешнего источника. Подачу этой частоты обеспечивает микросхема 3.

Программируемое логическое устройство - дешифратор 10 - работает как генератор случайных чисел, а также выступает в качестве дешифратора адресов при обмене данными между микроконтроллером 7 и периферийными устройствами - блоками 5, 6 памяти и управляющим узлом 1. Генератор 2 поддерживает протокол обмена данными, с помощью которого микроконтроллер получает случайное число с дешифратора 10.

Один из блоков 5 является основным, другой 6 выступает в качестве резервного, в котором хранится дубликат данных их основного банка. В памяти хранятся все статистические данные о работе устройства за все время, прошедшее с момента активации, такие как:

- количество денег и соответствующих им кредитов, принятое и выданное устройством с учетом подробностей о том, каким образом были получены и выданы деньги;

- общее количество всех сыгранных на устройстве игр, с учетом подробностей о выигранных и проигранных играх;

- количество выпавших призовых игр, соответствующее им количество выигранных кредитов;

- количество сыгранных игр на удвоение, соответствующее им количество выигранных и проигранных кредитов;

- количество открываний двери устройства, купюроприемника и монетоприемника;

- количество выключений устройства.

Кроме того, в блоках 5, 6 хранится контрольная информация о времени наработки устройства. Также в блоках 5, 6 остается 1 кб свободной памяти, которая используется микроконтроллером 7 в процессе вычислений при нехватке собственной памяти. Данные, которые находятся в этой области памяти, не учитываются в контрольной сумме при проверке целостности данных.

Обмен данными между платой математики и компьютером игрового устройства происходит по узлу 1, поддержку которого на плате математики обеспечивает микросхема 3. Выходная тактовая частота 6 MHz, необходимая для работы микросхемы, обеспечивается кварцевым резонатором 4. Эта же тактовая частота преобразуется внутри микросхемы в 16 MHz и подается на вход микроконтроллера 7.

Имеется таймер 8 текущего времени, который обеспечен автономным питанием. Таймер обменивается данными с микроконтроллером 7 напрямую по протоколу I2С.

При получении пакета данных с компьютера игрового устройства по узлу 1 этот пакет декодируется микросхемой 3 и передается в микроконтроллер 7. Данные, возвращаемые микроконтроллером 7, передаются в микросхему 3 и далее на узел 1. Необходимая для работы микросхемы 3 частота 6 MHz задается кварцевым резонатором 4. Эта же частота преобразуется микросхемой в 16 MHz и подается в микроконтроллер 7.

Генератор 2 выступает в качестве дешифратора адресов при обращении микроконтроллера 7 к внешней памяти либо к микросхеме 3. Процесс чтения и записи в память блоков 5, 6 сопровождается проведением процедур, контролирующих целостность данных. Как при чтении, так и при записи сначала проверяются контрольные суммы в обоих блоках 5, 6 памяти, после чего соответствие контрольного байта в блоке памяти и в EEPROM. Если результаты этой проверки оказываются отрицательными, то работа платы математики прекращается с фиксацией соответствующей ошибки. Исключение составляют случаи, когда устройство находится в режиме демо-игры или сервисной игры. Генерация 3 случайных чисел выполняется по запросу микроконтроллера 7. Запрос и возврат сгенерированного случайного числа осуществляется по протоколу SPI. Таймер реального времени отслеживает текущее время и возвращает его значение непосредственно на микроконтроллер 7. Установка значения текущего времени также производится непосредственно с микроконтроллера 7. Таймер 8 снабжен источником 9 резервного питания, обеспечивающего ход часов при отключении основного питания устройства.

Инициализация проводится при каждом включении платы математики. В процессе инициализации проверяется состояние компонентов платы и целостность данных. После инициализации плата готова к работе. После включения устройства микроконтроллер 7 посылает первый запрос на получение случайного числа, в ответ на который возвращается два числа, которые сравниваются между собой. Если оказывается, что они одинаковы, это свидетельствует об ошибке и работа платы математики прекращается с фиксацией соответствующей ошибки. В противном случае микроконтроллер 7 принимает последнее из полученных чисел.

Инициализация происходит в следующей последовательности:

- проверяется память блоков 5, 6 при этом:

- проверяется контрольная сумма в блоке 5;

- проверяется контрольная сумма в блоке 6;

- при неверной контрольной сумме блока 5 происходит восстановление данных блока 6;

- при неверной контрольной сумме блока 6 плата математики фиксирует критическую ошибку, в результате чего дальнейшая работа становится невозможной;

- проверяется совпадение счетчиков наработки и контрольных байта, хранящихся в EEPROM и блоках 5, 6;

- проверяется наличие цифровой подписи в EEPROM. Если цифровая подпись не обнаружена, то плата работает в нективированном режиме. Этот режим не допускает полноценную эксплуатацию устройства в нем, в частности невозможно использовать купюроприемник, а также снять кредиты со счета игрока;

- инициализируется узел 1, тактовая частота на выходе микросхемы 3 повышается до 16 MHz;

- проверяется таймер. Текущее время должно быть больше, чем время последней игры, которое хранится в памяти блоков 5, 6.

Результаты инициализации записываются в память блоков 5, 6 и возвращаются компьютеру устройства аппарата по команде "Initialize".

При активации в EEPROM заносится информация о ключе активации, происходит полный сброс обоих блоков 5, 6 и плата переходит в нормальный режим работы.

Выходной сигнал каждого генератора 12 поступает на соответствующий вход мультиплексора 17, который управляет двоичным счетчиком 18. Состояние счетчика 18 изменяется по приходу каждого последующего импульса с выхода источника 13 управляющего сигнала. Тем самым обеспечивается поочередная передача соответствующего входного сигнала (прямого или инвертированного) на выход мультиплексора 17, то есть на выход блока 14, от одного из генераторов 12.

Нормализация выходных сигналов блока 14, а именно устранение дребезга, осуществляется в регистре 15 за счет фиксации по такту счетчика 18. В результате на выходе 16 регистра 15, который является выходом устройства, формируется случайная двоичная импульсная последовательность, имеющая требуемые параметры.

Тестирование генератора 2 проводилось с использованием теста из источника "DIEHARD Battery of Test of Randomness" (http://www.csis.hku/hk/˜diehard/). Съем сигнала выполнялся с помощью 16-разрядного сдвигового регистра на различных частотах.

Выходной сигнал каждого генератора 12 поступает на соответствующий вход мультиплексора 17, который управляется двоичным счетчиком 18. Состояние счетчика 18 изменяется по приходу последующего импульса с выхода источника 13 управляющего сигнала. Тем самым обеспечивается поочередная передача соответствующего входного сигнала (прямого или инвертированного) на выход мультиплексора 17, то есть на выход блока 14, от одного из генераторов 12.

Нормализация выходных сигналов блока 14, а именно устранение дребезга осуществляется в регистре 15 за счет фиксации сигнала по такту счетчика 18. В результате на выходе 16 регистра 15, который является выходом устройства. Формируется случайная двоичная импульсная последовательность, имеющая требуемые параметры.

Тестирование генератора 2 проводилось с использованием теста их источника "DIEHARD Battery of Test of Randomness" (http://www.csis.hku/hk/˜diehard/). Съем сигнала выполнялся с помощью 16-разрядного сдвигового регистра на различных частотах. Размер данных для тестирования составлял не менее 10 Мбайт. Результаты тестов приведены ниже.

| Количество генераторов в группе | Частота сдвига (KHz) | p-values |

| 16 | 100 | 0.90460 |

| 16 | 500 | 0.65141 |

| 16 | 1000 | 0.447471 |

Проведенное тестирование показало, что формируемая последовательность логических сигналов удовлетворяет статическим критериям, принятым характеристикам двоичной последовательности как истинно случайной (True Random Numbers).

Таким образом, изобретение повышает эффективность в эксплуатации.

Промышленная применимость

Изобретение может быть использовано при изготовлении устройств для проведения игр.

1. Устройство для проведения игры, содержащее связанные между собой компьютер, управляющий узел, генератор случайных чисел и средство для генерации, обработки данных игрового процесса и контроля их целостности, отличающееся тем, что средство для генерации и обработки данных игрового процесса и контроля их целостности выполнено в виде микроконтроллера, связанного с таймером реального времени, имеющего источник резервного питания, а генератор случайных чисел предназначен для выдачи случайного числа микроконтроллеру при обращении его к блокам внешней памяти, компьютер предназначен для передачи пакета данных через управляющий узел и декодирующую микросхему в микроконтроллер, декодирующая микросхема с кварцевым резонатором предназначена для преобразования рабочей частоты в 6 MHz в тактовую частоту в 16 MHz, и подачи на микроконтроллер, при этом генератор случайных чисел содержит группу по меньшей мере из двух генераторов периодического импульсного сигнала, источник управляющего сигнала, блок формирования случайной импульсной последовательности, регистр, выход каждого из генераторов периодического импульсного сигнала связан с соответствующим информационным входом блока формирования случайной импульсной последовательности, информационный выход которого связан с информационным входом регистра для выдачи случайного числа микроконтроллеру, выход источника управляющего сигнала подключен к управляющему входу блока формирования случайной импульсной последовательности, а выход регистра является выходом генератора случайных чисел.

2. Устройство по п.1, отличающееся тем, что каждый из генераторов периодического импульсного сигнала выполнен в виде инвертора, охваченного положительной обратной связью.

3. Устройство по п.1, отличающееся тем, что блок формирования случайной импульсной последовательности содержит мультиплексор и счетчик, выходы которого подключены к адресному входу мультиплексора, прямые и инверсные информационные входы мультиплексора являются информационными входами блока, счетный вход счетчика является управляющим входом блока, а выход мультиплексора является выходом блока.

4. Устройство по п.1, отличающееся тем, что источник управляющего сигнала состоит из последовательно соединенных генератора периодического сигнала и делителя частоты, выход которого является выходом источника управляющего сигнала.

5. Устройство по п.1, отличающееся тем, что генератор случайных чисел выполнен на базовом матричном кристалле.