Устройство логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц

Иллюстрации

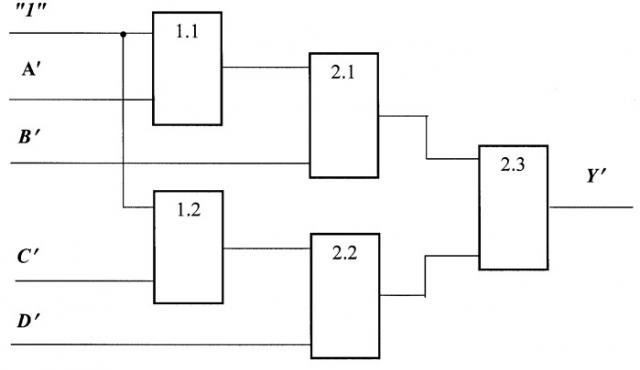

Показать всеИзобретение относится к вычислительной технике для реализации логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц. Технический результат заключается в улучшении точности оценки. Устройство содержит аналоговые вычитатели (1.1, 1.2), аналоговые перемножители (2.1, 2.2, 2.3). Аналоговые значения (единица или ноль) либо дискретные значения (с уровнем логической единицы или нуля) поступают параллельно на первый (А'), второй (В'), третий (С') и четвертый (D') информационные входы. Дополнительный информационный вход устройства «1» предназначен для подачи сигнала «1», из которого вычитается значение сигнала, поступающего на третий информационный вход (С). 1 ил., 3 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для реализации как логических, так и арифметических операций с дискретными и аналоговыми значениями нулей и единиц.

Известны логические устройства, реализующие различные функции преобразования дискретных значений: "Многофункциональный логический модуль" (SU 1621164 А1), "Логическая схема исключающее ИЛИ с тремя входами" (JP 2867253 В2 10098374 А), "Оптимизированные для топологии тракта передачи данных арифметические и логические функциональные схемы" (US 5982194 А).

Каждое из перечисленных устройств аналогов имеет три и более информационных входа, на которые поступают сигналы с уровнями логического нуля либо единицы, один или два информационных выхода и общие устройства - различные логические элементы. Рассматриваемые устройства построены по принципу каскадного соединения логических элементов и формируют на одном или двух информационных выходах значения сигналов с уровнями логического нуля либо единицы, в зависимости от значений сигналов, подаваемых на их информационные входы.

К недостаткам следует отнести возможность функционирования данных устройств только с дискретными значениями сигналов, то есть с уровнями логического нуля либо единицы.

В качестве прототипа выберем наиболее близкое по технической сущности к заявляемому логическое устройство, выполненное как логическая схема на основе булевой функции (Токхайм Р. Микропроцессоры: Курс и упражнения / Пер. с англ., под ред. В.Н.Грасевича. М.: Энергоатомиздат, 1987. - 336 с., на стр.52, рис.3.6). Рассматриваемое логическое устройство состоит из первого и второго логических элементов "НЕ" и четырехвходового логического элемента "И". Первый информационный вход логического устройства является информационным входом первого логического элемента "НЕ", выход которого соединен с первым информационным входом четырехвходового логического элемента "И", второй информационный вход логического устройства является вторым информационным входом четырехвходового логического элемента "И", третий информационный вход логического устройства является информационным входом второго логического элемента "НЕ", выход которого соединен с третьим информационным входом четырехвходового логического элемента "И", четвертый информационный вход логического устройства является четвертым информационным входом четырехвходового логического элемента "И", информационный выход которого является информационным выходом устройства.

Недостатком устройства-прототипа является возможность функционирования только с дискретными значениями сигналов, то есть с уровнями логического нуля либо единицы.

В аппаратуре передачи дискретной информации широко используются устройства, реализующие различные логические операции. Однако, в ряде случаев, для улучшения точности оценки необходимо производить вычисления с использованием аналоговых значений. В этом случае возникает необходимость разработки дискретно-аналогового устройства, оперирующего как дискретными, так и аналоговыми значениями.

Технической задачей, на решение которой направлено предлагаемое устройство, является расширение функциональных возможностей устройства за счет реализации как логических, так и арифметических операций с дискретными и аналоговыми значениями нулей и единиц. Аналоговые значения от 0 (нет сигнала) до 1 (максимальный уровень сигнала) могут быть получены в дробных значениях путем дискретизации, например, принимаемой псевдослучайной последовательности, сформированной на основе характеристического полинома n-го порядка, где n≥3, путем нелинейного преобразования по заданной дискретной функции. Дискретизируют ее элементы с частотой, в k раз превышающей тактовую частоту принимаемой псевдослучайной последовательности, где k≥2.

Поставленная задача решается с помощью предлагаемого устройства логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц, содержащего первый, второй, третий, четвертый информационные входы и информационный выход, а также дополнительный информационный вход, первый и второй аналоговые вычитатели, первый, второй и третий аналоговые перемножители. Дополнительный информационный вход устройства является первым информационным входом первого и второго аналоговых вычитателей. Первый информационный вход устройства является вторым информационным входом первого аналогового вычитателя, информационный выход которого соединен с первым информационным входом первого аналогового перемножителя. Второй информационный вход устройства является вторым информационным входом первого аналогового перемножителя, информационный выход которого соединен с первым информационным входом третьего аналогового перемножителя. Третий информационный вход устройства является вторым информационным входом второго аналогового вычитателя, информационный выход которого соединен с первым информационным входом второго аналогового перемножителя. Четвертый информационный вход устройства является вторым информационным входом второго аналогового перемножителя, информационный выход которого соединен с вторым информационным входом третьего аналогового перемножителя, информационный выход которого является информационным выходом устройства.

Для получения дискретно-аналогового устройства необходимо заменить логические операции соответствующими им аналоговыми. Схемы аналоговых элементов, которые использованы в устройстве, известны и приведены в книге: А.А.Сикарев, О.Н.Лебедев. "Микроэлектронные устройства формирования и обработки сложных сигналов". - М.: Радио и связь, 1983, стр.194, рис.7.6.

В таблице 1 представлены реализуемые логическая и аналоговая функции, а также таблицы истинности рассматриваемых устройств.

| Таблица 1 | ||||

| Логическое устройство | Аналоговое устройство | |||

| Наименование | Инвертор ("НЕ") | Аналоговый инвертор | ||

| Реализуемая функция | Отрицание (инверсия) | |||

| Таблица истинности | х | y | х | y |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 0 |

В таблице 2 представлены реализуемые логическая и аналоговая функции, а также таблицы истинности рассматриваемых устройств.

| Таблица 2 | ||||||

| Логическое устройство | Аналоговое устройство | |||||

| Наименование | Конъюнктор ("И") | Аналоговый конъюнктор | ||||

| Реализуемая функция | Конъюнкция y=х1x2 | y=х1х2 | ||||

| Таблица истинности | х1 | x2 | y | x1 | x2 | y |

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 |

Таким образом, заменяя логические операции соответствующими аналоговыми, получим аналоговое устройство, оперирующее с аналоговыми значениями.

Аналоговое устройство реализует функцию: Y'=(1-А')В'(1-C')D', где Y', A', B', C', D' - аналоговые значения.

В таблице 3 представлена таблица истинности предлагаемого устройства.

| Таблица 3 | ||||

| D' | С' | B' | А' | Y' |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

Указанная новая совокупность признаков заявленного устройства, за счет замены логических элементов соответствующими им арифметическими, позволяет расширить функциональные возможности устройства, как видно из таблицы 3, за счет реализации как логических, так и арифметических операций с дискретными и аналоговыми значениями нулей и единиц.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественными всем признакам заявленного устройства, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Предложенное устройство изображено на чертеже, на котором представлена структурная схема устройства логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц.

Устройства 1.1, 1.2, представляют собой аналоговые вычитатели, устройства 2.1, 2.2, 2.3 представляют собой аналоговые перемножители.

Устройство логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц состоит из первого и второго аналоговых вычитателей 1.1, 1.2 и первого, второго и третьего аналоговых перемножителей 2.1, 2.2, 2.3. Дополнительный информационный вход устройства "1" является первым информационным входом первого и второго аналоговых вычитателей 1.1, 1.2 соответственно, первый информационный вход устройства А' является вторым информационным входом первого аналогового вычитателя 1.1, информационный выход которого соединен с первым информационным входом первого аналогового перемножителя 2.1, второй информационный вход устройства В' является вторым информационным входом первого аналогового перемножителя 2.1, информационный выход которого соединен с первым информационным входом третьего аналогового перемножителя 2.3, третий информационный вход устройства С' является вторым информационным входом второго аналогового вычитателя 1.2, информационный выход которого соединен с первым информационным входом второго аналогового перемножителя 2.2, четвертый информационный вход устройства D' является вторым информационным входом второго аналогового перемножителя 2.2, информационный выход которого соединен с вторым информационным входом третьего аналогового перемножителя 2.3, информационный выход которого является информационным выходом устройства.

Первый и второй аналоговые вычитатели 1.1, 1.2, соответственно, предназначены для вычитания значений сигналов, поступающих на их входы. Первый, второй и третий аналоговые перемножители 2.1, 2.2, 2.3, соответственно, предназначены для перемножения аналоговых значений сигналов, поступающих на их входы.

Заявленное устройство логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц работает следующим образом. Аналоговые значения (единица или ноль), либо дискретные значения (с уровнем логической единицы или нуля) поступают параллельно на первый А', второй В', третий С' и четвертый D' информационные входы дискретно-аналогового устройства. На дополнительный информационный вход "1" дискретно-аналогового устройства поступает сигнал с уровнем логической единицы. В первом аналоговом вычитателе 1.1 производится вычитание из сигнала, поступающего на дополнительный информационный вход "1" дискретно-аналогового устройства, значения сигнала, поступающего на первый информационный вход А' дискретно-аналогового устройства. Во втором аналоговом вычитателе 1.2 производится вычитание из сигнала, поступающего на дополнительный информационный вход "1" дискретно-аналогового устройства, значения сигнала, поступающего на третий информационный вход С' дискретно-аналогового устройства. В первом аналоговом перемножителе 2.1 производится перемножение разностного сигнала, поступающего с информационного выхода первого аналогового вычитателя 1.1, с информационным сигналом, поступающим на второй информационный вход В' дискретно-аналогового устройства. Во втором аналоговом перемножителе 2.2 производится перемножение разностного сигнала, поступающего с информационного выхода второго аналогового вычитателя 1.2, с информационным сигналом, поступающим на четвертый информационный вход D' дискретно-аналогового устройства. В третьем аналоговом перемножителе 2.3 производится перемножение сигналов, поступающих с информационных выходов первого и второго аналоговых перемножителей 2.1, 2.2 соответственно. Результирующий сигнал поступает на информационный выход третьего аналогового перемножителя 2.3, являющийся информационным выходом Y' дискретно-аналогового устройства.

Устройство логических и арифметических операций с дискретными и аналоговыми значениями нулей и единиц, содержащее первый и второй аналоговые вычитатели и первый, второй и третий аналоговые перемножители, отличающееся тем, что введен дополнительный информационный вход устройства, на который поступает сигнал с уровнем логической единицы, причем дополнительный информационный вход устройства является первым информационным входом первого и второго аналоговых вычитателей, в которых производится вычитание из сигнала, поступающего на дополнительный информационный вход, значения сигнала, поступающего на первый и, соответственно, на третий информационные входы устройства, являющиеся вторыми информационными входами первого и второго аналоговых вычитателей соответственно, информационный выход первого аналогового вычитателя соединен с первым информационным входом первого аналогового перемножителя, второй информационный вход устройства является вторым информационным входом первого аналогового перемножителя, информационный выход которого соединен с первым информационным входом третьего аналогового перемножителя, информационный выход второго аналогового вычитателя соединен с первым информационным входом второго аналогового перемножителя, четвертый информационный вход устройства является вторым информационным входом второго аналогового перемножителя, информационный выход которого соединен со вторым информационным входом третьего аналогового перемножителя, информационный выход которого является информационным выходом устройства.