Многоканальный перепрограммируемый цифровой приемный тракт

Иллюстрации

Показать всеИзобретение относится к области цифровой обработки сигнала в приемных устройствах. Перепрограммируемый цифровой приемный тракт обеспечивает работу в различных стандартах связи и содержит, в том числе, несколько каналов, каждый из которых может использоваться как независимый канал, частотно разделенный от других, при этом цифровой гетеродин предназначен для переноса спектра сигнала с промежуточной частоты на нулевую частоту, с выхода гетеродина сигнал поступает на фильтр-дециматор. Порядок фильтра может быть изменен за счет возможности отключения каскадов фильтров, образующих фильтр-дециматор. От порядка и степени фильтра, а также от спектральной плотности мощности входного сигнала зависит коэффициент усиления, устанавливаемый в блоке амплитудно-фазовой коррекции. Наличие маршрутизаторов позволяет подключать любой из входов к любому из выходов блока децимации. Наличие в составе маршрутизаторов наряду с коммутаторами сумматоров позволяет выполнять объединение любой пары каналов. Технический результат заключается в создании цифрового перепрограммируемого мультистандартного приемника, использующего цифровую промежуточную частоту и обеспечивающего высокую скорость обработки сигнала при высокой функциональной гибкости и надежности. 8 з.п. ф-лы, 10 ил.

Реферат

Область техники

Настоящее изобретение относится к области цифровой обработки сигнала в приемных устройствах и более точно касается перепрограммируемого мультистандартного приемника и многоканального перепрограммируемого цифрового приемного тракта. Изобретение предназначено для решения различных фильтровых задач, в том числе при приеме сигналов систем связи, организуемых по стандартам IS-95, GSM, IS136, EDGE, PHS, 3GPP, 3GPP2 и т.п., а также при построении фазированных антенных решеток различных типов и в других многоканальных приложениях. Особенно эффективно использовать данное изобретение при построении многоцелевых перепрограммируемых устройств.

Уровень техники

На современном этапе развития техники в приемных устройствах все большая часть обработки сигнала выполняется в цифровом виде. При этом одной из самых сложных с точки зрения физической реализации задач является предварительная обработка сигнала, выполняемая до декодирования и выделения информации: цифровое гетеродинирование, децимация и фильтрация сигнала по полосе.

Особенно актуальна эта проблема при построении перепрограммируемых мульти-стандартных приемопередатчиков (так называемая технология SDR - Soft Definable Radio), использующих цифровую промежуточную частоту (ПЧ), при этом главным ограничением выступает ограничение по скорости обработки сигнала. Объектом изобретения по настоящей заявке является перепрограммируемый цифровой приемный тракт (тракт приема сигнала).

В современной связной аппаратуре наиболее часто используются следующие три типа приемных устройств:

- Супергетеродинный.

- С прямым преобразованием.

- Супергетеродинный с цифровой ПЧ.

Каждый из перечисленных приемников имеет свои преимущества и недостатки, а следовательно, и область применения. Возможности цифровой обработки на современном этапе развития достаточно высоки, а стоимость устройств цифровой обработки неуклонно падает. В связи с этим привлекательность цифровой обработки возрастает и появляется возможность построения перепрограммируемых приемных устройств в концепции SDR.

Концепция SDR обычно понимается следующим образом. Можно спроектировать перепрограммируемое приемное устройство и при помощи такого перепрограммируемого приемника обеспечивать требования множества стандартов связи. Сложность и стоимость такого приемника на настоящий момент высока. Вследствие этого, концепция SDR находит применение пока только в базовых станциях.

Одной из составных частей концепции SDR является использование цифровой ПЧ (Digital IF) и перепрограммируемых устройств частотной селекции сигнала. Приемники с цифровой ПЧ являются на настоящий момент быстро развивающейся областью, находящей применение в современных базовых станциях 2-3 поколения. Использование цифровой ПЧ стало реальностью благодаря появлению высокоскоростных АЦП с большой разрядностью и высокой линейностью и высокопроизводительных устройств цифровой обработки сигналов.

Отличительной особенностью устройств, предназначенных для реализации цифровой ПЧ, является наличие скоростного квадратурного гетеродина ("конвертора" частоты), из-за чего такие устройства часто называют DDC (Digital Down Converter - цифровой понижающий преобразователь частоты). Наиболее часто их реализуют в виде специализированных интегральных микросхем (ИМС). Лидерами в разработке и производстве DDC являются такие фирмы как Analog Devices, Intersil и Texas Instruments. Наиболее полная информация о предлагаемых на сегодняшний день устройствах этого класса и их параметрах доступна на сайтах производителей (www.analog.com, www.intersil.com, www.ti.com).

Фирма Analog Devices выпустила на рынок серию микросхем цифровой ПЧ. Наиболее близки к заявленному техническому решению следующие из них: AD6620, AD6634, AD6635, AD6652, которые можно рассматривать как функциональные аналоги. Далее кратко рассмотрим каждый из них для пояснения технической задачи, лежащей в основе изобретения.

Микросхема AD6620 [65 MSPS Digital Receive Signal Processor AD6620. Analog Devices, Inc., 1998] - первая микросхема этой серии, в которой была практически реализована концепция перепрограммируемого цифрового приемного тракта. Входной интерфейс микросхемы обеспечивает работу в нескольких режимах, при этом в зависимости от режима работы изменяются максимально допустимые тактовые частоты.

Гетеродин AD6620 построен табличным способом формирования опорных частот с использованием так называемых LUT (Look Up Table) - записанных опорных таблиц, содержащих отсчеты косинуса и/или синуса. Кроме этого, гетеродин AD6620 позволяет декоррелировать шумы квантования, используя методы фазового преобразования и амплитудного преобразования - Phase Dither и Amplitude Dither, для улучшения показателя SFDR (spurious-free dynamic range).

Фильтровое поле AD6620 состоит из последовательно соединенного каскада фильтров: CIC2 и CIC5 фильтры (представляющие собой Cascaded Integrator Comb фильтры с конечной импульсной характеристикой (КИХ) второй и пятой степени соответственно), а также RCF фильтр (RAM Coefficient FIR фильтр). Возможность использования микросхемы для обработки сигналов определяется производительностью каналообразующего RCF фильтра при выбранной частоте дискретизации сигнала. Недостатком этой ИМС можно считать низкую производительность RCF фильтра для обработки широкополосных сигналов, таких как сигналы стандартов сотовой связи IS-95, 3GPP и 3GPP2. Для обработки широкополосного сигнала необходимо проектировать полифазную структуру. Поскольку данная ИМС содержит только один канал, необходимо использовать несколько микросхем AD6620, что значительно повышает стоимость системы и ее габариты.

Этот недостаток устранен в ИМС AD6634, представляющей собой четырехканальный высокоскоростной DDC. Входной интерфейс обеспечивает работу с двумя высокоскоростными аналого-цифровыми преобразователями (АЦП). Структура одного канала микросхемы аналогична структуре AD6620. Отличия заключаются в наличии передискретизатора в CIC2 (resampler - устройство, изменяющее частоту дискретизации сигнала в нецелое число раз, например 3/4).

Основные преимущества данной микросхемы перед AD6620 заключаются в наличии 4-х идентичных каналов и возможности их перекоммутирования по входам к одному или двум внешним АЦП. Отличительной особенностью микросхемы является наличие перекрестных связей между 4-мя каналами после децимации. Это позволяет децимировать сигнал в одном канале, а для канальной фильтрации использовать четыре RCF фильтра, построив тем самым полифазную структуру, позволяющую обрабатывать широкополосные сигналы.

ИМС AD6635 является дальнейшим развитием технологии, первоначально реализованной в устройствах AD6620/AD6634 и представляет собой четырехвходовой (предусматривающий возможность работы с 4 внешними АЦП), восьмиканальный DDC. За исключением общего входного коммутатора, подключающего каждый из каналов к одному из входов, эта ИМС представляет собой два интегрированных в один корпус четырехканальных устройства, идентичных AD6634.

Технические решения, представляемые компанией Intersil, реализованы в микросхемах HSP50016 и HSP50216.

Структура одноканального DDC HSP50016 подобна структуре микросхемы AD6620: децимация сигнала выполняется с помощью CIC фильтра пятой степени, канальная фильтрация осуществляется RCF фильтром. В гетеродине данной ИМС отсутствует схема декорреляции шума при помощи Phase Dither и Amplitude Dither. Это устройство, так же как и AD6620, предназначено преимущественно для узкополосных приложений.

Микросхема HSP50216 представляет собой четырехвходовое, четырехканальное устройство. Структура данной ИМС подобна описанной выше структуре AD6634. Каждый из 4-х каналов состоит из блока коммутации к одному из входов, конвертора формата принимаемых данных, гетеродина, CIC фильтра, RCF фильтра, выходного АРУ и преобразователя из декатровских в полярные координаты. Степень используемого CIC фильтра может изменяться программным путем от 1 до 5. В отличие от Analog Devices, Intersil располагает передискретизатор сигнала не в первых каскадах фильтрового поля, а непосредственно в RCF фильтре. Одновременное использование ресурсов всех 4-х каналов обработки так же как и в случае AD6634 позволяет создать полифазную структуру фильтрации и обрабатывать широкополосные стандарты связи. Для этого между CIC и RCF фильтрами введен маршрутизатор сигнала (Bus Routing), а на выходе ИМС установлен блок, управляющий выдачей отфильтрованных потоков и преобразующий сигнал к необходимому формату представления данных.

Корпорацией Texas Instruments были разработаны две ИМС, каждая из которых представляет собой четырехканальный DDC: микросхема GC4014 и результат ее усовершенствования GC4016.

Микросхема GC4016 отличается гибким входным интерфейсом, позволяющим работать с данными, как с фиксированной точкой, так и с плавающей. Децимация сигнала в микросхеме осуществляется в три этапа. При этом общий коэффициент децимации микросхемы зависит от режима работы: каждый канал обрабатывает свой входной сигнал, обрабатывается сигнал одного источника двумя каналами микросхемы или же в обработке сигнала одного источника задействованы все четыре канала. Первый этап децимации реализован на CIC фильтре пятой степени, после которого реализована грубая регулировка усиления, доступная пользователю. Второй этап децимации реализован на КИХ-фильтре 21 порядка. Помимо децимации на КИХ-фильтр возложена коррекция частотной характеристики сигнала после CIC фильтра. Возможности реализации канальных фильтров ограничены фильтром 63-го порядка. Структура гетеродина микросхемы реализована аналогично реализациям других производителей. В гетеродине присутствует схема декорреляции шума при помощи Phase Dither.

Наиболее близким техническим решением к заявляемому изобретению (ближайший аналог) является многоканальный перепрограммируемый цифровой приемный тракт, выполненный в виде микросхемы AD 6652. На настоящее время это последняя разработка фирмы Analog Devices. Микросхема AD6652 [12-Bit, 65 MSPS IF to Base Band Diversity Receiver AD6652. Analog Devices, Inc., 2002] включает в себя лучшие технические решения, реализованные в вышеописанных предыдущих микросхемах этой фирмы, а также имеет дополнительно два встроенных АЦП. Микросхема представляет собой четырехканальный DDC и разбита на два логических блока: двухканальный высокоскоростной аналого-цифровой тракт и четырехканальный сигнальный процессор. Блок-схема данной ИМС показана на Фиг.1.

Важнейшим узлом аналого-цифрового тракта микросхемы являются два интегрированных АЦП. Технологически АЦП представляют собой наиболее критический узел при практической реализации, во многом определяющий параметры всей системы в целом.

Каждый из четырех каналов цифровой обработки сигнального процессора включает в себя цифровой гетеродин, блок CIC-децимаци и блок фильтрации-децимации. В целом, основные узлы сигнального процессора, определяющие фильтровые характеристики микросхемы имеют архитектуру и параметры аналогичные AD6634.

Входом устройства являются два АЦП (блоки 1 и 2), обрабатывающие действительные аналоговые сигналы (SRC1 и SRC2). Каждый из АЦП, посредством входного интерфейса может быть подключен к любому из каналов обработки. Для тактирования АЦП используется внешний сигнал "Encode".

Входные данные могут представлять собой сигнал на промежуточной частоте (два независимых сигнала подаются на два входа) или сигнал на нулевой частоте (каждая компонента комплексного сигнала подается на свой АЦП). Это позволяет использовать ИМС как в приложениях с цифровой ПЧ, так и в системах связи с прямым переносом частоты в аналоговом виде.

Цифровой квадратурный гетеродин (блоки 4-7) обеспечивает перенос спектра входного действительного сигнала с промежуточной частоты на нулевую частоту, умножая отсчеты входного сигнала на отсчеты опорного сигнала sin(ωt) t) и cos(ωt). Выдаваемый с выхода входного интерфейса (блок 3) сигнал всегда представлен в комплексном виде. При необходимости, гетеродинирование может быть выключено при помощи мультиплексоров 8-11.

Блоки 12-15 CIC децимации строятся на основе фильтров дециматоров второго и пятого порядков (CIC2 и CIC5) и выполняют предварительную децимацию сигнала. В устройствах реализована возможность отключения каскада децимации на основе фильтра CIC2.

С выхода блока CIC децимации сигналы всех каналов поступают на коммутатор 16, выполняющий подключение выходов этих блоков ко входам (одному или нескольким) блоков 17-20 фильтрации-децимации. Блоки 17-20 фильтрации-децимации выполнены в прототипе с использованием RCF - фильтра и предназначены для получения требуемой согласно условиям эксплуатации устройства спектральной маски. В устройстве-прототипе предусмотрена возможность регулирования коэффициента усиления на выходе каждого из дециматоров, позволяющая ограничить разрядность сигнала и реализовать грубую регулировку уровня сигнала.

Отфильтрованный сигнал подается на вход второго коммутатора (блоки 21), который позволяет сразу передать его в выходной интерфейс либо пропустить через один из двух блоков, а именно через блок интерполяции и АРУ (блоки 22 и 23, соответственно).

Выходной интерфейс (блок 24) предназначен для формирования выходного потока в удобном для пользователя формате. В описании к данной микросхеме указано, что выходной интерфейс представляет собой два независимых порта, каждый из которых может быть включен в режиме линк порта ("LINK") или параллельного порта ("Parallel")

Общее управление и синхронизацию потоков и блоков устройства выполняет блок синхронизации (блок 26), формирующий необходимые для совместной работы всех блоков тактовые и управляющие сигналы (формирователь внутренних стробирующих сигналов обработки и генерации адресов для блоков памяти). При этом может использоваться сигнал внешней синхронизации "SYNC". Для задания всех параметров функционирования устройства используется установка соответствующих значений в регистрах управления (блок 25) посредством сигнала установки "SPI".

Ограничения описанного ближайшего аналога состоят в недостаточной функциональной гибкости реализованных каскадов, не позволяющей реализовать оптимальные фильтровые решения в ряде приложений. Сложность схемотехнической реализации устройств с использованием прототипа также является его недостатком. В частности, обязательное использование встроенных АЦП ограничивает возможности использования всех заложенных в устройство ресурсов, а также исключает возможность использования альтернативного АЦП или обработки сигнала, поступающего на вход устройства в цифровом виде. В ряде случаев отсутствие такой возможности не только снижает диапазон функциональных возможностей данной ИМС как перепрограммируемого устройства, но и может оказаться критичным с точки зрения надежности реализуемого на базе ИМС конечного устройства. Еще одно ограничение накладывается отсутствием блока хранения-выдачи отсчетов на выходе устройства. Это не позволяет выдавать отфильтрованные отсчеты в асинхронном режиме, который часто реализуется при использовании для дальнейшей обработки сигнала микропроцессоров. Также ограничены возможности блока синхронизации, не позволяющего одновременно синхронизировать работу нескольких ИМС.

Раскрытие изобретения

В основу настоящего изобретения положена техническая задача создать цифровой перепрограммируемый мультистандартный приемник (приемный тракт), использующий цифровую промежуточную частоту (ПЧ), обеспечивающий высокую скорость обработки сигнала при высокой функциональной гибкости и надежности.

Многоканальный перепрограммируемый цифровой приемный тракт согласно настоящему изобретению должен обеспечивать возможность реализации высокоскоростных трактов фильтрации сигнала при построении радиоаппаратуры систем связи. В частности, устройство по настоящему изобретению должно обеспечивать возможность:

- Использовать устройство для реализации мультистандартных перепрограммируемых приемопередатчиков (концепция Soft Definable Radio).

- Использовать при построении приемопередатчиков фазированные антенные решетки и организовывать направленную передачу и прием сигнала (алгоритмы умной антенны и пространственной селекции помех).

- Реализовывать с использованием нескольких ИМС:

- многоканальные приемники сигнала с частотным разделением каналов, такие как приемник Глонасс;

- устройства защиты от узкополосных помех на основе гребенки фильтров (параллельный анализатор спектра).

- Решать широкий спектр фильтровых задач, среди которых:

- построение трактов фильтрации с высокой избирательностью и прямоугольностью;

- блоки преобразования частоты сигнала и изменения частоты дискретизации сигнала и т.п.;

- построение трактов фильтрации сигнала с использованием цифровой промежуточной частоты, существенно упрощающих реализацию смежных с ними аналоговых трактов.

Согласно поставленной задаче устройство по настоящему изобретению должно иметь большую гибкость за счет наличия нескольких идентичных каналов приема, каждый из которых может использоваться как независимый канал, частотно разделенный от остальных. Это позволяет, с одной стороны, реализовывать системы со сложной многоканальной структурой сигналов (cdma2000 3х), а, с другой стороны, оптимально перераспределять ресурсы при обработке сигналов с высокой тактовой частотой (UMTS, 802. 11b).

Возможность использования высокой тактовой частоты обработки сигналов делает перспективным использование устройства по настоящему изобретению при построении высокоскоростных систем передачи данных. Удобный интерфейс заявляемого устройства позволяет при необходимости построения многоканальной структуры легко сопрягать несколько таких устройств между собой, и, кроме того, согласован с интерфейсом цифровых сигнальных процессоров и ряда периферийных устройств.

Простота переконфигурирования устройства позволяет использовать его для построения портативных мультистандартных терминалов, совмещающих в себе, например, функции устройства позиционирования при помощи глобальной сети навигации и мобильного терминала системы сотовой связи.

Поставленная задача решается за счет того, что согласно настоящему изобретению предложен многоканальный перепрограммируемый цифровой приемный тракт, который содержит входной интерфейс, первый и второй аналого-цифровой преобразователь, подключенные последовательно между входным интерфейсом и, по меньшей мере, двумя имеющимися в тракте идентичными каналами передачи сигнала, выполненными с возможностью выполнения функции аналогово-цифрового преобразования, гетеродинирования, децимации и канальной фильтрации входного сигнала, причем в каждом из каналов использованы последовательно соединенные гетеродин, мультиплексор и блок децимации сигнала, а также первый блок фильтрации-децимации, причем каждый их каналов выполнен с возможностью использования, по меньшей мере, двух маршрутизаторов (также в ряде источников из уровня техники обозначаемых как коммутаторы-маршрутизаторы), предназначенных для распределения сигналов, причем все каналы выполнены с возможностью вывода обработанного сигнала через общий выходной интерфейс, к которому они подключены, причем приемный тракт включает также регистр управления и блок синхронизации, приспособленные для осуществляется управления процессом приема, обработки и передачи сигнала, отличающийся тем, что каждый из каналов дополнительно включает соединенные последовательно второй блок фильтрации-децимации и блок амплитудно-фазовой коррекции сигнала, соединенные с блоком хранения-выдачи отсчетов, причем блок синхронизации выполнен с возможностью синхронизировать независимо работу, по меньшей мере, двух устройств, а каждый из маршрутизаторов выполнен с возможностью не только коммутировать входы и выходы блоков, но и выполнять при необходимости суммирование сигналов двух любых каналов, причем тракт дополнительно включает цифровые входы, выполненные параллельно аналого-цифровым преобразователям, приспособленные для получения входного действительного или комплексного сигнала и передачи его для дальнейшей обработки в тракте в обход аналого-цифровых преобразователей.

Предпочтительным является использование, по меньшей мере, четырех соединенных параллельно идентичных каналов, что обеспечивает лучшую работу предлагаемого устройства.

Предпочтительно блок децимации сигнала включает две ветви фильтрации, каждая из которых включает последовательно соединенные первый фильтр, включающий первый дециматор и первый блок масштабирования, первый мультиплексор, второй фильтр, включающий второй дециматор и второй блок масштабирования, второй мультиплексор, причем первые блоки масштабирования и вторые блоки масштабирования связаны между собой через устройство логического "или". Предпочтительно, второй фильтр выполнен с возможностью программного изменения свойств фильтра с 4-го до 6-го порядка включительно.

Предпочтительно маршрутизатор включает демультиплексор, соединенный с комплексными сумматорами, построенными с использованием сумматора и мультиплексора, причем количество комплексных сумматоров соответствует числу каналов передачи сигнала в тракте, причем выходы каналов соединены с устройством коммутатора.

Преимущественно первый и второй блоки фильтрации-децимации включают комплексный фильтр, использующий одну и туже память коэффициентов и две независимые системы памяти данных. Предпочтительно в качестве комплексного фильтра использован фильтр с конечной импульсной характеристикой.

Предпочтительно тракт по настоящему изобретению содержит дополнительно, по меньшей мере, один АЦП. Предпочтительно тракт по настоящему изобретению выполнен в виде специализированной интегральной микросхемы (аналого-цифровая система на кристалле).

Предпочтительный вариант осуществления изобретения.

Настоящее изобретение будет понятно специалисту в данной области из приведенного ниже подробного описания вариантов его осуществления, а также примеров практической реализации устройства по настоящему изобретению и его составных частей. Подробное описание будет вестись со ссылками на чертежи, на которых однотипные блоки разных устройств обозначены одними позициями для удобства сравнения.

На чертежах показано следующее:

на Фиг.1 показана блок-схема устройства-прототипа;

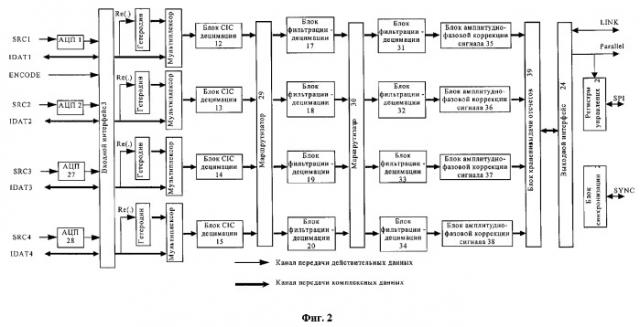

на Фиг.2 - блок-схема устройства по настоящему изобретению;

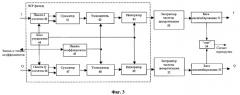

на Фиг.3 - схема реализации блока CIC децимации по настоящему изобретению;

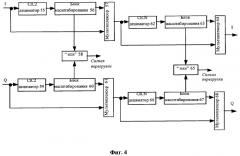

на Фиг.4 - схема реализации блока фильтрации-децимации по настоящему изобретению;

на Фиг.5 - схема реализации CICN фильтра-дециматора по настоящему изобретению;

на Фиг.6 - схема реализации маршрутизатора по настоящему изобретению;

на Фиг.7 - схема реализации квадратурного гетеродина по настоящему изобретению;

на Фиг.8 - блок-схема блока синхронизации по настоящему изобретению;

на Фиг.9 - блок-схема генератора опорного сигнала (Sin(ωt) и Cos(ωt));

на Фиг.10 - блок-схема приемника с цифровой ПЧ.

Блок-схема многоканального перепрограммируемого цифрового приемного тракта согласно настоящему изобретению, например, для случая четырех параллельных каналов обработки показана на Фиг.2

Цифровой приемный тракт содержит четыре идентичных канала, реализующих функции аналогово-цифрового преобразования, гетеродинирования, децимации и канальной фильтрации входного сигнала.

Входной интерфейс (блок 3) позволяет работать с дифференциальным аналоговым и комплексными (двухкомпонентными) цифровыми сигналами. В основе входного интерфейса лежит коммутатор, посредством которого каждый из каналов обработки может быть без ограничений подключен к любому из источников сигнала. Входной интерфейс способен принимать до 4 потоков действительных аналоговых или до 2 потоков комплексных аналоговых данных (входы SRC1-SRC4 устройства) и до 4 потоков комплексных цифровых данных (входы IDAT1-IDAT4). При этом цифровые входы IDAT1-IDAT4 являются двунаправленными и могут использоваться как для загрузки в устройство входных отсчетов, так и для вывода за пределы устройства оцифрованного сигнала с выхода АЦП. На выходе у устройства с выходного интерфейса могут быть получены сигналы LINK, Parallel. Кроме того, регистр 4 управления выдает сигнал SPI, а блок 26 синхронизации выдает сигнал SYNC.

Входные данные могут представлять сигнал на промежуточной или нулевой частоте, что позволяет использовать данное техническое решение как в приложениях с цифровой ПЧ, так и в системах связи с прямым переносом частоты в аналоговом виде.

Так же как и в случае прототипа, цифровой квадратурный гетеродин обеспечивает перенос спектра входного действительного сигнала с промежуточной частоты на нулевую частоту, умножая отсчеты входного сигнала на отсчеты опорного сигнала sin(ωt) и cos(ωt). Выдаваемый с выхода входного интерфейса сигнал всегда представлен в комплексном виде. Поскольку гетеродин предназначен для обработки действительного сигнала (обычно это сигнал ПЧ), на его вход поступает только одна из компонент - его реальная часть. Блок-схема гетеродина (блоки 4-7 на Фиг.2) показана на Фиг.7.

Генератор опорной частоты формирует отсчеты sin(ωt) и cos(ωt) с нужной для преобразования частотой ω, обычно равной несущей частоте входного сигнала (частоте ПЧ). Устанавливаемые пользователем значения частоты генерируемого сигнала и начального сдвига фазы записываются в соответствующие управляющие регистры, откуда поступают в гетеродин. Генератор шума 106 формирует сигнал, представляющий собой псевдослучайный шумовой сигнал с нулевым математическим ожиданием и равномерной функцией распределения амплитуды.

Генератор фазы 102 представляет собой совокупность интегратора 108 с переполнением и сумматоров 109 и 110. Интегратор с переполнением представляет собой сумматор с ограниченной разрядностью. В результате непрерывного прибавления (накопления) кода частоты происходит естественное переполнение, обусловленное конечной разрядностью, и в интеграторе снова начинается накопление до достижения следующего переполнения. В результате работы блока формируется адрес для генератора 103 опорного сигнала гетеродина. Физический смысл адреса, генерируемого в блоке, представляющем собой генератор фазы 102, - это значение фазы ϕ опорного сигнала.

На Фиг.9 показана структура генератора 103 опорного сигнала гетеродина. Общий принцип формирования опорных сигналов гетеродина основан на последовательной выборке из таблицы значений отсчетов с определенным шагом. Изменением шага считывания достигается установка требуемого значения частоты. Генератор представляет собой устройство, выполняющее кусочно-линейную аппроксимацию функций синуса и косинуса. Аппроксимация каждого отсчета Sin(.) и Cos(.) вычисляется с использованием двух таблиц, для чего в устройстве используются пары таблиц: блоки 111 и 112 и блоки 113 и 114. Первая таблица содержит отсчеты синуса или косинуса, вторая - поправочные коэффициенты.

Работает устройство следующим образом. В таблицах хранятся отсчеты четверти периода синуса и косинуса, взаимно дополняющие друг друга до половины периода. Поступающий на вход генератора 103 k-разрядный адрес разделяется на:

- n старших разрядов;

- k-n младших разрядов - используются для вычисления аддитивной добавки к отсчетам основной таблицы (Sin(.) и Cos(.))

Старшие разряды в свою очередь делятся на:

- 2 старших разряда из n - используются для управления коммутатором 115 и вычисления знака отсчетов;

- n-2 оставшихся разрядов ("средних" относительно исходного k-разрядного адреса) являются непосредственно адресом для всех 4-х таблиц (блоки 111-114).

Коммутатор 115 в зависимости от значения второго по старшинству бита коммутирует входные сигналы напрямую (sin→sin и cos→cos) или перекрестно (sin→cos и cos→sin). Знак отсчетов опорного сигнала определяется по следующему правилу:

- для синуса знаком является старший бит k-разрядного адреса (0 это "+", 1 это "-"); для реализации этого правила используются перемножитель 122 и преобразователь 123 формата;

- для косинуса знак определяется по 2-м старшим битам 18-разрядного адреса (если биты равны, то знак "+", в противном случае "-"); это правило реализуется при помощи перемножителя 120, схемы 121 "исключающего или" и преобразователя 124 формата.

Преобразователи формата 123 и 124 выполняют преобразование без знаковых сигналов в знаковые: "0" в "1" и "1" в "-1".

Выходной поток перемножителей 122 и 120 выдается на выход генератора 103 и используется собственно для переноса сигнала по частоте в перемножителях 104 и 105 (см. Фиг.7). Округлитель 107 сокращает избыточную разрядность после гетеродинирования путем отбрасывания части младших разрядов с округлением.

Гетеродины двух каналов могут быть объединены для обработки комплексного входного сигнала. Для этого реальная часть сигнала подается на вход гетеродина одного канала, а мнимая часть сигнала поступает на вход гетеродина другого канала. В маршрутизаторах 29 или 30, в зависимости от используемой пользователем схемы перераспределения ресурсов эти два потока данных объединяются, образуя единый комплексный сигнал.

Сигнал с выхода входного интерфейса через мультиплексоры 8-11 может подаваться сразу (минуя любой из гетеродинов, блоки 4-7) на вход соответствующих блоков 12-15 CIC децимации сигнала.

Блоки 12-15 CIC децимации (блоки децимации согласно формуле изобретения) предназначены для предварительной децимации сигнала. Основу блока составляют фильтры с единичными коэффициентами. Применение этих фильтров эффективно при больших значениях децимации и высоких тактовых частотах обработки сигнала. Данный блок может быть реализован, например, в виде структуры, изображенной на Фиг.4.

Как показано на Фиг.4, каждая из квадратурных компонент сигнала (I и Q) поступает на свою ветвь фильтрации, состоящую из последовательно соединенных CIC2 (блоки 55 и 59) и CICN дециматоров (блоки 62 и 66). При необходимости каждый из этих фильтров может быть выключен посредством мультиплексоров 57, 61, 64 и 68.

Оба каскада CIC децимации построены по известной из уровня техники схеме Хогенауэра [Reduced complexity comb-filters for decimation and interpolation in mobile communications terminals. Tim Hentschel, Gerhard Fettweis]. Особенности этой схемы заключаются в том, что фильтр дециматор, выполняющий внеполосную фильтрацию сигнала, интегрирован в единое целое с экстрактором частоты дискретизации, выполняющим непосредственно прореживание отсчетов сигнала. В отличие от прототипа второй каскад CIC децимации сделан перестраиваемым: порядок используемого фильтра CICN может программно изменяться от CIC4 до CIC6. В схеме Хогенауэра это достигается путем размыкания/замыкания цепей обратной связи в интеграторах и цепей прямой связи в дифференциаторах.

На Фиг.5 показан пример реализации такого фильтра перестраиваемого от CIC4 до CIC6. Схема Хогенауэра представляет собой каскадное соединение набора интеграторов 69-74, экстрактора 75 частоты дискретизации и дифференциаторов 76-81. Количество интеграторов равно количеству дифференциаторов, а количество задействованных пар интегратор-дифференциатор определяет порядок CIC фильтра. Структура неотключаемых интеграторов 69-72 и дифференциаторов 76-79 раскрыта на примере блоков 69 и 76 и в таком виде понятна специалисту, и не требует дополнительных пояснений. В отключаемые интеграторы 73 и 74 дополнительно введен ключ, позволяющий разомкнуть цепь обратной связи. В результате этого сигнал пропускается со входа на выход без изменений. Аналогично в отключаемых дифференциаторах 80 и 81 посредством ключа выполняется замыкание/размыкания цепи прямой связи.

Для регулирования коэффициента усиления на выходе каждого из дециматоров CIC2 и CICN установлен блок масштабирования (блоки 56, 60, 63 и 67), позволяющие ограничить разрядность сигнала и выбрать, какие из разрядов с выхода дециматора будут использованы для дальнейшей обработки. При помощи этих блоков в данных точках возможна грубая регулировка уровня сигнала с шагом в 6 дБ. Такой блок может быть реализован, например, как мультиплексор, коммутирующий в соответствии с установленным значением в управляющих регистрах часть своих входов (параллельно поступающих разрядов многоразрядного числа) на выходы, при этом количество выходов равно требуемой разрядности числа после ограничения.

В процессе ограничения сигнала возможно возникновение превышения сигналом допустимой разрядности. В некоторых приложениях это ограничение может привести к ухудшению характеристик приемного устройства. Для отслеживания подобных ситуаций здесь и в других точках ограничения разрядности вырабатывается контрольный сигнал перегрузки (блоки 58 и 65).

С выхода блока CIC децимации сигналы всех каналов поступают на соответствующие входы маршрутизатора 29 (также обозначаемого как коммутатор-маршрутизатор), построенного на основе коммутатора. В отличие от использованных в прототипе коммутаторов в состав данного блока входят сумматоры (четыре в данном случае), выполняющие объединение сигналов любой пары каналов. Это связано с упомянутым ранее режимом обработки комплексного сигнала с гетеродинировнием и необходимо для формирования квадратурных компонент сигнала после комплексного переноса частоты.

Маршрутизаторы 29 и 30, так же как и входной интерфейс, позволяют подключать любой из входов к любому из выходов данного блока без каких бы то ни было ограничений и перенаправлять таким образом потоки данных для объединения вычислительных ресурсов блоков обработки. За счет указанных маршрутизаторов обеспечиваются преобразование частоты комплексного входного сигнала и повышение производительности КИХ фильтров. Так, при реализации устройства на современной элементной базе, в случае объединения четырех каналов в один, частота дискретизации сигнала на выходе блока фильтрации-децимации может достигать 10 МГц для фильтра 64-го порядка при тактовой частоте 80 МГц. Такие параметры позволяют выполнить требования фильтрации практически всех известных стандартов связи.

Структура маршрутизатора для случая 4-х каналов обработки раскрыта на Фиг.6. На рисунке символами I и Q с цифровым индексом обозначены комплексные сигналы обрабатываемых каналов. Демультиплексор 92 может подключить сигналы из двух любых каналов ко входу одного из комплексных сумматоров (блоки 93-96). Сигнал с выхода любого из комплексных сумматоров через коммутатор 97 может быть передан в любой из 4-х каналов обработки.

Структура комплексных сумматоров раскрыта на примере блока 93. В качестве примера показано прохождение сигнала через данный блок при суммировании сигналов первого и второго канала. Сумматоры 98 и 99 суммируют реальные и мнимые части сигналов двух каналов и передают суммы на вход мультиплексоров 100 и 101. Мультиплексоры позволяют выбрать, какой сигнал будет передан на выход комплексного сумматора, то есть блока 93: в данном примере это выбор между сигналом первого канала обработки или суммой сигналов первого и второго каналов.

Как видно из Фиг.2, маршрутизаторы 29 и 30 и блоки 16, 17, 18, 19, 31, 32, 33 и 34 фильтрации-децимации соответственно образуют два одинаковых каскада обработки сигнала (последовательных). Такой подход позволяет при использовании гибко перераспределять ресурсы в соответствии с решаемыми задачами и упростить саму разработку в сложных случаях, например, когда нужно не только отфильтровать сигнал по полосе, но и скорректировать искажения АЧХ, внесенные предыдущими каскадами. Особенно актуально это при необходимости оперативной перестройки фильтра-корректора под изменяющиеся параметры аналоговых каскадов. При этом возможность дополнительной децимации в каждом их каскадов позволяет на каждом из этапов дополнительно понизить частоту обработки сигнала, а следовательно, понизить порядки фильтров и упростить реализацию.

Блоки 16, 17, 18, 19, 31, 32, 33 и 34 фильтрации-децимации могут быть реализованы, например, по схеме, показанной на Фиг.3. Данный блок состоит из комплексного RCF-фильтра, использующего одну и туже память коэффициентов и две независимые системы памяти данных. Приведенная структура рассчитана на использование фильтров с симметричной импульсной характеристикой, что позволяет выполнять одно умножение для двух отсчетов фильтруемого сигнала. Сумматоры 41 и 47 выполняют суммирование очередной пары отсчетов, после чего они умножаются на соответствующий коэффициент филь