Устройство для прогнозирования случайных событий

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для оценки надежности и качества функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, в которых используется циклический характер производства, предоставления телекоммуникационных услуг и временное резервирование. Техническим результатом является повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях неоднозначности (нечеткости) параметров моделируемых сигналов, характеризующих принадлежность конкретного сигнала состояния к пространству состояния безотказной работы системы либо к пространству отказов. Устройство содержит блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов, блок регистрации, блок контроля сигналов отказов, блок преобразования сигналов отказов, блок опознавания сигналов отказов, блок сравнения сигналов отказов. 6 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для оценке надежности и качества функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, в которых используется циклический характер производства, предоставления телекоммуникационных услуг и временное резервирование.

Известно устройство для прогнозирования случайных событий по ав. св. СССР №№ 1167619, G 06 F 15/46, 1985, бюл. № 14, содержащее блок управления, блок модели системы и блок регистрации.

Недостатком данного устройства является относительно большое время определения численных значений оценок показателей качества функционирования производственных систем с циклическим характером работы.

Известно устройство для прогнозирования случайных событий, содержащее блок модели системы, блок формирования сигналов отказов и блок регистрации (см. ав. св. СССР № 1198484, G 05 В 23/02, 1985, бюл. № 26).

Однако данное устройство имеет относительно большое время процесса оценивания показателей надежности сложных производственных систем с временным резервированием.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство для прогнозирования случайных событий (см. ав. св. СССР № 1441421, G 06 F 15/46, 1988, бюл. № 44), содержащее блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов и блок регистрации. При этом информационный вход блока регистрации подключен к информационному выходу блока формирования сигналов отказов, управляющий вход которого подключен к управляющему выходу блока модели системы. Сбросовый выход блока управления соединен с сбросовыми входами блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, М≥2 контрольных выходов блока управления подключены к соответствующим М контрольным входам блока модели системы. Синхронизирующий выход блока управления подключен к синхронизирующим входам блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации. Управляющий выход блока управления соединен с управляющим входом блока имитаторов состояний участков системы, N≥2 групповых входов которого подключены к соответствующим N групповым выходам блока модели системы, N групповых входов которого соединены с соответствующими N групповыми выходами блока имитаторов состояний участков системы. Вход блока управления подключен к выходу блока регистрации, сигнальный вход которого соединен с сигнальным выходом блока формирования сигналов отказов.

В прототипе реализуется возможность повышения скорости оценивания показателей надежности сложных производственных и телекоммуникационных систем с циклическим характером работы и временным резервированием.

Однако прототип имеет недостаток - относительно низкую достоверность идентификации состояния безотказной работы системы (выполнения сменных заданий за оперативное время) и противоположного состояния - отказа системы в условиях неоднозначности (нечеткости) параметров модели процесса функционирования исследуемой системы. Данное устройство позволяет с высокой достоверностью оценивать численные значения показателей надежности и качества функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, параметры моделей процессов функционирования которых заданы количественно и параметры состояния которых принимают однозначные, четко идентифицируемые значения, в то время как подавляющее большинство параметров состояния, задаваемых в интересах моделирования и, как следствие, подавляющее большинство результатов прогнозирования случайных событий в рамках реально функционирующей сложной системы с непополняемым временным резервом, объективно могут быть идентифицированы лишь на качественном уровне (неоднозначно, нечетко), с привлечением лингвистической переменной.

Под "наличием у производственной или телекоммуникационной системы и ее отдельных участков непополняемого временного резерва" понимается тот факт, что в процессе функционирования системы может быть израсходовано некоторое время для восстановления ее технических характеристик (восстановления отказавших в процессе функционирования системы агрегатов).

Под "оперативным временем" понимается время, выделяемое для выполнения системой задания. Временной резерв системы и ее участков образуется за счет увеличения времени, выделяемого для выполнения задания.

Под "отказом системы с непополняемым временным резервом" понимается несвоевременное выполнение сменного задания, т.е. отказ системы фиксируется тогда, когда оперативное время истекло, а сменное задание еще не выполнено.

Под "параметрами модели процесса функционирования исследуемой системы" понимаются исходные данные для моделирования - множество числовых значений характеристик свойств конкретного процесса в данный момент времени.

Под "результатами прогнозирования случайных событий" понимаются итоговые результаты моделирования - соотношение времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг).

Целью заявленного технического решения является создание устройства для прогнозирования случайных событий, обеспечивающего повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях неоднозначности (нечеткости) параметров моделируемых сигналов, характеризующих принадлежность конкретного сигнала состояния к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов, устройства, способного с высокой достоверностью идентифицировать соотношение ключевых параметров моделируемого процесса функционирования системы - времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг) в условиях, присущих реальному процессу функционирования производственной или телекоммуникационной системы с непополняемым временным резервом, когда исходные данные для моделирования и, как следствие, результаты прогнозирования случайных событий, обуславливающие численные значения показателей надежности и качества функционирования таких сложных систем, могут иметь как количественно, так и качественно (неоднозначно, нечетко, с привлечением лингвистической переменной) выраженный физический смысл.

Указанная цель достигается тем, что в известное устройство для прогнозирования случайных событий, содержащее блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов и блок регистрации, выход которого подключен к входу блока управления, управляющий вход блока формирования сигналов отказов подключен к управляющему выходу блока модели системы, сбросовый выход блока управления соединен с сбросовыми входами блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, М≥2 контрольных выходов блока управления подключены к соответствующим М контрольным входам блока модели системы, синхронизирующий выход блока управления подключен к синхронизирующим входам блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, управляющий выход блока управления соединен с управляющим входом блока имитаторов состояний участков системы, N≥2 групповых входов которого подключены к соответствующим N групповым выходам блока модели системы, N групповых входов которого соединены с соответствующими N групповыми выходами блока имитаторов состояний участков системы, дополнительно включены блок контроля сигналов отказов, блок преобразования сигналов отказов, блок опознавания сигналов отказов и блок сравнения сигналов отказов. При этом сбросовые и синхронизирующие входы блока контроля сигналов отказов, блока преобразования сигналов отказов, блока опознавания сигналов отказов и блока сравнения сигналов отказов подключены соответственно к сбросовому и синхронизирующему выходам блока управления. Информационный и сигнальный выходы блока сравнения сигналов отказов соединены соответственно с информационным и сигнальным входами блока регистрации. Информационный и сигнальный выходы блока формирования сигналов отказов соединены соответственно с информационным и сигнальным входами блока сравнения сигналов отказов, запирающий вход которого подключен к запирающему выходу блока контроля сигналов отказов, первичный и вторичный выходы которого соединены соответственно с первичным и вторичным входами блока преобразования сигналов отказов. Первичный и вторичный выходы блока преобразования сигналов отказов подключены соответственно к первичному и вторичному входам блока опознавания сигналов отказов, опознавательный выход которого соединен с опознавательным входом блока сравнения сигналов отказов. Вспомогательный выход блока опознавания сигналов отказов подключен к вспомогательному входу блока преобразования сигналов отказов. Контрольно-информационный и контрольно-сигнальный входы блока контроля сигналов отказов соединены соответственно с дополнительным контрольно-информационным и дополнительным контрольно-сигнальным выходами блока формирования сигналов отказов.

Блок контроля сигналов отказов состоит из контрольно-информационного и контрольно-сигнального дешифраторов, контрольного счетчика и контрольного анализатора. При этом входы контрольно-информационного и контрольно-сигнального дешифраторов являются соответственно контрольно-информационным и контрольно-сигнальным входами блока, выходы контрольно-информационного и контрольно-сигнального дешифраторов подключены соответственно к информационному и сигнальному входам контрольного счетчика, сбросовый и синхронизирующий входы которого являются соответственно сбросовым и синхронизирующим входами блока. Информационный и сигнальный выходы контрольного счетчика подключены соответственно к информационному и сигнальному входам контрольного анализатора, запирающий выход которого является запирающим выходом блока. Первичный и вторичный выходы контрольного анализатора являются соответственно первичным и вторичным выходами блока контроля сигналов отказов.

Блок преобразования сигналов отказов состоит из преобразующего счетчика-вычислителя, первичного и вторичного элементов хранения, первичного и вторичного элементов преобразования. Причем первичный и вторичный входы преобразующего счетчика вычислителя соединены соответственно с входом первичного и основным входом вторичного элементов хранения и являются соответственно первичным и вторичным входами блока. Выходы первичного и вторичного элементов хранения подключены соответственно к основным входам первичного и вторичного элементов преобразования, выходы которых являются соответственно первичным и вторичным выходами блока. Вспомогательный вход вторичного элемента хранения соединен с вспомогательным входом преобразующего счетчика-вычислителя и является вспомогательным входом блока. Вспомогательные входы первичного и вторичного элементов преобразования подключены соответственно к первичному и вторичному выходам преобразующего счетчика-вычислителя, сбросовый и синхронизирующий входы которого являются соответственно сбросовым и синхронизирующим входами блока преобразования сигналов отказов.

Блок опознавания сигналов отказов состоит из опознавательного счетчика-вычислителя и опознавателя уровня сигналов отказов. При этом выход опознавателя уровня сигналов отказов является опознавательным выходом блока, выход опознавательного счетчика-вычислителя подключен к входу опознавателя уровня сигналов отказов и является вспомогательным выходом блока, первичный и вторичный входы опознавательного счетчика-вычислителя являются соответственно первичным и вторичным входами блока, сбросовый и синхронизирующий входы опознавательного счетчика-вычислителя являются соответственно сбросовым и синхронизирующим входами блока опознавания сигналов отказов.

Блок сравнения сигналов отказов состоит из сравнивающего счетчика, отказного и исполнительного элементов И. Причем опознавательный вход исполнительного элемента И соединен с опознавательным входом отказного элемента И и является опознавательным входом блока, информационный и сигнальный выходы сравнивающего счетчика подключены соответственно к основным входам отказного и исполнительного элементов И, выходы которых являются соответственно информационным и сигнальным выходами блока. Запирающий вход сравнивающего счетчика является запирающим входом блока, информационный и сигнальный входы сравнивающего счетчика являются соответственно информационным и сигнальным входами блока. Сбросовый и синхронизирующий входы сравнивающего счетчика являются соответственно сбросовым и синхронизирующим входами блока сравнения сигналов отказов.

Блок формирования сигналов отказов состоит из элемента ИЛИ, основного и дополнительного счетчиков, основного и дополнительного дешифраторов. При этом сбросовый вход элемента ИЛИ является сбросовым входом блока, счетные входы основного и дополнительного счетчиков являются соответственно синхронизирующим и управляющим входами блока. Выход дополнительного дешифратора подключен к сигнальному входу элемента ИЛИ и является сигнальным выходом блока, выход элемента ИЛИ соединен с сбросовыми входами основного и дополнительного счетчиков, выходы которых подключены соответственно к входам основного и дополнительного дешифраторов и являются соответственно дополнительным контрольно-информационным и дополнительным контрольно-сигнальным выходами блока. Выход основного дешифратора является информационным выходом блока формирования сигналов отказов.

Благодаря новой совокупности существенных признаков, за счет введения блоков контроля сигналов отказов, преобразования сигналов отказов, опознавания сигналов отказов и сравнения сигналов отказов, обеспечивающих обработку и трансформирование нечетких параметров модели процесса функционирования исследуемой системы и, как следствие, нечетких результатов прогнозирования случайных событий к виду, пригодному для достоверной идентификации времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг), в заявленном устройстве достигается возможность предварительного анализа и верификации сигналов о выполнении сменного задания и сигналов отказов, обуславливающая повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях неоднозначности (нечеткости) параметров модели процесса функционирования исследуемой системы.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами, на которых представлены:

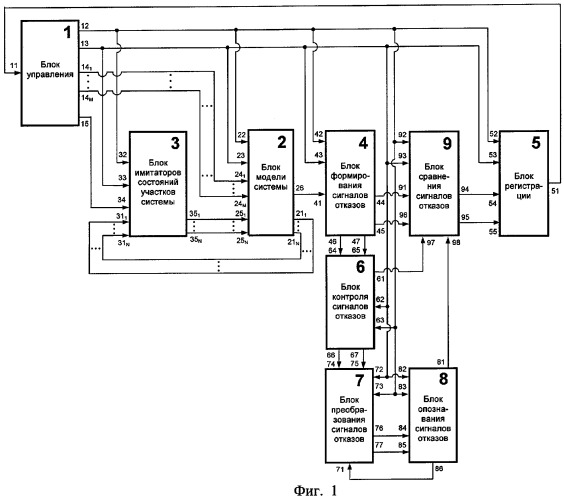

на фиг.1 - структурная схема устройства для прогнозирования случайных событий;

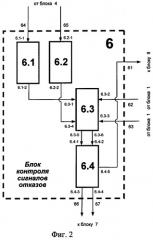

на фиг.2 - структурная схема блока контроля сигналов отказов;

на фиг.3 - структурная схема блока преобразования сигналов отказов;

на фиг.4 - структурная схема блока опознавания сигналов отказов;

на фиг.5 - структурная схема блока сравнения сигналов отказов;

на фиг.6 - структурная схема блока формирования сигналов отказов;

на фиг.7 - структурная схема блока управления;

на фиг.8 - пример структуры конкретной системы (из шести участков, N=6);

на фиг.9 - структурная схема блока модели системы;

на фиг.10 - структурная схема n-го () модельного элемента участка системы;

на фиг.11 - структурная схема блока имитаторов состояний участков системы;

на фиг.12 - структурная схема блока регистрации.

Устройство для прогнозирования случайных событий, изображенное на фиг.1, состоит из блока управления 1, блока модели системы 2, блока имитаторов состояний участков системы 3, блока формирования сигналов отказов 4, блока регистрации 5, блока контроля сигналов отказов 6, блока преобразования сигналов отказов 7, блока опознавания сигналов отказов 8 и блока сравнения сигналов отказов 9. При этом выход 51 блока регистрации 5 подключен к входу 11 блока управления 1, управляющий вход 41 блока формирования сигналов отказов 4 подключен к управляющему выходу 26 блока модели системы 2, сбросовый выход 12 блока управления 1 соединен с сбросовым входом 32 блока имитаторов состояний участков системы 3, сбросовым входом 22 блока модели системы 2, сбросовым входом 42 блока формирования сигналов отказов 4, сбросовым входом 52 блока регистрации 5, сбросовым входом 62 блока контроля сигналов отказов 6, сбросовым входом 72 блока преобразования сигналов отказов 7, сбросовым входом 82 блока опознавания сигналов отказов 8 и сбросовым входом 92 блока сравнения сигналов отказов 9. Причем М≥2 контрольных выходов 141-14М блока управления 1 подключены к соответствующим М контрольным входам 241-24М блока модели системы 2. Синхронизирующий выход 13 блока управления 1 подключен к синхронизирующему входу 33 блока имитаторов состояний участков системы 3, синхронизирующему входу 23 блока модели системы 2, синхронизирующему входу 43 блока формирования сигналов отказов 4, синхронизирующему входу 53 блока регистрации 5, синхронизирующему входу 63 блока контроля сигналов отказов 6, синхронизирующему входу 73 блока преобразования сигналов отказов 7, синхронизирующему входу 83 блока опознавания сигналов отказов 8 и синхронизирующему входу 93 блока сравнения сигналов отказов 9. Управляющий выход 15 блока управления 1 соединен с управляющим входом 34 блока имитаторов состояний участков системы 3, N≥2 групповых входов 311-31N которого подключены к соответствующим N групповым выходам 211-21N блока модели системы 2, N групповых входов 251-25N которого соединены с соответствующими N групповыми выходами 351-35N блока имитаторов состояний участков системы 3. Информационный 94 и сигнальный 95 выходы блока сравнения сигналов отказов 9 соединены соответственно с информационным 54 и сигнальным 55 входами блока регистрации 5. Информационный 44 и сигнальный 45 выходы блока формирования сигналов отказов 4 соединены соответственно с информационным 91 и сигнальным 96 входами блока сравнения сигналов отказов 9, запирающий вход 97 которого подключен к запирающему выходу 61 блока контроля сигналов отказов 6, первичный 66 и вторичный 67 выходы которого соединены соответственно с первичным 74 и вторичным 75 входами блока преобразования сигналов отказов 7. Первичный 76 и вторичный 77 выходы блока преобразования сигналов отказов 7 подключены соответственно к первичному 84 и вторичному 85 входам блока опознавания сигналов отказов 8, опознавательный выход 81 которого соединен с опознавательным входом 98 блока сравнения сигналов отказов 9. Вспомогательный выход 86 блока опознавания сигналов отказов 8 подключен к вспомогательному входу 71 блока преобразования сигналов отказов 7. Контрольно-информационный 64 и контрольно-сигнальный 65 входы блока контроля сигналов отказов 6 соединены соответственно с дополнительным контрольно-информационным 46 и дополнительным контрольно-сигнальным 47 выходами блока формирования сигналов отказов 4.

Число "N, (N≥2)" (элементов, входов, выходов и т.п.) определяется в соответствии с возможным количеством участков исследуемой производственной или телекоммуникационной системы и, как правило, составляет от 2 (двух) до 50 (пятидесяти).

Число "М, (М≥2)" характеризует возможное количество агрегатов участка исследуемой производственной или телекоммуникационной системы и, как правило, составляет от 2 (двух) до 20 (двадцати).

Блок контроля сигналов отказов 6 (фиг.2) предназначен для контрольного распознавания и регистрации сигналов состояния, характеризующих параметры, полученные в результате моделирования производственного или телекоммуникационного процесса - время выполнения сменного задания и количество изделий, изготовленных производственной (количество услуг, предоставленных телекоммуникационной) системой. Помимо этого, в блоке контроля сигналов отказов 6 осуществляется как процедура принятия решения о логико-математической природе этих параметров, обуславливающих результаты прогнозирования случайных событий (параметры, полученные в результате моделирования, идентифицируются однозначно либо неоднозначно, нечетко, могут быть описаны с привлечением лингвистической переменной и требуют дополнительной верификации), так и процедура формулировки (присвоения значения функциям принадлежности) двух начальных решений - по начальному количеству мнений экспертов (количество экспертов равно двум) о степени принадлежности конкретного сигнала состояния, характеризующего конкретный параметр, к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов.

Блок контроля сигналов отказов 6 состоит из контрольно-информационного 6.1 и контрольно-сигнального 6.2 дешифраторов, контрольного счетчика 6.3 и контрольного анализатора 6.4. При этом входы 6.1-1 и 6.2-1 контрольно-информационного 6.1 и контрольно-сигнального 6.2 дешифраторов являются соответственно контрольно-информационным 64 и контрольно-сигнальным 65 входами блока 6, выходы 6.1-2 и 6.2-2 контрольно-информационного 6.1 и контрольно-сигнального 6.2 дешифраторов подключены соответственно к информационному 6.3-1 и сигнальному 6.3-4 входам контрольного счетчика 6.3, сбросовый 6.3-2 и синхронизирующий 6.3-3 входы которого являются соответственно сбросовым 62 и синхронизирующим 63 входами блока 6. Информационный 6.3-5 и сигнальный 6.3-6 выходы контрольного счетчика 6.3 подключены соответственно к информационному 6.4-1 и сигнальному 6.4-2 входам контрольного анализатора 6.4, запирающий выход 6.4-5 которого является запирающим выходом 61 блока 6. Первичный 6.4-3 и вторичный 6.4-4 выходы контрольного анализатора 6.4 являются соответственно первичным 66 и вторичным 67 выходами блока контроля сигналов отказов 6.

Контрольно-информационный дешифратор 6.1 блока контроля сигналов отказов 6 предназначен для контрольного распознавания сигнала состояния, характеризующего время выполнения сменного задания. Контрольно-информационный дешифратор 6.1 может быть технически реализован в виде серийно выпускаемого дешифратора, описанного в книге [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С.432-436, рис.4.46].

Контрольно-сигнальный дешифратор 6.2 блока контроля сигналов отказов 6 предназначен для контрольного распознавания сигнала состояния, характеризующего количество изделий, изготовленных производственной системой, или количество доведенных до абонента телекоммуникационной системы услуг за текущую смену. Контрольно-сигнальный дешифратор 6.2 может быть технически реализован по аналогии с контрольно-информационным дешифратором 6.2 - на базе серийно выпускаемого дешифратора, описанного в работе [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С.432-436, рис.4.46].

Контрольный счетчик 6.3 блока контроля сигналов отказов 6 предназначен для контрольной регистрации сигналов состояния, характеризующих параметры, полученные в результате моделирования производственного или телекоммуникационного процесса - время выполнения сменного задания и количество изделий, изготовленных производственной (количество услуг, предоставленных телекоммуникационной) системой. Контрольный счетчик 6.3 может быть технически реализован на базе цифрового счетчика, как описано в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С.96-100].

Контрольный анализатор 6.4 блока контроля сигналов отказов 6 предназначен для сравнения вида сигнала состояния с эталонным, однозначно идентифицируемым видом сигнала состояния, осуществления процедуры принятия решения о логико-математической природе моделируемых параметров, описывающих эти состояния - параметры, полученные в результате моделирования, идентифицируются однозначно либо неоднозначно, нечетко, могут быть описаны с привлечением лингвистической переменной и требуют дополнительной верификации, а также осуществления процедуры формулировки (присвоения значения функциям принадлежности) двух начальных решений - по начальному количеству мнений экспертов (количество экспертов равно двум) о степени принадлежности конкретного сигнала состояния, характеризующего конкретный параметр, к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов. Контрольный анализатор 6.4 представляет собой серийно выпускаемый программируемый ТТЛ-компаратор типа 74LS85, описанный в [Янсен Й. Курс цифровой электроники: Сложные ИС для устройств передачи данных. Т.3. - М.: Мир, 1987. С.38-40, рис.1.21].

Блок преобразования сигналов отказов 7 (фиг.3) предназначен для математически корректного преобразования сигналов состояния, характеризующих параметры, полученные в результате моделирования производственного или телекоммуникационного процесса, и идентифицируемых в нечеткой форме (неоднозначно) к виду, пригодному для получения достоверных (однозначно трактуемых) результатов прогнозирования случайных событий.

Блок преобразования сигналов отказов 7 состоит из преобразующего счетчика-вычислителя 7.1, первичного 7.2 и вторичного 7.3 элементов хранения, первичного 7.4 и вторичного 7.5 элементов преобразования. Причем первичный 7.1-4 и вторичный 7.1-5 входы преобразующего счетчика вычислителя 7.1 соединены соответственно с входом 7.2-1 первичного 7.2 и основным входом 7.3-1 вторичного 7.3 элементов хранения и являются соответственно первичным 74 и вторичным 75 входами блока 7. Выходы 7.2-2 и 7.3-2 первичного 7.2 и вторичного 7.3 элементов хранения подключены соответственно к основным входам 7.4-1 и 7.5-1 первичного 7.4 и вторичного 7.5 элементов преобразования, выходы 7.4-3 и 7.5-3 которых являются соответственно первичным 76 и вторичным 77 выходами блока 7. Вспомогательный вход 7.3-3 вторичного элемента хранения 7.3 соединен с вспомогательным входом 7.1-1 преобразующего счетчика-вычислителя 7.1 и является вспомогательным входом 71 блока 7. Вспомогательные входы 7.4-2 и 7.5-2 первичного 7.4 и вторичного 7.5 элементов преобразования подключены соответственно к первичному 7.1-6 и вторичному 7.1-7 выходам преобразующего счетчика-вычислителя 7.1, сбросовый 7.1-2 и синхронизирующий 7.1-3 входы которого являются соответственно сбросовым 72 и синхронизирующим 73 входами блока преобразования сигналов отказов 7.

Преобразующий счетчик-вычислитель 7.1 блока преобразования сигналов отказов 7 предназначен для осуществления операции арифметического вычитания из единицы значений функций принадлежности нечетких множеств, поступающих из блока 6 и характеризующих мнения двух экспертов о степени принадлежности конкретного сигнала состояния, характеризующего конкретный параметр, к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов. Преобразующий счетчик-вычислитель 7.1 представляет собой типовое арифметико-логическое устройство и технически реализуется в виде серийно выпускаемого арифметико-логического устройства (АЛУ), описанного в [Дроздов Е.А., Комарницкий В.А., Пятибратов А.П. Электронно-вычислительные машины Единой системы. - М.: Машиностроение, 1981. С.158-170].

Первичный элемент хранения 7.2 блока преобразования сигналов отказов 7 предназначен для хранения нечеткой информации от первого эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на основной вход 7.4-1 первичного элемента преобразования 7.4. Первичный элемент хранения 7.2 технически реализуется в виде типового программируемого запоминающего устройства в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.197-199, рис.6.10].

Вторичный элемент хранения 7.3 блока преобразования сигналов отказов 7 предназначен для хранения нечеткой информации от второго эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на основной вход 7.5-1 вторичного элемента преобразования 7.5. Вторичный элемент хранения 7.3 отличается от первичного элемента хранения 7.2 лишь наличием вспомогательного входа 7.3-3, который технически может быть легко объединен с основным входом 7.3-1, что позволяет осуществить реализацию вторичного элемента хранения 7.3 аналогично первичному элементу хранения 7.2, в виде программируемого постоянного запоминающего устройства, как описано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.197-199, рис.6.10].

Первичный элемент преобразования 7.4 блока преобразования сигналов отказов 7 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого первым экспертом с дополнением нечеткого множества, формулируемого вторым экспертом. Первичный элемент преобразования 7.4 представляет собой цифровой узел сравнения, описанный в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Вторичный элемент преобразования 7.5 блока преобразования сигналов отказов 7 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого вторым экспертом с дополнением нечеткого множества, формулируемого первым экспертом. Вторичный элемент преобразования 7.5 идентичен первичному элементу преобразования 7.4 и также может быть технически реализован на базе цифрового узла сравнения, описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Блок опознавания сигналов отказов 8 (фиг.4) предназначен для реализации завершающих вычислений в рамках теории нечетких множеств, направленных на окончательное и однозначное принятие решения (опознавание) о принадлежности конкретного сигнала состояния, характеризующего конкретный параметр моделируемой системы, к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов.

Блок опознавания сигналов отказов 8 состоит из опознавательного счетчика-вычислителя 8.1 и опознавателя уровня сигналов отказов 8.2. При этом выход 8.2-2 опознавателя уровня сигналов отказов 8.2 является опознавательным выходом 81 блока 8, выход 8.1-1 опознавательного счетчика-вычислителя 8.1 подключен к входу 8.2-1 опознавателя уровня сигналов отказов 8.2 и является вспомогательным выходом 86 блока 8, первичный 8.1-4 и вторичный 8.1-5 входы опознавательного счетчика-вычислителя 8.1 являются соответственно первичным 84 и вторичным 85 входами блока 8, сбросовый 8.1-2 и синхронизирующий 8.1-3 входы опознавательного счетчика-вычислителя 8.1 являются соответственно сбросовым 82 и синхронизирующим 83 входами блока опознавания сигналов отказов 8.

Опознавательный счетчик-вычислитель 8.1 блока опознавания сигналов отказов 8 предназначен для реализации завершающего цикла дизъюнктивного суммирования нечетких множеств - выполнения математической операции объединения нечетких множеств, являющихся результатом соответственно пересечения нечеткого множества, формулируемого первым экспертом с дополнением нечеткого множества, формулируемого вторым экспертом, и пересечения нечеткого множества, формулируемого вторым экспертом с дополнением нечеткого множества, формулируемого первым экспертом. Опознавательный счетчик-вычислитель 8.1 может быть технически реализован на базе цифрового узла сравнения, описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.149-152, рис.5.19].

Опознаватель уровня сигналов отказов 8.2 блока опознавания сигналов отказов 8 предназначен для реализации процедуры однозначного выбора (опознавания и присвоения) количественных значений соотношения анализируемых нечетких параметров моделируемого производственного или телекоммуникационного процесса - времени выполнения сменного задания и количества изделий, изготовленных производственной (количества услуг, предоставленных телекоммуникационной) системой. Опознаватель уровня сигналов отказов 8.2 представляет собой цифровую программируемую пороговую схему сравнения, описанную в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. С.152-156, рис.5.22].

Блок сравнения сигналов отказов 9 (фиг.5) предназначен для реализации ряда задач, завершающих цикл преобразований в интересах получения достоверных (однозначно трактуемых) результатов прогнозирования случайных событий - регистрации сигналов состояния, поступающих из блока 4 и характеризующих параметры моделируемой системы, а также для передачи в блок регистрации 5 либо изначально однозначно (четко) идентифицируемых сигналов состояния из блока 4, либо математически корректно преобразованных в блоках 6, 7 и 8 сигналов состояния, изначально идентифицируемых в нечеткой форме (неоднозначно).

Блок сравнения сигналов отказов 9 состоит из сравнивающего счетчика 9.1, отказного 9.2 и исполнительного 9.3 элементов И. Причем опознавательный вход 9.3-2 исполнительного элемента И 9.3 соединен с опознавательным входом 9.2-2 отказного элемента И 9.2 и является опознавательным входом 98 блока 9, информационный 9.1-6 и сигнальный 9.1-7 выходы сравнивающего счетчика 9.1 подключены соответственно к основным входам 9.2-1 и 9.3-1 отказного 9.2 и исполнительного 9.3 элементов И, выходы 9.2-3 и 9.3-3 которых являются соответственно информационным 94 и сигнальным 95 выходами блока 9. Запирающий вход 9.1-1 сравнивающего счетчика 9.1 является запирающим входом 97 блока 9, информационный 9.1-4 и сигнальный 9.1-5 входы сравнивающего счетчика 9.1 являются соответственно информационным 91 и сигнальным 96 входами блока 9. Сбросовый 9.1-2 и синхронизирующий 9.1-3 входы сравнивающего счетчика 9.1 являются соответственно сбросовым 92 и синхронизирующим 93 входами блока сравнения сигналов отказов 9.

Сравнивающий счетчик 9.1 блока сравнения сигналов отказов 9 предназначен для регистрации сигналов состояния, поступающих из блока 4, и реализации запрета на их передачу в блок 5 (запирания) при получении из блока 6 запирающего сигнала, подтверждающего, что параметры моделируемой системы, обуславливающие вид сигналов состояния, идентифицированы нечетко (неоднозначно). Сравнивающий счетчик 9.1 может быть технически реализован на базе цифрового счетчика с одиночным запрещающим входом, описанного в работе [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С.101-102].

Отказной элемент И 9.2 блока сравнения сигналов отказов 9 предназначен для конъюнкции и передачи в блок регистрации 5 достоверного значения параметра моделируемой системы - вр