Конфигурируемое вычислительное устройство

Иллюстрации

Показать всеИзобретение относится к конфигурируемым по длине вычислительным устройствам для длинных чисел. Техническим результатом является повышение быстродействия вычислительного устройства, сокращение времени обработки данных. Указанный результат достигается за счет того, что устройство содержит два блока вычислительного устройства, каждый из которых разделен, по меньшей мере, на четыре субблока, состоящих из множества элементарных ячеек, при этом упомянутые блоки пространственно размещены таким образом, что расстояние между элементарной ячейкой первого блока и равнозначной элементарной ячейкой второго блока минимально. При этом конфигурация вычислительного устройства может быть изменена при помощи конфигурационных переключателей, установленных между субблоками устройства. 11 з.п. ф-лы, 6 ил.

Реферат

Предлагаемое изобретение относится к вычислительным устройствам и, в частности, к конфигурируемым по длине вычислительным устройствам для длинных чисел.

DE 3631992 T2 описывает криптографический процессор для эффективного выполнения способа с открытым ключом Rivest, Shamir, Adleman, который известен также как RSA-метод. Необходимое для этого способа модульное возведение в степень вычисляется с применением способа умножения с упреждением и метода сокращения с упреждением. Для этого используется трехоперандовый сумматор. Известный трехоперандовый сумматор имеет длину 660 бит. Элементарная ячейка состоит из нескольких криптографических регистров, регистра сдвига, полусумматора, полного сумматора и элемента ускоренного переноса. Четыре подобные элементарные ячейки образуют четырехъячеечный блок, причем к нему присоединен элемент ускоренного переноса. Пять подобных четырехъячеечных блоков образуют 20-ти ячеечный блок. Устройство шифрования состоит из 33 таких 20-ти ячеечных блоков и устройства управления, которое включает в себя тактовый генератор для тактирования элементарных ячеек. Элементы ускоренного переноса четырехъячеечных блоков включены совместно, чтобы распознать, распространяется ли перенос на большее расстояние, а именно на 20 разрядов. Если активирован сигнал продвижения 20-ти разрядного блока, то это означает, что перенос рассматриваемого 20-ти разрядного блока зависит от переноса на выходе предшествующего блока. Если, напротив, сигнал продвижения 20-ти разрядного блока не активирован, то это означает, что имеющийся в наличии перенос на выходе этого блока, т.е. на самом старшем по значимости разряде этого блока, формируется внутри этого блока, а не зависит от предшествующего блока.

Тем самым является возможным повысить быстродействие рабочего цикла вычислительного устройства, т.е. скорость запитки новых входных операндов, по сравнению с наихудшим случаем, при котором дорожка переноса продолжается от самого младшего разряда всего вычислительного устройства до самого старшего разряда всего вычислительного устройства. Если активирован сигнал распространения для 20-ти разрядного блока, то рабочий цикл всего вычислительного устройства замедляется до такой степени, что принимается во внимание наихудший случай, т.е. вычислительное устройство останавливается до тех пор, пока перенос не распространится от самого младшего до самого старшего разряда всего вычислительного устройства.

Поэтому время цикла, т.е. время, спустя которое следующий входной операнд подается в вычислительное устройство, задается таким образом, чтобы его хватило для обработки переноса непосредственно соседних блоков. Преимущество этого состоит в том, что независимо от числа ячеек вычислительного устройства необходимо принимать во внимание только время переноса блока. Если же, напротив, установлено, что на перенос текущего блока влияет не только предыдущий блок, но и предыдущий блок предшествующего блока, то время цикла замедляется настолько, чтобы имелось достаточно времени для полной дорожки переноса.

На фиг.4 изображена элементарная ячейка для разряда i известного вычислительного устройства. Элементарная ячейка состоит из нескольких регистров для нескольких входных операндов, из которых на фиг.4 показаны лишь две регистровые ячейки 110 и 112. Элементарная ячейка также включает в себя сумматор 114 и регистровую ячейку для результата, которая на фиг.4 обозначена ссылочной позицией 116. Из относительно большого количества компонентов в элементарной ячейке, представленных на фиг.4, следует, что одна такая элементарная ячейка в своей практической реализации имеет относительно небольшую высоту h, но относительно большую ширину d. Основываясь на факте, что 660 таких элементарных ячеек должны быть уложены друг на друга, то получается узкая высокая башня. Технологически все же желательными являются по возможности квадратные чипы, так что узкая высокая башня разделяется на несколько малых стопок, которые размещаются рядом друг с другом. При этом каждая вторая стопка повернута вершиной вниз. Данные, которые требуются стопке от предыдущей стопки, переносятся на верхней и нижней стороне стопки к соседним стопкам.

Для того чтобы сократить время обработки, определенные криптографические алгоритмы могут обрабатываться при помощи двух параллельно работающих вычислительных устройств. Определенные алгоритмы имеют требование: если они, например, являются итеративными, то содержимое в регистре результата одного вычислительного устройства загружается в регистр операнда другого вычислительного устройства.

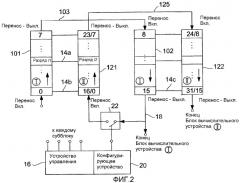

Подобная ситуация представлена на фиг.3. На фиг.3 изображены первое вычислительное устройство 91 длинных чисел и второе вычислительное устройство 92 длинных чисел. Каждое вычислительное устройство включает в себя некоторое количество элементарных ячеек 90, причем каждая элементарная ячейка имеет структуру, как показано на фиг.4. Количество элементарных ячеек в каждом вычислительном устройстве длинных чисел является одинаковым и составляет n. В зависимости от применения, вычислительные устройства имеют разную длину. Описанное в DE 36 312 992 C2 вычислительное устройство имеет длину 660 битов. Если должны быть параллельно выполнены две такие операции шифрования, то необходимо использовать два 660-битовых вычислительных устройства длинных чисел.

Для криптографии с использованием эллиптических кривых уже достигнута достаточная надежность, если используется секретный ключ, имеющий длину, например 160 битов. Поэтому такое вычислительное устройство должно иметь ширину минимум 160 битов. Для RSA-криптосистем существуют реализации с удовлетворительным уровнем надежности, при которых модуль имеет 1024 разряда. Более надежные RSA-системы имеют 2048 разряда. Поэтому для параллельного применения необходимо включить параллельно, например, два 1024-разрядных или два 2048-разрядных вычислительных устройства.

Чтобы загрузить содержимое в регистре результата, например, вычислительного устройства 1 длинных чисел (91 на фиг.3) во входной регистр операнда вычислительного устройства 2 длинных чисел (92 на фиг.3), можно использовать первый интерфейс шины, второй интерфейс 94 шины, а также, к примеру, 32-разрядную шину 95. Поэтому интерфейс 93 шины будет содержать блочную выборку 32-разрядных блоков из вычислительного устройства 1 длинных чисел. Затем каждый 32-разрядный блок переносится друг за другом к интерфейсу 94 шины через шину 95, причем интерфейс 94 шины обуславливает, что каждый новый 32-разрядный блок загружается в соответствующую элементарную ячейку вычислительного устройства длинных чисел. Для 660-разрядного вычислительного устройства требуется двадцать циклов, причем каждый цикл состоит из следующих этапов: адресация 32 элементарных ячеек в исходном вычислительном устройстве длинных чисел, выборка 32 элементарных ячеек в исходном вычислительном устройстве длинных чисел, перенос 32 битов через шину, адресация 32 элементарных ячеек в конечном вычислительном устройстве длинных чисел и загрузка в память 32 битов в адресованных 32 элементарных ячейках вычислительного устройства длинных чисел.

Доступ вычислительного устройства к регистру другого вычислительного устройства происходит при помощи предшествующего обмена в явном виде операндов через систему шин, с которой связаны оба вычислительных устройства. Согласно стандарту, ширина этой шины составляет 32 бита. В зависимости от предлагаемой системы шина может быть шириной 8 битов. Поэтому обмен для вычислительных устройств длинных чисел и, особенно, для последовательно-параллельных вычислительных устройств занимает продолжительное время. Кроме того, часто возникает проблема надежности, поскольку передача данных наблюдается в профиле тока.

Задача предлагаемого изобретения состоит в том, чтобы создать эффективное и надежное вычислительное устройство. Эта задача решается путем создания вычислительного устройства в соответствии с п.1 формулы изобретения.

В основе предлагаемого изобретения лежит идея о том, что регистровый обмен между двумя вычислительными устройствами длинных чисел можно ускорить, если первый блок вычислительного устройства размещен рядом со вторым блоком вычислительного устройства; если расстояние между одной элементарной ячейкой первого блока вычислительного устройства и равнозначной элементарной ячейкой второго блока вычислительного устройства меньше, чем среднее расстояние между такой же элементарной ячейкой первого блока вычислительного устройства и, по меньшей мере, двумя неравнозначными элементарными ячейками второго блока вычислительного устройства. Блоки вычислительного устройства соединены через устройство связи при помощи определенного количества линий связи, при этом количество линий связи равняется количеству элементарных ячеек в одном блоке вычислительного устройства, причем одна линия связи соединяет по меньшей мере одну регистровую ячейку в элементарной ячейке первого блока вычислительного устройства с по меньшей мере одной регистровой ячейкой элементарной ячейки, в соответствии со значимостью во втором блоке вычислительного устройства, и кроме того, предусмотрено устройство управления для загрузки содержимого регистровых ячеек одного блока вычислительного устройства через линии связи в регистровые ячейки другого блока вычислительного устройства.

Преимущество предлагаемого изобретения состоит в том, что регистровый обмен между обоими параллельно работающими вычислительными устройствами протекает быстрее, так как при этом требуется только один цикл.

Другое преимущество предлагаемого изобретения состоит в том, что оба параллельных вычислительных устройства расположены рядом, так что элементарные ячейки в обоих вычислительных устройствах с одинаковой значимостью расположены рядом, линии связи являются короткими и поэтому существенно затрудняется несанкционированное прослушивание, поскольку такое несанкционированное прослушивание может быть осуществлено тем легче, чем больше длина линии связи, подвергающейся такому прослушиванию.

Следующее преимущество предлагаемого изобретения сводится к тому, что профиль тока, в частности, у вычислительных устройств длинных чисел при передаче данных является однородным, поскольку параллельно переносится множество независимых друг от друга битов.

Еще одно преимущество предлагаемого изобретения сводится к тому, что вычислительное устройство можно подвергнуть реконфигурации за счет того, что два параллельно расположенных вычислительных устройства можно переконфигурировать в одно вычислительное устройство с двойной длиной, если дорожка переноса выходного сигнала переноса старшего разряда первого вычислительного устройства подключается на вход переноса младшего разряда второго блока вычислительного устройства. Другими словами, это означает, что очень длинное вычислительное устройство можно переконфигурировать путем воздействия на дорожку переноса между двумя или более блоками вычислительного устройства на 2, 4 параллельно работающих вычислительных устройства меньшей длины. Это свойство имеет особое преимущество для многоцелевого криптографического процессора, поскольку для определенных криптографических задач требуются различные длины вычислительных устройств. В криптографии с использованием эллиптических кривых длины кодов достигают порядка величины в пределах от 150 до 180 битов, предпочтительно 160 битов, для обеспечения достаточной надежности. Напротив, в обычной RSA-системе надежность достигается только в том случае, если применяются длины кодов 1024 битов или в последнее время даже 2048 битов, что неизбежно ведет к тому, что для эффективной обработки криптосистемы требуются вычислительные устройства длинных чисел длиной более чем 1024 или, соответственно, более 2048 битов.

С другой стороны, в частности в случае криптографических процессоров, которые размещаются на смарткартах в форме чипов, требование к поверхности чипа задается извне, и соответствующие размеры жестко соблюдаются. Возникает задача разместить в чипе заданных размеров такие необходимые компоненты для криптографического процессора, как, например, вычислительное устройство, запоминающее устройство и т.д. Требования, предъявляемые к поверхности чипа, приводят к тому, что предпочтительно предусматривать отдельное вычислительное устройство не для каждого криптографического алгоритма, а по возможности для всех криптографических алгоритмов одни и те же вычислительные устройства. С другой стороны, разная длина кода и сильно отличающаяся длина вычислительного устройства уже являются существенным отличительным критерием криптографических алгоритмов.

Способность к реконфигурации длины вычислительного устройства за счет введения дорожки переноса между двумя блоками вычислительного устройства и за счет обеспечения конфигурирующего устройства для соединения цепи вычислительного устройства, если требуется длинное вычислительное устройство, или для прерывания дорожки переноса, если требуются несколько параллельных коротких вычислительных устройств, обеспечивает преимущество, заключающееся в том, что может использоваться одно вычислительное устройство для нескольких приложений, и, дополнительно, если имеются более короткие длины кода, то часть вычислительного устройства не просто отключается, а может работать как второе параллельное вычислительное устройство, которое может осуществлять быстрый регистровый обмен с первым вычислительным устройством.

Для того чтобы разместить вычислительное устройство согласно данному изобретению на микросхеме, т.е. на интегральной схеме с заданной геометрией, каждый блок вычислительного устройства разбивается на субблоки. При этом субблоки вкладываются друг в друга так, что между двумя субблоками первого блока вычислительного устройства всегда размещается один субблок второго блока вычислительного устройства, и кроме того, субблоки первого и второго блоков вычислительного устройства размещены таким образом, что элементарные ячейки одинаковой значимости имеют между собой как можно меньшее расстояние. Это приводит к вложенной друг в друга двойной меандровой структуре. Таким образом, меандры обоих параллельных блоков вычислительного устройства размещаются попеременно. За первым выступом меандра одного вычислительного устройства следует первый выступ меандра другого блока вычислительного устройства, причем последний является геометрически зеркально отраженным, чтобы реализовать короткие расстояния между элементарными ячейками одинаковой значимости, если оба блока вычислительного устройства работают параллельно друг другу. Расположение блоков вычислительного устройства в виде входящей друг в друга меандровой структуры делает возможным такой вариант, при котором блоки вычислительного устройства посредством активации дорожки переноса соединяются в единое вычислительное устройство с двойной длиной.

Предпочтительные примеры выполнения предлагаемого изобретения детально разъясняются на прилагаемых чертежах:

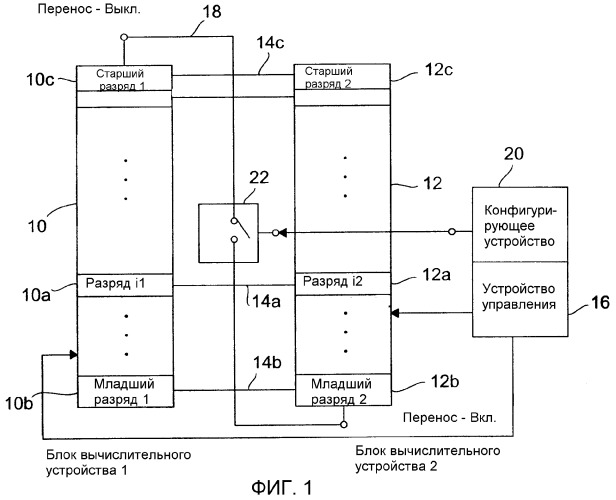

фиг.1 - блок-схема вычислительного устройства согласно данному изобретению;

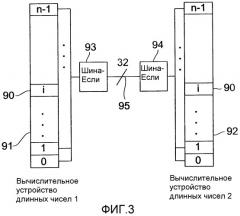

фиг.2 - блок-схема предпочтительной конфигурации вычислительного устройства согласно данному изобретению;

фиг.3 - блок-схема для осуществления регистрового обмена между первым вычислительным устройством длинных чисел и вторым вычислительным устройством длинных чисел при помощи обычной системы шин;

фиг.4 - схематичное изображение элементарной ячейки для бита i в вычислительном устройстве длинных чисел;

фиг.5 - блок-схема другого предпочтительного расположения вычислительного устройства согласно данному изобретению;

фиг.6 - детальный вид для разъяснения расположения двух блоков вычислительного устройства относительно друг друга.

На фиг.1 показана блок-схема вычислительного устройства согласно данному изобретению. Вычислительное устройство включает в себя первый блок 10 вычислительного устройства и второй блок 12. Каждый блок сам состоит из определенного количества элементарных ячеек 10а и, соответственно, 12а, а также из элементарной ячейки для младшего разряда 10в и 12в и элементарной ячейки для старшего разряда 10с и 12с. Элементарная ячейка 10в для младшего разряда вычислительного устройства 10 также обозначается как LSB1. Элементарная ячейка для старшего разряда вычислительного устройства 10 также обозначается как MSB1. Аналогичные обозначения выбраны для второго блока вычислительного устройства 12, причем термин "LSB" (least significant bit) используется для младшего разряда, а термин "MSB" (most significant bit) - для старшего разряда. Каждая элементарная ячейка, показанная на фиг.1, 10а, 10в, 10с, 12а, 12в, 12с, может быть выполнена так, как показано на фиг.4. Следует указать на то, что каждая элементарная ячейка включает в себя больше или меньше регистровых ячеек для операндов, подлежащих обработке сумматором элементарной ячейки, или больше или меньше регистровых ячеек для одного или нескольких результатов. Чтобы обеспечить быстрый обмен данными между регистрами обоих вычислительных устройств, каждое вычислительное устройство должно располагать элементарными ячейками, которые имеют по меньшей мере одну регистровую ячейку для сохранения в памяти разряда обрабатываемого вычислительным устройством операнда.

Показанное на фиг.1 вычислительное устройство включает в себя устройство соединения, которое имеет определенное количество линий связи 14а, 14в, 14с, причем каждая линия связи соединяет между собой две элементарные ячейки одинакового значения в обоих блоках вычислительного устройства. Так, например, линия связи 14а соединяет элементарную ячейку для бита i первого блока вычислительного устройства, которая на фиг.1 обозначена как 10а, с элементарной ячейкой для бита i второго блока вычислительного устройства 12, которая обозначена как 12а. Аналогично линия связи соединяет LSB-элементарную ячейку 10в первого блока 10 с LSB-элементарной ячейкой 12в второго блока. То же самое применимо к линии связи 14с, которая соединяет между собой обе MSB-элементарные ячейки обоих блоков вычислительного устройства.

Согласно данному изобретению, вычислительное устройство включает в себя устройство 16 управления для управления блоками 10, 12 вычислительного устройства, чтобы содержимое регистровых ячеек одного блока вычислительного устройства можно было загружать в содержимое другого блока через линии связи 14а, 14в, 14с напрямую для каждой элементарной ячейки.

Оба блока 10, 12 вычислительного устройства, показанного на фиг.1 предпочтительного варианта осуществления, могут функционировать как параллельные блоки, в известной степени независимо друг от друга. Другой вариант состоит в том, что оба блока 10 и 12 соединены таким образом, что они функционируют как единое вычислительное устройство с шириной, которая равна количеству элементарных ячеек в первом блоке 10 вычислительного устройства плюс количество элементарных ячеек во втором блоке 12 вычислительного устройства. Это достигается тем, что предусмотрена линия 18 переноса, которая соединяет выход переноса MSB-элементарной ячейки первого блока вычислительного устройства с входом переноса LSB-элементарной ячейки второго блока вычислительного устройства. Эта функциональность в дальнейшем достигается посредством конфигурирующего устройства 20, которое управляет выключателем 22, при этом если выключатель 22 открыт, то оба блока вычислительного устройства функционируют как два параллельных вычислительных устройства. Если выключатель 22 замкнут, то оба блока вычислительного устройства работают как единое вычислительное устройство. Биты операнда, которые хранятся в памяти элементарной ячейки первого блока 10 вычислительного устройства, представляют собой в этом случае младшие разряды полного операнда, в то время как разряды операнда, которые хранятся в памяти элементарных ячеек второго блока 12 вычислительного устройства, представляют собой старшие разряды полного операнда.

В соответствии с конструкцией и количеством элементарных ячеек в блоке вычислительного устройства и заданной геометрией для интегральной микросхемы, с помощью которой реализуется показанное на фиг.1 вычислительное устройство, может быть вполне достаточно пространственной конфигурации, показанной на фиг.1. Это имеет место в том случае, если заданная геометрия для процессора предписывает, что требуется вычислительное устройство с относительно незначительной шириной, или необходим прямоугольный чип.

Как правило, требование в этом отношении состоит в том, что желательно использовать квадратные чипы.

Для этой цели перейдем к представленной на фиг.2 предпочтительной двойной структуре меандра. Каждый блок вычислительного устройства разбит по меньшей мере на два субблока. На показанном на фиг.2 примере видно, что каждый из первого и второго блоков вычислительного устройства состоит из 16 элементарных ячеек, и что каждый блок вычислительного устройства разбит на два субблока с восемью элементарными ячейками. Следует указать на то, что типичные размеры для многоцелевых криптографических вычислительных устройств требуют более 1024 элементарных ячеек на каждый субблок.

Первый блок 10 вычислительного устройства разбит на первый субблок 101 и на второй субблок 102. Аналогичным образом второй блок вычислительного устройства разбивается на первый субблок 121 и на второй субблок 122. Первый субблок 101 и второй субблок 102 первого блока вычислительного устройства соединены дорожкой переноса 103. Таким же образом первый субблок 121 второго блока вычислительного устройства соединен дорожкой переноса 123 со вторым субблоком 122 второго блока вычислительного устройства (12 на фиг.1). Принадлежность отдельных субблоков к показанным на фиг.1 блокам вычислительного устройства обозначается на фиг.2 римскими цифрами.

Для того чтобы обеспечить короткие линии связи в меандровой структуре, оба блока вычислительного устройства располагаются в виде входящей друг в друга меандровой структуры, как показано на фиг.2. Так, например, LSB-элементарная ячейка первого блока вычислительного устройства соединена с LSB-элементарной ячейкой второго блока вычислительного устройства через линию связи 14в. То же самое действует для элементарной ячейки для разряда i первого блока вычислительного устройства и элементарной ячейки для разряда i второго блока вычислительного устройства, которые соединены между собой при помощи линии связи 14а. И, наконец, MSB-элементарная ячейка первого блока вычислительного устройства и MSB-элементарная ячейка второго блока вычислительного устройства соединены посредством линии связи 14с. В выбранном примере выполнения значение заносится в соответствующую элементарную ячейку. Значение элементарных ячеек первого блока составляет от 0 (LSB-элементарная ячейка) до 15 (MSB-элементарная ячейка). Значение второго блока составляет от 16 (LSB-элементарная ячейка) до 32 (MSB-элементарная ячейка), причем эти характеристики справедливы для случая, если первый и второй блоки вычислительного устройства соединены между собой через линию переноса 18 и выключатель 22, который удерживается конфигурирующим устройством 20 в закрытом положении.

В случае, если оба блока вычислительного устройства работают параллельно, значения элементарных ячеек первого блока вычислительного устройства не изменяются. Значения второго блока вычислительного устройства составляют, как показано на фиг.2, от 0 до 15.

Устройство 16 управления, как показано на фиг.2, имеет управляющее соединение к каждому субблоку вычислительного устройства, чтобы сделать возможным регистровый обмен между элементарными ячейками первого и второго субблока через соединительные линии 14а, 14в, 14с.

Показанная на фиг.2 вложенная друг в друга меандровая структура обоих блоков вычислительного устройства и, в частности, отдельных субблоков обеспечивает то, что соединительные линии между соответствующими элементарными ячейками одинаковой значимости являются как можно более короткими.

Следует указать, что на практике двойная меандровая структура состоит из большего количества субблоков, чем показано на фиг.2. На практике, в частности, отдельные субблоки имеют значительно большую высоту по сравнению с шириной. В этом случае для того, чтобы добиться приближенно квадратной формы чипа, необходимо разделить блок вычислительного устройства на более чем два субблока, и разместить в соответствии с показанной на фиг.2 встречно-штыревой структурой.

На фиг.5 показана другая предпочтительная конфигурация вычислительного устройства, которая возникает посредством отражения показанного на фиг.2 вычислительного устройства согласно первому примеру осуществления предлагаемого изобретения относительно горизонтальной оси. Показанное на фиг.5 вычислительное устройство включает в себя два блока вычислительного устройства, причем первый блок состоит из субблоков 1001, 1002, 1003 и 1004, а второй блок - из субблоков 1005, 1006, 1007 и 1008. Как показано на фиг.5, MSB вычислительного устройства с низким порядковым номером от 1 до 7 всегда соединяется с LSB вычислительного устройства с порядковым номером большим на единицу. Отдельные субблоки соединены посредством показанных на фиг.5 соединительных линий, которые представляют собой дорожку переноса, которая должна быть проложена от одного субблока к другому. На субблоках 1001 до 1008 направление от LSB до MSB соответствующего субблока обозначено стрелкой.

На фиг.5 также изображен переключатель 22, который имеет ту же функцию, что и переключатель 22 на фиг.2. Если выключатель замкнут, то вычислительное устройство, показанное на фиг.5, функционирует как одно единое вычислительное устройство длинных чисел с количеством разрядов 8 х m, где m - количество разрядов субблока 1001 до 1007.

Если, наоборот, выключатель разомкнут, то вычислительное устройство функционирует как два параллельных и соответственно более коротких вычислительных устройства. Первый блок вычислительного устройства имеет субблоки 1-4, в то время как в состав второго блока вычислительного устройства входят субблоки 5-8. Из фиг.5 далее видно, что разряды одинакового порядка в обоих более коротких вычислительных устройствах расположены настолько близко друг к другу, что расстояние между элементарной ячейкой первого блока вычислительного устройства и равнозначной элементарной ячейкой второго блока вычислительного устройства меньше, чем среднее расстояние между элементарной ячейкой первого блока вычислительного устройства и по меньшей мере двумя неравнозначными ячейками второго блока вычислительного устройства.

Следует отметить, что среднее расстояние можно рассчитать так, что все элементарные ячейки одного блока вычислительного устройства, неравнозначные относительно элементарной ячейки другого блока вычислительного устройства, соединены с элементарной ячейкой второго блока вычислительного устройства, интервал каждого отдельного соединения суммируется, и затем можно рассчитать среднее значение, например, путем деления получившейся длины на количество суммированных соединений. Однако для расчета среднего интервала не нужно суммировать каждое возможное соединение между обоими блоками вычислительного устройства и затем рассчитывать среднее значение. Вместо этого достаточно измерить некоторые соединения (например, 2) неравнозначных элементарных ячеек и затем на их основе рассчитать среднее значение. В любом случае конфигурация такова, что дорожки переноса между равнозначными элементарными ячейками являются короткими, чтобы был возможен быстрый регистровый обмен от одного блока вычислительного устройства к другому блоку вычислительного устройства, а именно через соединения между элементарными ячейками, посредством которых каждая элементарная ячейка одного блока вычислительного устройства соединена с соответствующей другой элементарной ячейкой другого блока вычислительного устройства одинакового порядка.

Следует указать на то, что отдельные субблоки не обязательно должны располагаться строго параллельно друг к другу, т.е. не обязательно так, что расстояние между двумя элементарными ячейками одинакового порядка всегда меньше, чем пространственный интервал между элементарной ячейкой первого блока вычислительного устройства и элементарной ячейкой на единицу большего порядка второго блока вычислительного устройства. Если, например, субблок 5 сдвигается в вертикальном направлении на длину половины, целой или нескольких элементарных ячеек, то тем не менее эффект согласно данному изобретению все равно достигается, хотя расстояние между равнозначными элементарными ячейками в субблоках 1001 и 1005 является таким же как расстояние от элементарной ячейки одного субблока до элементарной ячейки другого субблока следующего старшего или младшего разряда.

Это поясняется ниже со ссылкой на фиг.6. На фиг.6 изображен увеличенный фрагмент из фиг.1. Слева на фиг.6 показан первый блок 10 вычислительного устройства и, в частности, элементарные ячейки порядка i+2, i+1, i, i-1, i-2. Справа на фиг.6 показан второй блок вычислительного устройства с элементарными ячейками i+3, i+2, i+1, i, i-1, i-2. Принято, что высота каждой элементарной ячейки равна в обоих блоках. Высота каждой элементарной ячейки обозначена на фиг.6 как h. Исходя из этого, оба блока размещены не точно на одинаковой высоте, как показано на фиг.6, а смещены относительно друг друга на расстояние, равное половине высоты (h/2). Следует отметить, что возможны и другие значения смещения, при которых все же можно добиться наиболее коротких соединений между элементарными ячейками одинакового порядка, при условии, что смещение v между обоими блоками вычислительного устройства равно 0.

Линия связи 14а между обеими элементарными ячейками одинакового порядка в обоих блоках вычислительного устройства обозначена на фиг.6 сплошной линией. Согласно изобретению, оба блока вычислительного устройства размещаются так, что длина линии связи 14а короче, чем среднее расстояние между элементарной ячейкой i первого блока вычислительного устройства и минимум двумя элементарными ячейками различного порядка, например, элементарными ячейками порядка i+1 и i-1 или i+1, i+2 второго блока вычислительного устройства. Расстояние между элементарной ячейкой 10а и элементарной ячейкой ближайшего старшего разряда в блоке 12 вычислительного устройства, то есть элементарной ячейкой i+1 обозначено на фиг.6 как 60. Из фиг.6 видно, что это расстояние равно длине линии связи 14а. Из фиг.6 также видно, что расстояние между элементарной ячейкой 10а первого блока вычислительного устройства и, например, элементарной ячейкой с порядком i-1, которое обозначено на фиг.6 как 62, больше, чем расстояние 60. Если вычислить среднее арифметическое обоих расстояний 60, 62, то окажется, что это среднее арифметическое больше, чем длина линии связи 14а.

Следует указать на то, что для предлагаемого изобретения не важно, имеют ли оба блока вычислительного устройства форму прямоугольных столбцов, которые размещены параллельно друг другу. Вместо этого блоки вычислительного устройства могут иметь вид прямоугольных столбцов, которые размещены под углом друг к другу. Блоки вычислительных устройств также могут быть круговыми сегментами, а отдельные элементарные ячейки могут иметь форму кругового сектора, т.е. они не обязательно должны быть строго прямоугольными. Более того, отдельные размеры элементарных ячеек не обязательно должны быть одинаковы, хотя это и является предпочтительным в смысле более простого дизайна схемы и более простой разводки.

Каждое вычислительное устройство согласно изобретению имеет преимущество, которое заключается в том, что элементарные ячейки одинакового порядка расположены так друг к другу, что можно использовать короткие соединительные линии, чтобы обеспечить быстрый, полностью параллельный обмен данными между регистрами элементарных ячеек обоих блоков вычислительного устройства, если оба блока вычислительного устройства работают как отдельные вычислительные устройства.

Следует также отметить, что показанная на фиг.5 конфигурация вычислительного устройства может функционировать и таким образом, что параллельно будут работать четыре отдельных вычислительных устройства. Это достигается тем, что дополнительные переключатели 50а, 50в встроены между субблоками 1002 и 1003 и соответственно между субблоками 1006 и 1007. В этом случае имеются четыре независимых друг от друга более коротких вычислительных устройства, а именно, первое вычислительное устройство, которое состоит из субблоков 1 и 2; второе вычислительное устройство, состоящее из субблоков 5 и 6; третье вычислительное устройство, состоящее из субблоков 3 и 4, и четвертое вычислительное устройство, состоящее из субблоков 1007 и 1008.

Из фиг.5 видно, что и четыре вычислительных устройства размещены по отношению друг к другу таким образом, что возможен быстрый обмен данными между регистрами двух отдельных вычислительных устройств.

Если в соответствующие соединительные линии встроены переключатели от 52а до 52d, как показано на фиг.5, то конфигурация вычислительного устройства может использоваться как восемь отдельных вычислительных устройств, причем каждое вычислительное устройство имеет число элементарных ячеек, равное числу элементарных ячеек в субблоке 1001-1007.

Из фиг.5 видно, что соответствующее изобретению вычислительное устройство меандровой структуры является оптимально масштабируемым. Оно может функционировать как вычислительное устройство длинных чисел, а если открыт выключатель 22, то оно может действовать как два коротких вычислительных устройства. Если при открытом выключателе 22 выключатели 50а и 50в также открыты, то вычислительное устройство может функционировать как четыре коротких вычислительных устройства, благодаря чему всегда возможен быстрый обмен данными между двумя соседними вычислительными устройствами посредством линий связи.

Описание чертежей

| 10 | первый блок вычислительного устройства |

| 10а | элементарная ячейка i |

| 10b | LSB1-элементарная ячейка |

| 10с | MSB1-элементарная ячейка |

| 12 | второй блок вычислительного устройства |

| 12а | элементарная ячейка i |

| 12b | LSB1-элементарная ячейка |

| 12с | MSB1-элементарная ячейка |

| 14а | линия связи |

| 14b | линия связи |

| 14с | линия связи |

| 16 | устройство управления |

| 18 | линия переноса |

| 20 | конфигурирующее устройство |

| 22 | коммутационное устройства переноса |

| 50а-50b | переключатель конфигураций |

| 52а-52d | переключатель конфигураций |

| 60, 62 | расстояние между неравнозначными элементарными ячейками |

| 90 | элементарная ячейка |

| 91 | первое вычислительное устройство длинных чисел |

| 92 | второе вычислительное устройство длинных чисел |

| 93 | интерфейс шины |

| 94 | интерфейс шины |

| 101 | первый субблок первого блока вычислительного устройства |

| 102 | второй субблок первого блока вычислительного устройства |

| 110 | регистровая ячейка для первого операнда |

| 112 | регистровая ячейка для второго операнда |

| 114 | сумматор |

| 116 | регистровая ячейка для результата |

| 121 | первый субблок второго блока вычислительного устройства |

| 122 | второй субблок второго блока вычислительного устройства |

| 1001-1008 | субблоки |

1. Конфигурируемое устройство для обмена данными между вычислительными устройствами, обрабатывающими длинные числа, содержащее первый блок (10) вычислительного устройства, который состоит из первого множества элементарных ячеек (10а, 10b, 10 с), которые включают в себя элементарную ячейку (10b) для младшего разряда первого операнда и элементарную ячейку (10с) для старшего разряда первого операнда, причем каждая элементарная ячейка первого блока вычислительного устройства имеет, по меньшей мере, одну регистровую ячейку для сохранения в памяти разряда первого операнда или разряда результата, вычисле