Арифметический вычислитель

Иллюстрации

Показать всеИзобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых процессоров, выполняющих основные арифметические операции в прямых кодах с фиксированной и плавающей запятой. Техническим результатом является расширение функциональных возможностей, повышение скорости выполнения арифметических операций, повышение надежности работы. Устройство содержит блок ввода чисел и кода операций, блок выполнения операций с фиксированной запятой, блок выполнения операций с плавающей запятой, блок хранения результатов, блок управления. 36 ил., 4 табл.

Реферат

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых процессоров, выполняющих основные операции: суммирование, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой.

Известна "Схема цифрового сумматора" (заявка RU №99109089/09 от 04.07.1997 г. Бюл. №7 (1 ч.). 2001 г.), позволяющая выполнять операцию сложение чисел в двоичной системе счисления.

Известно "Устройство для сложения" (заявка RU №4892584/24 от 19.12.1990 г. Бюл. №25 1995 г.), позволяющее суммировать двоичные числа.

Известно "Устройство для вычисления модуля М-мерного вектора" (заявка RU №95104370/09 от 01.03.1995. Бюл. №15, 1997 г.), которое выполняет операции суммирования и вычитания над М-мерными векторами.

В качестве прототипа выбран "Сумматор-вычитатель старшими разрядами вперед на нейронах" (патент №2205444, 27.05.2003 г.), который выполняет операции суммирования и вычитания двоичных чисел.

Задача заключалась в следующем:

1) расширить функциональные возможности вычислителя,

2) повысить скорость выполнения арифметических операций,

3) повысить надежность работы арифметического вычислителя.

В представленном арифметическом вычислителе выполняются основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой. Предлагаемый арифметический вычислитель позволит расширить функциональные возможности устройства, повысить скорость выполнения арифметических операций, упростить алгоритм работы устройства.

Решение задачи осуществляется тем, что арифметический вычислитель, содержащий блок ввода чисел, блок управления, отличающийся тем, что дополнительно введены блок операций с фиксированной запятой, блок операций с плавающей запятой, блок хранения результатов, причем информационный выход блока ввода чисел соединен с информационным входом блока операций с фиксированной запятой и с информационным входом блока операций с плавающей запятой, управляющий вход которого соединен с первым управляющим выходом блока управления, третий управляющий вход которого соединен с управляющим выходом блока операций с плавающей запятой, информационный выход которого соединен с первым информационным входом блока хранения результатов, с первого по четвертый управляющие входы которого соединены соответственно с третьим по шестой управляющими выходами блока управления, второй управляющий выход которого соединен с управляющим входом блока операций с фиксированной запятой, управляющий выход которого соединен с четвертым управляющим входом блока управления, информационный выход блока операций с фиксированной запятой соединен со вторым информационным входом блока хранения результатов, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами арифметического вычислителя.

БВЧ - блок ввода чисел служит для ввода операндов и знака операции (+, -, *, /).

БОФЗ - блок выполнения операций с фиксированной запятой в прямом коде служит для выполнения основных арифметических операций в формате с фиксированной запятой.

БОПЗ - блок выполнения операций с плавающей запятой в прямом коде служит для выполнения основных арифметических операций в формате с плавающей запятой.

БХР - блок хранения результатов служит для записи и хранения в нем результатов выполнения арифметических операций.

БУ - блок служит для управления устройством.

В современных ЭВМ операция вычитания выполняется с применением дополнительного или обратного кода. При вводе отрицательного числа осуществляется перевод его в дополнительный или обратный код. Полученный результат также анализируется. Если получен отрицательный результат, то осуществляется перевод в дополнительный или обратный код. Если получен положительный результат, то перевода в коды не происходит. По этому алгоритму результат можно получить только после анализа знакового разряда результата. В случае ввода двух отрицательных чисел необходимо перевести оба числа в коды. Результат в этом случае также переводится в дополнительный или обратный код [1, 2].

Известен алгоритм сложения чисел в прямых кодах. Этот алгоритм позволяет сразу получить правильный результат в прямом коде. В этом случае необходимо применить операцию вычитания чисел. Для этого используется комбинационная схема вычитателя чисел в прямых кодах.

Для получения суммы двух чисел возможны два случая:

1) слагаемые имеют одинаковые знаки;

2) слагаемые имеют разные знаки.

Алгоритм получения суммы двух чисел с одинаковыми знаками определяется следующим образом:

Алгоритм первый.

1) сложить два числа;

2) сумме присвоить знак одного из слагаемых.

Алгоритм получения суммы двух чисел с разными знаками определяется следующим образом:

1) сравниваются знаки слагаемых и, если они одинаковы, то выполняется сложение по первому алгоритму;

2) если знаки слагаемых разные, то сравниваются числа по абсолютной величине;

3) если есть необходимость, переставить числа местами, чтобы вычитать из большего меньшее;

4) произвести вычитание двух чисел;

5) результату присвоить знак большего слагаемого.

Этот алгоритм позволяет получить сумму или разность чисел в прямых кодах. В арифметическом вычислителе не происходит сравнения чисел, если числа имеют разные знаки, в нем применена операция вычитания из первого числа второе. Если формируется заем из знакового разряда, то в этом случае от меньшего числа вычитается большее. Числа в этом случае с помощью коммутатора меняются местами на входе нейронов сумматора-вычитателя. На втором такте от второго большего числа вычитается первое меньшее. Если заема не образуется, то от большего первого числа вычитается меньшее второе. Менять местами числа на входе нейронов не нужно.

Операция умножения выполняется в прямом коде умножением младшими разрядами множителя со сдвигом суммы частичных произведений влево. Знак произведения определяется путем сложения знаковых цифр сомножителей по модулю два.

Операция деления выполняется по алгоритму деления чисел без восстановления остатков. Для определения следующей цифры частного необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак остатка определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный - записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр. Знак частного определяется путем сложения знаковых цифр делимого и делителя по модулю два. По таким алгоритмам выполняются основные арифметические операции с фиксированной запятой [1, 2].

Числа в формате с плавающей запятой представляются в виде знака порядка, значения порядка, знака мантиссы, мантиссы. При выполнении основных арифметических операций в формате с плавающей запятой необходимо выполнять операции над порядками, затем над мантиссами чисел.

Операции сложения, вычитания чисел, представленных в формате с плавающей запятой, выполняются по следующему алгоритму:

1) Осуществляется сравнение порядков путем вычитания их как целых чисел.

2) Производится выравнивание мантиссы числа с меньшим порядком в сторону числа с большим порядком.

3) Производятся алгебраическое сложение или вычитание мантисс чисел.

4) В случае получения левой или правой денормализации мантиссы производится нормализация результата. Нормализация осуществляется с помощью операций сдвига вправо на один разряд и серии сдвигов влево до получения значащей цифры после запятой.

Операция умножения чисел с плавающей запятой выполняется в следующей последовательности:

1) Находится знак произведения при помощи операции суммы по модулю два знаковых разрядов мантисс чисел.

2) Выполняется сложение порядков сомножителей.

3) Находится произведение мантисс сомножителей по алгоритму произведения чисел с фиксированной запятой, т.е. умножением младшими разрядами множителя со сдвигом суммы частичных произведений влево.

4) При получении денормализации осуществляется нормализация результата путем сдвига произведения влево до получения значащей цифры после запятой.

Операция деления чисел в формате с плавающей запятой выполняется по следующему алгоритму:

1) Определяется знак частного с помощью операции суммы по модулю два знаковых разрядов мантисс делимого и делителя.

2) Вычитаются порядки чисел по правилам вычитания операндов с фиксированной запятой. Из порядка делимого вычитается порядок делителя. При возникновении денормализации результата выполняется операция сдвига, тем самым осуществляется нормализация результата.

3) Находится частное мантисс делимого и делителя по алгоритму деления чисел без восстановления остатков в формате чисел с фиксированной запятой. Для определения следующей цифры частного необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак остатка определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный - записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр.

4) Нормализация частного при помощи операций сдвига [1, 2].

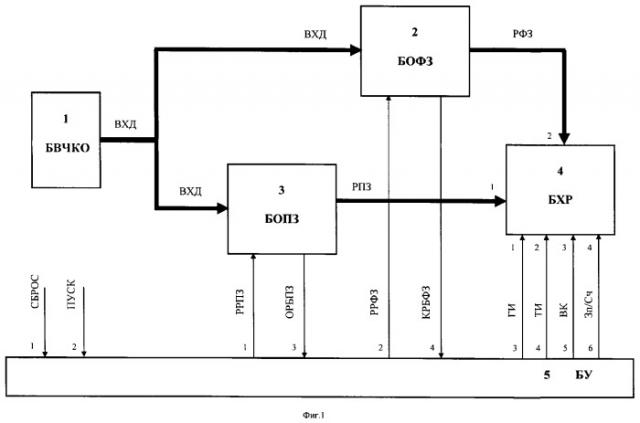

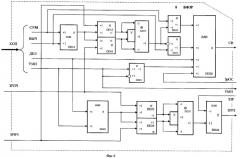

На фиг.1 изображена структурная схема арифметического вычислителя.

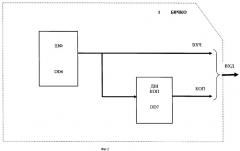

На фиг.2 представлен вариант технической реализации блока ввода чисел и кода операций.

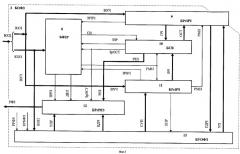

На фиг.3 представлен вариант технической реализации блока операций, выполняющий вычисления с фиксированной запятой.

На фиг.4 изображена функциональная схема блока формирования знакового разряда результата.

На фиг.5 показана функциональна схема блока регистра первого числа.

На фиг.6 показана принципиальная схема многоразрядного сумматора-вычитателя и коммутатора на нейронах и логических элементах.

На фиг.7 изображена функциональная схема одноразрядного сумматора-вычитателя, выполняющего операции суммирования или вычитания со знаковыми разрядами чисел.

На фиг.8 изображена функциональная схема одноразрядного сумматора-вычитателя, выполняющего операции суммирования или вычитания с i-ми разрядами чисел.

На фиг.9 показана функциональная схема блока регистра второго числа.

На фиг.10 представлен вариант технической реализации блока регистра результата.

На фиг.11а, 11б - содержательная ГСА работы устройства.

На фиг.12а, 12б - размеченная ГСА работы устройства.

Арифметический вычислитель (фиг.1) содержит блок ввода чисел, блок операций с фиксированной запятой, блок операций с плавающей запятой, блок хранения результата, блок управления, пороговые элементы, нейроны.

Для описания алгоритма работы блока 5 управления используются следующие идентификаторы:

1. БВЧКО - блок ввода чисел и кода операции.

2. БОФЗ - блок выполнения операций с фиксированной запятой.

3. БОПЗ - блок выполнения операций с плавающей запятой.

4. БХР - блок хранения результатов.

5. БУ - блок управления.

6. БРгПЧ - блок регистра первого числа.

7. БСВ - блок сумматора-вычитателя.

8. БРгВЧ - блок регистра второго числа.

9. БФЗР - блок формирования знакового разряда.

10. БРгРЕЗ - блок регистра результата.

11. ВХЧ - входные числа.

12. ЗРПЧ - знаковый разряд первого числа.

13. ЗРВЧ - знаковый разряд второго числа.

14. ЗЗР - знаковый разряда большего по модулю числа.

15. ЗРРЗ - знаковый разряд результата.

16. РЕЗ - окончательный результат.

17. ПЧ - первое число.

18. ВЧ - второе число.

19. ОСТ - остаток при делении.

20. ПДЧ - признак дробной части при делении.

21. ЦДЧ - целая и дробная часть результата при делении.

22. УПР - сигналы управления в блок регистра результата.

23. СУП - сигналы управления (обнуление, синхронизация, разрешение записи, сдвига блока регистра второго числа.

24. УП - сигналы управления блока регистра первого числа (обнуление, синхронизация, разрешение записи).

25. РФЗ - результат с фиксированной запятой.

26. РМН - разряд множителя при умножении.

27. КОП - код операции (СУМ, ВЫЧ, ДЕЛ, УМН).

28. УМН - операция умножения.

29. СУМ - операция суммирования.

30. ВЫЧ - операция вычитания.

31. ДЕЛ - операция деления.

32. ЗрВЧi - двоичные разряды второго числа.

33. ЗрПЧi - двоичные разряды первого числа.

34. ЗрПЧ - знаковый разряд первого числа.

35. ЗрВЧ - знаковый разряд второго числа.

36. ЗрОСТ - знаковый разряд остатка при делении чисел.

37. ППР - признак пустого регистра второго числа.

38. РЗАП - сигнал разрешения записи информации в регистр первого числа блока регистра первого числа.

39. ОБЛ - сигнал обнуления триггеров регистра первого числа блока регистра первого числа.

40. СДВ - сигнал сдвига информации влево на один разряд регистра первого числа блока БРгПЧ.

41. ВХД - выходные данные блока ввода чисел и кода операции.

42. РПЗ - результат с плавающей запятой.

43. РРФЗ - разрешение работы блока с фиксированной запятой.

44. КРБФЗ - конец работы блока с фиксированной запятой.

45. РРПЗ - разрешение работы блока с плавающей запятой.

46. КРБФЗ - конец работы блока с фиксированной запятой.

47. ОРБПЗ - окончание работы блока с плавающей запятой.

48. ГИ - генератор прямоугольных импульсов.

49. ТИ - тактовые импульсы.

50. ВК - сигнал выбора кристала.

51. Зп/Сч - сигнал записи/считывания информации из ОЗУ.

52. СВ - признак операций суммирования или вычитания.

53. Зрi - двоичные разряды остатка.

54. Дрi - двоичные разряды входного числа.

55. ЗАЕМ - управляющий сигнал заема из старших разрядов при вычитании чисел.

56. РЕЗi - двоичные разряды резутата.

57. Pi - перенос из младших разрядов в старшие.

58. Zi - заем из старших разрядов в младшие.

59. Ri - двоичный разряд разности при выполнении операции вычитания.

60. Si - двоичный разряд суммы при выполнении операции суммирования.

61. ССБ - сигнал сброса триггеров блока второго числа.

62. СЗ - сигнал разрешения записи информации в триггере блока второго числа.

63. ССД - сигнал сдвига информации вправо на один разряд блока второго числа.

64. ВВЧi - входная информация триггеров блока второго числа.

65. ВЧi - выходная информация триггеров блока второго числа.

66. ЗнРР - выходное знаковое значение результата.

67. СС - сигнал сдвига информации влево на один разряд блока результата.

68. УС0 - установка в нулевое значение триггеров блока результата.

69. БУОФЗ - блок управления операциями с фиксированной запятой.

70. СБРОС - сигнал сброса (обнуления) всех комбинационных блоков и элементов памяти арифметического вычислителя.

71. ПУСК - сигнал начала работы арифметического вычислителя.

Работа алгоритма управления арифметического вычислителя.

Содержательная ГСА управления приведена на фиг.11а и фиг.11б и отражает работу блока управления (фиг.1).

В блоке 2 алгоритма осуществляется подача сигнала установки в нулевое состояние - СБРОС на входы всех элементов устройства.

В блоке 3 алгоритма происходит установка сигнала - пуск в единичное значение ПУСК:=1.

В блоке 4 алгоритма управляющий сигнал разрешения работы блока, выполняющего операции с фиксированной запятой, РРФЗ:=1 принимает единичное значение. Арифметический вычислитель выполняет операции в формате с фиксированной запятой.

В блоке 5 алгоритма по команде БОФЗ:=ВХД блок операций с фиксированной запятой принимает входные числовые значения и код операции.

В блоке 6 алгоритма по команде БРгПЧ:=ВХЧ блок регистр первого числа принимает числовое значение первого числа, по команде БРгВЧ:=ВЧ блок регистр второго числа принимает двоичный код второго числа, по команде БФЗР:=КОП на вход блока формирования знакового разряда поступает код операции для выполнения операции дешифрации и формирования режимов работы вычислителя (фиг.3).

В блоках 7-17 алгоритма происходят вычисление суммы чисел, формирование знака результата и запись полученного результата в регистр результата.

В блоке 7 алгоритма анализируется сигнал операции суммирования чисел - СУМ. Если установлена операция суммирования - выход ДА, то осуществляется переход на блок 8 алгоритма, иначе - выход НЕТ на блок 18.

В блоке 8 алгоритма по команде СВ:=0 устанавливается сигнал СВ - суммирование-вычитание в нулевое значение, тем самым устанавливаются режимы функционирования блока по выполнению операции суммирования входных чисел.

В блоке 9 алгоритма по командам БСВ:=ПЧ и БСВ:=ВЧ блок сумматора-вычитателя принимает значения первого и второго чисел соответственно для выполнения операции суммирования.

В блоке 10 алгоритма, используя операцию суммы по модулю два знаковых разрядов первого и второго чисел - ЗрПЧ и ЗрВЧ, происходят вычисление и анализ результата этой операции ЗрПЧ ⊕ ЗрВЧ. Если результат этой операции равен нулю, то это означает, что необходимо выполнять операцию сложения, так как числа имеют одинаковые знаковые разряды, и установлена операция в блоке 8 алгоритма - суммирование. В этом случае осуществляется переход на блок 15 алгоритма - выход нуль. Если результат в блоке 10 алгоритма равен единице, то это означает, что входные числа имеют разные знаковые разряды и при этом необходимо выполнить операцию вычитания. По выходу - единица данного блока осуществляется переход на блок 11 алгоритма.

В блоке 11 алгоритма по команде РЕЗ:=ПЧ-ВЧ вычисляется разность между первым ПЧ числом и вторым ВЧ.

В блоке 12 алгоритма анализируется сигнал ЗАЕМ - результат вычитания первого и второго чисел. Если ЗАЕМ равен нулю - выход нуль блока, то осуществляется переход на блок 16 алгоритма. В этом случае при выполнении операции вычитания первое число оказалось больше второго, разность между числами получена положительная. Если сигнал ЗАЕМ равен единице - выход единица блока 12 алгоритма, то это означает, что первое число меньше второго и для получения положительной разности необходимо поменять местами входные числа и от второго большего числа вычесть первое меньшее.

В блоке 13 алгоритма по команде РЕЗ:=ВЧ-ПЧ вычисляется разность между вторым ВЧ числом и первым ПЧ.

В блоке 14 алгоритма по команде ЗРРЗ:=ЗРВЧ знаковому разряду результата присваивается знаковый разряд второго большего числа.

В блоке 15 алгоритма по команде РЕЗ:=ПЧ+ВЧ вычисляется сумма первого ПЧ и второго числа ВЧ.

В блоке 16 алгоритма по команде ЗРРЗ:=ЗРПЧ знаковому разряду результата присваивается знаковый разряд первого числа ПЧ.

В блоке 17 алгоритма по команде БРгРЕЗ:=РЕЗ в блок регистр результата записывается результат - сумма в случае равенства знаковых разрядов чисел и разность, если знаковые разряды операндов различные.

В блоках 18-28 алгоритма происходит вычисление разности чисел, формирование результата и его знакового разряда, а также запись полученного результата в регистр результата.

В блоке 18 алгоритма анализируется сигнал операции вычитания чисел - ВЫЧ. Если установлена операция вычитания - выход ДА, то осуществляется переход на блок 19 алгоритма, иначе - выход НЕТ на блок 29.

В блоке 19 алгоритма по команде СВ:=1 устанавливается сигнал СВ - суммирование-вычитание в единичное значение, это означает, что устанавливается режим функционирования вычитателя для выполнения операции вычитания входных чисел.

В блоке 20 алгоритма по командам БСВ:=ПЧ и БСВ:=ВЧ блок сумматора-вычитателя принимает значения первого ПЧ и второго ВЧ чисел соответственно для выполнения операции вычитания.

В блоке 21 алгоритма, применяя операцию сумму по модулю два знаковых разрядов первого и второго чисел - ЗрПЧ и ЗрВЧ, - происходят вычисление и анализ результата этой операции ЗрПЧ ⊕ ЗрВЧ. Если результат этой операции равен единице, то это означает, что необходимо выполнять операцию сложения, так как числа имеют разные знаковые разряды и установлена операция в блоке 19 алгоритма - вычитание. В этом случае осуществляется переход на блок 26 алгоритма - выход единица. Если результата в блоке 21 алгоритма равен нулю, то это означает, что входные числа имеют одинаковые знаковые разряды и при этом необходимо выполнить операцию вычитание. По выходу - нуль блока 21 алгоритма осуществляется переход на блок 22 алгоритма.

В блоке 22 алгоритма по команде РЕЗ:=ПЧ-ВЧ вычисляется разность между первым ПЧ числом и вторым ВЧ.

В блоке 23 алгоритма анализируется сигнал ЗАЕМ - результат вычитания первого и второго чисел. Если ЗАЕМ равен нулю - выход нуль блока, то осуществляется переход на блок 27 алгоритма. В этом случае при выполнении операции вычитания первое число оказалось больше второго, разность между числами получена положительная. Если сигнал ЗАЕМ равен единице - выход единица блока 23 алгоритма, то это означает, что первое число меньше второго. В этом случае, чтобы получить положительную разность, необходимо поменять местами входные числа и от второго большего числа вычесть первое меньшее.

В блоке 24 алгоритма по команде РЕЗ:=ВЧ-ПЧ вычисляется разность между вторым ВЧ числом и первым ПЧ.

В блоке 25 алгоритма по команде ЗРРЗ:=ЗРВЧ знаковому разряду результата присваивается знаковый разряд второго большего числа.

В блоке 26 алгоритма по команде РЕЗ:=ПЧ+ВЧ вычисляется сумма первого ПЧ и второго числа ВЧ.

В блоке 27 алгоритма по команде ЗРРЗ:=ЗРПЧ знаковому разряду результата присваивается знаковый разряд первого числа ПЧ.

В блоке 28 алгоритма по команде БРгРЕЗ:=РЕЗ в блок регистр результата записываются результат - разность в случае равенства знаковых разрядов чисел - и сумма, если знаковые разряды операндов различные.

В блоке 29 алгоритма анализируется сигнал операции деления чисел - ДЕЛ. Если установлена операция деления - выход ДА, то осуществляется переход на блок 30 алгоритма, иначе - выход НЕТ на блок 49.

В блоке 30 алгоритма по команде СВ:=1 устанавливается сигнал СВ - суммирование-вычитание в единичное значение, это означает, что устанавливается режим функционирования вычитателя для выполнения операции деления входных операндов.

В блоке 31 алгоритма по командам БСВ:=ПЧ и БСВ:=ВЧ блок сумматора-вычитателя принимает значения первого ПЧ и второго ВЧ чисел соответственно для выполнения операции деления, где делимое - первое число ПЧ, делитель - второе число ВЧ для получения первого остатка - OCT.

В блоке 32 алгоритма по команде ОСТ:=ПЧ-ВЧ определяется первый остаток между делимым ПЧ и делителем ВЧ.

Блоки 33-45 алгоритма образуют цикл, в результате которого формируется целая часть частного. Как только целая часть будет получена, то блоки 36-46 вычисляют дробную часть частного до определенной точности - количество знаков после запятой, которая определяется количеством разрядов регистра блока регистра результата.

В блоке 33 алгоритма анализируется сигнал ПДЧ - признак дробной части частного. Если вычисляется целая часть частного, при этом признак ПДЧ равен нулю - выход блока нуль, то осуществляется переход на блок 35 алгоритма. Если вычисляется дробная часть результата - выход единица, то осуществляется переход на блок 34 алгоритма.

В блоке 34 алгоритма по команде ЦДЧ:=1 целая и дробная часть результата принимает значение единицы, это означает, что вычисляются двоичные разряды частного в дробной части.

В блоке 35 алгоритма по команде ЦДЧ:=0 целая и дробная часть результата принимает значение нуля, это означает, что формируются двоичные разряды частного в целой части.

В блоках 36-44 алгоритма анализируется знаковый разряд остатка и при этом определяется двоичный разряд частного. Частное формируется поразрядно согласно алгоритму деления чисел без восстановления остатка.

В блоке 36 анализируется знаковый разряд остатка - ЗрОСТ. Если ЗрОСТ равен единице - выход единица блока, то это означает, что очередной двоичный разряд частного равен нулю и при этом осуществляется переход на блок 41 алгоритма. В случае знакового разряда ЗрОСТ, равного нулевому значению, разряд частного при этом будет равен единице. В результате этого осуществляется переход на блок 37 алгоритма.

В блоке 37 алгоритма по команде БРгРЕЗ:=1 происходит загрузка единичного значения частного в регистр блока регистра результата.

В блоке 38 алгоритма по команде БРгПЧ:=ОСТ в регистр блока первого числа записывается очередной остаток - ОСТ для формирования частного заданной точности.

В блоке 39 по команде БРгПЧ:=СДВ на вход регистра блока регистра первого числа поступает управляющий сигнал сдвига СДВ из блока управления, для выполнения операции сдвига информации влево на один разряд, находящийся в регистре блока.

В блоке 40 алгоритма по команде БРгРЕЗ:=СС на вход блока регистра результата поступают управляющий сигнал СС - сдвига информации влево на один разряд, тем самым формируются двоичные разряды частного. По команде ОСТ:=ПЧ-ВЧ вычисляется разность между предшествующим остатком и делителем, при этом вычисляется очередной остаток.

В блоке 41 алгоритма по команде БРгРЕЗ:=0 происходит загрузка нулевого значения частного в регистр блока регистра результата.

В блоке 42 алгоритма по команде БРгПЧ:=ОСТ в регистр блока первого числа записывается очередной остаток - ОСТ для формирование частного заданной точности.

В блоке 43 по команде БРгПЧ:=СДВ на вход регистра блока регистра первого числа поступает управляющий сигнал сдвига - СДВ из блока управления для выполнения операции сдвига информации влево на один разряд.

В блоке 44 алгоритма по команде БРгРЕЗ:=СС на вход блока регистра результата поступает управляющий сигнал СС - сдвига информации влево на один разряд, тем самым формируются двоичные разряды частного. По команде ОСТ:=ПЧ+ВЧ происходит сложение с предшествующим остатком и делителем, тем самым вычисляется очередной остаток.

В блоке 45 алгоритма анализируется информационный сигнал ЦДЧ - целая и дробная часть частного. Если этот сигнал равен нулевому значению - выход нуль блока, то осуществляется переход на блок 33 алгоритма. В этом случае вычисляются разряды целой части частного и после очередного полученного разряда целой части происходит проверка на признак дробной части. Этот цикл формирует целую часть частного до получения признака конца разрядов целой части делимого, скажем, до обнаружения кода запятой в двоичном числе делимого. Если этот признак ЦДЧ равен единице - выход единица блока, то это означает, что целая часть частного получена и при этом необходимо получать двоичные разряды дробной части результата. С выхода блока 45 по единице осуществляется переход на блок 46 алгоритма.

В блоке 46 алгоритма анализируется признак получения окончательного результата - РЕЗ. Если не все двоичные разряды частного сформированы, то осуществляется переход на блок 36 алгоритма - выход блока НЕТ. В этом случае процесс получения разрядов частного продолжается в циклическом режиме до получения частного с заданной точностью в дробной части. По выходу - ДА этого блока осуществляется переход на блок 47 алгоритма.

В блоке 47 алгоритма по команде БРгРЕЗ:=РЕЗ окончательный результат - частное входных чисел записывается в регистр блока регистра результата.

В блоке 48 алгоритма определяется знаковый разряд частного - ЗРРЗ по операции суммы по модулю два знаковых разрядов первого числа ПЧ и второго числа ВЧ. Определение знака осуществляется по команде ЗРРЗ:=ЗРПЧ ⊕ ЗРВЧ.

В блоке 49 алгоритма по команде БСВ:=УМН на вход блока сумматора-вычитателя поступает управляющий сигнал УМН для выполнения операции умножения между входными числами. Известны несколько способов умножения чисел в двоичной системе счисления. В представленном вычислителе произведение чисел первого числа ПЧ и второго числа ВЧ выполняется путем умножения с младших разрядов множителя со сдвигом множимого влево.

Блоки 50-54 алгоритма формируют цикл, в котором анализируется разряд множителя, начиная с младшего, затем происходит суммирование накапливаемой суммы частичных произведений со сдвинутым влево на один или несколько разрядов множимым.

В блоке 50 алгоритма анализируется управляющий сигнал - признак произведения ППР, при котором окончательно будет сформировано произведение чисел. Если признак произведения ППР равен нулю - выход нуль блока, то это означает, что все двоичные значимые разряды множителя просмотрены в регистре блока регистров второго числа и при этом осуществляется переход на блок 55 алгоритма, в котором формируется окончательный результат. Если признак произведения ППР равен единице - выход единица блока - это означает, что не все разряды множителя просмотрены, процесс вычисления произведения продолжается в циклическом режиме. При этом осуществляется переход на блок 51 алгоритма.

В блоке 51 алгоритма по команде БРгВЧ:=ССД на вход регистра блока регистра второго числа поступает сигнал сдвига вправо на один разряд для анализа очередного двоичного разряда множителя - РМН.

В блоке 52 алгоритма анализируется очередной разряд множителя - РМН. Если разряд множителя РМН равен нулевому значению - выход нуль блока, то осуществляется переход на блок 54 алгоритма. В этом случае не происходит суммирования частичных произведений со сдвинутым множимым. Если двоичный разряд множителя равен единице - выход единица блока, то осуществляется переход на блок 53 алгоритма.

В блоке 53 алгоритма по команде БСВ:=ПЧ+БСВ происходит суммирование частичных произведений со сдвинутым влево множимым.

В блоке 54 алгоритма по команде БРгПЧ:=СДВ на вход регистра блока регистра первого числа поступает из блока управления сигнал сдвига влево на один разряд, в этом регистре хранится множимое.

В блоке 55 алгоритма по команде БРгРЕЗ:=РЕЗ произведение входных чисел записывается в регистр блока регистра результата.

В блоке 56 алгоритма определяется знаковый разряд произведения - ЗРРЗ по операции суммы по модулю два знаковых разрядов первого числа ПЧ и второго числа ВЧ. Определение знака осуществляется по команде ЗРРЗ:=ЗРПЧ ⊕ ЗРВЧ.

Блок 57 алгоритма является конечным.

Работа арифметического вычитателя заключается в следующем.

Внешние управляющие сигналы "СБРОС" и "ПУСК" поступают в блок 5 управления.

Предлагаемое арифметическое устройство выполняет операции суммирования, вычитания, умножения и деления в параллельном формате. Определяется перенос в старшие разряды при суммировании, который необходимо учитывать при сложении чисел. Вычисляется заем из старших разрядов в младшие при вычитании. Умножение выполняется младшими разрядами множителя со сдвигом суммы частичных произведений влево. Операция деления осуществляется по алгоритму деления чисел без восстановления остатков.

Блок 1 ввода чисел и кода операций - БВЧКО содержит шифратор (обычная стандартная клавиатура) ШФ DD6, дешифратор DD7 (фиг.2). Этот блок позволяет вводить двоичные числа и дешифрировать код операций, т.е. распознать, какую операцию необходимо выполнить вычислителю - сложение, вычитание, умножение, деление. С выхода шифратора формируется двоичный код чисел со своими знаками: ЗрiПЧ, ЗрiВЧ, ЗРПЧ, ЗРВЧ в виде информационного сигнала - ВХЧ. Двоичные разряды с выхода шифратора поступают на вход регистров первого и второго числа. С выхода дешифратора кода операций DD7 (фиг.2) формируется информационный сигнал КОП - код операций, который поступает на вход блока формирования знакового разряда (фиг.3). В зависимости от кода операции вычислитель выполняет соответствующую арифметическую операцию. Выходным информационным сигналом блока 1 БВЧКО является сигнал - ВХД - выходные данные.

Блок 2 операций с фиксированной запятой содержит: блок 8 формирования знакового разряда результата - БФЗР, блок 9 регистра первого числа - БРгПЧ, блок 10 сумматора - вычитателя - БСВ, блок 11 регистра второго числа - БРгВЧ, блок 12 регистра результата - БРгРЕЗ, блок 13 управления операциями с фиксированной запятой - БУОФЗ (фиг.3). Основная функция этого блока заключается в вычислении результата и формировании знакового разряда результата при выполнении операций: умножение и деление, а также определения типа операций: сложение или вычитание. На информационные входы блоков 9 и 11 регистров первого и второго числа поступают входные операнды - ВХЧ из блока 2 ввода чисел (фиг.2, 3). В случае выполнения операций умножения или деления этот блок по операции суммы по модулю два определяет знаковый разряд результата - ЗРРЗ, поступающий на вход блока 12 регистра результата ЗРРЗ=ЗРПЧ ⊕ ЗРВЧ, где ЗРПЧ - знаковый разряд первого числа, ЗРВЧ - знаковый разряд второго числа. Если вычислитель выполнял операции сложения или вычитания, то знаковый разряд результата ЗЗР формируется в блоке 10 сумматора-вычитателя и поступает на вход блока 8 формирования знакового разряда. На управляющие входы блоков 9, 11, 12 регистра первого числа, второго числа, результата из блока 13 управления операциями с фиксированной запятой поступают соответственно информационные сигналы: УП на блок 9 регистра первого числа, СУП на блок 11 регистра второго числа, УПР на блок 12 регистра результата. По приходу сигналов осуществляются обнуление регистров этих блоков, синхронизация по записи информации, а также сигналы сдвига в блоки регистров первого и второго числа. На входы блока сумматора-вычитателя поступают двоичные коды чисел ПЧ - первое число и ВЧ - второе число для выполнения операций сложения, вычитания, умножения и деления. На вход блока 10 сумматора-вычитателя из блока 8 формирования знакового разряда поступают управляющие сигналы: СВ - суммирование-вычитание для управления по выполнению операций суммирования или вычитания и УМН - умножение для выполнения операции произведения чисел. Из блока 10 сумматора-вычитателя выходной управляющий сигнал ЗрОСТ - знаковый разряд остатка - поступает на вход блока 8 формирования знакового разряда и на вход блока 12 регистра результата для определения признака операции - сигнала СВ и очередной цифры частного при выполнении операции деления. Выходным управляющим сигналом блока 10 сумматора-вычитателя является сигнал - ЗЗР знаковый разряд, который поступает на вход блока 8 для формирования окончательного знака результата. Выходной сигнал блока 10 сумматора-вычитателя ОСТ - остаток, поступает на вход блока 9 регистра первого числа, формирование этого сигнала необходимо при выполнении операции деления. Выходной информационный сигнал РЕЗ является результатом операций, который поступает на вход блока 12 регистра результата. Выходным информационным сигналом блока 12 регистра результата является сигнал РФЗ - результат с фиксированной запятой. С входа блока 9 регистра первого числа на вход блока 13 управления операциями с фиксированной запятой поступает управляющий сигнал ПДЧ - признак дробной части при делении, который является признаком конца целой части двоичного первого числа. При поступлении этого сигнала на блок управления необходимо установить знак, отделяющий целую часть числа от дробной в блоке 12 регистра результата. На вход блока 12 регистра результата поступает с выхода блока 13 управления операциями с фиксированной запятой признак целой и дробной части результата при делении - ЦДЧ, который формирует позицию, отделяющую целую часть от дробной (точку или запятую). На вход блока 8 формирования знакового разряда поступает информационный сигнал КОП - код операции сложения, вычитания, умножения и деления, этот сигнал поступает на вход блока 13 управления операциями с фиксированной запятой для анализа и генерации соответствующих управляющих сигналов, поступающих на входы блоков. С выхода блока 11 регистра второго числа выходит управляющий сигнал РМН - соответствующий значению двоичного разряда второго числа при выполнении операции умножения вычислителем, который поступает на вход блока 9 регистра первого числа. При РМН равным нулю, происходит сдвиг двоичного числа блока 9 регистра первого числа на один разряд влево, если сигнал РМН равен единице, то блок 10 суммирования-вычитания принимает значение из блока 9 регистра первого числа. Выходной управляющий сигнал ППР - признак пустого регистра - поступает на вход блока 13 управления операциями с фиксированной запятой. Этот сигнал принимает значение