Дифференциальный усилитель с повышенным ослаблением синфазного сигнала

Иллюстрации

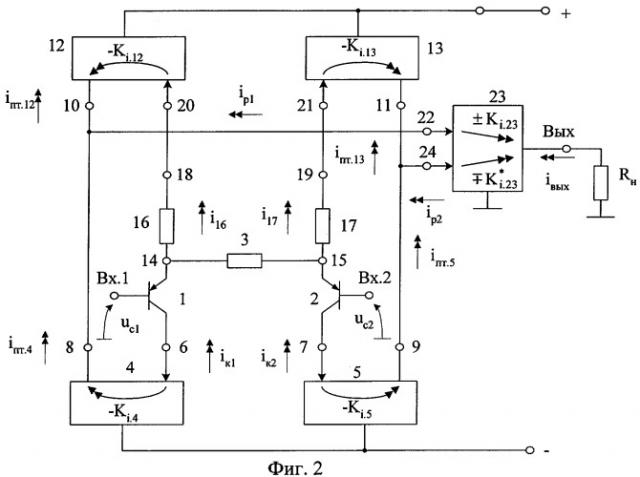

Показать всеИзобретение относится к радиотехнике для использования в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в повышении коэффициента ослабления входного синфазного сигнала. Дифференциальный усилитель (ДУ) (фиг.2) содержит входные транзисторы (Т) (1, 2), между эмиттерами которых включен резистор (Р) (3) местной обратной связи, первое (4) и второе (5) токовые зеркала (ТЗ), входы которых (6) и (7) связаны с коллекторами входных Т (1, 2), а выходы (8, 9) соединены с выходами (10, 11) третьего (12) и четвертого (13) ТЗ, причем эмиттеры входных Т (1, 2) соединены с первыми выводами (14, 15) токостабилизирующих Р (16, 17), вторые выводы (18, 19) которых подключены ко входам (20, 21) третьего (12) и четвертого (13) ТЗ, выходы первого (4) и третьего (12) ТЗ соединены с первым (22) токовым входом дополнительного сумматора токов (23), а выходы (9) и (11) второго (5) и четвертого (13) ТЗ соединены со вторым токовым входом (24) сумматора токов (23). 1 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы классических дифференциальных усилителей (ДУ), реализованных на основе двух входных транзисторов с токостабилизирующими резисторами в их эмиттерных цепях и резистором местной отрицательной обратной связи, включенным между эмиттерами входных транзисторов [1-7]. Такие ДУ стали одним из основных элементов современной аналоговой микросхемотехники, широко используются в структуре различных прецизионных преобразователей «напряжение-ток». Существенный недостаток таких ДУ состоит в том, что они имеют невысокие значения коэффициента ослабления входного синфазного сигнала (Кос.сф), который существенно зависит от сопротивлений токостабилизирующих резисторов.

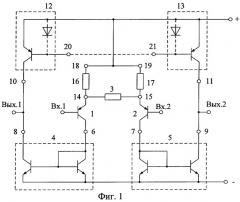

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте ЕР №1351381 А1 (он же - в патенте США №6657465 В2), содержащий первый 1 и второй 2 входные транзисторы, между эмиттерами которых включен резистор 3 местной обратной связи, первое 4 и второе 5 токовые зеркала, входы которых 6 и 7 связаны с коллекторами входных транзисторов 1 и 2, а выходы 8 и 9 соединены с выходами 10, 11 третьего 12 и четвертого 13 токовых зеркал, причем эмиттер первого 1 и второго 2 входных транзисторов соединены с первыми выводами 14 и 15 токостабилизирующих резисторов 16 и 17.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ при использовании сравнительно низкоомных токостабилизирующих резисторов 16 и 17.

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 и второй 2 входные транзисторы, между эмиттерами которых включен резистор 3 местной обратной связи, первое 4 и второе 5 токовые зеркала, входы которых 6 и 7 связаны с коллекторами входных транзисторов 1 и 2, а выходы 8 и 9 соединены с выходами 10, 11 третьего 12 и четвертого 13 токовых зеркал, причем эмиттер первого 1 и второго 2 входных транзисторов соединены с первыми выводами 14 и 15 токостабилизирующих резисторов 16 и 17, вводятся новые элементы и связи - вторые выводы 18 и 19 токостабилизирующих резисторов 16 и 17 подключены ко входам 20 и 21 третьего 12 и четвертого 13 токовых зеркал, выходы первого 4 и третьего 12 токовых зеркал соединены с первым 22 токовым входом дополнительного сумматора токов 23, а выходы 9 и 11 второго 5 и четвертого 13 токовых зеркал соединены со вторым токовым входом 24 дополнительного сумматора токов 23.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

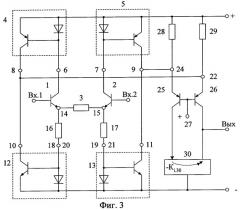

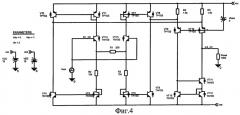

На фиг.3 показан заявляемый ДУ в соответствии с п.2 формулы изобретения. Результаты компьютерного моделирования ДУ фиг.3 в среде PSpice при синфазном входном сигнале на моделях интегральных транзисторов ФГУП НПП «Пульсар» и параметрах элементов и режимах, указанных на фиг.4, показаны на фиг.5 и 6. Причем графики фиг.5 сняты при сопротивлении нагрузки ДУ Rн=100 кОм, а графики фиг.6 при Rн=1 кОм.

На фиг.7 представлена схема ДУ фиг.3 (фиг.4) для случая, когда инвертирующий повторитель тока 30 (F1) является идеальным усилительным элементом, т.е. имеет коэффициент передачи по току, равный единице в широком диапазоне частот (Кi.30=1). Это позволяет выявить предельные возможности заявляемого ДУ по ослаблению синфазных сигналов, которые представлены характеристиками фиг.8 (при Rн=100 кОм) и фиг.9 (при Rн=1 кОм).

На фиг.5-9 приняты следующие обозначения параметров ДУ:

Kуд - коэффициент передачи дифференциального входного напряжения ДУ uвх;

Кус - коэффициент передачи синфазного входного напряжения uc.

Причем между этими параметрами и коэффициентом ослабления входных синфазных сигналов Кос.сф существует следующая взаимосвязь:

где uвх - напряжение между входами ДУ;

uc - синфазное входное напряжение на входах ДУ;

uвых - выходное напряжение ДУ (uвых=iвыхRн);

Rн - сопротивление нагрузки, подключаемое к выходу ДУ;

Sсс - крутизна передачи ДУ по дифференциальному входному сигналу uвх;

Sдс - крутизна передачи ДУ по синфазному входному сигналу uc.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, между эмиттерами которых включен резистор 3 местной обратной связи, первое 4 и второе 5 токовые зеркала, входы которых 6 и 7 связаны с коллекторами входных транзисторов 1 и 2, а выходы 8 и 9 соединены с выходами 10, 11 третьего 12 и четвертого 13 токовых зеркал, причем эмиттер первого 1 и второго 2 входных транзисторов соединены с первыми выводами 14 и 15 токостабилизирующих резисторов 16 и 17. Вторые выводы 18 и 19 токостабилизирующих резисторов 16 и 17 подключены ко входам 20 и 21 третьего 12 и четвертого 13 токовых зеркал, выходы первого 4 и третьего 12 токовых зеркал соединены с первым 22 токовым входом дополнительного сумматора токов 23, а выходы 9 и 11 второго 5 и четвертого 13 токовых зеркал соединены со вторым токовым входом 24 дополнительного сумматора токов 23.

В соответствии с п.2 формулы изобретения (фиг.3) дополнительный сумматор тока 23 содержит первый 25 и второй 26 выходные транзисторы с объединенными базами, которые подключены к источнику смещения 27, эмиттеры первого 25 и второго 26 выходных транзисторов, являющиеся первым 22 и вторым 24 токовыми входами дополнительного сумматора токов 23, связаны со вспомогательными токостабилизирующими двухполюсниками 28 и 29, а коллектор первого 25 выходного транзистора соединен с коллектором второго выходного транзистора 26 и выходом дифференциального усилителя через инвертирующий повторитель тока 30.

Рассмотрим работу заявляемого ДУ фиг.2.

Если на входы ДУ подать синфазное напряжение uc=uc1=uc2, то в резисторах 16, 17 появятся переменные составляющие токов

где - проводимости токостабилизирующих резисторов 16 и 17 соответственно.

Эти приращения токов i16, i17, которые равны соответствующим приращениям токов эмиттеров транзисторов 1, 2, передаются, с одной стороны, на входы 6 и 7 и выходы 8, 9 токовых зеркал 4 и 5, а с другой - на входы 20 и 11, а затем выходы 10, 21 токовых зеркал 12 и 13:

где αi≈1 - коэффициент передачи по току эмиттера i-го транзистора.

Следует обратить внимание, что в узлах 22 и 24 происходит первое вычитание близких по величине выходных токов токовых зеркал

или

Разности выходных токов ip1, ip2 токовых зеркал 12 и 4, 13 и 5, обусловленные отличием их коэффициентов передачи по току Кi.12 и Кi.4, а также Кi.13 и Ki.5 поступают на входы дополнительного сумматора токов 23, в котором происходит их вычитание систематических ошибок усиления синфазного сигнала. Выходной ток ДУ

Поэтому выходное напряжение ДУ, обусловленное наличием на его входах синфазного сигнала uc

Следовательно, коэффициент передачи синфазного сигнала со входа ДУ на его выход

где - коэффициент асимметрии, учитывающий неидентичность резисторов 17 и 16, а также усилений по току со входов 22 и 24 сумматора 23.

При высокой идентичности y17 и y16, Ki.23 и коэффициент асимметрии принимает единичное значение Кac=1. Как следствие коэффициент передачи синфазного сигнала будет определяться только разностью близких по величине коэффициентов усиления Кi.12 и Кi.13, Ki.4 и Кi.5, α1 и α2. Так как токовые зеркала 12 и 13, 4 и 5 попарно идентичны, выполнены по одинаковым схемам, то поэтому передача синфазного сигнала на выход

Kсф=Rнy16Ki.23[Ki.12-Ki.13+α2Ki.5-α1Ki.4]≈0.

Отличие коэффициентов передач по току Ki.12 и Кi.13, Ki.4 и Кi.5 обусловлено в реальных схемах неодинаковыми значениями β применяемых р-n-р (12, 13) и n-p-n (4, 5) транзисторов, а также неодинаковыми значениями их статического режима по напряжению коллектор-база. Именно эти причины приводят к появлению токовых ошибок ip1 и ip2, которые поступают на входы 22 и 24 дополнительного сумматора 23. Однако входные токи ip1=ip2 дополнительного усилителя 23 будут иметь почти одинаковые значения, т.к. токовые зеркала 4 и 5, а также 12 и 13 попарно идентичны.

Как уже отмечалось выше, схемотехническим и технологическим путем достаточно просто обеспечить равенства , α1=α2, при котором на выходе дополнительного сумматора 23 будут отсутствовать составляющие, обусловленные входным синфазным сигналом, то есть крутизна преобразования входного синфазного напряжения в выходной ток Sсс=iвых/uс будет близка к нулю, а Кос.сф≫1.

Коэффициент передачи дифференциального входного напряжения ДУ фиг.2 определяется по формуле

Если (как это имеет место в ДУ фиг.3), то

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва). Коэффициент ослабления синфазного входного сигнала ДУ фиг.4 превышает величину Kос.сф>105 (100 дБ) в достаточно широком диапазоне частот - до 5,6 МГц (фиг.5), а при низкоомной нагрузке (фиг.6) он больше в 107 (140 дБ) до частоты 1 МГц. Следует отметить, что данные значения Kос.сф значительно лучше аналогичных параметров лучших зарубежных операционных усилителей.

Кроме этого, высокий Кос.сф получен без использования источников опорного тока во входном каскаде. Это достигнуто путем обеспечения полной симметрии ДУ и создания дополнительных условий взаимной компенсации систематических погрешностей усиления сигнала по двум идентичным каналам передачи со входов ДУ на его выход.

Путем совершенствования схемотехники инвертирующего повторителя тока 30 (фиг.3 и 4) - приближения его коэффициента усиления по току к единице в широком диапазоне частот, в заявляемом устройстве возможно получение высоких Кос.сф (100 ДБ) до частоты 26 МГц.

В рассматриваемой схеме ДУ обеспечивается также высокая степень параметрической компенсации влияния температуры и радиации на э.д.с. смещения нуля, обусловленной смещением входных и выходных характеристик транзисторов.

Источники информации

1. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с. - стр.156 рис.4.25.

2. Патент США №4131809, H 03 FK.

3. Патент США №3323070, H 03 F 3/45.

4. Патент ЕР №1351381, А1, H 03 F 3/30.

5. Патент США №5365191, H 03 F 3/45.

6. Патент США №4511852, H 03 F 3/45.

7. Патент США №6657465, H 03 F 3/45.

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, между эмиттерами которых включен резистор (3) местной обратной связи, первое (4) и второе (5) токовые зеркала, входы которых (6) и (7) связаны с коллекторами входных транзисторов (1) и (2), а выходы (8) и (9) соединены с выходами (10), (11) третьего (12) и четвертого (13) токовых зеркал, причем эмиттер первого (1) и второго (2) входных транзисторов соединены с первыми выводами (14) и (15) токостабилизирующих резисторов (16) и (17), отличающийся тем, что вторые выводы (18) и (19) токостабилизирующих резисторов (16) и (17) подключены ко входам (20) и (21) третьего (12) и четвертого (13) токовых зеркал, выходы первого (4) и третьего (12) токовых зеркал соединены с первым (22) токовым входом дополнительного сумматора токов (23), а выходы (9) и (11) второго (5) и четвертого (13) токовых зеркал соединены со вторым токовым входом (24) дополнительного сумматора токов (23).

2. Устройство по п.1, отличающееся тем, что дополнительный сумматор тока (23) содержит первый (25) и второй (26) выходные транзисторы с объединенными базами, которые подключены к источнику смещения (27), эмиттеры первого (25) и второго (26) выходных транзисторов, являющиеся первым (22) и вторым (24) токовыми входами дополнительного сумматора токов (23), связаны со вспомогательными токостабилизирующими двухполюсниками (28) и (29), а коллектор первого (25) выходного транзистора соединен с коллектором второго выходного транзистора (26) и выходом дифференциального усилителя через инвертирующий повторитель тока (30).