Дифференциальный усилитель с повышенным ослаблением входного синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в повышении коэффициента ослабления входного синфазного сигнала. Усилитель содержит входной параллельно-балансный каскад (1) с первым (2) источником опорного тока в общей эмиттерной цепи, выход которого (3) соединен со входом токового зеркала (4), вспомогательный транзистор (5), коллектор которого подключен к выходу токового зеркала (4) и выходу (6) дифференциального усилителя, а эмиттер соединен со вторым (7) источником опорного тока, первый источник опорного тока (2) в общей эмиттерной цепи входного параллельно-балансного каскада (1) связан с базой вспомогательного транзистора (5). 2 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы классических дифференциальных усилителей (ДУ), реализованных на основе классического параллельно-балансного каскада с источником опорного тока в общей эмиттерной цепи входных транзисторов и токовым зеркалом, выход которого подключен к нагрузке [1-9]. Такие ДУ стали одним из основных элементов современной аналоговой микросхемотехники широко используются в структуре различных прецизионных преобразователей «напряжение-ток» и операционных усилителях. Существенный недостаток таких ДУ состоит в том, что они имеют невысокие значения коэффициента ослабления входного синфазного сигнала (Кос.сф), который существенно зависит от выходного сопротивления источника опорного тока.

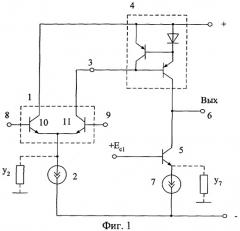

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4.264.873, содержащий входной параллельно-балансный каскад 1 с первым 2 источником опорного тока в общей эмиттерной цепи, выход которого 3 соединен со входом токового зеркала 4, вспомогательный транзистор 5, коллектор которого подключен к выходу токового зеркала 4 и выходу 6 дифференциального усилителя, а эмиттер соединен со вторым 7 источником опорного тока. Источники опорного тока 2 и 7 имеют соответственно выходные проводимости у2 и у7. База транзистора 5 связана с источником опорного напряжения Ec1.

Существенный недостаток известного ДУ (фиг.1) состоит в том, что он имеет невысокое ослабление входных синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ (Кос.сф).

Поставленная цель достигается тем, что в дифференциальный усилитель (фиг.1), содержащий входной параллельно-балансный каскад 1 с первым 2 источником опорного тока в общей эмиттерной цепи, выход которого 3 соединен со входом токового зеркала 4, вспомогательный транзистор 5, коллектор которого подключен к выходу токового зеркала 4 и выходу 6 дифференциального усилителя, а эмиттер соединен со вторым 7 источником опорного тока, вводятся новые связи - первый источник опорного тока 2 в общей эмиттерной цепи входного параллельно-балансного каскада 1 связан с базой вспомогательного транзистора 5. В частном случае параллельно первому 2 источнику опорного тока включен третий 8 источник опорного тока, идентичный первому 2 и второму 7 источникам опорного тока.

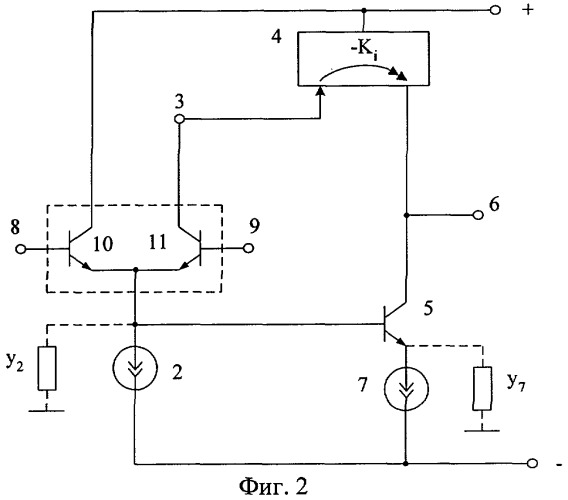

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

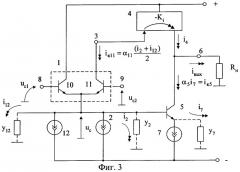

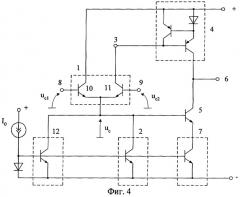

На фиг.3 показан заявляемый ДУ в соответствии с п.2 формулы изобретения, а на фиг.4 - конкретная реализация ДУ фиг.3. Здесь источники опорного тока 2, 7 и 12 реализованы на соответствующих биполярных транзисторах, статический режим которых устанавливается двухполюсником I0.

Схема ДУ в соответствии с п.3 формулы изобретения представлена на фиг.5, а на фиг.6 показан конкретный вариант построения дополнительного повторителя напряжения 13.

Результаты компьютерного моделирования ДУ фиг.1, фиг.4 и 5 в среде PSpice при дифференциальном и синфазном входных сигналах на моделях интегральных транзисторов ФГУП НПП «Пульсар» и параметрах элементов (режимах), указанных на фиг.7 (заявляемый ДУ - фиг.5), фиг.8 (прототип - фиг.1), фиг.9 (заявляемый ДУ - фиг.5), фиг.10 (прототип - фиг.1) показаны на фиг.11, 12 и 13. Причем:

- фиг.7 - схема заявляемого ДУ при подаче на его входы дифференциального сигнала uас.1=uвх;

- фиг.8 - схема ДУ прототипа при подаче на его входы дифференциального сигнала uac.2=uвх;

- фиг.9 - схема заявляемого ДУ (фиг.5) при подаче на его входы синфазного сигнала;

- фиг.10 - схема ДУ прототипа (фиг.1) при подаче на его входы синфазного сигнала;

- фиг.11 - амплитудно-частотная характеристика крутизны (Sдс) преобразования входного дифференциального напряжения заявляемого ДУ (фиг.7) и ДУ прототипа (фиг.8) в их выходные токи;

- фиг.12 - амплитудно-частотные характеристики крутизны преобразования (Scc) входного синфазного напряжения заявляемого ДУ (фиг.9) и ДУ прототипа (фиг.10) в их выходные токи. Причем измерения проводились при подаче на базы входных транзисторов ДУ относительно общей шины одинаковых напряжений uc1=uc2=uс=uac;

- фиг.13 - частотная зависимость коэффициента ослабления входного синфазного напряжения заявляемого (фиг.7, 9) и известного (фиг.8, 10) усилителей.

На фиг.7-13 и в тексте описания приняты следующие обозначения параметров ДУ и элементов схемы:

Куд - коэффициент передачи дифференциального входного напряжения ДУ uвх;

Кус - коэффициент передачи синфазного входного напряжения uc.

Причем между этими параметрами и коэффициентом ослабления входных синфазных сигналов Кос.сф существует следующая взаимосвязь

где uвх - напряжение между входами ДУ;

uc - синфазное входное напряжение на входах ДУ;

uвых - выходное напряжение ДУ (uвых=iвыхRн);

Rн - сопротивление нагрузки, подключаемое к выходу ДУ;

Sдс - крутизна передачи ДУ по дифференциальному входному сигналу uвх;

Scc - крутизна передачи ДУ по синфазному входному сигналу uc;

C1=С2=Cs - емкость на подложку транзисторов источников опорного тока.

Дифференциальный усилитель (фиг.2) содержит входной параллельно-балансный каскад 1 с первым 2 источником опорного тока в общей эмиттерной цепи. Выход 3 каскада 1 соединен со входом токового зеркала 4, причем коллектор вспомогательного транзистора 5 подключен к выходу токового зеркала 4 и выходу 6 дифференциального усилителя, а эмиттер соединен со вторым 7 источником опорного тока. Первый источник опорного тока 2 в общей эмиттерной цепи входного параллельно-балансного каскада 1 связан с базой вспомогательного транзистора 5. Входами 8 и 9 ДУ (фиг.2) являются базы транзисторов 10 и 11.

В соответствии с п.2 формулы изобретения (фиг.3) параллельно первому 2 источнику опорного тока включен третий 12 источник опорного тока, идентичный первому 2 и второму 7 источникам опорного тока.

В соответствии с п.3 формулы изобретения (фиг.5) первый 2 источник опорного тока в общей эмиттерной цепи входного параллельно-балансного каскада 1 связан с базой вспомогательного транзистора 5 через дополнительный повторитель напряжения 13, который в частном случае выполнен на транзисторе 14 и двухполюснике 15 (фиг.6).

Рассмотрим работу заявляемого ДУ на примере анализа схемы (фиг.3).

Если на входы 8 и 9 ДУ (фиг.3) подать синфазное входное напряжение uc=uc1=uc2, то в выходных проводимостях у2, у7, у12 источников опорного тока I2=I7=I12=I0 появятся переменные составляющие

Приращения токов i12, i2 поступают в общую эмиттерную цепь дифференциального каскада 1 и делятся пополам. Как следствие коллекторный ток транзистора 11 (ток выхода 3) и выходной ток i4 токового зеркала 4

где α11≈1 - коэффициент усиления по току эмиттера транзистора 11;

Ki≈1 - коэффициент усиления по току токового зеркала 4.

С другой стороны коллекторный ток транзистора 5

Таким образом, в выходной цепи 6 заявляемого ДУ происходит взаимная компенсация двух близких по величине токов iк5 и i4, обусловленных наличием на его входах 8 и 9 синфазной составляющей входного сигнала uc:

С учетом (1) и (4) из (5) можно найти, что

Причем крутизна передачи синфазного сигнала и коэффициент передачи uc на выход ДУ (фиг.3)

где Rн - сопротивление нагрузки ДУ.

Коэффициент передачи ДУ (фиг.3) по дифференциальному входу

где rэ10, rэ11 - сопротивления эмиттерных переходов транзисторов 10 и 11;

ϕт≈25 мВ - температурный потенциал;

I0=I2=I7=I12.

В заявляемой схеме в соответствии с П2 формулы изобретения за счет интегральной технологии изготовления транзисторов и схемотехники обеспечивается высокая идентичность выходных проводимостей применяемых источников опорного тока 2, 7 и 12: у2=у12=у7=у0.

Поэтому

где I0=I2=I12=I7, у0=у2=у12=у7.

Так как Ki=1, α11=α5≈1, из формулы (12) следует, что Кос.сф в заявляемом ДУ повышается в N раз (по сравнению с ДУ прототипом - фиг.1), где

Реальные значения N достигают одного-двух порядков (N=10÷100 раз).

Полученные выше аналитические выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва).

Коэффициент ослабления синфазного входного сигнала ДУ (фиг.5, 7) превышает величину Кос.сф>94 дБ в достаточно широком диапазоне частот (фиг.13). При этом в заявляемом ДУ (фиг.5, 7) расширяется диапазон частот по дифференциальному сигналу (фиг.11) с 482 до 745 МГц.

В сравнении с ДУ-прототипом (фиг.1, 8), который имеет Кос.сф=63 дБ до частоты 2,4 МГц, заявляемый ДУ позволяет получить более широкий диапазон частот (fвсс=30,7 МГц) с таким же ослаблением синфазного сигнала (фиг.13).

В рассматриваемой схеме ДУ (фиг.2, 3, 4 и 5) обеспечивается также высокая степень параметрической компенсации влияния температуры и радиации на э.д.с. смещения нуля, обусловленной смещением входных и выходных характеристик транзисторов источников опорного тока 2, 7, 12.

Если изменяется напряжение питания ДУ и, как следствие, ток Iо (фиг.4), то в заявляемом устройстве также уменьшается коэффициент подавления помехи по питанию.

Источники информации

1. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983.

2. Патент США №4.264.873, H 03 F 3/45.

3. Патент США №5.365.191, H 03 F 3/45.

4. Патент США №5.936.468, H 03 F 3/45.

5. Патент США №5.551.005, H 03 F 3/45.

6. Патент США №4.783.637, H 03 F 3/45.

7. Патент США №5.291.149, H 03 F 3/45.

8. Патент Японии JP 2004, 040157, H 03 F 3/45.

9. Патент Японии JP 7050528, H 03 F 3/45.

1. Дифференциальный усилитель с повышенным ослаблением входного синфазного сигнала, содержащий входной параллельно-балансный каскад (1) с первым (2) источником опорного тока в общей эмиттерной цепи, выход которого (3) соединен со входом токового зеркала (4), вспомогательный транзистор (5), коллектор которого подключен к выходу токового зеркала (4) и выходу (6) дифференциального усилителя, а эмиттер соединен со вторым (7) источником опорного тока, отличающийся тем, что первый источник опорного тока (2) в общей эмиттерной цепи входного параллельно-балансного каскада (1) связан с базой вспомогательного транзистора (5).

2. Устройство по п.1, отличающееся тем, что параллельно первому (2) источнику опорного тока включен третий (12) источник опорного тока, идентичный первому (2) и второму (7) источникам опорного тока.

3. Устройство по п.1, отличающееся тем, что первый (2) источник опорного тока в общей эмиттерной цепи входного параллельно-балансного каскада (1) связан с базой вспомогательного транзистора (5) через дополнительный повторитель напряжения (13).