Быстродействующий дифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления импульсных сигналов, в структуре аналоговых интерфейсов различного функционального назначения. Технический результат заключается повышении максимальной скорости нарастания выходного напряжения. Усилитель содержит соединенные параллельно по входу первый и второй дифференциальные каскады (ДК), коллекторы первых n-р-n и р-n-р входных транзисторов (Т) (1), (4) соединены со входом (9) буферного усилителя (10) и основным корректирующим конденсатором (К) (11) через первое (12) и второе (13) токовые зеркала. Введены первый (14) и второй (15) дополнительные К, емкость которых выбирается в пределах Сд=(0,3÷1,5)Ск, где Ск - емкость основного К (11) и подключенные к эмиттерам входных Т соответственно первого и второго ДК. При этом коллектор второго (2) входного n-р-n Т соединен со входом второго токового зеркала (13) через первое дополнительное токовое зеркало (16), а коллектор второго (5) р-n-р входного Т соединен со входом первого (12) токового зеркала через второе (17) токовое зеркало. 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления импульсных сигналов, в структуре аналоговых интерфейсов различного функционального назначения.

Известны схемы дифференциальных операционных усилителей (ОУ), реализованных на основе двух параллельно-включенных (по входу) дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые «dual input stage») [1-32]. По такой архитектуре, на модификации которой и на ее применение выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Все ОУ данного класса можно разделить на два больших подкласса - ОУ, в которых каждый из входных дифференциальных каскадов нагружен на токовые зеркала [18-32], и ОУ, в которых входные каскады нагружены на так называемые «перегнутые» каскады - каскады с общей базой [1-17].

ОУ первого подкласса могут иметь так называемый rail-to-rail выходной каскад и отличаются от ОУ второго подкласса несколько меньшими значениями верхней граничной частоты. ОУ второго подкласса имеют наиболее высокие значения верхней граничной частоты, но сравнительно низкое быстродействие из-за нелинейных режимов работы промежуточного каскада. Предлагаемое изобретение относится к первому подклассу ОУ, то есть имеющим токовые зеркала в промежуточном каскаде.

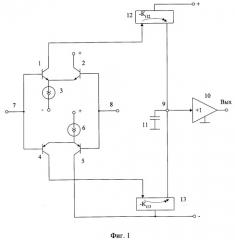

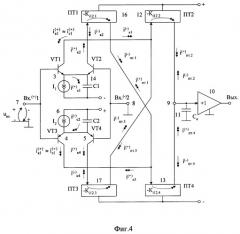

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный операционный усилитель, описанный в патентах США №6268769 (фиг.3), 5291149, 5512859, 5515505, а также патенте Японии JP 7050528. Он содержит первый дифференциальный каскад на первом 1 и втором 2 входных n-р-n транзисторах, в общую эмиттерную цепь которых включен первый 3 источник опорного тока, второй дифференциальный каскад на первом 4 и втором 5 входных р-n-р транзисторах, в общую эмиттерную цепь которых включен второй 6 источник опорного тока, причем базы первых р-n-р и n-р-n входных транзисторов 1, 4 соединены с первым входом 7 быстродействующего дифференциального операционного усилителя, базы вторых р-n-р и n-р-n входных транзисторов 2, 5 соединены со вторым входом 8 быстродействующего дифференциального операционного усилителя, коллекторы первых n-р-n и р-n-р входных транзисторов 1, 4 соединены со входом 9 буферного усилителя 10 и основным корректирующим конденсатором 11 через первое 12 и второе 13 токовые зеркала.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокие значения максимальной скорости нарастания выходного напряжения в режиме большого сигнала ϑвых=80÷180 В/мкс (низкое быстродействие).

Основная цель предлагаемого изобретения состоит в повышении быстродействия дифференциального операционного усилителя в режиме большого сигнала - увеличении максимальной скорости нарастания выходного напряжения ϑвых на один-два порядка.

Поставленная цель достигается тем, что в дифференциальный операционный усилитель фиг.1, содержащий первый дифференциальный каскад на первом 1 и втором 2 входных n-р-n транзисторах, в общую эмиттерную цепь которых включен первый 3 источник опорного тока, второй дифференциальный каскад на первом 4 и втором 5 входных р-n-р транзисторах, в общую эмиттерную цепь которых включен второй 6 источник опорного тока, причем базы первых р-n-р и n-р-n входных транзисторов 1, 4 соединены с первым входом 7 быстродействующего дифференциального операционного усилителя, базы вторых р-n-р и n-р-n входных транзисторов 2, 5 соединены со вторым входом 8 быстродействующего дифференциального операционного усилителя, коллекторы первых n-р-n и р-n-р входных транзисторов 1, 4 соединены со входом 9 буферного усилителя 10 и основным корректирующим конденсатором 11 через первое 12 и второе 13 токовые зеркала, вводятся новые элементы и связи между ними - в схему введены первый 14 и второй 15 дополнительные корректирующие конденсаторы, первое 16 и второе 17 дополнительные токовые зеркала, причем первый дополнительный корректирующий конденсатор 14 подключен к эмиттерам первого 1 и второго 2 n-p-n входных транзисторов, второй дополнительный корректирующий конденсатор 15 подключен к эмиттерам первого 4 и второго 5 входных р-n-р транзисторов, коллектор второго 2 входного n-p-n транзистора соединен со входом второго токового зеркала 13 через первое дополнительное токовое зеркало 16, а коллектор второго 5 р-n-р входного транзистора соединен со входом первого 12 токового зеркала через второе 17 токовое зеркало.

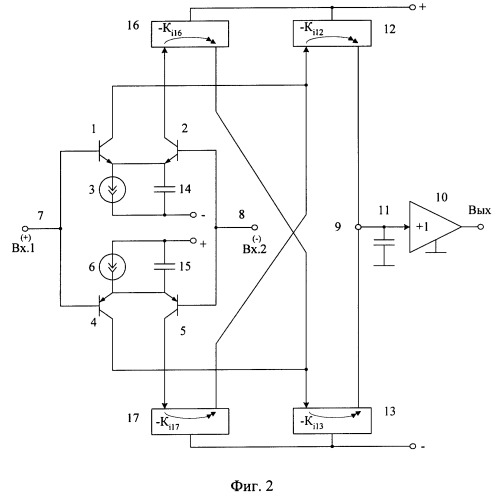

Схема заявляемого устройства в соответствии с п.1-п.2 формулы изобретения показана на фиг.2.

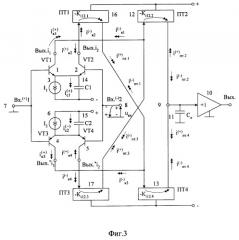

На фиг.3 и 4 показаны токи в элементах схемы фиг.2 при подаче на инвертирующий (фиг.3) и неинвертирующий (фиг.4) входы ОУ импульсного сигнала большой амплитуды.

На фиг.6 и 7 приведены результаты компьютерного моделирования заявляемого ОУ фиг.5, соответствующего фиг.2, в среде PSpice на транзисторах ФГУП «Пульсар», который исследовался авторами при подаче на входы ОУ импульсных (фиг.7) и синусоидальных (фиг.8) сигналов.

На фиг.3 и 7 приняты следующие обозначения:

Ку - коэффициент усиления по напряжению разомкнутого ОУ;

Ку.ос - коэффициент усиления по напряжению замкнутого ОУ;

«Фаза» - фазовый сдвиг по петле обратной связи замкнутого ОУ;

Vu=ϑвых - максимальная скорость нарастания выходного напряжения замкнутого ОУ;

Сс=Сд - емкость дополнительных корректирующих конденсаторов 14 и 15;

Ск - емкость основного корректирующего конденсатора;

Кimn≈1 - коэффициент передачи токовых зеркал.

Быстродействующий дифференциальный операционный усилитель фиг.2 содержит первый дифференциальный каскад на первом 1 и втором 2 входных n-р-n транзисторах, в общую эмиттерную цепь которых включен первый 3 источник опорного тока, второй дифференциальный каскад на первом 4 и втором 5 входных р-n-р транзисторах, в общую эмиттерную цепь которых включен второй 6 источник опорного тока, причем базы первых р-n-р и n-р-n входных транзисторов 1, 4 соединены с первым входом 7 быстродействующего дифференциального операционного усилителя, базы вторых р-n-р и n-р-n входных транзисторов 2, 5 соединены со вторым входом 8 быстродействующего дифференциального операционного усилителя, коллекторы первых n-р-n и р-n-р входных транзисторов 1, 4 соединены со входом 9 буферного усилителя 10 и основным корректирующим конденсатором 11 через первое 12 и второе 13 токовые зеркала. В схему введены первый 14 и второй 15 дополнительные корректирующие конденсаторы, первое 16 и второе 17 дополнительные токовые зеркала, причем первый дополнительный корректирующий конденсатор 14 подключен к эмиттерам первого 1 и второго 2 n-p-n входных транзисторов, второй дополнительный корректирующий конденсатор 15 подключен к эмиттерам первого 4 и второго 5 входных р-n-р транзисторов, коллектор второго 2 входного n-p-n транзистора соединен со входом второго токового зеркала 13 через первое дополнительное токовое зеркало 16, а коллектор второго 5 р-n-р входного транзистора соединен со входом первого 12 токового зеркала через второе 17 токовое зеркало.

Рассмотрим работу заявляемого устройства (фиг.3) при импульсном изменении положительного входного напряжения uвх.

Положительный «скачок» напряжения на входе 8 вызывает появление тока заряда корректирующего конденсатора 14, который затем передается на вход токового зеркала ПТ1 (16) и далее через токовое зеркало ПТ4 (13) - на вход 9 - и в основной корректирующий конденсатор 11.

Численные значения будут определяться сопротивлением эмиттерного перехода транзистора VT2 (2) и достигают больших значений. При этом в отличие от ОУ-прототипа в схеме фиг.3 сохраняется пропорциональность между входным напряжением uвх и током заряда (разряда) основного корректирующего конденсатора Ск (11). Это повышает быстродействие ОУ на один-два порядка (фиг.7).

При подаче входного импульсного сигнала на неинвертирующий вход (фиг.3) ОУ работает аналогично.

Важнейшим условием существенного повышения быстродействия заявляемого ОУ является правильный выбор соотношения емкостей дополнительных корректирующих конденсаторов 14, 15 (Сд) и основного корректирующего конденсатора (Ск). Авторы рекомендуют следующую пропорциональность Сд≥(0,3÷1,5)Ск.

При малых Сд новые элементы и связи между ними не дают положительного эффекта.

Компьютерное моделирование ОУ фиг.5, фиг.6, фиг.7 подтверждает эффективность заявляемого технического решения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2193273, H 03 F 3/45.

2. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - С.103. Рис.6.11.

3. Патент США №6.366.170 В1, H 03 F 3/45.

4. Патент США №5.153.529, H 03 F 3/45.

5. Патент США №6.420.931, H 03 F 3/45.

6. Патент США №5.729.177, H 03 F 3/45.

7. Патент США №4.649.352, H 03 F 3/45.

8. Патент США №4.555.673, H 03 F 3/45.

9. Патент США №6.657.495, H 03 F 3/45.

10. Патент США №5.294.893, H 03 F 3/45.

11. Патент США №5.455.535, H 03 F 3/45.

12. Патент США №6.628.168, H 03 F 3/45.

13. Патент США №6.642.789, H 03 F 3/45.

14. Патент США №5.523.718, H 03 F 3/45.

15. Патент США №4.837.523, H 03 F 3/45.

16. Патент США №4.600.893, H 03 F 3/45.

17. Патент США №4.532.479, H 03 F 3/45.

18. Патент США №4.595.883, H 03 F 3/45.

19. Патент США №5.225.791, H 03 F 3/45.

20. Патент США №3.974.455, H 03 F 3/45.

21. Патент США №4.783.637, H 03 F 3/45.

22. Патент США №5.291.149, H 03 F 3/45.

23. Авт. Свид. СССР №611288, H 03 F 3/45.

24. Патент Франции №2.224.932, H 03 F 3/45.

25. Патент США №3.968.451, H 03 F 3/45.

26. Патент Японии №53-25232, кл. 98 (5) А 332.

27. Патент США №5.512.859, H 03 F 3/45.

28. Патент США №6.268.769, H 03 F 3/45 (фиг.3).

29. Патент США №5.515.005, H 03 F 3/45.

30. Патент US 2005/0024140 А1.

31. Патент США №4.636.743, H 03 F 3/45.

32. Патент Японии JP 7050528.

Быстродействующий дифференциальный операционный усилитель, содержащий первый дифференциальный каскад на первом (1) и втором (2) входных n-р-n транзисторах, в общую эмиттерную цепь которых включен первый (3) источник опорного тока, второй дифференциальный каскад на первом (4) и втором (5) входных р-n-р транзисторах, в общую эмиттерную цепь которых включен второй (6) источник опорного тока, причем базы первых р-n-р и n-р-n входных транзисторов (1), (4) соединены с первым входом (7) быстродействующего дифференциального операционного усилителя, базы вторых р-n-р и n-р-n входных транзисторов (2), (5) соединены со вторым входом (8) быстродействующего дифференциального операционного усилителя, коллекторы первых n-р-n и р-n-р входных транзисторов (1), (4) соединены со входом (9) буферного усилителя (10) и основным корректирующим конденсатором (11) через первое (12) и второе (13) токовые зеркала, отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные корректирующие конденсаторы, первое (16) и второе (17) дополнительные токовые зеркала, причем первый дополнительный корректирующий конденсатор (14) подключен к эмиттерам первого (1) и второго (2) n-р-n входных транзисторов, второй дополнительный корректирующий конденсатор (15) подключен к эмиттерам первого (4) и второго (5) входных р-n-р транзисторов, коллектор второго (2) входного n-p-n транзистора соединен со входом второго токового зеркала (13) через первое дополнительное токовое зеркало (16), а коллектор второго (5) р-n-р входного транзистора соединен со входом первого (12) токового зеркала через второе (17) токовое зеркало, причем емкость первого (14) и второго (15) дополнительных корректирующих конденсаторов выбирается в пределах Сд=(0,3÷1,5)Ск, где Ск - емкость основного корректирующего конденсатора (11).