Устройство обслуживания разноприоритетных запросов абонентов вычислительной системы

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может быть использовано в системах обмена данными и локальных вычислительных сетях. Техническим результатом является повышение вероятности своевременного обслуживания пользователей в условиях реального процесса функционирования систем обмена данными, при непрерывной динамике смены состояний разноприоритетных запросов абонентов. Указанный результат достигается за счет того, что устройство содержит N≥2 абонентских блоков, генератор тактовых импульсов, N абонентских контроллеров времени, элемент ИЛИ, элемент И-НЕ, селектор-мультиплексор, два N-входовых элемента И-НЕ, два шифратора приоритетов, главный контроллер времени ожидания. 3 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в системах обмена данными и локальных вычислительных сетях (ЛВС).

Известно многоканальное устройство с динамическим изменением приоритета по а.с. СССР №1562912, G 06 F 9/46, 1990, бюл. №17, содержащее N≥2 абонентских блоков, счетчик, элемент И, генератор тактовых импульсов, делитель, блок анализа приоритетов и блок наращивания приоритета.

Недостатком данного устройства является относительно большое время обслуживания запросов абонентов вычислительной системы с низким приоритетом.

Известно устройство обслуживания запросов пользователей вычислительной системы, содержащее N≥2 абонентских блоков, счетчик, элемент И, генератор тактовых импульсов, делитель, N-входовый элемент ИЛИ-НЕ, мультиплексор и инвертор (см. а.с. СССР №2140666, G 06 F 9/46, 1999, бюл. №30).

Однако данное устройство имеет относительно невысокую надежность и большое время обслуживания сложных запросов, обусловленные большим количеством взаимоувязанных элементов, входящих в его состав.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство обслуживания разноприоритетных запросов абонентов вычислительной системы (см. патент РФ №2186420, G 06 F 9/46, 2002, бюл. №21), содержащее N≥2 абонентских блоков, генератор тактовых импульсов, первый и второй N-входовые элементы И-НЕ, первый и второй шифраторы приоритетов, элемент ИЛИ, элемент И-НЕ и селектор-мультиплексор. При этом выход генератора тактовых импульсов подключен к тактовым входам каждого из N абонентских блоков. Запросные входы и K-разрядные входы «Код максимального времени ожидания» каждого из N абонентских блоков, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими запросными входами и K-разрядными входами «Код максимального времени ожидания» устройства. Входы «Обнуление» каждого из N абонентских блоков являются соответствующими входами «Обнуление» устройства. Каждый из N входов первого и второго N-входовых элементов И-НЕ подключены к соответствующим N инверсным входам соответственно первого и второго шифраторов приоритетов. Инверсные выходы первого и второго N-входовых элементов И-НЕ подключены соответственно к второму и первому входам элемента ИЛИ. Каждый n, n=1, 2,..., N, инверсный вход первого и второго шифраторов приоритетов подключен соответственно к первому и второму сигнальному выходу ((N+1)-n)-го абонентского блока. Выход элемента ИЛИ подключен к второму входу элемента И-НЕ, первый вход которого является опросным входом устройства, а выход элемента И-НЕ подключен к инверсному разрешающему входу селектора-мультиплексора и является разрешающим выходом устройства. Управляющий вход селектора-мультиплексора подключен к второму входу элемента ИЛИ. Каждый из J, где J=]log2N[, инверсных выходов первого и второго шифраторов приоритетов подключены к соответствующим J первичным входам и соответствующим J вторичным входам селектора-мультиплексора, а J-разрядный выход селектора-мультиплексора является J-разрядным выходом «Код подлежащего обслуживанию абонента» устройства.

В прототипе реализуется возможность уменьшения времени обслуживания сложных запросов и повышения надежности за счет сокращения количества элементов, входящих в состав устройства обслуживания разноприоритетных запросов абонентов вычислительной системы.

Однако прототип имеет недостаток - относительно низкую вероятность своевременного обслуживания абонентов в условиях непрерывной динамики смены состояний разноприоритетных запросов и с учетом влияющих факторов. Это связано с тем, что устройство-прототип не позволяет динамически корректировать максимальное время ожидания обслуживания запросов, различных как по приоритету, так и по динамично изменяющимся требованиям к своевременности предоставления услуг в рамках запросов различного приоритета. Данное устройство-прототип позволяет обслуживать разноприоритетные запросы абонентов вычислительной системы с раз и навсегда заданными значениями (границами) максимального времени ожидания обслуживания для каждого запроса, в то время как большое количество запросов, поступающих от абонентов реальной - многофункциональной, сложной и управляемой вычислительной системы, могут в динамике функционирования изменять свое состояние (могут динамично изменяться требования к качеству и своевременности предоставления конкретных услуг в рамках запросов различного приоритета, например, текущие требования к значениям максимального времени ожидания обслуживания для конкретного запроса) под влиянием управляющих воздействий на вычислительную систему исходя из текущих требований абонентов или под влиянием внешних факторов. Это исключает применение прототипа для своевременного и динамического обслуживания абонентов в реальных условиях, когда в динамике функционирования управляемой вычислительной системы объективно изменяются во времени не только свойства самой системы и окружающей среды, но и требования к качеству и своевременности обслуживания [1-5].

Под «обслуживанием» понимается совокупность действий вычислительной системы, включающая выборку запроса из очереди, выделение ему ресурса, а также проведение завершающих операций. Запрос - посылка сигнала, инициирующего ответ. Входное сообщение, содержащее требование к системе на выделение ресурса.

Под «приоритетом» понимается число, предписанное задаче, процессу или операции, определяющее очередность их выполнения или обслуживания. Чем меньше число, тем выше уровень приоритета.

Под «состоянием разноприоритетных запросов» понимается набор значений параметров, характеризующих эти запросы (их приоритет и максимальное время ожидания обслуживания для каждого запроса) в конкретный момент времени.

Под «максимальным временем ожидания» обслуживания запроса понимается максимальное время нахождения запроса в очереди на обслуживание второго или первого порядка. Код максимального времени ожидания обслуживания запроса Тож n от конкретного абонента (где n=1, 2,..., N - соответствующий номер приоритета n-го абонента, а N - общее число абонентов), запоминается, затем формируется сигнал запроса и из таких сигналов запросов формируется очередь второго порядка в соответствии с номерами приоритетов абонентов. Запросы из очереди второго порядка, достигшие максимального времени ожидания, переносят в очередь первого порядка на позиции, соответствующие номерам их приоритетов.

Целью заявленного технического решения является создание устройства обслуживания разноприоритетных запросов абонентов вьяислительной системы, обеспечивающего повышение вероятности своевременного обслуживания пользователей в условиях, присущих реальному процессу функционирования вычислительной системы - в условиях непрерывной динамики смены состояний разноприоритетных запросов и с учетом влияющих факторов, устройства, способного своевременно предоставлять пользователям ресурс вычислительной системы, с учетом, как динамики управляющих воздействий или внешних факторов, так и изменяющихся во времени текущих требований абонентов, на основе динамически корректируемых значений (границ) максимального времени ожидания обслуживания для каждого запроса.

Указанная цель достигается тем, что в известное устройство обслуживания разноприоритетных запросов абонентов вычислительной системы, содержащее N≥2 абонентских блоков, генератор тактовых импульсов, первый и второй N-входовые элементы И-НЕ, первый и второй шифраторы приоритетов, элемент ИЛИ, элемент И-НЕ и селектор-мультиплексор, J-разрядный, где J=]log2N[, выход которого является J-разрядным выходом «Код подлежащего обслуживанию абонента» устройства, выход генератора тактовых импульсов подключен к тактовым входам каждого из N абонентских блоков, запросные входы и K-разрядные входы «Код максимального времени ожидания» каждого из N абонентских блоков, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими N запросными входами и N K-разрядными входами «Код максимального времени ожидания» устройства, входы «Обнуление» каждого из N абонентских блоков являются соответствующими входами «Обнуление» устройства, каждый из N входов первого и второго N-входовых элементов И-НЕ подключены к соответствующим N инверсным входам соответственно первого и второго шифраторов приоритетов, инверсные выходы первого и второго N-входовых элементов И-НЕ подключены соответственно к второму и первому входам элемента ИЛИ, выход которого подключен к второму входу элемента И-НЕ, первый вход которого является опросным входом устройства, выход элемента И-НЕ подключен к инверсному разрешающему входу селектора-мультиплексора и является разрешающим выходом устройства, управляющий вход селектора-мультиплексора подключен к второму входу элемента ИЛИ, каждый из J инверсных выходов первого и второго шифраторов приоритетов подключены к соответствующим J первичным входам и соответствующим J вторичным входам селектора-мультиплексора, дополнительно включены N≥1 идентичных абонентских контроллеров времени, предназначенных для дешифровки, дополнительного сравнения и контроля K-разрядного кода, обуславливающего новое значение максимального времени ожидания обслуживания для каждого запроса конкретного абонента, и главный контроллер времени ожидания, предназначенный для динамической коррекции значений максимального времени ожидания обслуживания для каждого запроса любого из N абонентов вычислительной системы. При этом n-й, где n=1, 2,..., N, инверсный вход первого шифратора приоритетов подключен к первому сигнальному выходу ((N+1)-n)-го абонентского контроллера времени, n-й инверсный вход второго шифратора приоритетов подключен к второму сигнальному выходу ((N+1)-n)-го абонентского контроллера времени. Первый и второй сигнальные выходы n-го абонентского блока подключены соответственно к первому и второму сигнальным входам n-го абонентского блока подключены соответственно к первому и второму сигнальным входам n-го абонентского контроллера времени. Причем K-разрядный корректирующий вход n-го абонентского блока соединен с K-разрядным проверочным входом n-го абонентского контроллера времени и подключен к n-му, где n=1, 2,..., N, K-разрядному выходу главного контроллера времени ожидания, N K-разрядных входов которого являются соответствующими N K-разрядными входами «Коррекция максимального времени ожидания» устройства.

Абонентский контроллер времени (АКВ) состоит из дешифратора корректированного кода максимального времени ожидания и регистра сравнения-коррекции максимального времени ожидания. При этом K-разрядный вход дешифратора корректированного кода максимального времени ожидания является K-разрядным проверочным входом абонентского контроллера времени. Первичный и вторичный проверочные выходы дешифратора корректированного кода максимального времени ожидания подключены соответственно к первичному и вторичному проверочным входам регистра сравнения-коррекции максимального времени ожидания, первый и второй сигнальные входы которого являются соответственно первым и вторым сигнальными входами абонентского контроллера времени. Первый и второй сигнальные выходы регистра сравнения-коррекции максимального времени ожидания являются соответственно первым и вторым сигнальными выходами абонентского контроллера времени.

Главный контроллер времени ожидания состоит из регистрирующего элемента времени ожидания и элемента хранения нового значения времени ожидания. При этом N К-разрядных входов регистрирующего элемента времени ожидания являются соответствующими N K-разрядными входами главного контроллера времени ожидания. Причем N К-разрядных выходов регистрирующего элемента времени ожидания подключены к соответствующим N K-разрядным входам элемента хранения нового значения времени ожидания, N К-разрядных выходов которого являются соответствующими N К-разрядными выходами главного контроллера времени ожидания.

Абонентский блок состоит из счетчика, инвертора, трехвходового элемента И и корректирующего регистра. При этом инверсный вход разрешения счета счетчика является запросным входом абонентского блока и подключен к второму входу трехвходового элемента И и к входу инвертора. Причем К-разрядный первичный вход корректирующего регистра является K-разрядным входом «Код максимального времени ожидания» абонентского блока, К-разрядный вторичный вход корректирующего регистра является K-разрядным корректирующим входом абонентского блока, а К выходов корректирующего регистра подключены к соответствующим К информационным входам счетчика. Вход сброса счетчика является входом «Обнуление» абонентского блока. Инверсный выход счетчика подключен к первому входу трехвходового элемента И и является первым сигнальным выходом абонентского блока. Третий вход трехвходового элемента И является тактовым входом абонентского блока, а выход трехвходового элемента И подключен к счетному входу счетчика. Выход инвертора является вторым сигнальным выходом абонентского блока.

Благодаря новой совокупности существенных признаков, за счет введения N≥2 идентичных абонентских контроллеров времени и главного контроллера времени ожидания, обеспечивающих, соответственно, дешифровку и динамическую коррекцию значений (границ) максимального времени ожидания обслуживания для каждого запроса, в заявленном устройстве достигается возможность предоставления пользователям ресурса вычислительной системы, с учетом, как динамики управляющих воздействий или внешних факторов, так и изменяющихся во времени текущих требований абонентов, обуславливающая повышение вероятности своевременного обслуживания пользователей в условиях, присущих реальному процессу функционирования вычислительной системы - в условиях непрерывной динамики смены состояний разноприоритетных запросов и с учетом влияющих факторов.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявленное устройство поясняется чертежами, на которых представлены:

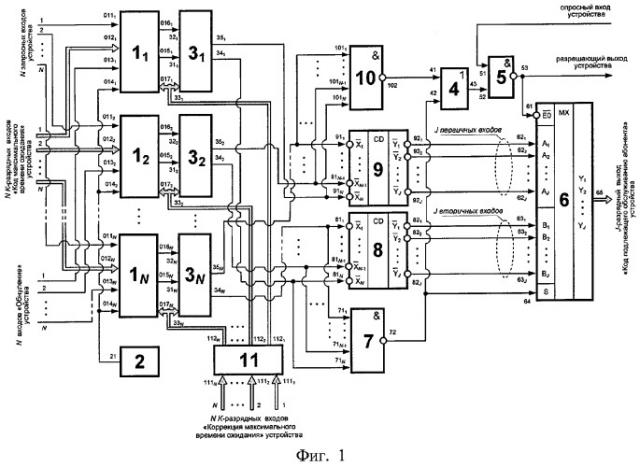

на фиг.1 - структурная схема устройства обслуживания разноприоритетных запросов абонентов вычислительной системы,

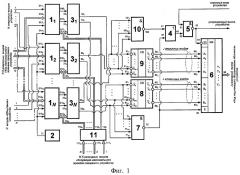

на фиг.2 - структурная схема n-го () абонентского контроллера времени;

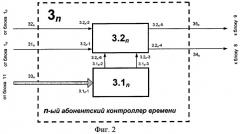

на фиг.3 - структурная схема главного контроллера времени ожидания;

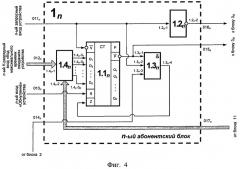

на фиг.4 - структурная схема n-го () абонентского блока;

на фиг.5 - структура вычислительной системы;

на фиг.6 - размещение сигналов запросов в очереди второго порядка;

на фиг.7 - порядок переноса запросов из очереди второго порядка в очередь первого порядка.

Устройство обслуживания разноприоритетных запросов абонентов вычислительной системы, изображенное на фиг.1, состоит из N≥2 идентичных абонентских блоков 11-1N (АБ), генератора тактовых импульсов 2, N≥2 идентичных абонентских контроллеров времени 31-3N, элемента ИЛИ 4, элемента И-НЕ 5, селектора-мультиплексора 6, первого 7 и второго 10 N-входовых элементов И-НЕ, первого 8 и второго 9 шифраторов приоритетов, главного контроллера времени ожидания 11. При этом J-разрядный, где J=]log2N[, выход 65 селектора-мультиплексора 6 является J-разрядным выходом «Код подлежащего обслуживанию абонента» устройства, выход 21 генератора тактовых импульсов 2 подключен к тактовым входам 0141-014N каждого из N абонентских блоков 11-1N, запросные входы 0111-011N и K-разрядные входы «Код максимального времени ожидания» 0121-012N каждого из N абонентских блоков 11-1N, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими N запросными входами и N К-разрядными входами «Код максимального времени ожидания» устройства. Входы «Обнуление» 0131-013N каждого из N абонентских блоков 11-1N являются соответствующими N входами «Обнуление» устройства. Каждый из N входов первого 7 и второго 10 N-входовых элементов И-НЕ (соответственно 711-71N и 1011-101N) подключены к соответствующим N инверсным входам (811-81N и 911-91N) соответственно первого 8 и второго 9 шифраторов приоритетов. Инверсные выходы первого 7 и второго 10 N-входовых элементов И-НЕ (соответственно 72 и 102) подключены соответственно к второму 42 и первому 41 входам элемента ИЛИ 4, выход 43 которого подключен к второму входу 52 элемента И-НЕ 5, первый вход 51 которого является опросным входом устройства. Выход 53 элемента И-НЕ 5 подключен к инверсному разрешающему входу 61 селектора-мультиплексора 6 и является разрешающим выходом устройства. Управляющий вход 64 селектора-мультиплексора 6 подключен к второму входу 42 элемента ИЛИ 4. Каждый из J инверсных выходов (соответственно 821-82J и 921-92J) первого 8 и второго 9 шифраторов приоритетов подключены к соответствующим J первичным входам 621-62J и соответствующим J вторичным входам 631-63J селектора-мультиплексора 6. При этом n-й, где n=1, 2,..., N, инверсный вход 81n первого шифратора приоритетов 8 подключен к первому сигнальному выходу 34(N+1)-n ((N+1)-n)- го абонентского контроллера времени 3(N+1)-n, n-й инверсный вход 91n второго шифратора приоритетов 9 подключен к второму сигнальному выходу 35(N+1)-n ((N+1)-n)-го абонентского контроллера времени 3(N+1)-n. Первый 015n и второй 016n сигнальные выходы n-го абонентского блока 1n подключены соответственно к первому 31n и второму 32n сигнальным входам n-го абонентского контроллера времени 3n. Причем K-разрядный корректирующий вход 017n n-го абонентского блока 1n соединен с K-разрядным проверочным входом 33n n-го абонентского контроллера времени 3n и подключен к n-му, где n=1, 2,..., N, К-разрядному выходу 112n главного контроллера времени ожидания 11, N K-разрядных входов 1111-111N которого являются соответствующими N K-разрядными входами «Коррекция максимального времени ожидания» устройства.

Число «N, (N≥2)» (абонентских блоков, входов, выходов и т.п.) определяется в соответствии с возможным количеством абонентов вычислительной системы и, как правило, составляет от 2 (двух) до 50 (пятидесяти). Число «К, (К≥2)» характеризует разрядность кода максимального времени ожидания обслуживания запросов абонентов и, как правило, составляет от 2 (двух) до 10 (десяти).

Абонентские контроллеры времени 31-3N идентичны и предназначены для дешифровки, дополнительного сравнения и контроля нового, вводимого в динамике управления процессом обслуживания разноприоритетных запросов абонентов вычислительной системы, K-разрядного кода, обуславливающего новое значение (границы) максимального времени ожидания обслуживания для каждого запроса конкретного абонента.

Абонентский контроллер времени (например, n-й АКВ) 3n, где n=1, 2,..., N, (фиг.2), состоит из дешифратора корректированного кода максимального времени ожидания 3.1n и регистра сравнения-коррекции максимального времени ожидания 3.2n. При этом К-разрядный вход 3.1n-1 дешифратора корректированного кода максимального времени ожидания 3.1n является K-разрядным проверочным входом 33n абонентского контроллера времени 3n. Первичный 3.1n-2 и вторичный 3.1n-3 проверочные выходы дешифратора корректированного кода максимального времени ожидания 3.1n подключены соответственно к первичному 3.2n-6 и вторичному 3.2n-3 проверочным входам регистра сравнения-коррекции максимального времени ожидания 3.2n, первый 3.2n-1 и второй 3.2n-2 сигнальные входы которого являются соответственно первым 31n и вторым 32n сигнальными входами абонентского контроллера времени 3n. Первый 3.2n-4 и второй 3.2n-5 сигнальные выходы регистра сравнения-коррекции максимального времени ожидания 3.2n являются соответственно первым 34n и вторым 35n сигнальными выходами абонентского контроллера времени 3n.

Дешифратор корректированного кода максимального времени ожидания 3.1n абонентского контроллера времени 3n предназначен для преобразования K-разрядного кода, обуславливающего новое, вводимое в процессе управления, значение (границы) максимального времени ожидания обслуживания для каждого запроса конкретного n-го абонента в двоичный код. Дешифратор корректированного кода максимального времени ожидания 3.1n может быть технически реализован в виде серийно выпускаемого дешифратора, описанного в книге [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С.432-436, рис.4.46].

Регистр сравнения-коррекции максимального времени ожидания 3.2n абонентского контроллера времени 3n предназначен для дополнительной проверки (сравнения) принадлежности запроса с изначальным и вновь вводимым максимальным времени ожидания обслуживания к очереди первого или второго порядка для каждого запроса конкретного n-го абонента и коррекции (формирования по итогам сравнения) на первом 34n и втором 35n сигнальных выходах АКВ 3n сигналов низкого либо высокого уровня, характеризующих принадлежность этого запроса соответственно к очереди первого либо второго порядка с учетом нового времени ожидания. Регистр сравнения-коррекции максимального времени ожидания 3.2n может быть реализован технически на базе серийно выпускаемого узла сравнения (цифрового компаратора), как показано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.149-152, рис.5.19].

Главный контроллер времени ожидания 11 предназначен для динамической коррекции значений (границ) максимального времени ожидания обслуживания для каждого запроса любого из N абонентов вычислительной системы.

Главный контроллер времени ожидания 11 (фиг.3) состоит из регистрирующего элемента времени ожидания 11.1 и элемента хранения нового значения времени ожидания 11.2. При этом N K-разрядных входов 11.1-11-11.1-1N регистрирующего элемента времени ожидания 11.1 являются соответствующими N K-разрядными входами 1111-111N главного контроллера времени ожидания 11. Причем N K-разрядных выходов 11.1-21-11.1-2N регистрирующего элемента времени ожидания 11.1 подключены к соответствующим N K-разрядным входам 11.2-11-11.2-1N элемента хранения нового значения времени ожидания 11.2, N К-разрядных выходов 11.2-21-11.2-2N которого являются соответствующими N K-разрядными выходами 1121-112N главного контроллера времени ожидания 11.

Регистрирующий элемент времени ожидания 11.1 главного контроллера времени ожидания 11 предназначен для контроля и регистрации в К-разрядном коде нового, вводимого в динамике управления процессом обслуживания разноприоритетных запросов абонентов вычислительной системы, значения максимального времени ожидания обслуживания для каждого запроса конкретного абонента. Регистрирующий элемент времени ожидания 11.1 может быть технически реализован в виде серийно выпускаемого многоразрядного сдвигающего регистра для сдвига влево, как показано в литературе [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.158-160, рис.5.28(б)].

Элемент хранения нового значения времени ожидания 11.2 главного контроллера времени ожидания 11 предназначен для записи и хранения в K-разрядном коде нового, вводимого в динамике управления процессом обслуживания, значения максимального времени ожидания. Элемент хранения нового значения времени ожидания 11.2 может быть технически реализован в виде обычного запоминающего устройства на базе типового многоразрядного регистра сдвига с последовательным вводом и выводом информации, описанного в [Быстров Ю.А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга/Под ред. Быстрова Ю.А. - СПб.: Энергоатомиздат, 1996. С.291-292, рис.6.7].

Абонентские блоки (АБ) 11-1N идентичны и предназначены для контроля поступления сигналов запросов, контроля оставшегося времени ожидания, а также выработки управляющих сигналов по истечении установленного изначального или вновь вводимого в динамике управления времени ожидания для каждого запроса.

Абонентский блок (например, n-й АБ) 1n, где n=1, 2,..., N, (фиг.4), состоит из счетчика 1.1n, инвертора 1.2n, трехвходового элемента И 1,3n и корректирующего регистра 1.4n. При этом инверсный вход разрешения счета счетчика 1.1n является запросным входом 011n абонентского блока 1n и подключен к второму входу 1.3n-2 трехвходового элемента И 1.3n и к входу 1.2n-1 инвертора 1.2n. Причем K-разрядный первичный вход 1.4n-1 корректирующего регистра 1.4n является K-разрядным входом 012n «Код максимального времени ожидания» абонентского блока 1n, K-разрядный вторичный вход 1.4n-2 корректирующего регистра 1.4n является K-разрядным корректирующим входом 017n абонентского блока 1n, а К выходов 1.4n-31-1.4n-3K-корректирующего регистра 1.4n подключены к соответствующим К информационньм входам D1-DK счетчика 1.1n. Вход сброса R счетчика 1.1n и является входом 013n «Обнуление» абонентского блока 1n. Инверсный выход счетчика 1.1n подключен к первому входу 1.3n-1 трехвходового элемента И 1.3n и является первым сигнальным выходом 015n абонентского блока 1n. Третий вход 1.3n-3 трехвходового элемента И 1.3n является тактовым входом 014n абонентского блока 1n, а выход 1.3n-4 трехвходового элемента И 1.3n подключен к счетному входу Z счетчика 1.1n. Выход 1.2n-2 инвертора 1.2n является вторым сигнальным выходом 016n абонентского блока 1n.

Счетчик 1.1n абонентского блока 1n предназначен для счета поступающих на его вход импульсов (счетных импульсов), выработки управляющего сигнала, определяемого кодом начального заполнения по входам D1-DK и периодом следования тактовых импульсов, то есть является настраиваемым таймером. Описание работы и схема такого счетчика известны и приведены, например, в работе [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: Справочник. - М.: Радио и связь, 1994, С.64-65].

Инвертор 1.2n абонентского блока 1n предназначен для преобразования сигналов высокого уровня, поступающих на запросный вход 011n абонентского блока 1n, в сигналы низкого уровня, совокупность которых на вторых сигнальных выходах 0161-016N абонентских блоков 11-1N образует очередь второго порядка. Инвертор 1.2n может быть технически реализован в виде элемента НЕ в соответствии с описанием, приведенньм в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.14, рис.1.3].

Трехвходовый элемент И 1.3n абонентского блока 1n предназначен для регистрации запросов на обслуживание, а также коммутации тактового входа 014n абонентского блока 1n и инверсного выхода счетчика 1.1n в интересах контроля времени ожидания для каждого запроса, либо установленного изначального, либо вновь вводимого в динамике управления обслуживанием. Трехвходовый элемент И 1.3n может быть технически реализован на основе серийно выпускаемого элемента И, описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.13-14, рис.1.2].

Корректирующий регистр 1.4n абонентского блока 1n предназначен для регистрации и предварительного сравнения изначального и вновь вводимого в динамике управления К-разрядного кода, а также коррекции (формирования по итогам сравнения) на своих К выходах 1.4n-31-1.4n-3K информационных сигналов, характеризующих предварительное решение о значении максимального времени ожидания обслуживания для каждого запроса конкретного n-го абонента. Корректирующий регистр 1.4n может быть технически реализован на основе серийно выпускаемого узла сравнения многоразрядных чисел, как описано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.149-152, рис.5.21].

Генератор тактовых импульсов 2, входящий в общую структурную схему, предназначен для выработки синхронизирующей последовательности импульсов. Техническая реализация генератора тактовых импульсов 2 возможна на базе серийно выпускаемого генератора тактовых импульсов, описанного в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С.50-53].

Элемент ИЛИ 4, входящий в общую структурную схему, предназначен для объединения выходных сигналов определенного логического уровня, поступающих с выходов первого 7 и второго 10 N-входовых элементов И-НЕ. Элемент ИЛИ 4 может быть технически реализован на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.24-26, рис.1.7].

Элемент И-НЕ 5, входящий в общую структурную схему, предназначен для выработки сигналов низкого либо высокого логического уровня и соответственно разрешения либо запрещения трансляции данных селектору-мультиплексору 6. Элемент И-НЕ 5 может быть технически реализован на основе серийно выпускаемого элемента И-НЕ, как показано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.26-28, рис.1.9(a)].

Селектор-мультиплексор 6, входящий в общую структурную схему, предназначен для коммутации либо J первичных 621-62J либо J вторичных 631-63J входов селектора-мультиплексора 6 на его J-разрядный выход 65. Частный случай технической реализации селектора-мультиплексора 6 описан в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: Справочник. - М.: Радио и связь, 1994. С.34-35].

Первый 7 и второй 10 N-входовые элементы И-НЕ, входящие в общую структурную схему, аналогичны по структуре и принципу действия, предназначены для установления высокого уровня выходного сигнала при наличии в очереди (соответственно первого и второго порядка) хотя бы одного сигнала запроса. Первый 7 и второй 10 N-входовые элементы И-НЕ могут быть технически реализованы на основе серийно выпускаемого многовходового элемента И-НЕ, как показано в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.26-28, рис.1.9(б)].

Первый 8 и второй 9 шифраторы приоритетов, входящие в общую структурную схему, аналогичны по структуре и принципу действия, предназначены для преобразования сигнала низкого уровня на одном из их входов в двоичный код на выходе, причем преобразование осуществляется с учетом приоритетов сигналов, соответствующих номерам входов. Первый 8 и второй 9 шифраторы приоритетов могут быть технически реализованы на базе серийно выпускаемых шифраторов, как показано в [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С.147-148].

Устройство обслуживания разноприоритетных запросов абонентов вычислительной системы работает следующим образом.

Известно [1-5], что с точки зрения повышения вероятности своевременного обслуживания пользователей в условиях, присущих реальному процессу функционирования вычислительной системы - в условиях непрерывной динамики смены состояний разноприоритетных запросов и с учетом влияющих факторов, существует возможность варьировать временем обслуживания абонентов. Эта возможность реализуется на основе принципа динамической коррекции значений (границ) максимального времени ожидания обслуживания для каждого запроса.

Очевидно, что при обработке разноприоритетных запросов объективно изменяются во времени не только управляющие воздействия на систему или внешние факторы, но и текущие требования абонентов к качеству и своевременности предоставления услуг вычислительной системы. В данных условиях затруднено своевременное обслуживание пользователей, которое напрямую зависит от динамики изменения во времени параметров, режимов и методов обслуживания, от динамики внутренних и внешних воздействий на вычислительную систему, а также от динамики изменения требований, целей и задач обслуживания, обусловленных конкретной ситуацией.

Анализ работ [1-5], посвященных алгоритмам и принципам обслуживания разноприоритетных запросов абонентов в рамках локальных вычислительных сетей и иных сложных технических систем, позволяет сделать вывод о возможности реализации процедур повышения вероятности своевременного обслуживания пользователей на основе технической реализации принципа динамической коррекции значений (границ) максимального времени ожидания обслуживания для каждого запроса в условиях непрерывной динамики смены состояний разноприоритетных запросов и с учетом влияющих факторов.

Построение устройства обслуживания разноприоритетных запросов абонентов вычислительной системы на основе предложенного принципа работы позволяет получить преимущество перед прототипом, обеспечивая повышение вероятности своевременного предоставления пользователям ресурса в рамках реальной вычислительной системы, когда запросы абонентов в динамике функционирования данной системы могут изменять пороговые значения своих состояний под влиянием управляющих воздействий (текущих требований) абонентов или внешних факторов.

Техническая реализация принципа динамической коррекции значений (границ) максимального времени ожидания обслуживания в заявленном устройстве осуществлена путем введения внешнего динамического управления временем ожидания (в заявленном устройстве - K-разрядные входы «Коррекция максимального времени ожидания» устройства) и введения регистрации, контроля и динамической коррекции максимального времени ожидания обслуживания для каждого запроса (в заявленном устройстве реализованы соответственно в рамках абонентских блоков 11-1N, абонентских контроллеров времени 31-3N и главного контроллера времени ожидания 11).

С учетом этого, в заявленном устройстве осуществляется управляемое формирование очереди на обслуживание разноприоритетных запросов и реализация изменяющихся во времени потребностей абонентов в вычислительном ресурсе, обуславливающие повышение вероятности своевременного обслуживания пользователей. Перед началом работы устройства с его K-разрядных входов «Код максимального времени ожидания» через K-разрядные входы 0121-012N абонентских блоков 11-1N на K-разрядные первичные входы 1.41-1-1.4N-1 корректирующих регистров 1.41-1.4N поступают значения кода, задающие начальное максимальное время ожидания обслуживания запросов для каждого n-го () абонента.

Если в ходе обслуживания абонентов отсутствует внешнее динамическое управление временем ожидания для всех запросов всех N абонентов, на K-разрядных корректирующих входах 0171-017N абонентских блоков 11-1N, а значит и на K-разрядных вторичных входах 1.41-2-1.4N-2 корректирующих регистров 1.41-1.4N, кодовые сигнал