Устройство поиска информации

Иллюстрации

Показать всеИзобретение относится к области электросвязи и может быть использовано для поиска и оперативной идентификации информации в мультисервисных цифровых сетях передачи данных с коммутацией пакетов. Техническим результатом является расширение области применения устройства и повышение быстродействия. Устройство содержит N формирователей временных интервалов, N блоков селекции, делитель частоты, N регистров временного хранения, N двухвходовых элементов И, разрешающий трехвходовый элемент И, N-входовый элемент ИЛИ-НЕ, электронный ключ, регистр хранения маски, N-входовый элемент И-НЕ, блок управления. 4 з.п. ф-лы, 6 ил.

Реферат

Заявленное техническое решение относится к области электросвязи и может быть применено для поиска и оперативной идентификации информации в мультисервисных цифровых сетях передачи данных с коммутацией пакетов.

Известны устройства поиска информации - см., например, Авт.св. СССР №1621049 "Устройство поиска информации", МПК G 06 F 15/40, заявленное 09.01.89, Авт.св. СССР №1711185 "Устройство поиска информации", МПК G 06 F 15/40, заявленное 05.04.89.

Известные аналоги содержат регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации. В ходе приема цифрового сообщения и поиска в нем определенной цифровой последовательности необходимо определить его параметры и соответствие последовательности передачи правилам обмена данными, установленным для данного протокола. Известные аналоги не в полном объеме выполняют эти требования.

В первом аналоге определение коммуникационных пакетов реализовано с вероятностью правильного распознавания менее 0.1, поскольку распознавание производится статистическим способом и не учитывает признаков последовательной передачи информации.

Во втором аналоге существенным недостатком является невозможность получения однозначного решения в связи с низким уровнем достоверности и вероятности идентификации коммуникационного протокола (менее 0.3), так как поиск информационных блоков реализован дихотомическим методом без учета наличия допустимой последовательности пакетов.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство Патент РФ №2115952 "Устройство поиска информации", МПК G 06 F 17/40, опубликованное 20.07.98.

Устройство-прототип включает блок памяти, регистр стратегии поиска и вычитающий счетчик, делитель частоты, коммутатор, первый, второй, третий и четвертый блоки селекции, формирователь временных интервалов и блок индикации.

При этом в устройстве-прототипе выход делителя частоты соединен с первыми входами блока памяти, вычитающего счетчика, первого, второго, третьего и четвертого блоков селекции, регистра стратегии поиска. Выходы блока памяти соединены соответственно с четвертым-одиннадцатым входами коммутатора, а первый выход вычитающего счетчика соединен с десятым входом блока памяти, двенадцатым входом коммутатора, одиннадцатым входом первого блока селекции, десятыми входами второго, третьего и четвертого блоков селекции, третьим входом регистра стратегии поиска и является командным выходом устройства. Второй выход вычитающего счетчика соединен с одиннадцатыми входами второго, третьего и четвертого блоков селекции, а третий выход вычитающего счетчика соединен с двенадцатым входом первого блока селекции. Выходы коммутатора соединены с вторым-девятым входами первого, второго, третьего и четвертого блоков селекции соответственно, а первый и второй выходы первого блока селекции соединены соответственно с первым и вторым входами коммутатора. При этом третий выход первого блока селекции соединен с четвертым входом регистра стратегии поиска и четырнадцатым входом вычитающего счетчика, а четвертый выход первого блока селекции соединен с пятым входом регистра стратегии поиска, четырнадцатым входом вычитающего счетчика и входом формирователя временных интервалов. Пятый выход первого блока селекции соединен с третьим входом коммутатора. Шестой выход первого блока селекции и первые выходы второго, третьего и четвертого блоков селекции, выход регистра стратегии поиска соединены с первым входом блока индикации, десятым входом первого блока селекции и четырнадцатым входом вычитающего счетчика. Второй выход второго блока селекции соединен с вторым входом регистра стратегии поиска, а второй выход третьего блока селекции соединен с третьим входом регистра стратегии поиска. При этом второй выход четвертого блока селекции и выход формирователя временных интервалов соединены с вторым входом блока индикации и четырнадцатым входом вычитающего счетчика. Вход делителя частоты, второй-девятый входы блока памяти и второй-тринадцатый входы вычитающего счетчика являются соответственно входом тактовой частоты, сигнальными и информационными входами устройства.

Такая схема позволяет по сравнению с устройствами-аналогами осуществить возможность работы устройства в режиме, близком к режиму реального времени, и обеспечить нулевую вероятность пропуска (в случае наличия априорно достоверной информации о протоколе) за счет синтаксического распознавания протокола TFTP, основанного на операции идентификации передаваемых по каналу пакетов и правил обмена ими в ходе сеанса связи.

Однако данное устройство имеет существенный недостаток - узкую область применения, а именно только для анализа протокола TFTP. Кроме того, идентификация пакетов в устройстве-прототипе осуществляется методом последовательного структурного разбора. Анализ пакетов стека протоколов пакетной передачи данных показал, что идентификация пакетов различных протоколов возможна путем сравнения значений полей пакета или их комбинаций с эталонными значениями, уникальными для каждого из протоколов, причем данное сравнение может выполняться параллельно (Золотов С. Протоколы Internet. - СПб.: BHV - Санкт-Петербург, 1998. - 304 с.: ил.). Анализ сетей, построенных на базе стека протоколов TCP/IP показал, что подавляющее число нарушений безопасности в сетях данного типа связано с атаками на доступность, которые заключаются в формировании направленного шторма пакетов (например, запросов на установление соединения) в адрес атакуемого узла сети, вызывающих непредусмотренный расход ресурсов узла, что приводит к снижению эффективности функционирования, а иногда и к полной недоступности его ресурсов для абонентов сети (Медведовский И.Д. и др. Атака на Internet. - М.: ДМК, 1999. - 336 с.: ил.). При этом последовательность поступления указанных пакетов может полностью соответствовать правилам обмена информацией, предусмотренных спецификациями на соответствующий протокол (например, в соглашениях принятых для стека протоколов TCP/IP количество последовательно поступающих запросов на установление соединения не ограничивается). Устройство-прототип позволяет осуществлять синтаксический анализ протоколов без учета возможных злоупотреблений, связанных с наличием большого числа повторяющихся типов пакетов.

Целью заявленного технического решения является разработка устройства поиска информации, обеспечивающего расширение области его применения и повышение быстродействия за счет реализации параллельной структурной идентификации пакетов широкого спектра протоколов пакетной передачи данных, а также обнаружения последовательностей повторяющихся пакетов с контролем допустимых интервалов их следования.

Поставленная цель в заявленном устройстве поиска информации достигается тем, что в известном устройстве обслуживания запросов абонентов вычислительной системы, содержащем N формирователей временных интервалов, где N≥1, N блоков селекции, делитель частоты, вход которого является первым тактовым входом устройства, дополнительно введены N регистров временного хранения, N двухвходовых элементов И, разрешающий трехвходовый элемент И, N-входовый элемент ИЛИ-НЕ, электронный ключ, регистр хранения маски, N-входовый элемент И и блок управления.

При этом в заявленном устройстве выход делителя частоты соединен с вторыми тактовыми входами формирователей временных интервалов. Соответствующие разряды К-разрядных входов "Код времени хранения", где K≥1 - разрядность кода времени хранения, формирователей временных интервалов соединены между собой и являются соответствующими разрядами K-разрядного входа "Код времени хранения" устройства. Разрешающие входы N формирователей временных интервалов и первый вход разрешающего трехвходового элемента И соединены между собой и являются разрешающим входом устройства. Соответствующие разряды М-разрядных информационных входов, где М≥1 - количество двоичных разрядов анализируемого блока информации, N регистров временного хранения, N блоков селекции и электронного ключа соединены между собой и являются соответствующими разрядами первого М-разрядного информационного входа устройства. Входы "Инициализация" N формирователей временных интервалов и регистра хранения маски соединены между собой и являются входом "Инициализация" устройства. Выход разрешающего трехвходового элемента И подключен к входам "Разрешение" формирователей временных интервалов, электронного ключа и является выходом "Разрешение" устройства. При этом i-й выход "Выбор блока" блока управления, где i=1, 2...N, соединен с входом "Выбор блока" i-го формирователя временных интервалов. Выход i-го двухвходового элемента И соединен с i-м входом N-входового элемента ИЛИ-НЕ и входом "Результат сравнения" i-го формирователя временных интервалов. Выход "Установка" i-го формирователя временных интервалов соединен с входом "Установка" i-го регистра временного хранения. Выход "Статус блока" i-го формирователя временных интервалов соединен с вторым входом i-го двухвходового элемента И, i-м входом блока управления и i-м входом N-входового элемента И-НЕ. Выход N-входового элемента И-НЕ соединен с третьим входом трехвходового элемента И и является выходом "Статус устройства" устройства. Разряды М-разрядного входа "Установка маски" регистра хранения маски являются соответствующими разрядами М-разрядного входа "Установка маски" устройства. Разряды М-разрядного выхода регистра хранения маски подключены к соответствующим разрядам М-разрядных входов "Маска" N блоков селекции. М-разрядный выход i-го регистра временного хранения подключен ко второму М-разрядному информационному входу i-го блока селекции. Выход "Предварительный результат" i-го блока селекции подключен к первому входу i-го двухвходового элемента И. Инверсный выход N-входового элемента ИЛИ-НЕ подключен к второму входу разрешающего трехвходового элемента И. М-разрядный информационный выход электронного ключа является третьим М-разрядным информационным выходом устройства.

Формирователь временных интервалов состоит из первого, второго, третьего и четвертого двухвходовых элементов И, первого и второго двухвходовых элементов ИЛИ-НЕ, двухвходового элемента И-НЕ, двухвходового элемента ИЛИ, RS-триггера и счетчика. При этом K-разрядный вход счетчика является К-разрядным входом "Код времени хранения" формирователя. Первый вход первого двухвходового элемента И подключен к второму входу двухвходового элемента И-НЕ и является входом "Выбор блока" формирователя. Второй вход первого двухвходового элемента И является входом "Разрешение" формирователя, выход первого двухвходового элемента И соединен с первым информационным входом RS-триггера, первым входом первого двухвходового элемента ИЛИ-НЕ и является выходом "Установка" формирователя. Второй вход первого двухвходового элемента ИЛИ-НЕ является входом "Результат сравнения" формирователя. Инверсный выход первого двухвходового элемента ИЛИ-НЕ соединен с инверсным установочным входом счетчика. Первый вход двухвходового элемента ИЛИ является входом "Инициализация" формирователя. Выход двухвходового элемента ИЛИ соединен с вторым информационным входом RS-триггера. При этом выход RS-триггера соединен с первым входом третьего двухвходового элемента И, вторым входом второго двухвходового элемента И и первым входом четвертого двухвходового элемента И. Выход четвертого двухвходового элемента И является выходом "Статус блока" формирователя. Первый вход второго двухвходового элемента И является вторым тактовым входом формирователя. Выход второго двухвходового элемента И соединен со счетным входом счетчика, а его инверсный выход переполнения соединен с вторым входом второго двухвходового элемента ИЛИ-НЕ. Инверсный выход второго двухвходового элемента ИЛИ-НЕ соединен с вторым входом третьего двухвходового элемента И. Выход третьего двухвходового элемента И соединен с входом сброса счетчика и вторым входом двухвходового элемента ИЛИ. Инверсный выход двухвходового элемента И-НЕ соединен с вторым входом четвертого двухвходового элемента И. Первый вход второго двухвходового элемента ИЛИ-НЕ подключен к первому входу двухвходового элемента И-НЕ и является разрешающим входом формирователя.

Блок селекции состоит из первой и второй групп двухвходовых элементов И по М элементов в каждой группе и компаратора. При этом первый вход j-го двухвходового элемента И первой группы двухвходовых элементов И, где j=1, 2...М, является j-м разрядом первого М-разрядного информационного входа блока селекции. Первый вход j-го двухвходового элемента И второй группы двухвходовых элементов И является j-м разрядом второго М-разрядного информационного входа блока селекции. Второй вход j-го двухвходового элемента И первой группы двухвходовых элементов И соединен с вторым входом j-го двухвходового элемента И второй группы двухвходовых элементов И и является j-м разрядом М-разрядного входа "Маска" блока селекции. Выход j-го двухвходового элемента И первой группы двухвходовых элементов И соединен с j-м информационным входом первой группы информационных входов компаратора. Выход j-го двухвходового элемента И второй группы двухвходовых элементов И соединен с j-м информационным входом второй группы информационных входов компаратора, а выход равенства компаратора является выходом "Предварительный результат" блока селекции.

Электронный ключ состоит из М двухвходовых элементов И. При этом первый вход j-го двухвходового элемента И является j-м разрядом М-разрядного информационного входа электронного ключа. Вторые входы двухвходовых элементов И соединены между собой и являются входом "Разрешение" электронного ключа. Выход j-го двухвходового элемента И является j-м разрядом М-разрядного информационного выхода электронного ключа.

Блок управления состоит из шифратора приоритетов, первой группы инверторов из Р инверторов, где второй группы инверторов из N инверторов, дешифратора. При этом i-й инверсный вход шифратора приоритетов является i-м входом "Статус блока" блока управления, а k-й инверсный выход шифратора приоритетов, где k=1, 2...P, соединен с входом k-го инвертора первой группы инверторов. Инверсный выход k-го инвертора первой группы инверторов соединен с k-м входом дешифратора, i-й инверсный выход дешифратора соединен с входом i-го инвертора второй группы инверторов. Инверсный выход i-го инвертора является i-м выходом "Выбор блока" блока управления.

Указанная новая совокупность существенных признаков за счет введения N регистров временного хранения, N двухвходовых элементов И, разрешающего трехвходового элемента И, N-входового элемента ИЛИ-НЕ, электронного ключа, регистра хранения маски, N-входового элемента И-НЕ и блока управления обеспечивает повышение быстродействия устройства, возможность расширения спектра идентифицирования пакетов и возможность обнаружения последовательности повторяющихся пакетов с контролем допустимых интервалов их следования, что обуславливает возможность использования заявленного устройства как для идентификации протоколов путем структурного анализа пакетов, так и для защиты от возможных злоупотреблений, связанных с наличием большого числа повторяющихся типов пакетов.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественных всем признакам заявленного устройства поиска информации, отсутствуют. Следовательно, заявленное изобретение соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

Заявленные объекты изобретения поясняются чертежами, на которых:

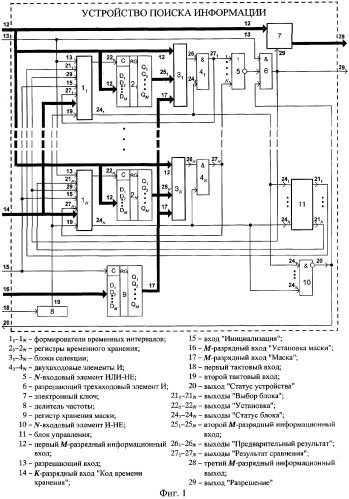

на фиг.1 - устройство поиска информации;

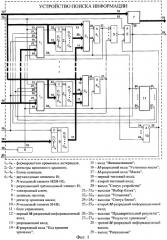

на фиг.2 - формирователь временных интервалов;

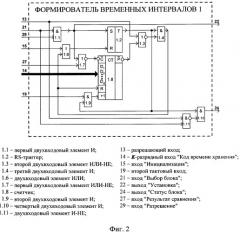

на фиг.3 - блок селекции;

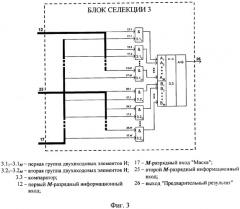

на фиг.4 - электронный ключ;

на фиг.5 - блок управления;

на фиг.6 - временная диаграмма работы устройства.

Устройство (см. фиг.1) состоит из N формирователей временных интервалов 1.1-1.N, где N≥1, N блоков селекции 3.1-3.N, делителя частоты 8, N регистров временного хранения 2.1-2.N, N двухвходовых элементов И 4.1-4.N, разрешающего трехвходового элемента И 6, N-входового элемента ИЛИ-НЕ 5, электронного ключа 7, регистра хранения маски 9, N-входового элемента И-НЕ 10, блока управления 11.

Элементы соединены между собой следующим образом (см. фиг.1). Вход делителя частоты 8 является первым тактовым входом 18 устройства, а его выход соединен с вторыми тактовыми входами 19 формирователей временных интервалов 1.1-1.N. Соответствующие разряды К-разрядных входов "Код времени хранения", где К≥1 - разрядность кода времени хранения, формирователей временных интервалов 1.1-1.N соединены между собой и являются соответствующими разрядами K-разрядного входа "Код времени хранения" 14 устройства. Разрешающие входы 13 формирователей временных интервалов 1.1-1.N и первый вход разрешающего трехвходового элемента И 6 соединены между собой и являются разрешающим входом 13 устройства. Соответствующие разряды М-разрядного информационного входа, где М≥1 - количество двоичных разрядов анализируемого блока информации, N регистров временного хранения 2.1-2.N, N блоков селекции 3.1-3.N и электронного ключа 7 соединены между собой и являются соответствующими разрядами первого М-разрядного информационного входа 12 устройства. Входы "Инициализация" формирователей временных интервалов 1.1-1.N и регистра хранения маски 9 соединены между собой и являются входом "Инициализация" 15 устройства. Выход разрешающего трехвходового элемента И 6 подключен к входам "Разрешение" 29 формирователей временных интервалов 1.1-1.N, электронного ключа 7 и является выходом "Разрешение" 29 устройства. При этом выход "Выбор блока" 21.i каждого блока управления 11 соединен с входом "Выбор блока" соответствующего формирователя временных интервалов 1.i. Выход i-го двухвходового элемента И 4.i соединен с i-м входом N-входового элемента ИЛИ-НЕ 5 и входом "Результат сравнения" i-го формирователя временных интервалов 1.i. Выход "Установка" 22.i каждого формирователя временных интервалов 1.i соединен с входом "Установка" соответствующего регистра временного хранения 2.i. Выход "Статус блока" 24 каждого формирователя временных интервалов 1.i соединен с вторым входом соответствующего двухвходового элемента И 4.i, i-м входом блока управления 11 и i-м входом N-входового элемента И-НЕ 10. Выход N-входового элемента И-НЕ 10 подключен к третьему входу разрешающего трехвходового элемента И 6 и является выходом "Статус устройства" 20 устройства. Разряды М-разрядного входа "Установка маски" 16 регистра хранения маски 9 являются соответствующими разрядами М-разрядного входа "Установка маски" 16 устройства. Разряды М-разрядного выхода регистра хранения маски 9 подключены к соответствующим разрядам М-разрядных входов "Маска" 17 N блоков селекции 3.1-3.N. М-разрядный выход i-го регистра временного хранения 2.i подключен ко второму М-разрядному информационному входу 25.i блока селекции 3.i. Выход "Предварительный результат" 26.1-26.N каждого блока селекции 3.1-3.N подключен к первому входу соответствующего двухвходового элемента И 4.1-4.N. Инверсный выход N-входового элемента ИЛИ-НЕ 5 подключен к второму входу разрешающего трехвходового элемента И 6, а М-разрядный информационный выход электронного ключа 7 является третьим М-разрядным информационным выходом 28 устройства.

Регистры временного хранения 2.1-2.N предназначены для сохранения копии поступившего блока информации. Регистр хранения маски 9 предназначен для хранения битовой маски, необходимой для сравнения значимых битов блока информации. Описание работы и схема таких регистров известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др. "Цифровые интегральные микросхемы". Справочник. - М.: "Радио и связь", 1994, с.57-62.

Делитель частоты 8 предназначен для выработки синхронизирующей последовательности импульсов и может быть построен по любой известной схеме. См., например, П.П.Мальцев, Н.С.Долидзе и др. Справочник "Цифровые интегральные микросхемы". - М.: "Радио и связь", 1994, с.62-74. При этом входом делителя будет счетный вход счетчика, а выходом делителя - один из выходов счетчиков.

Формирователи временных интервалов (ФВИ) 1.1-1.N предназначены для управления записью в соответствующие регистры временного хранения, контроля истечения времени хранения и формирования сигнала о состоянии соответствующих регистров временного хранения. ФВИ может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.2, состоит из первого 1.1, второго 1.9, третьего 1.4 и четвертого 1.10 двухвходовых элементов И, первого 1.7 и второго 1.3 двухвходовых элементов ИЛИ-НЕ, двухвходового элемента И-НЕ 1.11, двухвходового элемента ИЛИ 1.6, RS-триггера 1.2, счетчика 1.8. При этом K-разрядный вход счетчика 1.8 является К-разрядным входом "Код времени хранения" 14 ФВИ. Первый вход первого двухвходового элемента И 1.1 подключен к второму входу двухвходового элемента И-НЕ 1.11 и является входом "Выбор блока" 21 ФВИ. Второй вход первого двухвходового элемента И 1.1 является входом "Разрешение" 29 ФВИ. Выход первого двухвходового элемента И 1.1 соединен с первым информационным входом RS-триггера 1.2, первым входом первого двухвходового элемента ИЛИ-НЕ 1.7 и является выходом "Установка" 22 ФВИ. Второй вход первого двухвходового элемента ИЛИ-НЕ 1.7 является входом "Результат сравнения" 27 ФВИ. Инверсный выход первого двухвходового элемента ИЛИ-НЕ 1.7 соединен с инверсным установочным входом счетчика 1.8. Первый вход двухвходового элемента ИЛИ 1.6 является входом "Инициализация" 15 ФВИ. Выход двухвходового элемента ИЛИ 1.6 соединен с вторым информационным входом RS-триггера 1.2. Выход RS-триггера 1.2 соединен с первым входом третьего двухвходового элемента И 1.4, вторым входом второго двухвходового элемента И 1.9 и первым входом четвертого двухвходового элемента И 1.10, выход которого является выходом "Статус блока" 24 ФВИ. Первый вход второго двухвходового элемента И 1.9 является вторым тактовым входом 19 ФВИ. Выход второго двухвходового элемента И 1.9 соединен со счетным входом счетчика 1.8. Инверсный выход переполнения счетчика 1.8 соединен с вторым входом второго двухвходового элемента ИЛИ-НЕ 1.3. Инверсный выход второго двухвходового элемента ИЛИ-НЕ 1.3 соединен с вторым входом третьего двухвходового элемента И 1.4. Выход третьего двухвходового элемента И 1.4 соединен с входом сброса счетчика 1.8 и вторым входом двухвходового элемента ИЛИ 1.6. Первый вход второго двухвходового элемента ИЛИ-НЕ (1.3) подключен к первому входу двухвходового элемента И-НЕ (1.11) и является разрешающим входом 13 ФВИ. Инверсный выход двухвходового элемента И-НЕ (1.11) соединен с вторым входом четвертого двухвходового элемента И (1.10).

RS-триггер 1.2 предназначен для хранения логического значения, определяющего режим функционирования ФВИ, и может быть построен по любой известной схеме. См., например, Интегральные микросхемы. Справочник. Под редакцией Тарабрина - 2-е изд., испр. - М.: "Энергоатомиздат", 1985, с.197.

Счетчик 1.8 предназначен для счета поступающих на его вход счетных импульсов, выработки управляющего сигнала, определяемого кодом начального заполнения по информационным входам и периодом следования тактовых импульсов, то есть выполняет функцию настраиваемого таймера. Описание работы и схема такого счетчика известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др. "Цифровые интегральные микросхемы: справочник", - М.: "Радио и связь", 1994, с.64-65.

Блоки селекции 3.1-3.N предназначены для сравнения разрядов вновь поступившего блока информации с разрядами блоков информации, ранее сохраненных в регистрах временного хранения 2.1-2.N (с учетом маски) и формирования результата сравнения, причем сравнение осуществляется с учетом маски. Блок селекции может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.3, селекции состоит из первой и второй групп двухвходовых элементов И по М элементов в каждой группе 3.11-3.1M, 3.21-3.2M и компаратора 3.3. При этом первый вход j-го двухвходового элемента И первой группы двухвходовых элементов И, где j=1, 2...М, является j-м разрядом первого М-разрядного информационного входа 12 блока селекции. Первый вход j-го двухвходового элемента И второй группы двухвходовых элементов И является j-м разрядом второго М-разрядного информационного входа 25 блока селекции. Второй вход j-го двухвходового элемента И первой группы двухвходовых элементов И соединен с вторым входом j-го двухвходового элемента И второй группы двухвходовых элементов И и является j-м разрядом М-разрядного входа "Маска" 17 блока селекции. Выход j-го двухвходового элемента И первой группы двухвходовых элементов И соединен c j-м информационным входом первой группы информационных входов компаратора 3.3. Выход j-го двухвходового элемента И второй группы двухвходовых элементов И соединен с j-м информационным входом второй группы информационных входов компаратора 3.3. Выход равенства компаратора является выходом "Предварительный результат" 26 блока селекции.

Компаратор 3.3 предназначен для сравнения двух М-разрядных двоичных кодов, установленных на его входах, и формирования результата сравнения. Описание работы и схема компаратора приведены, например, в книге: В.Л.Шило "Популярные микросхемы ТТЛ", - М.: "АРГУС", 1993, с.183-184.

Электронный ключ 7 предназначен для коммутации поступающего на его вход М-разрядного двоичного кода на его выход при наличии разрешающего сигнала и может быть реализован по любой известной схеме с учетом описанной функции. В частности, его схема, показанная на фиг.4, состоит из М двухвходовых элементов И 7.1.1-7.1.M. При этом первый вход j-го двухвходового элемента И является j-м разрядом М-разрядного информационного входа электронного ключа. Вторые входы двухвходовых элементов И соединены между собой и являются входом "Разрешение" 29 электронного ключа. Выход j-го двухвходового элемента И является j-м разрядом М-разрядного информационного выхода электронного ключа.

Блок управления 11 предназначен для выбора из множества доступных для использования ФВИ ФВИ с наименьшим номером и может быть реализован по любой известной схеме. В частности, его схема, показанная на фиг.5, состоит из шифратора приоритетов 11.1, первой группы инверторов из Р инверторов, где где - операция округления до ближайшего большего целого, второй группы инверторов из N инверторов 11.21-11.2P, 11.41-11.4N и дешифратора 11.3. При этом i-й инверсный вход шифратора приоритетов 11.1 является i-м входом "Статус блока" 24.i блока управления, а каждый инверсный выход шифратора приоритетов 11.1 соединен с входом соответствующего инвертора первой группы инверторов. Инверсный выход каждого инвертора первой группы инверторов соединен с соответствующим входом дешифратора 11.3. Каждый инверсный выход дешифратора 11.3 соединен с входом соответствующего инвертора второй группы инверторов. Инверсный выход i-го инвертора второй группы инверторов является i-м выходом "Выбор блока" 21 блока управления.

Шифратор 11.1 и дешифратор 11.3 предназначены для преобразования одного или нескольких сигналов низкого уровня на одном из входов шифратора 11.1 в двоичный код наименьшего из них на выходе дешифратора 11.3. Данное преобразование осуществляется с учетом приоритетов сигналов, соответствующих номерам входов. Схемы их реализации известны и приведены, например, в книге В.Л.Шило "Популярные цифровые микросхемы", М.: "Радио и связь", 1987, с.147-148.

Для пояснения работы устройства рассмотрим следующие режимы его функционирования:

инициализацию устройства;

работу устройства при поступлении первого подлежащего анализу блока двоичной информации (БДИ);

работу устройства при поступлении последующих БДИ.

Инициализация устройства производится следующим образом. На М-разрядном входе "Установка маски" 16 устанавливается битовая маска, разрядность которой равна разрядности анализируемого БДИ. Битовая маска предназначена для указания значимых битов БДИ, посредством которых осуществляется его идентификация. При этом значения логической единицы в разрядах этой маски соответствуют позициям значимых битов в первом М-разрядном информационном входе 12 устройства. Во всех остальных позициях должны быть установлены значения логического нуля. На К-разрядном входе "Код времени хранения" 14 устройства устанавливается код, задающий максимальное время хранения копии БДИ в устройстве. Наименьшему времени хранения соответствует наибольший код, являющийся дополнением до максимального числа, представимого в К-разрядном коде. На разрешающем входе 13 устанавливается логический ноль, а на входе "Инициализация" 15 - логическая единица. Логическая единица на входе "Инициализация" 15 поступает на соответствующие входы ФВИ 11-1N и на вход инициализации регистра хранения маски 9. Логическая единица на входе инициализации регистра хранения маски 9 обеспечивает запись битовой маски в регистр, при этом значения разрядов М-разрядного выхода 17 регистра хранения маски 9 будут соответствовать значениям соответствующих битов маски. Логический ноль на разрешающем входе 13 устройства поступает на соответствующие входы ФВИ 11-1N и первый вход разрешающего трехвходового элемента И 6. При этом логический ноль на первом входе разрешающего трехвходового элемента И 6 обеспечивает формирование логического нуля на его выходе вне зависимости от логических значений на других его входах. Логический ноль с выхода трехвходового элемента И 6 поступает на выход "Разрешение" 29 устройства и соответствующие входы ФВИ 11-1N и на соответствующий вход электронного ключа 7. Логический ноль на входе "Разрешение" 29 электронного ключа 7 поступает на соответствующие входы двухвходовых элементов И 7.11-7.1M, что обеспечивает формирование на их выходах, а соответственно, на всех разрядах третьего М-разрядного информационного выхода 28 устройства логических нулей, вне зависимости от значений разрядов первого М-разрядного информационного входа 12 устройства. Логический ноль на выходе "Разрешение" 29 устройства означает отсутствие информации для считывания на третьем М-разрядном информационном выходе 28 устройства. Логический ноль на разрешающем входе 13 ФВИ поступает на вход двухвходового элемента И-НЕ 1.11, что приводит к появлению на его выходе логической единицы, которая, поступая на второй вход четвертого двухвходового элемента И 1.10, обеспечивает соответствие логического значения на выходе четвертого двухвходового элемента И 1.10 логическому значению на его первом входе. Логический ноль на входе "Разрешение" 29 ФВИ поступает на вход первого двухвходового элемента И 1, что обеспечивает значение логического нуля на его выходе, который поступает на вход S RS-триггера 1.2 и на выход "Установка" 22 ФВИ. Выход "Установка" 22 ФВИ предназначен для управления записью информации в соответствующий регистр временного хранения 2. Логический ноль на входе S RS-триггера 1.2 одновременно с логической единицей на его входе R, поступающей с входа "Инициализация" 15 через двухвходовый элемент ИЛИ 1.6, приводит к установке на выходе RS-триггера 1.2 логического нуля, что в свою очередь блокирует поступление на счетный вход счетчика 1.8 тактовых импульсов с второго тактового входа 19 ФВИ, формирует логический нуль на выходе "Статус блока" 24 ФВИ. Значение логического нуля на выходе "Статус блока" 24 ФВИ означает, что данный ФВИ свободен и готов к работе, а в соответствующем регистре временного хранения присутствует информация, которая не должна влиять на логику работы устройства. При наличии логического нуля на выходах "Статус блока" 241-24N всех ФВИ 11-1N на соответствующих входах N-входового элемента ИЛИ-НЕ 5, блока управления 11 и N-входового элемента И-НЕ 10 будут установлены логические нули. При этом на инверсном выходе N-входового элемента ИЛИ-НЕ 5 установится логическая единица, которая поступит на второй вход разрешающего трехвходового элемента И 6. На инверсном выходе N-входового элемента И-НЕ 10 также установится логическая единица, которая поступает на третий вход разрешающего трехвходового элемента И 6 и на выход "Статус устройства" 20 устройства. При этом на выходе разрешающего трехвходового элемента И 6 продолжает оставаться логический нуль, определенный наличием логического нуля на его первом входе. Логические значения на выходе "Статус устройства" 20 имеют следующий смысл: логическая единица на указанном выходе означает, что устройство готово к работе, а логический нуль - устройство занято. Логические нули на входах "Статус блока" 241-24N блока управления 11 поступают на соответствующие инверсные входы шифратора приоритетов 11.1. В соответствии с логикой работы на выходе шифратора приоритетов 11.1 устанавливается P-разрядный код, соответствующий номеру входа с наивысшим приоритетом из числа инверсных входов, на которых установлен логический нуль (чем меньше номер инверсного входа, тем выше его приоритет). Далее, первой группой инверторов 11.21-11.2P инверсный код преобразуется в прямой и поступает на вход дешифратора 11.3. В соответствии с логикой работы дешифратор 11.3 устанавливает логический нуль на одном из своих N инверсных выходов, номер которого соответствует коду, установленному на входах дешифратора, при этом на остальных инверсных выходах дешифратора будет установлена логическая единица. В целях обеспечения корректной работы блока управления выход дешифратора 11.3 не используется, поскольку в ситуации, когда все ФВИ заняты, на всех входах "Статус блока" 241-24N блока управления 11 будут установлены логические нули, что приведет к установлению на выходе дешифратора 11.3 логической единицы. Сигналы с инверсных выходов дешифратора инвертируются второй группой инверторов 11.41-11.4N. Таким образом, на одном из выходов "Выбор блока" 211-21N. блока управления 11, номер которого соответствует наименьшему номеру свободного и готового к работе ФВИ, будет установлена логическая единица, а на всех остальных - логический ноль. В результате инициализации устройства логическая единица установится на первом выходе "Выбор блока" 211 блока управления 11. Инициализация устройства заканчивается установкой на входе "Инициализация" 15 устройства логического нуля, который переводит в режим хранения регистр хранения маски 9, а также приводит к установке на выходе двухвходового элемента ИЛИ 1.6 ФВИ логического нуля, что переводит RS-триггер 1.2 ФВИ в режим хранения информации. Процедура инициализации устройства не предусматривает сброс регистров временного хранения 21-2N и по ее завершении в указанных регистрах находится случайная информация.

В начальный период, когда подлежащие анализу БДИ не поступают, на разрядах первого М-разрядного информационного входа 12, на разрешающем входе 13, входе "Инициализация" 15 устройства установлены логические нули. На вход делителя частоты 8 через первый тактовый вход 18 устройства от внешнего генератора поступают тактовые импульсы. На K-разрядном входе "Код времени хранения" 14 устройства установлен код, задающий максимальное время хранения копии БДИ в устройстве. На выходе "Разрешение" 29 устройства установлен логический нуль. На выходе "Статус устройства" 20 устройства установлена логическая единица. Тактовые импульсы с второго тактового выхода 19 делителя часто