Широкополосное приемопередающее устройство

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи и может быть использовано при построении приемо-передающих устройств для радиосвязи. Заявленное устройство расширяет арсенал средств данного назначения. Целью изобретения является разработка широкополосного приемопередающего устройства, обеспечивающего повышение помехоустойчивости радиосвязи к преднамеренным ответным помехам путем изменения скорости перестройки частот в зависимости от сложившейся помеховой обстановки. Заявленное широкополосное приемопередающего устройство содержит на передающей стороне кодер, первый фазовый манипулятор, второй фазовый манипулятор, первый высокочастотный ключ, второй высокочастотный ключ, элемент НЕ, сумматор, смеситель, частотный синтезатор, управляемый ключ, генератор псевдослучайной последовательности, генератор управления ключом. Приемная часть устройства содержит смеситель, усилитель промежуточной частоты, демодулятор, первый и второй фазовые детекторы, первый и второй ключи, элемент НЕ, элемент ИЛИ, декодер, дешифратор команды изменения скорости, анализатор качества канала, дешифратор квитанции, блок формирования сообщения, блок памяти, линии задержки, блок синхронизации, генератор псевдослучайной последовательности, генератор управления ключом, управляемый ключ и частотный синтезатор. Благодаря введению дополнительных блоков и новых связей обеспечивается возможность изменения скорости ППРЧ в случае действия ответных помех, что приведет к улучшению качества связи в радиоканале. При отсутствии помех радиолиния может работать на минимальной скорости переключения частот, что позволяет экономить энергетический и частотный ресурсы радиолинии. 3 ил.

Реферат

Заявленное устройство относится к области радиосвязи, в частности к широкополосным приемопередающим устройствам с псевдослучайной перестройкой рабочей частоты (ППРЧ), и может найти применение в радиолиниях при передачи дискретных сообщений.

Известны широкополосные приемопередающие устройства, осуществляющие передачу сообщений в режиме ППРЧ (см., например патент РФ №2185029). Данное устройство содержит на передающей стороне: кодер, блок синхронизации, генератор псевдослучайной последовательности (ГПСП), блок управления, синтезатор частот, модулятор, усилитель мощности, передающую антенну, преобразователь псевдослучайной последовательности, а на приемной стороне: приемную антенну, входной усилитель, смеситель-гетеродин, детектор, блок АРУ, решающее устройство, декодер, блок синхронизации, ГПСП, блок управления, преобразователь псевдослучайной последовательности. Недостатком данного аналога является низкая пропускная способность, обусловленная одноканальным режимом его работы.

Известно также широкополосное устройство с ППРЧ по патенту РФ №2210187 содержащее: смеситель, полосовой фильтр, амплитудный детектор, решающий блок, управляемый генератор тактовой частоты, перестраиваемый синтезатор частот (генератор кода). Недостатком данного аналога является низкая пропускная способность и низкая помехозащищенность к ответным помехам (помехам вслед).

Наиболее близким по технической сущности к заявленному устройству является широкополосное приемопередающее устройство (патент МПК 7 Н 04 7/00 РФ №2157051, 2000 год), функционирующее в режиме ППРЧ и осуществляющее передачу блоков сообщения по двум информационным каналам за счет фазовой манипуляции несущей частотно-манипулированного сигнала основного информационного канала. Данное устройство выбрано в качестве прототипа. Устройство-прототип в передающей части содержит первый и второй фазовые манипуляторы, входы которых объединены и являются информационным входом второго (дополнительного) канала, а их выходы соединены с первым и вторым входами сумматора через первый и второй высокочастотные ключи соответственно, вход первого информационного канала соединен со вторым входом первого высокочастотного ключа и через элемент НЕ со вторым входом второго высокочастотного ключа, выход сумматора соединен с первым входом смесителя, второй вход которого подключен к выходу частотного синтезатора, вход которого соединен с выходом ГПСП, а выход смесителя соединен с передающей антенной.

Приемная часть устройства содержит: приемную антенну, соединенную с первым входом смесителя, выход последнего подключен к входу усилителя УПЧ, выход которого соединен с входом демодулятора, первый выход которого является информационным выходом первого канала приемной части устройства и одновременно подключен ко второму входу смесителя через последовательно соединенные блоки синхронизации, генератора псевдослучайной последовательности (ГПСП) и частотного синтезатора, а также подключен ко второму входу первого ключа и через элемент НЕ ко второму входу второго ключа, а второй и третий выходы демодулятора подключены к входам первого и второго фазовых детекторов, выходы которых соединены с первым и вторым входами сумматора через первый и второй ключи соответственно, выход элемента ИЛИ является информационным выходом второго информационного канала.

Данное радиосредство позволяет вести передачу и прием сообщений в условиях непреднамеренных помех с заданным качеством.

Недостатком прототипа является относительно низкая помехоустойчивость к преднамеренным ответным помехам, которая обусловлена отсутствием возможности контроля качества рабочих каналов, что, в свою очередь, не дает возможности управлять устройством в зависимости от действующих на радиолинию помех и понижает количество одновременно работающих на одинаковых группах частот абонентов.

Целью изобретения является разработка широкополосного приемопередающего устройства, обеспечивающего повышение помехоустойчивости радиосвязи к преднамеренным ответным помехам путем изменения скорости перестройки частот в зависимости от сложившейся помеховой обстановки.

Для достижения технического результата в известном широкополосном приемопередающем устройстве, содержащем в передающей части генератор псевдослучайной последовательности, первый и второй фазовые манипуляторы, выходы которых подключены к первым входам соответственно первого и второго высокочастотных ключей, вторые входы которых подключены соответственно к входу и выходу элемента НЕ, выходы первого и второго высокочастотных ключей подключены соответственно к первому и второму входам сумматора, выход которого подключен к информационному входу смесителя, управляющий вход и выход которого подключены соответственно к выходу частотного синтезатора и входу передающей антенны, в приемной части устройство содержит блок синхронизации, выход которого подключен к входу генератора псевдослучайной перестройки частоты, а вход блока синхронизации подключен к первому входу первого ключа и информационному выходу демодулятора, второй и третий выходы которого подключены к входам соответственно первого и второго фазовых детекторов, выходы которых подключены ко вторым входам соответственно первого и второго ключей, выходы которых подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является информационным выходом второго канала, первый вход второго ключа подключен к выходу элемента НЕ, вход демодулятора подключен к выходу усилителя промежуточной частоты, вход которого подключен к выходу смесителя, первый и второй входы которого подключены к выходам соответственно частотного синтезатора и приемной антенны, дополнительно введены в передающей части кодер, управляемый ключ и генератор управления ключом. Вход кодера является информационным входом второго канала, а выход подключен к входам первого и второго фазовых манипуляторов. Частотный и управляющий входы управляемого ключа подключены к выходам соответственно генератора псевдослучайной последовательности и генератора управления ключом, а выход управляемого ключа подключен к входу частотного синтезатора. Вход генератора управления ключом подключен к выходу линии задержки приемной части. В приемной части введены дополнительно блок формирования сообщения, линия задержки, декодер, дешифратор команды изменения скорости, анализатор качества канала, блок памяти, дешифратор квитанции, генератор управления ключом и управляемый ключ. Выход блока формирования сообщения подключен к входу элемента НЕ и второму входу первого высокочастотного ключа передающей части, а его первый и второй входы подключены к выходам соответственно дешифратора команды изменения скорости и анализатора качества канала. Вход дешифратора команды изменения скорости и канальный вход анализатора качества канала объединены и подключены к входу дешифратора квитанции и выходу декодера, являющемуся выходом канала управления, вход декодера подключен к входу элемента НЕ и информационному выходу демодулятора. Выходы дешифратора команды изменения скорости и анализатора качества канала подключены соответственно к входу линии задержки и первому входу блока памяти второй вход которого и выход подключены соответственно к выходу дешифратора квитанции и входу генератора управления ключом, выход которого подключен к первому входу управляемого ключа, частотный вход и выход которого подключены соответственно к выходу генератора псевдослучайной последовательности и входу частотного синтезатора, а выход линии задержки подключен к входу генератора управления ключом передающей части.

Благодаря новой совокупности существенных признаков за счет введения новых блоков появляется возможность контролировать качество рабочих каналов радиолинии и при изменении качества связи управлять скоростью переключения частот, что повысит помехозащищенность устройства при постановке ответных помех и, соответственно, позволит повысить пропускную способность радиолинии за счет управления скоростью ППРЧ.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

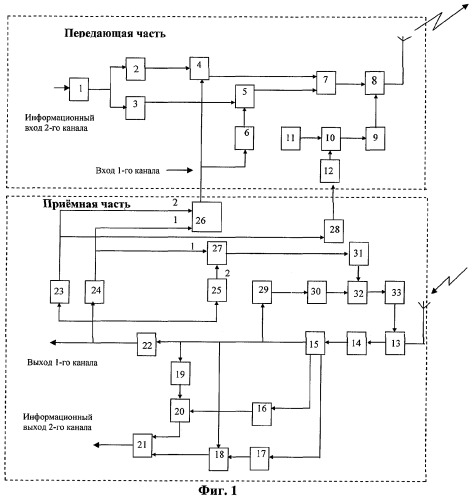

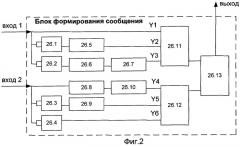

Заявляемое устройство поясняется чертежами, на которых показаны:

фиг.1 - структурная схема широкополосного приемопередающего устройства;

фиг.2 - функциональная схема блока формирования сообщения;

фиг.3 - функциональная схема блока памяти.

Заявленное широкополосное приемопередающего устройство содержит на передающей стороне кодер 1, первый фазовый манипулятор 2, второй фазовый манипулятор 3, первый высокочастотный ключ 4, второй высокочастотный ключ 5, элемент НЕ 6, сумматор 7, смеситель 8, частотный синтезатор 9, управляемый ключ 10, генератор псевдослучайной последовательности 11, генератор управления ключом 12. Вход кодера 1 является информационным входом устройства. Выход кодера 1 подключен параллельно к первому фазовому манипулятору 2 и второму фазовому манипулятору 3, а их выходы соединены с первым и вторым входами сумматора 7 через первый 4 и второй 5 высокочастотные ключи соответственно. Вход 1-го канала соединен со вторым входом первого высокочастотного ключа 4 и через элемент НЕ 6 со вторым входом второго высокочастотного ключа 5, выход сумматора 7 соединен с первым входом смесителя 8, второй вход которого подключен к выходу частотного синтезатора 9, вход которого через управляемый ключ 10, соединен с выходом генератора псевдослучайной последовательности 11. Второй (управляющий) вход управляемого ключа 10 соединен с выходом генератора управления ключом 12, вход которого соединен с приемной частью, а выход смесителя 8 соединен с передающей антенной.

В приемной части устройства-смесителя 13, усилителя промежуточной частоты 14, демодулятора 15, первого 17 и второго 16 фазовых детекторов, первого 18 и второго 20 ключей, элемента НЕ 19, элемента ИЛИ 21, декодера 22, дешифратора команды изменения скорости 23, анализатора качества канала 24, дешифратора квитанции 25, блока формирования сообщения 26, блока памяти 27, линии задержки 28, блока синхронизации 29, генератора псевдослучайной последовательности 30, генератора управления ключом 31, управляемого ключа 32, частотного синтезатора 33.

Приемная часть содержит: приемную антенну, соединенную с первым входом смесителя 13, выход последнего подключен к входу усилителя промежуточной частоты 14, выход которого соединен с входом демодулятора 15. Первый выход демодулятора 15 одновременно подключен к входам элемента НЕ 19, декодера 22 и блока синхронизации 29. Второй и третий выходы демодулятора 15 подключены соответственно к входам первого 17 и второго 16 фазовых детекторов, выходы которых соединены с первым и вторым входами элемента ИЛИ 21, через первый 18 и второй 20 ключи соответственно. Второй вход второго ключа 20 соединен с выходом элемента НЕ 19. Выход элемента ИЛИ 21 является информационным выходом 2-го канала. Выход декодера 22 подключен одновременно к входам дешифратора команды изменения скорости 23, анализатору качества канала 24 и дешифратору квитанции 25. Выход дешифратора команды изменения скорости 23 подключен к первому входу блока формирования сообщения 26 и к входу линии задержки 28, выход которой подключен к входу генератора управления ключом 12 передающей части. Выход анализатора качества канала подключен ко второму входу блока формирования сообщения 26 и первому входу блока памяти 27, второй вход которого соединен с выходом дешифратора квитанции 25, а выход соединен со входом генератора управления ключом 31, выход последнего подключен к управляющему входу управляемого ключа 32, частотный вход которого через генератор псевдослучайной последовательности 30 и блок синхронизации 29 подключен к первому выходу демодулятора 15, а выход через частотный синтезатор 33 подключен ко второму входу смесителя 13. Выход блока формирования сообщения 26 подключен к входу 1-го канала передающей части.

Кодер 1 служит для преобразования входной информационной последовательности импульсов в выходную последовательность с дополнительной кодовой избыточностью, позволяющей в декодере 22, служащем для восстановления исходной информационной последовательности, исправлять ошибки, появляющиеся из-за помех в переключаемых частотных каналах. Варианты реализации кодера 1 и декодера 22 известны и приведены, например, в /5/, стр.323-330, рис.8.9, 8.11, 8.16.

В заявленном устройстве фазовые манипуляторы 2 и 3 предназначены для формирования двух фазомодулированных сигналов (ОФМ), сдвинутых относительно друг друга по несущей частоте. Фазовые манипуляторы 2 и 3 известны и, в частности, могут быть реализованы по схеме относительного фазового модулятора, описанного в работе /6/, стр.119 на рис.4.25.

Высокочастотные ключи 4 и 5, предназначены для поочередного подключения одного из независимых трактов (выходов фазовых манипуляторов 2 и 3) на сумматор 7 по закону изменения информационного сигнала в первом канале.

Элемент НЕ 6 предназначен для инверсии сигнала первого информационного канала с целью обеспечения противофазного управления ключами 4 и 5 соответственно.

Сумматор 7 предназначен для объединения сигналов двух независимых трактов. Он может быть реализован в простейшем случае на обычном резистивном сумматоре и описан в патенте на изобретение №2157051 от 27.09.2000 г.

В качестве смесителя 8 и 13 могут быть использованы любые выпускаемые промышленностью смесители.

Генераторы псевдослучайной последовательности 11 и 30 предназначены для формирования одинаковых на передающей и приемной сторонах радиолинии последовательностей равновероятных номеров частот в диапазоне i=1,...,N. Реализация данного генератора известна и описана в патенте на изобретение 191.

Демодулятор 15 предназначен для выделения сигналов ЧМн первого канала и разделения сигналов ОФМ второго канала по двум независимым трактам. Он может быть реализован по известным схемам, в частности по схеме частотного детектора с двумя расстроенными контурами. Реализация демодулятора известна и описана в /9/.

Первый и второй фазовые детекторы 17 и 16 предназначены для детектирования фазоманипулируемых сигналов, соответствующих первому и второму трактам второго канала. Реализация фазовых детекторов известна и описана в /9/.

Ключи 18 и 20 предназначены для выбора тракта приема демодулированных сигналов от фазовых детекторов 17 и 16 на соответствующие входы элемента ИЛИ 21. Они могут быть выполнены на базе транзистора, в ключевом режиме представленного в /6/ на рис.3.4.9, стр.93.

Элемент НЕ 19 предназначен для инверсии сигнала первого информационного канала с целью обеспечения противофазного управления ключами 18 и 20 соответственно, он аналогичен элементу НЕ 6.

Элемент ИЛИ 21 предназначен для формирования единой последовательности информационных символов второго канала.

Использованные в заявленном устройстве элементы и их схемы описаны в следующих источниках информации:

- высокочастотные ключи 4 и 5 в /1/ на стр.376;

- элементы НЕ 6 и 19 в /1/ на стр.59;

- элемент ИЛИ 21 в /1/ на стр.74.

Управляемые ключи 10 и 32 предназначены для коммутации ГПСП и частотного синтезатора для передачи на частотный синтезатор цифровой последовательности, в соответствии с которой частотный синтезатор генерирует номер рабочей частоты. В качестве управляемого ключа можно использовать элемент 2И который реализован в микросхемах серии КР 1533.

Дешифратор команды изменения скорости 23 предназначены для преобразования цифрового кода, сформированного в блоке формирования сообщения приемной части корреспондента "Б", в сигнал для перестройки частоты генерирования импульсов управления в генераторе управления ключом предающей части. Схема дешифратора 23 описана например в /8/, стр.47, рис.2.4.

Блок синхронизации 29 служит для формирования тактовой последовательности импульсов с периодом следования Т/2, где Т - длительность работы радиолинии на одной частоте. Вариант реализации блока синхронизации 29 известен и описан, например, в /1/, стр.193, рис.5-19.

Генераторы псевдослучайной последовательности 11 и 30 предназначены для формирования одинаковых на передающей (11) и приемной (30) сторонах радиолинии последовательностей равновероятных номеров частот в диапазоне i=1,...,N. В качестве ГПСП можно использовать любой ГПСП, производимый промышленностью, например ГПСП, используемый в радиостанциях комплекса Р-168.

Синтезатор частот 9 и 33 служит для формирования несущего колебания на каждой очередной псевдослучайно перестраиваемой частоте. Вариант реализации синтезатора частот 9 и 33 известен и представлен, например, в /7/, стр.214, рис.7.7(а).

Усилитель промежуточной частоты 14 предназначен для усиления принятого радиосигнала на промежуточной частоте до величины, необходимой для работы последующих блоков приемного тракта. Вариант реализации усилителя промежуточной частоты 14 известен и описан, например, в /1/, стр.100, рис.3-3.

Анализатор качества канала 24 предназначен для контроля качества рабочего канала. Оценка рабочего канала производится по отношению уровней полезного сигнала и помех. В качестве анализатора рабочего канала можно взять анализатор канала, применяемый в аппаратуре Р-163-АР [8].

Дешифратор квитанции 25 предназначен для дешифрации цифрового кода, означающего, что корреспондент получил команду на изменение скорости перестройки частоты. В качестве дешифратора квитанции можно использовать дешифратор, аналогичный дешифратору команды изменения скорости.

Линия задержки 12 предназначена для задержки сигнала на увеличение скорости перестройки частоты на время передачи сообщения корреспонденту. В качестве линии задержки можно использовать выпускаемые промышленностью линии задержки с требуемым временем задержки.

Генератор управления ключом 12, 31 представляет из себя генератор импульсов с регулируемой частотой генерации и служит для генерации импульсов, поступающих на вход управляемого ключа. Частота генерации импульсов может быть увеличена в случае браковки канала. В качестве генератора управления ключом можно использовать, любой генератор с изменяющейся частотой импульсов.

Блок формирования сообщения 26 предназначен для формирования цифрового кода, обозначающего увеличение скорости переключения частоты, при подаче импульса на первый вход, и формирования цифрового кода, обозначающего квитанцию, при подаче импульса на второй вход.

Блок формирования сообщения 26, показанный на фиг.2, состоит из первого 26.1, второго 26.2, третьего 26.3, четвертого 26.4 элементов И-НЕ, первой 26.5, второй 26.6, третьей 26.7, четвертой 26.8, пятой 26.9 и шестой 26.10 линий задержки, первого трехвходового 26.11, второго трехвходового 26.12 и третьего двухвходового 26.13 элементов ИЛИ. Входы первого 26.1 и второго 26.2 элементов И-НЕ и первый вход первого трехвходового элемента И-НЕ 26.11 объединены и являются первым входом блока 26. Входы третьего 26.3, четвертого 26.4 элементов И-НЕ и вход четвертой линии задержки 26.8 объединены и являются вторым входом блока 26. Выходы первого 26.1 и второго 26.2 элементов И-НЕ подключены к входам соответственно первой 26.5 и второй 26.6 линий задержек. Выходы второй 26.6 и четвертой 26.8 линий задержек подключены к входам соответственно третьей 26.7 и шестой 26.10 линий задержки. Выходы первой 26.5 и третьей 26.7 линий задержки подключены соответственно к второму и третьему входам первого трехвходового элемента ИЛИ 26.11. Выходы шестой 26.10 и пятой 26.9 линий задержки и выход четвертого элемента И-НЕ подключены соответственно к первому, второму и третьему входам второго трехвходового элемента ИЛИ 26.11. Выходы первого 26.11 и второго 26.12 трехвходовых элементов ИЛИ подключены соответственно к первому и второму входам двухвходового элемента ИЛИ 26.13, выход которого является выходом блока 26.

Блок памяти 27 предназначен для формирования управляющего импульса, поступающего на вход блока 31, при поступлении импульсов на первый и второй входы.

Блок памяти 27, схема которого показана на фиг.3, состоит из первого 27.1 и второго 27.2 JK-триггеров и элемента ИЛИ 27.3. Входы i1 первого 27.1 и второго 27.2 JK-триггеров являются соответственно первым и вторым входами блока, а их входы r1 объединены и заземлены. Выходы первого 27.1 и второго 27.2 JK-триггеров подключены соответственно к первому и второму входам элемента ИЛИ 27.3, выход которого является выходом блока 27.

Элементная база, используемая для реализации генератора управления ключом 12, 31, блока формирования сообщения 26 и блока памяти 27 представлена в 10. В качестве автогенератора, показанного на фиг.2 и фиг.4, можно использовать любой автогенератор на элементах ТТЛ, выпускаемый промышленностью.

Устройство фиг.1 работает следующим образом. Дискретные сигналы второго канала одновременно поступают на вход кодера 1, преобразуются в информационную последовательность импульсов с дополнительной кодовой избыточностью и с выхода кодера 1 одновременно поступают на информационные входы первого 2 и второго 3 фазовых манипуляторов, на выходе которых формируются два ОФМ сигнала, отличающихся несущими частотами F1 и F2, сдвинутыми относительно друг друга по частоте на величину ΔF=F2-F1. Сигналы ОФМ второго канала с несущими F1 и F2 используются в качестве частот "нажатия" (F1) и "отжатия" (F2) при передаче сообщения по первому каналу. Таким образом, по второму каналу передача сообщений осуществляется с помощью сигналов ОФМ.

Дискретные сигналы первого канала одновременно подаются на второй управляющий вход первого высокочастотного ключа 4 и через элемент НЕ 6 на второй управляющий вход второго высокочастотного ключа 5, а на их первые информационные входы поступают ОФМ сигналы второго канала с выходов первого 2 и второго 3 фазовых манипуляторов соответственно. Причем дискретный сигнал первого канала осуществляет замыкание (размыкание) одного из двух высокочастотных ключей 4 или 5. Это обеспечит появление на одном из входов и выходе сумматора 7 одного из двух ОФМ сигналов с несущей частотой F1 или F2. Таким образом, по первому каналу передача сообщения осуществляется с помощью сигналов ОФМ/ЧМн.

Этот сигнал с ОФМ/ЧМн поступает на первый вход смесителя 8. На второй вход смесителя 8 подается перестраиваемое по псевдослучайной программе опорное колебание рабочей частоты fpi с выхода частотного синтезатора 9, управляемого с помощью ГПСП 11. При этом частотный синтезатор 9 формирует опорное колебание рабочей частоты передачи fpi, по псевдослучайной программе из совокупности n частот, выделенных для связи, со скоростью перестройки, которая может быть изменена по команде приемной части. Изменение скорости перестройки частотного синтезатора осуществляется с помощью управляемого ключа 10, первый (частотный) вход которого подключен к выходу ГПСП 11, второй (управляющий) вход подключен к выходу генератора управления ключом 12, а выход подключен ко входу частотного синтезатора 9. Изменение скорости переключения производится следующим образом: ГПСП 11 формирует цифровой код с частотой ωmax, который подается на вход управляемого ключа 10, коммутирующего выход ГПСП 11 со входом частотного синтезатора 9. Коммутация выхода ГПСП 11 со входом частотного синтезатора 9 происходит после прихода импульса с выхода генератора управления ключом 12 на второй (управляющий) вход управляемого ключа. Цифровой код поступает на вход частотного синтезатора 9, который формирует частоту, соответствующую этому коду. Формирование данной частоты происходит до поступления следующего цифрового кода, который поступит на вход частотного синтезатора 9 при следующей коммутации выхода ГПСП 11 со входом частотного синтезатора 9. Таким образом, время формирования частотным синтезатором одной частоты будет изменяться от частоты подачи импульсов управления на второй вход управляемого ключа.

Таким образом, на выходе смесителя 8 формируется сигнал с ОФМ/ЧМн на i-й рабочей частоте fpi, i=1...n, который излучается антенной в сторону корреспондента. Принятый сигнал ОФМ/ЧМн - ППРЧ на частоте fpi поступает на первый сигнальный вход смесителя 13, на второй вход которого подается перестраиваемое по псевдослучайной программе опорное колебание fi с выхода частотного синтезатора 33.

В результате преобразования в смесителе 13 принятого и опорного сигналов на его выходе формируется ОФМ/ЧМн сигналы промежуточной частоты, которые усиливаются в УПЧ 14 и подаются на вход демодулятора 15. На первом выходе демодулятора 15 формируется дискретный сигнал первого канала, по которому вместе с информационными сигналами передаются команды управления. Этот сигнал поступает на вход декодера 22 и одновременно на блок синхронизации 29, обеспечивающего формирование очередного номера рабочей частоты ГПСП 30 и синхронную перестройку частотного синтезатора 33, а с выхода декодера 22 - к получателю сообщения и одновременно на входы анализатора качества канала 24, дешифратора квитанции 25 и дешифратора команды изменения скорости 23. При браковке канала с выхода анализатора качества канала 24 подается сигнал логической единицы одновременно на первый вход блока памяти 27 и на первый вход блока формирования сообщения 26.

Блок формирования сообщения (фиг.2) работает следующим образом: на вход Y1 элемента ИЛИ 1 поступает логическая единица, на вход Y2, через время задержки τзадержки, логический ноль, на вход Y3, через время задержки 2τзадержки, логический ноль. С выхода элемента ИЛИ 1 сигналы поочередно поступают на вход элемента ИЛИ 3, и т.к. на второй вход элемента ИЛИ 3 сигналы в данный момент времени не подаются, на выходе элемента ИЛИ 3, т.е. выходе устройства, формируется цифровая последовательность 1 0 0, означающая команду на увеличение скорости переключения частот, которая передается корреспонденту. Линии задержки предназначены для последовательного прихода сигналов. На второй вход устройства сигнал логической единицы поступает с выхода дешифратора команды изменения скорости 23. Соответственно, на вход Y6 элемента ИЛИ 2 поступает логический ноль, на вход Y5, через время задержки τзадержки, логический ноль, на вход Y4, через время задержки 2τзадержки, логическая единица. На выходе устройства формируется последовательность 0 0 1, означающая квитанцию, которая передается корреспонденту.

Блок памяти 27 (фиг.3) работает следующим образом: при браковке канала связи с выхода анализатора качества канала 24 на вход i1 первого JK-триггера, являющийся первым входом устройства, поступает сигнал логической единицы. С выхода первого триггера на первый вход элемента ИЛИ поступает логическая единица. При поступлении сигнала логической единицы с выхода дешифратора квитанции 25 на вход i1 второго триггера, который является вторым входом устройства, на выходе элемента ИЛИ, являющемся выходом устройства, формируется сигнал логической единицы, который является управляющим сигналом для блока 31.

На приемной части корреспондента принятый цифровой код увеличения скорости переключения синтезатора частот подается на вход дешифратора команды изменения скорости 23, с выхода которого подается сигнал логической единицы на второй вход блока формирования сообщения 26 и через линию задержки 28 на вход генератора управления ключом 12 передающей части. Линия задержки 28 задерживает этот сигнал на время передачи ее корреспонденту. При подаче сигнала на второй вход блока формирования сообщения 26 данный блок формирует квитанцию и по 1-му каналу передающей части передает ее корреспонденту. На приемной части корреспондента квитанция поступает на вход дешифратора квитанции 25, на выходе которого формируется сигнал логической единицы, подающийся на второй вход блока памяти 27. С выхода блока памяти 27 передается сигнал на увеличение частоты генерации управляющих импульсов на вход генератора управления ключом 31. При поступлении этого сигнала генератор управления ключом 31 увеличивает частоту импульсов переключения управляемого ключа 32 в N раз, что в свою очередь приводит к уменьшению времени работы на одной частоте, т.е. к увеличению скорости ППРЧ. Число N может изменяться путем перепрограммирования блока 31.

На втором и третьем выходе демодулятора 15 выделяются сигналы ОФМ на одной из несущих частот F1 или F2, которые поступают на соответствующие входы фазового детектора 16 или 17. Дискретные сигналы второго канала с выходов первого 17 или второго 16 фазовых детекторов подаются на первые управляющие входы первого 18 и второго 20 ключей соответственно. На второй управляющий вход ключа 18 и через элемент НЕ 19, на второй управляющий вход ключа 20 поступают дискретные сигналы с первого выхода демодулятора 15, что обеспечивает поступление на вход элемента ИЛИ 21 дискретного сигнала второго канала с соответствующего выхода фазового детектора. С выхода элемента ИЛИ 21 дискретный сигнал второго канала поступает получателю сообщения.

По сравнению с прототипом предлагаемое техническое решение позволяет повысить помехозащищенность широкополосного устройства от преднамеренных ответных помех и увеличить пропускную способность радиоканала за счет регулировки скорости ППРЧ, в зависимости от действующих помех при передаче дискретных сообщений.

Литература.

1. Батушев В.А. Микросхемы и их применение. М.: Радио и связь, 1983. - 271 с.

2. Горелов Г.В., Волков А.А., Шелухин В.И. Каналообразующие устройства железнодорожной телемеханики и связи. - М.: Транспорт, 1994. - 240 с.

3. Интегральные микросхемы. Справочник. Под редакцией Тараблина Б.В. - М: Радио и связь, 1984. - 528 с.

4. Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987.- 392 с.

5. Королев А.И. Автоматика, телемеханика и связь на железнодорожном транспорте. М.: Воениздат, 1985. - 488 с.

6. Радиоприемные устройства / Под ред. Л.Г.Барулина. М.: Радио и связь, 1984. - 272 с.

7. Системы с прыгающей частотой / В кн.: Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987. - С.352-356.

8. Комплекс средств радиосвязи "Арбалет". - СПб.: ВАС, 1996. - 132 с.

9. Широкополосное приемопередающее устройство (патент на изобретение РФ №2157051, 2000 г.).

10. Шило В.Л. Популярные микросхемы ТТЛ. - М.: Аргус, 1993. - 63 с.

Широкополосное приемопередающее устройство, содержащее в передающей части генератор псевдослучайной последовательности, первый и второй фазовые манипуляторы, выходы которых подключены к первым входам соответственно первого и второго высокочастотных ключей, вторые входы которых подключены соответственно к входу и выходу элемента НЕ, выходы первого и второго высокочастотных ключей подключены соответственно к первому и второму входам сумматора, выход которого подключен к информационному входу смесителя, управляющий вход и выход которого подключены соответственно к выходу частотного синтезатора и входу передающей антенны, и в приемной части содержащее блок синхронизации, выход которого подключен к входу генератора псевдослучайной перестройки частоты, а вход блока синхронизации подключен к первому входу первого ключа и информационному выходу демодулятора, второй и третий выходы которого подключены к входам соответственно первого и второго фазовых детекторов, выходы которых подключены к вторым входам соответственно первого и второго ключей, выходы которых подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является информационным выходом второго канала, первый вход второго ключа подключен к выходу элемента НЕ, вход демодулятора подключен к выходу усилителя промежуточной частоты, вход которого подключен к выходу смесителя, первый и второй входы которого подключены к выходам соответственно частотного синтезатора и приемной антенны, отличающееся тем, что в передающей части дополнительно введены кодер, вход которого является информационным входом второго канала, а выход подключен к входам первого и второго фазовых манипуляторов, управляемый ключ, частотный и управляющий входы которого подключены к выходам соответственно генератора псевдослучайной последовательности и генератора управления ключом, а выход управляемого ключа подключен к входу частотного синтезатора, в приемной части введены дополнительно блок формирования сообщения, выход которого подключен к входу элемента НЕ и второму входу первого высокочастотного ключа передающей части, а первый и второй входы блока формирования сообщения подключены к выходам соответственно дешифратора команды изменения скорости и анализатора качества канала, вход дешифратора команды изменения скорости и канальный вход анализатора качества канала объединены и подключены к входу дешифратора квитанции и выходу декодера, являющемуся выходом первого канала, вход декодера подключен к входу элемента НЕ и информационному выходу демодулятора, выходы дешифратора команды изменения скорости и анализатора качества канала подключены соответственно к входу линии задержки и первому входу блока памяти, второй вход которого и выход подключены соответственно к выходу дешифратора квитанции и входу генератора управления ключом, выход которого подключен к первому входу управляемого ключа, частотный вход и выход которого подключены соответственно к выходу генератора псевдослучайной последовательности и входу частотного синтезатора, а выход линии задержки подключен к входу генератора управления ключом передающей части.