Устройство для демультиплексирования

Иллюстрации

Показать всеИзобретение относится к технике цифровой связи, а именно к устройствам для выделения компонентных потоков (каналов пользовательских данных) в цифровых системах передачи информации с временным уплотнением. Техническим результатом является расширение функциональных возможностей за счет обеспечения одним устройством демультиплексирования различных нестандартизированных цифровых передач информации, называемых радиоциклами, которые содержат часть символов канала пользовательских данных, а также проверочные или служебные символы, и в которых отсутствует синхрогруппа, с различными видами фазовой и квадратурно-амплитудной модуляции. Для этого устройство для демультиплексирования содержит устройство настройки, первое ОЗУ, первый перестроитель сигналов, преобразователь кода, сумматор по модулю К, устройство формирования канала данных. Новым является введение делителя на два, элемента И, первого счетчика, дешифратора, второго перестроителя сигналов, удалителя такта, второго счетчика, второго ОЗУ. 4 ил.

Реферат

Изобретение относится к технике цифровой связи, а именно к устройствам для выделения компонентных потоков (каналов пользовательских данных) в цифровых системах передачи информации с временным уплотнением.

Существуют цифровые передачи как соответствующие рекомендациям ИТI-Т (стандартные цифровые передачи), так и большое количество нестандартизированных цифровых передач, называемых радиоциклами.

Под радиоциклом понимается нестандартное с точки зрения рекомендаций ИТI-Т уплотнение цифровой информации.

Структура радиоцикла определяется фирмой - разработчиком аппаратуры передачи данных. Обычно радиоцикл содержит синхрогруппу, служебные символы и один канал пользовательских данных (информация, передаваемая в канале, как правило, соответствует рекомендациям ИТI-Т).

Прием такой цифровой передачи осуществляется путем синхронизации цифрового потока с последующим выделением канала пользовательских данных в соответствии с фазой работы синхронизатора.

Однако имеются радиоциклы, которые не содержат синхрогруппу. Они содержат часть символов канала пользовательских данных, к которым добавляется несколько символов, используемых при декодировании на приемном конце в случае применения какого-либо помехозащищенного кодирования либо для определенных целей пользователей.

Пример структуры такого радиоцикла приведен на фиг.4.

Известные устройства для демультиплексирования не позволяют осуществить выделение канала пользовательских данных из радиоцикла, содержащего часть символов канала пользовательских данных, а также проверочные или служебные символы, и в которых отсутствует синхрогруппа.

Известны устройство для выделения цифровых потоков [Левин А.С., Плоткин М.А. Цифровые системы передачи информации. М.: Радио и связь. - с.87. Рис.3.24.] и многоканальное устройство для приема дискретной информации [Авторское свидетельство СССР №1292200, Н 04 L 25/40], содержащие приемник синхросигнала, генераторное оборудование и канальные блоки. Эти устройства выделяют компонентные потоки в системах с временным уплотнением.

Основным недостатком данных устройств является невозможность одним и тем же устройством осуществлять демультиплексирование различных передач плезиохронной цифровой иерархии.

Известно устройство для демультиплексирования [Патент РФ №2173029, Н 04 L 25/40], содержащее устройство настройки и управления, К канальных блоков, каждый из которых состоит из оперативного запоминающего устройства, блока обработки стаффинга, выделителя компонентных позиций, формирователя тактов, информационного триггера. В этом устройстве для демультиплексирования канальные блоки представляют собой устройство, выделяющее компонентные потоки в системах с временным уплотнением.

Недостатки данного устройства следующие:

- невозможность демультиплексирования цифровых передач с видами фазовой модуляции ФМ-4, ФМ-8 и различными видами квадратурно-амплитудной модуляции, при которых одному тактовому сигналу на входе устройства соответствует К информационных сигналов.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для демультиплексирования [Решение от 7 июня 2004 о выдаче патента РФ на изобретение по заявке №2003111576/09 (012209) от 21.04.2003 г.], содержащее устройство настройки и управления, оперативное запоминающее устройство, формирователь сигналов, перестроитель сигналов, преобразователь кода, сумматор по модулю К, устройство формирования канала данных.

Указанное устройство позволяет осуществлять демультиплексирование различных нестандартизированных цифровых передач информации, называемых радиоциклами.

Недостатком данного устройства для демультиплексирования является невозможность выделения канала пользовательских данных из радиоцикла, содержащего часть символов канала пользовательских данных, а также проверочные или служебные символы, и в которых отсутствует синхрогруппа.

Технической задачей изобретения является расширение функциональных возможностей за счет обеспечения демультиплексирования одним устройством различных нестандартизированных цифровых передач, называемых радиоциклами, которые содержат часть символов канала пользовательских данных, а также проверочные или служебные символы, и в которых отсутствует синхрогруппа, с различными видами фазовой и квадратурно-амплитудной модуляции.

Указанная задача достигается тем, что в устройство для демультиплексирования, содержащее устройство настройки (УН), первое оперативное запоминающее устройство (первое ОЗУ), первый перестроитель сигналов (первый ПС), преобразователь кода (ПК), сумматор по модулю К (СМК), устройство формирования канала данных (УФКД), причем информационные входы/выходы, входы выбора режима, нового адреса, установки в ноль, записи, чтения, выбора настройки оперативных запоминающих устройств или регистров, номера настраиваемого оперативного запоминающего устройства УН являются соответствующими входами устройства для демультиплексирования, выход чтения, выход записи и первый выход выбора УН соединены соответственно с входами чтения, записи и выбора первого ОЗУ, входы/выходы позиций выделяемого канала пользовательских данных которого соединены с соответствующими входами/выходами УН, входами первого ПС и входами ПК, выходы которого соединены с соответствующими входами СМК, выходы результатов суммирования которого соединены с соответствующими его входами и входами УФКД, информационные выходы и выход разрешения первого ПС соединены с соответствующими входами УФКД, вход переноса которого соединен с соответствующим выходом СМК, выходы УН, задающие вид модуляции, соединены с соответствующими входами первого ПС, ПК, СМК и УФКД, информационные и тактовый выходы которого являются соответствующими выходами устройства для демультиплексирования, тактовый вход которого является тактовым входом для первого ПС, ПК, СМК и УФКД, согласно изобретению введены делитель на два, элемент И, первый счетчик, дешифратор, второй перестроитель сигналов (второй ПС), удалитель такта (УТ), второй счетчик, второе оперативное запоминающее устройство (второе ОЗУ), причем вход конца цикла устройства для демультиплексирования соединен с соответствующим входом делителя на два, выход которого соединен с вторым входом элемента И, выходом соединенного с разрешающим входом первого счетчика, вход К которого и вход К УТ соединены с соответствующим выходом дешифратора, выходы разрядов первого счетчика соединены с соответствующими входами дешифратора, выходы которого соединены с соответствующими входами второго ПС, информационные входы которого являются информационными входами устройства для демультиплексирования, информационные выходы второго ПС соединены с соответствующими входами первого ПС, задающие вид модуляции входы дешифратора соединены с соответствующими выходами УН, выходы чтения, записи и второй выход выбора которого соединены с соответствующими входами второго ОЗУ, адресные входы которого и адресные входы первого ОЗУ соединены с соответствующими выходами второго счетчика, тактовым входом соединенного с соответствующим выходом УТ, тактовый вход которого, а также тактовые входы делителя на два, первого счетчика и второго ПС соединены с тактовым входом устройства для демультиплексирования, выходы тактов настройки и установки в ноль УН соединены с соответствующими входами второго счетчика, вход выбора режима которого соединен с соответствующим входом устройства для демультиплексирования, вход/выход конца радиоцикла УН соединен с соответствующим входом/выходом второго ОЗУ и входом второго счетчика, вход поиска устройства для демультиплексирования соединен с первым входом элемента И и соответствующим входом УТ.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: делителя на два, элемента И, первого счетчика, дешифратора, второго перестроителя сигналов, удалителя такта, второго счетчика, второго оперативного запоминающего устройства.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в устройство для демультиплексирования с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить его функциональные возможности, обеспечивая одним устройством демультиплексирование различных нестандартизированных цифровых передач информации, называемых радиоциклами, которые содержат часть символов канала пользовательских данных, а также проверочные или служебные символы, и в которых отсутствует синхрогруппа, с различными видами фазовой и квадратурно-амплитудной модуляции.

Таким образом, изобретение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи с временным уплотнением цифровых потоков.

Таким образом, изобретение соответствует критерию "промышленная применимость".

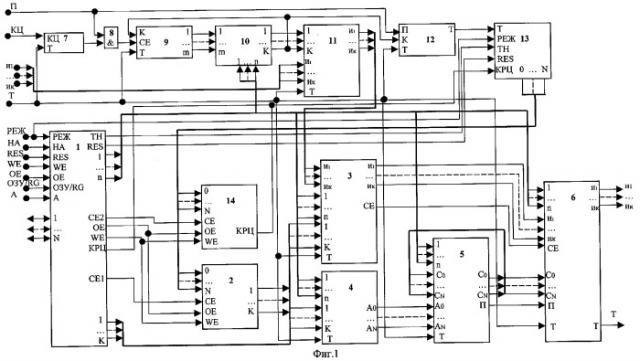

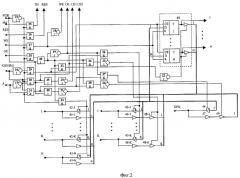

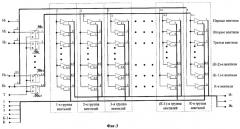

На фиг.1 представлена структурная электрическая схема устройства для демультиплексирования; на фиг.2 - принципиальная электрическая схема устройства настройки; на фиг.3 - принципиальная электрическая схема второго перестроителя сигналов; на фиг.4 - пример структуры радиоцикла.

Устройство для демультиплексирования (ДМ) (фиг.1) содержит устройство настройки (УН) 1, первое оперативное запоминающее устройство (первое ОЗУ) 2, первый перестроитель сигналов (первый ПС) 3, преобразователь кода (ПК) 4, сумматор по модулю К (СМК) 5, устройство формирования канала данных (УФКД) 6, делитель на два 7, элемент И 8, первый счетчик 9, дешифратор 10, второй перестроитель сигналов (второй ПС) 11, удалитель такта (УТ) 12, второй счетчик 13, второе оперативное запоминающее устройство (второе ОЗУ) 14, причем информационные входы/выходы (входы/выходы 1,...,N), входы выбора режима (вход РЕЖ), нового адреса (вход НА), установки в ноль (вход RES), записи (вход WE), чтения (вход ОЕ), выбора настройки оперативных запоминающих устройств или регистров (вход ОЗУ/RG), номера настраиваемого оперативного запоминающего устройства (вход А) УН 1 являются соответствующими входами устройства для демультиплексирования, выход чтения (выход ОЕ), выход записи (выход WE) и первый выход выбора (выход СЕ1) УН 1 соединены соответственно с входами чтения (вход ОЕ), записи (вход WE) и выбора (вход СЕ) первого ОЗУ 2, входы/выходы позиций выделяемого канала пользовательских данных (входы/выходы 1,...,К) которого соединены с соответствующими входами/выходами (входы/выходы 1,...,К) УН 1, входами первого ПС 3 и входами ПК 4, выходы (выходы A0,...,AN) которого соединены с соответствующими входами СМК 5, выходы результатов суммирования (выходы С0,...,Сн) которого соединены с соответствующими его входами и входами УФКД6, информационные выходы (выходы И1,...,Ик) и выход разрешения (выход СЕ) первого ПС3 соединены с соответствующими входами УФКД 6, вход переноса (вход П) которого соединен с соответствующим выходом СМК 5, выходы УН 1, задающие вид модуляции (выходы 1,...,n), соединены с соответствующими входами первого ПС 3, ПК 4, СМК 5 и УФКД 6, информационные (выходы И1,...,Ик) и тактовый выходы (выход Т) которого являются соответствующими выходами устройства для демультиплексирования, тактовый вход которого является тактовым входом для первого ПС 3, ПК 4, СМК 5 и УФКД 6, вход конца цикла (вход КЦ) устройства для демультиплексирования соединен с соответствующим входом (вход КЦ) делителя на два 7, выход которого соединен с вторым входом элемента И 8, выходом соединенного с разрешающим входом (вход СЕ) первого счетчика 9, вход К которого и вход КУТ 12 соединены с соответствующим выходом (выход К) дешифратора 10, выходы разрядов (выходы 1,...,m) первого счетчика 9 соединены с соответствующими входами (входы 1,...,m) дешифратора 10, выходы (выходы 1,...,К) которого соединены с соответствующими входами (входы 1,...,К) второго ПС 11, информационные входы (входы И1,...,Ик) которого являются информационными входами устройства для демультиплексирования, информационные выходы (выходы И1,...,Ик) второго ПС 11 соединены с соответствующими входами (входы И1,...,Ик) первого ПС 3, задающие вид модуляции входы (входы 1,...,n) дешифратора 10 соединены с соответствующими выходами (выходы 1,...,n) УН 1, выходы чтения (выход ОЕ), записи (выход WE) и второй выход выбора (выход СЕ 2) которого соединены с соответствующими входами второго ОЗУ 14, адресные входы (входы 0,...,N) которого и адресные входы (входы 0,...,N) первого ОЗУ 2 соединены с соответствующими выходами второго счетчика 13, тактовым входом (вход Т) соединенного с соответствующим выходом (выход Т) УТ 12, тактовый вход (вход Т) которого, а также тактовые входы (входы Т) делителя на два 7, первого счетчика 9 и второго ПС 11 соединены с тактовым входом (вход Т) устройства для демультиплексирования, выходы тактов настройки (выход ТН) и установки в ноль (выход RES) УН 1 соединены с соответствующими входами второго счетчика 13, вход выбора режима (вход РЕЖ) которого соединен с соответствующим входом устройства для демультиплексирования, вход/выход конца радиоцикла (вход/выход КРЦ) УН 1 соединен с соответствующим входом/выходом (вход/выход КРЦ) второго ОЗУ 14 и входом (вход КРЦ) второго счетчика 13, вход поиска (вход П) устройства для демультиплексирования соединен с первым входом элемента И 8 и соответствующим входом (вход П) УТ 12.

Устройство настройки (УН) (фиг.2) содержит инверторы 15,...,24, элементы И 25,...,И 37, элементы ИЛИ 38,..., ИЛИ 40, блок запоминания 41, содержащий N триггеров запоминания и управляемых вентилей, выходные управляемые вентили 42-1,...,42-N, 43-1,...,43-K, 44, входные вентили 45-1,...,45-N, 46-1,...,46-K, 47, управляемые вентили 48-1,...,48-К, 49, причем вход инвертора 15 соединен с вторыми входами элементов ИЛИ 38,..., ИЛИ 40 и является входом выбора режима (вход РЕЖ) УН, выход инвертора 15 соединен с вторыми входами элементов И 25,...,И 30, И 33 и третьим входом элемента И 31, вход нового адреса (вход НА) УН соединен с первым входом элемента И 25, выход которого является выходом тактов настройки (выход ТН) УН, вход установки в ноль (вход RES) УН соединен с первым входом элемента И 26, выход которого является выходом установки в ноль (выход RES) УН, вход записи (вход WE) УН соединен с первым входом элемента И 27, выход которого соединен с тактовыми входами (входы К) триггеров запоминания блока запоминания 41 и входом инвертора 18, выход которого является выходом записи (выход WE) УН, вход чтения (вход ОЕ) УН соединен с первым входом элемента И 28, выходом соединенного с первым входом элемента ИЛИ 38, выход которого соединен с входом инвертора 19 и первыми входами элементов И 32,..., И 35, вход выбора настройки оперативных запоминающих устройств или регистра (вход ОЗУ/RG) УН соединен с первыми входами элементов И 30, 31 и входом инвертора 16, выход которого соединен с первым входом элемента И 29, выход которого соединен с вторым входом элемента И 32 и разрешающими входами триггеров запоминания блока запоминания 41, вход номера настраиваемого оперативного запоминающего устройства (вход А) УН соединен с вторым входом элемента И 31 и входом инвертора 17, выход которого соединен с третьим входом элемента И 30, выходом соединенного с вторыми входами элементов И 34, И 36 и первым входом элемента ИЛИ 39, выход которого соединен с входом инвертора 20, выход которого является первым выходом выбора (выход СЕ1) УН, выход инвертора 19 является выходом чтения (выход ОЕ) УН, а также соединен с первыми входами элементов И 36, И 37, выходы которых соединены соответственно с управляющими входами управляемых выходных вентилей 43-1,...,43-К и 44, инвертор 23 входом соединен с выходом элемента И 34, а выходом - с управляющими входами управляемых вентилей 48-1,...,48-К, информационные входы которых соответственно соединены с выходами входных вентилей 46-1,...,46-К, вход инвертора 22 соединен с выходом элемента И 32, а выход - с управляющими входами управляемых вентилей блока запоминания 41, выходы триггеров запоминания которого соответственно являются задающими вид модуляции выходами (выходы 1,...,n) УН, а также соответственно соединены с входами управляемых вентилей блока запоминания 41, вход инвертора 24 соединен с выходом элемента И 35, а выход - с управляющим входом управляемого вентиля 49, вход которого соединен с выходом входного вентиля 47, вход инвертора 21 соединен с выходом элемента ИЛИ 40, а выход является вторым выходом выбора (выход СЕ2) УН, выход элемента И 31 соединен с вторыми входами элементов И 35, И 37 и первым входом элемента ИЛИ 40, выход элемента И 33 соединен с управляющими входами выходных управляемых вентилей 42-1,...,42-N, входы/выходы позиций выделяемого канала пользовательских данных (входы/выходы 1,...,К) УН соединены соответственно с выходами выходных управляемых вентилей 43-1,...,43-К и с входами входных вентилей 46-1,...,46-К, вход/выход конца радиоцикла (вход/выход КРЦ) УН соединен с выходом выходного управляемого вентиля 44 и входом входного вентиля 47, выходы входных вентилей 45-1,...,45-N соединены соответственно с информационными входами (входы D) триггеров запоминания блока запоминания 41 и с информационными входами выходных управляемых вентилей 43-1,...,43-К, 44, выходы управляемых вентилей 48-1,..., 48-К, 49 и выходы управляемых вентилей блока запоминания 41 соответственно соединены с информационными входами выходных управляемых вентилей 42-1,...,42-N, входы/выходы 1,...,N УН соединены с выходами выходных управляемых вентилей 42-1,...,42-N и с входами входных вентилей 45-1,...,45-N.

Второй перестроитель сигналов (фиг.3) содержит триггеры 501,...,50k-1, где К равно количеству информационных входов, и К групп вентилей, при этом каждая группа вентилей содержит К вентилей, причем информационные И2,...,Иk входы второго перестроителя сигналов соединены с соответствующими информационными входами триггеров 501,...,50k-1, информационный И1 вход второго перестроителя сигналов соединен с входами от первого до К-го вентилей первой группы вентилей, информационный И2 вход второго перестроителя сигналов соединен с входами от второго до К-го вентилей второй группы вентилей, информационный И3 вход второго перестроителя сигналов соединен с входами от третьего до К-го вентилей третьей группы вентилей, информационный Иk-1 вход второго перестроителя сигналов соединен с входами (K-1)-го и К-го вентилей (К-1)-й группы вентилей, информационный Иk вход второго перестроителя сигналов соединен с входом К-го вентиля К-й группы вентилей, информационные входы между информационными И3 и Иk-1 входами второго перестроителя сигналов соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, выход триггера 502 соединен с входом первого вентиля второй группы вентилей, выход триггера 501 соединен с входами первого и второго вентилей третьей группы вентилей, выход триггера 50k-2 соединен с входами от первого до (К-2)-го вентилей (К-1)-й группы вентилей, выход триггера 50k-1 соединен с входами от первого до (K-1)-го вентилей К-й группы вентилей, информационные выходы триггеров, расположенных между триггерами 502 и 50k-2, соединены с входами вентилей групп, расположенных между третьей и (К-1)-й группами вентилей, в соответствии с порядком соединений, описанном выше, вход 1 второго перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей соответствует порядковому номеру группы вентилей, вход 2 второго перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-1)-й определяется порядковым номером группы вентилей, увеличенным на число 1, а в К-й группе вентилей - порядковым номером группы вентилей, уменьшенным на число К-1, вход 3 второго перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в группах вентилей от первой до (К-2)-й определяется порядковым номером группы вентилей, увеличенным на число 2, а в К-й и в (К-1) группах вентилей - порядковым номером группы вентилей, уменьшенным на число К-2, вход К-1 второго перестроителя сигналов соединен с управляющими входами вентилей, порядковый номер которых в первой и второй группах вентилей определяется порядковым номером группы вентилей, увеличенным на число К-2, а в группах вентилей от третьей до К-й - порядковым номером группы вентилей, уменьшенным на число 2, вход К второго перестроителя сигналов соединен с управляющим входом К-го вентиля первой группы вентилей и с управляющими входами вентилей от второй до К-й группы вентилей, в которых порядковый номер вентилей определяется порядковым номером группы вентилей, уменьшенным на число 1, входы, расположенные между 3 и К-1 входами второго перестроителя сигналов, соединены с управляющими входами вентилей в соответствии с порядком соединения, описанном выше, одноименные выходы вентилей от первой до К-й группы вентилей соединены между собой и с соответствующими информационными И1,...,Иk выходами второго перестроителя сигналов, тактовый Т вход второго перестроителя сигналов соединен с тактовыми входами триггеров 501,...,50k-1.

Устройство для демультиплексирования работает следующим образом.

Устройство для демультиплексирования (ДМ) имеет два режима работы: первый - режим настройки и диагностики, второй - режим работы.

В первом режиме на входы УН 1 поступают сигналы с контроллера, работающего совместно с персональной электронной вычислительной машиной (ПЭВМ). Режим настройки и диагностики разрешается сигналом Лог."0", который поступает на вход выбора режима (вход РЕЖ) УН. Сигналом Лог."1", поступающим на вход выбора настройки оперативных запоминающих устройств или регистра (вход ОЗУ/RG) УН1, разрешается настройка оперативных запоминающих устройств (ОЗУ). Выбор настраиваемого ОЗУ осуществляется сигналом, поступающим на вход А УН 1. При настройке первого ОЗУ 2 на его вход выбора (вход СЕ) поступает сигнал Лог."0" с выхода СЕ1 УН 1, разрешая работу первого ОЗУ 2. При записи информации в первое ОЗУ 2 с выхода чтения (выход ОЕ) УН1 на соответствующий вход первого ОЗУ 2 поступает сигнал Лог."1". На вход установки в ноль (вход RES) УН 1 поступает импульсный сигнал положительной полярности, который с выхода RES УН1 поступая на соответствующий вход второго счетчика 13, устанавливает его в нулевое состояние. Адресные 0,...,N выходы второго счетчика 13 соединены с соответствующими адресными входами первого 2 и второго 14 ОЗУ. Далее по сигналу записи, поступающему с выхода записи (выход WE) УН 1 на соответствующий вход первого ОЗУ 2, в последнее по нулевому адресу в разрядах позиций выделяемого канала пользовательских данных (входы/выходы 1,...,К) осуществляется запись данных, поступающих с соответствующих входов/выходов УН 1. После этого на вход нового адреса (вход НА) УН 1 поступает сигнал, который, поступая с выхода тактов настройки (выход ТН) УН 1 на соответствующий вход счетчика 13, осуществляет смену его адреса и, следовательно, адреса первого ОЗУ 2.

Далее запись данных по новому адресу осуществляется так же, как было описано ранее.

Для проверки правильности настройки первого ОЗУ 2 сигналом установки в ноль, поступившим с выхода RES УН 1 на соответствующий вход счетчика 13, последний устанавливается в нулевое состояние. После этого сигналом Лог."1", поступившим на вход записи (вход WE) УН1 и далее с выхода WE УН1 на соответствующий вход первого ОЗУ 2, последнее переводится в режим чтения. Затем сигналом Лог."0", поступившим на вход чтения (вход ОЕ) УН1 и далее с выхода ОЕ УН1 на соответствующий вход первого ОЗУ 2, осуществляется считывание информации по нулевому адресу первого ОЗУ 2. При этом сигналы с выходов 1,...,К последнего поступают на соответствующие входы УН 1 и далее в контроллер ПЭВМ для их сравнения с исходными. Затем по сигналу нового адреса осуществляется смена адреса первого ОЗУ 2 и считывание данных по новому адресу так же, как было описано ранее.

Аналогично осуществляется настройка и проверяется правильность настройки второго ОЗУ 14. Номер настраиваемого ОЗУ задается сигналом, поступающим на вход А УН 1.

После настройки и проверки правильности настройки первого 2 и второго 14 ОЗУ осуществляется настройка блока запоминания 41, расположенного в УН 1. Настройка блока запоминания разрешается сигналом Лог."0", поступающим на ОЗУ/RG вход УН1. При этом порядок настройки и проверки ее правильности такой же, как для ОЗУ. С выходов блока запоминания сигналы, задающие вид модуляции, поступают на 1,...,n выходы УН 1 и далее на соответствующие входы первого ПС 3, ПК 4, СМК 5, УФКД 6 и дешифратора 10.

Перевод устройства для ДМ в режим работы осуществляется сигналом Лог."1", поступающим на вход РЕЖ УН 1. При этом сигналами выбора, поступающими с СЕ 1 и СЕ 2 выходов УН 1, разрешается работа первого 2 и второго 14 ОЗУ, а сигналами Лог."0" и Лог."1", поступающими соответственно с выходов чтения ОЕ и записи WE УН 1 на соответствующие входы первого 2 и второго 14 ОЗУ, последние переводятся в режим считывания данных.

В рабочем режиме устройство для ДМ осуществляет разуплотнение нестандартного цифрового потока (радиоцикла).

Демультиплексирование входного цифрового потока осуществляется следующим образом. При работе на входы поиска (вход П) и конца цикла (вход КЦ) устройства для ДМ поступают сигналы с выхода устройства для синхронизации. На информационные входы (входы И1,...,Ик) и тактовый вход (вход Т) устройства для ДМ поступают сигналы с выходов демодулятора. Пока устройство для синхронизации находится в режиме поиска первой синхрокомбинации, на вход П устройства для ДМ поступает сигнал Лог."1". Информационные сигналы с информационных входов устройства для ДМ поступают на соответствующие входы второго перестроителя сигналов 11. Тактовые сигналы с тактового входа устройства 15 для ДМ поступают на тактовые входы первого ПС 3, ПК 4, СМК 5, УФКД 6, делителя на два 7, первого счетчика 9, второго ПС 11, удалителя такта 12. Информационные сигналы с выходов (выходы И1,...,Ик) второго ПС 11 поступают на соответствующие входы первого ПС 3. На входы (1,...,n), задающие вид модуляции первого ПС 3, поступают сигналы с соответствующих выходов УН 1. Эти же сигналы поступают на соответствующие входы ПК 4, СМК 5, УФКД 6, дешифратора 10. Сигналы, задающие вид модуляции, определяют количество информационных входов на один тактовый вход. На входы позиций выделяемого канала пользовательских данных (входы 1,...,К) первого ПС 3 и ПК 4 поступают сигналы с соответствующих выходов первого ОЗУ 2.

Первый ПС 3 осуществляет перестроение информационных сигналов, поступающих на его информационные входы в зависимости от значения сигналов на его 1,...,К входах. Например, при наличии сигнала единичного уровня на входах К2, К5, K8 информационные сигналы, поступившие на входы И2, И5, И8, соответственно скоммутируются на информационные выходы И1, И2, И3 первого ПС 3.

Преобразователь кода 4 осуществляет преобразование количества сигналов, равных Лог."1", на его 1,...,К входах, в двоичный код, значение которого с выходов А0,...,An поступает на соответствующие входы сумматора по модулю К 5, где К - количество информационных входов устройства для ДМ. СМК 5 осуществляет суммирование в двоичном коде предыдущего его значения с поступившем на входы А0,...,АN. Результат суммирования в двоичном коде с выходов С0,...,СN СМК 5 поступает на соответствующие входы УФКД 6. В случае, если результат суммирования СМК 5 равен или превышает значение К, то на выходе переноса П СМК 5 формируется сигнал единичного уровня, а на его выходах C0,...,CN формируются сигналы в двоичном коде, соответствующие разности между числом суммирования и числом К.

Устройство формирования канала данных 6 осуществляет коммутацию информационных сигналов в соответствии с порядком и временем их поступления и формирование информационных сигналов на его информационных выходах (выходы И1,...,Ик) и тактового сигнала на его тактовом выходе Т при поступлении на его вход П сигнала переноса. Информационные и тактовый сигналы с выходов УФКД 6 поступают на соответствующие выходы устройства для ДМ и далее с выходов последнего на входы работающего совместно с устройством для ДМ устройства для синхронизации.

Пока не найдена синхрокомбинация, сигнал Лог."1", поступая с устройства для синхронизации на вход П устройства для ДМ и далее на первый вход элемента И 8 и соответствующий вход удалителя тактов 12, разрешает работу последних. При этом также разрешается работа первого счетчика 9.

Сигнал конца цикла, поступая из устройства для синхронизации на вход КЦ устройства для ДМ и далее на соответствующий вход делителя на два 7, разрешает работу последнего. При переходе делителя на два из нулевого в единичное состояние сигналом с его выхода, поступившим через открытый инвертор 8 на вход СЕ первого счетчика 9, разрешается его работа, и при поступлении тактового сигнала первый счетчик 9 увеличивает свое состояние на единицу. Сигналы с выходов разрядов (выходы 1,...,m) первого счетчика 9 в двоичном коде поступают на соответствующие входы дешифратора 10, сигналы с выходов 1,...,К которого поступают на соответствующие входы второго ПС 11, определяя порядок перестроения информационных сигналов, поступающих на информационные входы (входы И1,...,Ик) последнего. Число К дешифратора 10 определяется сигналами, поступающими на его 1,...,n входы с соответствующих выходов УН 1.

После появления сигнала на выходе К дешифратора 10 (конец перестроения), поступающего на соответствующий вход УТ 12, в последнем осуществляется запрет прохождения одного такта с выхода Т УТ 12 на соответствующий вход второго счетчика 13. Тем самым меняется фаза работы этого счетчика по отношению к фаза цифрового потока. Также сигнал с выхода К дешифратора 10 поступает на соответствующий вход первого счетчика 9, разрешая синхронную установку этого счетчика в нулевое состояние. Теперь при поступлении сигнала на вход СЕ счетчика 9 последний по переднему фронту тактового сигнала устанавливается в нулевое состояние.

В описанном режиме устройство для ДМ работает до тех пор, пока на входе П последнего не появится сигнал Лог."0", указывающий на то, что в устройстве для цикловой синхронизации найдена синхрокомбинация. Сигнал Лог."0", поступая с входа П устройства для ДМ на входы элемента И 8 и УТ 12, запрещает работу элемента И 8 и запрещает пропуск такта УТ 12. При этом первый счетчик 9 остается в том состоянии, в котором находился в момент появления сигнала Лог."0" на входе П устройства для ДМ.

Это состояние счетчика 9 после дешифрации его дешифратором 10 определяет порядок перестроения информационных сигналов во втором ПС 11.

Устройство настройки (УН) работает следующим образом.

Режим настройки разрешается сигналом Лог."0", который поступает на вход РЕЖ УН и далее на вход инвертора 15 и на вторые входы элементов ИЛИ 38,..., ИЛИ 40. Сигналом с выхода инвертора 15 разрешается по второму входу работа элементов И 25,...,И 30, И 33 и по третьему входу элемента И 31. При настройке первого 2 или второго 14 ОЗУ с входа ОЗУ/RG УН сигнал Лог."1" поступает на первые входы элементов И 30 и И 31, разрешая их работу по этим входам. При настройке первого ОЗУ 2 с входа А УН сигнал Лог."0" поступает на вход инвертора 17 и второй вход элемента И 31, запрещая его работу. С выхода инвертора 17 сигнал Лог."1" поступает на третий вход открытого по первому и второму входам элемента И 30. Сигнал Лог."1" с выхода элемента И 30 поступает на вторые входы элементов И 34, И 36, разрешая их работу по этим входам, и на первый вход элемента ИЛИ 39 18 и далее с выхода последнего на вход инвертора 20. С выхода инвертора 20 сигнал Лог."0" поступает на выход СЕ1 УН и далее на вход СЕ первого ОЗУ 2, разрешая его работу. С входа ОЕ УН на первый вход открытого элемента И 28 поступает сигнал Лог."1". Сигналом Лог."1", поступающим с выхода инвертора 19 через выход ОЕ УН на соответствующий вход первого ОЗУ 2, последнее устанавливается в режим записи. При этом выходные управляемые вентили 42-1,...,42-N закрыты сигналом, поступающим на их управляющие входы с выхода элемента И 33, выходной управляемый вентиль 44 закрыт сигналом, поступающим на его управляющий вход с выхода элемента И 37, управляемые вентили 48-1,...,48-К закрыты сигналом, поступающим на их управляющие входы с выхода инвертора 23, управляемый вентиль 49 закрыт сигналом, поступающим на его управляющий вход с выхода инвертора 24, управляемые вентили блока запоминания 41 закрыты сигналом, поступающим на их управляющие входы с выхода инвертора 22, выходные управляемые вентили 43-1,...,43-К открыты сигналом, поступающим на их управляющие входы с выхода элемента И 36. Сигнал записи WE поступает с соответствующего входа УН на первый вход открытого элемента И 27, и далее через инвертор 18 и через выход WE УН поступает на вход записи WE первого ОЗУ 2, осуществляя запись информации, поступающей на входы 1,...,К последнего с входов 1,...,К УН через входные вентили 45-1,...,45-К и выходные управляемые вентили 43-1,...,43-К. После этого на вход нового адреса (вход НА) УН поступает сигнал, который через открытый элемент И 25 и выход ТН УН поступает на соответствующий вход второго счетчика 13, изменяя его состояние. Далее запись данных в первое ОЗУ 2 осуществляется так же, как было описано ранее.

Для определения правильности настройки первого ОЗУ 2 сигналом установки в ноль, поступившим с входа RES УН через открытый элемент И 26 и выход RES УН на соответствующий вход второго счетчика 13, последний устанавливается в нулевое состояние. Далее по сигналу чтения ОЕ, поступившему на вход УН сигналами, поступающими на управляющие входы, открываются выходные управляемые вентили 42-1,...,42-К, закрываются выходные управляемые вентили 43-1,...,43-К и открываются управляемые вентили 48-1,...,48-К. Также по сигналу чтения, поступившему через открытый элемент И 28, элемент ИЛИ 38, инвертор 19 выход ОЕ УН, на соответствующий вход первого ОЗУ 2, в последнем осуществляется считывание информации. Считанная информация с выходов 1,...,К первого ОЗУ 2 через входы 1,...,К УН, входные вентили 46-1,...,46-К, управляемые вентили 48-1,...,48-К, выходные управляемые вентили 42-1,...,42-К и выходы 1,...,К УН поступает в контроллер ПЭВМ для ее сравнения с исходной. Далее по сигналу, поступившему на вход НА УН, как описано выше, осуществляется смена адресов первого ОЗУ 2 и считывание его данных.

При настройке второго ОЗУ 14 на вход А УН поступает сигнал Лог."1". При этом сигналом Лог."1", поступающим с выхода инвертора 20 через выход СЕ 1 УН на вход выбора СЕ первого ОЗУ 2, запрещается его работа, а сигналом Лог."0", поступающим с выхода инвертора 21 через выход СЕ 2 УН на вход выбора СЕ второго ОЗУ 14, разрешается работа последнего. При этом закрываются выходные управляемые вентили 43-1,...,43-К и управляемые вентили 48-1,...,48-К, и открывается выходной управляемый вентиль 44, а при чтении - управляемый вентиль 49. В остальном настройка второго ОЗУ 14 и правильность его настройки осуществляется, как описано выше.

При настройке регистра на вход ОЗУ/RG УН поступает сигнал Лог."0", через инвертор 16 открывая элемент И 29, сигнал с выхода которого разрешает работу триггеров запоминания блока запоминания 41. Сигналами Лог."1", поступающими с выходов инверторов 20, 21 соответственно через выходы СЕ 1 и СЕ 2 на входы СЕ первого 2 и второго 14 ОЗУ, запрещается их работа. Выходные управляемые вентили 43-1,...,43-К, 44 и управляемые вентили 48-1,...,48-К, 49 закрыты соответствующими сигналами, поступающими на их управляющие входы. По сигналу записи, поступившему с входа WE УН через открытый элемент И 27 на тактовые входы К триггеров запоминания блока запоминания 41, в последних запоминается информация, поступившая через входы 1,...,N УН и входные вентили 45-1,...,45-N на информационные входы (входы D) триггеров запоминания. Далее по сигналу чтения, поступившему на вход ОЕ УН, сигналом с выхода инвертора 22, поступившем на управляющие входы управляемых вентилей блока запоминания 41, последние открываются, и информация, записанная в триггерах запоминания, как описано ранее, поступает в контроллер ПЭВМ для ср