Преобразователь бинарного кода в фазоманипулированный код

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Его использование в системах передачи цифровой информации позволяет получить технический результат, заключающийся в уменьшении времени передачи информации и упрощении схемы преобразователя кода. Преобразователь бинарного кода в фазоманипулированный код содержит: элемент (15) ИЛИ-НЕ, элементы (11, 12) ИЛИ. Технический результат достигается благодаря тому, что введены: RS-триггер (1), счетчик (6), элементы (7-9) И-НЕ, элемент (10) ИЛИ-НЕ, мажоритарный элемент (13) и инвертор (16). 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь бинарного кода в фазоманипулированный код (см. статью В.П.Климова, И.М.Казанова, И.Л.Вишнякова "Кодирующие устройства оптических каналов" в сборнике статей "Электронная техника в автоматике", под ред. Ю.И.Конева, выпуск 16. - М.: Радио и связь, 1985 г., с.262, рис.4), выбранный в качестве аналога изобретения и содержащий тактируемый фронтом D-триггер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является информационным входом преобразователя, второй вход соединен с выходом генератора тактовых импульсов, а выход - с D-входом триггера, выход которого является информационным выходом преобразователя, а С-вход - его тактовым входом, соединенным с шиной тактовых импульсов удвоенной частоты.

Первым недостатком известного преобразователя является формирование на выходе в режиме ожидания последовательности импульсов, затрудняющей выделение момента начала поступления полезной информации.

Вторым недостатком является отсутствие возможности формирования признака начала информационной посылки, обеспечивающего взаимную синхронизацию приемника и передатчика и достоверную передачу сообщений.

Известен преобразователь бинарного кода в фазоманипулированный код (см. патент РФ №2159988 от 16.03.99, МПК: Н 03 М 5/12, "Преобразователь бинарного кода в фазоманипулированный код", Курочкин А.А., Мартынов А.П., Шишкин Г.И., опубл. 27.11.2000, Бюл. №33), выбранный в качестве прототипа и содержащий входную информационную шину и шину тактовых импульсов удвоенной частоты, соединенную с С-входом тактируемого фронтом D-триггера, D-вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с выходной информационной шиной. Устройство также содержит шину разрешения преобразования, шину запрета сигнала, формирователь синхросигнала, коммутатор, элемент ИЛИ-НЕ и счетный триггер, счетный вход которого соединен с шиной тактовых импульсов удвоенной частоты, а инверсный выход - с тактовым входом формирователя синхросигнала и первым входом элемента ИЛИ-НЕ, Второй вход элемента ИЛИ-НЕ соединен с шиной разрешения преобразования, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом коммутатора. Первый вход коммутатора соединен с входной информационной шиной, управляющий вход - с третьим входом элемента ИЛИ-НЕ и с управляющим выходом формирователя синхросигнала, информационный выход которого соединен со вторым входом коммутатора, а управляющий вход - с шиной запрета синхросигнала.

Формирователь синхросигнала содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетный триггер, регистр сдвига, содержащий первый и второй тактируемые фронтом D-триггеры, D-вход второго D-триггера соединен с прямым выходом первого D-триггера, D-вход которого соединен с шиной питания. Объединенные R-входы и С-входы первого и второго тактируемых фронтом D-триггеров являются соответственно R-входом и С-входом регистра сдвига, а инверсные выходы - соответственно выходами первого и второго разряда регистра сдвига. R-вход регистра сдвига соединен с R-входом счетного триггера, с управляющим входом формирователя синхросигнала и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к управляющему выходу формирователя синхросигнала. Второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом второго разряда регистра сдвига, выход первого разряда которого соединен с информационным выходом формирователя синхросигнала и с первым выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с тактовым входом формирователя синхросигнала. Выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со счетным входом счетного триггера, инверсный выход которого соединен с С-входом регистра сдвига.

Первым недостатком прототипа является большое время передачи информации.

Вторым недостатком является сложность схемы из-за необходимости формирования синхросигнала.

Задачей, решаемой заявляемым изобретением, является создание преобразователя кода, обладающего уменьшенным временем передачи информации и отличающегося простотой схемной реализации.

Технический результат заключается в уменьшении времени передачи информации и упрощении схемы преобразователя кода.

Это достигается тем, что преобразователь бинарного кода в фазоманипулированный код содержит двухвходовый элемент ИЛИ-НЕ, второй вход которого соединен с шиной разрешения преобразования, входную и выходную информационные шины, первый и второй элементы ИЛИ, шину тактовых импульсов. Новым является то, что дополнительно введены шина выходных тактовых импульсов, RS-триггер, трехвходовый элемент ИЛИ-НЕ, инвертор, мажоритарный элемент, первый, второй, третий элементы И-НЕ, счетчик, выход первого разряда которого соединен с первыми входами первого и второго элементов И-НЕ, выходы которых соединены с входами третьего элемента И-НЕ, выход которого соединен с первым входом мажоритарного элемента, второй вход которого соединен с шиной выходных тактовых импульсов, с выходом мажоритарного элемента и с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены, соответственно, с инверсным выходом RS-триггера и выходом трехвходового элемента ИЛИ-НЕ, первый вход которого соединен с выходом инвертора, вход которого соединен с шиной тактовых импульсов, третьим входом мажоритарного элемента и с тактовым входом счетчика, выход второго разряда которого соединен со вторым входом второго элемента И-НЕ, второй вход первого элемента И-НЕ соединен с выходом двухвходового элемента ИЛИ-НЕ, первый вход которого соединен с входной информационной шиной, а второй вход соединен со вторым входом трехвходового элемента ИЛИ-НЕ и R-входом RS-триггера, S-вход которого соединен с выходом трехвходового элемента ИЛИ-НЕ, третий вход которого соединен с прямым выходом RS-триггера, выход первого элемента ИЛИ соединен с R-входом счетчика, выход второго элемента ИЛИ соединен с выходной информационной шиной.

Указанная совокупность признаков позволяет:

- уменьшить время передачи информации за счет того, что в заявляемом устройстве время передачи логического "0" равна Тт/4 (где Тт - длительность тактового интервала на шине выходных тактовых импульсов 14), время передачи логической "1" равна 3Тт/4, а в прототипе время передачи как логического "0", так и логической "1" равна Тт;

- упростить схему преобразователя кода за счет исключения необходимости использования формирователя синхросигнала.

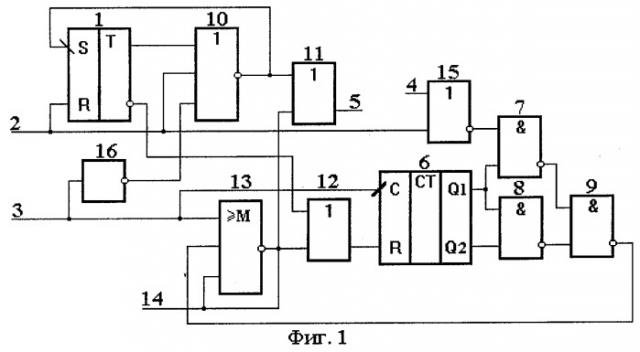

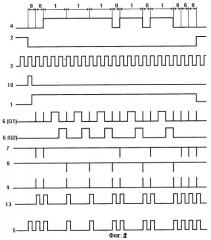

На фиг.1 приведена принципиальная схема преобразователя бинарного кода в фазоманипулированный код, на фиг.2 - диаграммы работы преобразователя.

Преобразователь бинарного кода в фазоманипулированный код содержит RS-триггер 1, шину разрешения преобразования 2, шину тактовых импульсов 3, входную 4 и выходную 5 информационные шины, счетчик 6, первый 7, второй 8, третий 9 элементы И-НЕ, первый 10, второй 15 элементы ИЛИ-НЕ, первый 11, второй 12 элементы ИЛИ, мажоритарный элемент 13, шину выходных тактовых импульсов 14 и инвертор 16.

R-вход триггера 1 подключен к шине разрешения преобразования 2, первому входу двухвходового элемента ИЛИ-НЕ 15 и первому входу трехвходового элемента ИЛИ-НЕ 10. Выход трехвходового элемента ИЛИ-НЕ 10 соединен с S-входом RS-триггера 1 и со вторым входом первого элемента ИЛИ 11. Выход первого элемента ИЛИ 11 соединен с выходной информационной шиной 5, а первый вход соединен с первым входом второго элемента ИЛИ 12, первым входом и выходом мажоритарного элемента 13 и шиной выходных тактовых импульсов 14. Выход второго элемента ИЛИ 12 соединен с R-входом счетчика 6, а второй вход - с инверсным выходом триггера 1. Прямой выход триггера 1 соединен со вторым входом трехвходового элемента ИЛИ-НЕ 10, третий вход трехвходового элемента ИЛИ-НЕ 10 соединен с выходом инвертора 16, вход которого соединен с шиной тактовых импульсов 3, вторым входом мажоритарного элемента 13 и С-входом счетчика 6. Выход второго разряда счетчика 6 соединен с первым входом первого элемента И-НЕ 8, выход первого разряда счетчика 6 соединен со вторым входом первого элемента И-НЕ 8 и с первым входом второго элемента И-НЕ 7. Второй вход второго элемента И-НЕ 7 соединен с выходом двухвходового элемента ИЛИ-НЕ 15. Второй вход двухвходового элемента ИЛИ-НЕ 15 соединен с входной информационной шиной 4. Выходы второго и первого элементов И-НЕ 7, 8 соединены с первым и вторым входами третьего элемента И-НЕ 9 соответственно. Выход третьего элемента И-НЕ 9 соединен с третьим входом мажоритарного элемента 13.

Преобразователь бинарного кода в фазоманипулированный код работает следующим образом (Фиг.2).

В режиме ожидания входной информации триггер 1 и триггеры счетчика 6 удерживаются в состоянии логического "0" сигналом разрешения преобразования 2. На информационном выходе 5 присутствует уровень логического "0". По фронту одного из тактовых импульсов, поступающих по шине 3 с периодом повторения Тт/4 (где Тт - длительность тактового интервала на шине выходных тактовых импульсов 14), формируется отрицательный перепад сигнала разрешения 2. Разрешается переключение счетчика 6, триггера 1 и прохождение входной информации через элемент ИЛИ-НЕ 15. Первый тактовый импульс проходит через элемент ИЛИ-НЕ 10 и задним фронтом вызывает переключение триггера 1 в состояние логической "1", Одновременно указанный тактовый импульс проходит на выход 5 для формирования информации в коде ИМ. После переключения триггера 1 прохождение сигналов через элемент ИЛИ-НЕ 10 запрещено. Дальнейшее формирование сигналов на информационном выходе 5 осуществляется с помощью мажоритарного элемента 13. После переключения триггера 1 в состояние логической "1" разрешается переключение счетчика 6 и в зависимости от сигнала на информационном входе 4 с задержкой Тт/8 или 5Тт/8 выход мажоритарного элемента 13 переключается в состояние логической "1" на время действия тактового импульса. Сигнал с выхода элемента 13 проходит на выходную информационную шину 5, вызывает установку в состояние логического "0" триггеров счетчика 6 и смену информации на входной шине 4 путем выдачи сигнала на выход 14. После окончания информационной посылки на входной шине разрешения 2 устанавливается уровень логической "1", и устройство переходит в режим ожидания.

Таким образом, данный преобразователь кода осуществляет передачу логического "0" сигналом на выходной информационной шине 5 с длительностью Тт/8 и паузой Тт/8, а при передаче логической "1" с длительностью Тт/8 и паузой 5Тт/8. Это позволяет уменьшить время передачи (информационной посылки с равным количеством сигналов логического "0" и логической "1") в два раза по сравнению с прототипом, поскольку в прототипе время передачи сигнала логического "0" и логической "1" равна Тт (где Тт - длительность тактового интервала). Одновременно упрощается схема преобразователя за счет отказа от использования формирователя синхросигнала.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили работоспособность и практическую ценность заявляемого объекта.

Преобразователь бинарного кода в фазоманипулированный код, содержащий двухвходовый элемент ИЛИ-НЕ, второй вход которого соединен с шиной разрешения преобразования, входную и выходную информационные шины, первый и второй элементы ИЛИ, шину тактовых импульсов, отличающийся тем, что дополнительно введены шина выходных тактовых импульсов, R-S-триггер, трехвходовый элемент ИЛИ-НЕ, инвертор, мажоритарный элемент, первый, второй, третий элементы И-НЕ, счетчик, выход первого разряда которого соединен с первыми входами первого и второго элементов И-НЕ, выходы которых соединены с входами третьего элемента И-НЕ, выход которого соединен с первым входом мажоритарного элемента, второй вход которого соединен с шиной выходных тактовых импульсов, с выходом мажоритарного элемента и с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены, соответственно, с инверсным выходом R-S-триггера и выходом трехвходового элемента ИЛИ-НЕ, первый вход которого соединен с выходом инвертора, вход которого соединен с шиной тактовых импульсов, третьим входом мажоритарного элемента и с тактовым входом счетчика, выход второго разряда которого соединен со вторым входом второго элемента И-НЕ, второй вход первого элемента И-НЕ соединен с выходом двухвходового элемента ИЛИ-НЕ, первый вход которого соединен с входной информационной шиной, а второй вход соединен со вторым входом трехвходового элемента ИЛИ-НЕ и R-входом R-S-триггера, S-вход которого соединен с выходом трехвходового элемента ИЛИ-НЕ, третий вход которого соединен с прямым выходом R-S-триггера, выход первого элемента ИЛИ соединен с R-входом счетчика, выход второго элемента ИЛИ соединен с выходной информационной шиной.