Устройство выделения маркера для системы кадровой синхронизации

Иллюстрации

Показать всеИзобретение относится к области электросвязи и может быть использовано для создания кадровой синхронизации приемников в системах передачи цифровой информации. Сущность изобретения состоит в том, что устройство выделения маркера для системы кадровой синхронизации, содержащее последовательно соединенные К ступеней анализа, в котором ступени анализа со второй по (К-1) выполнены идентично в виде блоков формирования трехразрядных результатов сравнения, при этом выходы двух предыдущих ступеней анализа подключены ко входам одного соответствующего элемента последующей ступени анализа, а к К ступени анализа, выполненной в виде блока конечного анализируемого элемента, подключены выходы блока формирования трехразрядных результатов сравнения (К-1) ступени анализа, при этом первая ступень анализа содержит регистр сдвига, выполненный в виде последовательно соединенных D-триггеров, вход первого D-триггера и выход последнего является информационным входом и информационным выходом устройства, а каждый D-триггер регистра сдвига имеет вход установки эталонной кодовой комбинации и вход настройки на длину маркера, при этом каждая смежная пара D-триггеров регистра сдвига входит в состав каждого из N блоков промежуточного анализа первой ступени анализа, отличающееся тем, что в состав каждого из N блоков промежуточного анализа первой ступени анализа введены блоки формирования пятиразрядных результатов сравнения, ко входам каждой из которых подключены трехразрядные выходы каждой пары блоков промежуточного анализа, а в состав каждой из последовательно соединенных со второй по (К-1) ступеней анализа введены блоки формирования двухразрядных результатов сравнения, причем ко входам каждого блока формирования трехразрядных результатов сравнения и каждого блока формирования двухразрядных результатов сравнения второй ступени анализа подключены выходы соответствующей пары блоков формирования пятиразрядных результатов сравнения первой ступени анализа, ко входам каждого блока формирования трехразрядных результатов сравнения и каждого блока формирования двухразрядных результатов сравнения каждой с третьей по (К-1) последующих ступени анализа подключены выходы соответствующей пары блоков формирования пятиразрядных результатов сравнения предыдущей ступени анализа, а выходы блока формирования пятиразрядных результатов сравнения (К-1) ступени анализа подключены к соответствующим дополнительным входам конечного анализирующего элемента К ступени анализа, вторые входы которого являются входами установки дополнительного количества ошибок в сигнале кадровой синхронизации, а выход является выходом кадрового синхроимпульса. Технический результат - повышение помехозащищенности и быстродействия. 4 ил.

Реферат

Изобретение относится к области электросвязи и может быть использовано для создания кадровой синхронизации приемников в системах передачи цифровой информации.

Все возрастающие скорости передачи цифровой информации (120 Мбит/с и выше) в спутниковых линиях связи с временным уплотнением цифрового потока требуют особого внимания к созданию устройств выделения маркера системы кадровой синхронизации, которые работают на частоте входного информационного потока и должны удовлетворять требованиям по быстродействию и высокой помехозащищенности.

Создание таких устройств на основе известных способов (1, 2) довольно трудоемкая задача, поэтому для удовлетворения указанных требований был использован весьма простой способ (3), основанный на преобразовании сигнала из последовательного кода в параллельный и сравнение его в эталонной комбинации маркера.

Этот способ выделения маркера кадровой синхронизации предопределяет модульность и регулярность структуры построения реализующего его устройства. Простота операций на всех ступенях анализа этого способа позволяет создавать чрезвычайно простые, высокоскоростные структурные модули выделения маркера кадровой синхронизации, а его суммирующие и анализирующие элементы способны различать К+2 возможных состояний результатов сравнения фрагментов входной информации последовательности и эталона маркера (К - допустимое количество ошибок в сигнале кадровой синхронизации).

Для понятия сущности работы устройства-прототипа рассмотрим алгоритм обработки информационной последовательности для выделения маркера кадровой синхронизации, который осуществляется в следующей последовательности:

- входной сигнал с кодово-импульсной модуляцией, представляющий собой последовательную комбинацию двоичных символов, преобразуют из последовательного кода в параллельный;

- анализируемый фрагмент входного сигнала разбивают на К-символьные группы, где К - максимально допустимое количество пораженных символов маркера;

- для каждой из возможных К-элементных групп, независимо от других групп определяют количество символов фрагмента анализируемой входной последовательности, отличающихся от соответствующих символов эталона маркера, причем результат операции представляют в виде кодового слова длиной в (К+1) бит, за каждой позицией которого закрепляется функция регистрации своего, отличного от других, количества несовпадающих символов из множества {0, 1, 2,..., К};

- полученные в результате предыдущей операции кодовые слова разбивают на смежные пары и по информации, содержащейся в каждой паре этих слов каждого анализируемого фрагмента входного сигнала длиною в 2К бит, определяют суммарное количество символов, отличающихся от соответствующих символов эталона маркера, при этом форма представления результата операции на отдельной смежной паре кодовых слов в точности совпадает с формой представления результата в предыдущей операции, причем если количество символов в анализируемом фрагменте входного сигнала, не совпадающих с соответствующими символами эталона маркера, превышает допустимое К, то на всех (К+1) позициях кодового слова, полученного в результате данной операции, устанавливают равные между собой значения логических переменных;

- полученные в результате предыдущей операции кодовые слова снова разбивают на смежные пары и повторяют все действия, описанные в предыдущей операции;

- повторяют предыдущую операцию до тех пор, пока весь результат окажется сосредоточенным в одном кодовом слове длиной в (К+1) бит;

- по полученному в результате предыдущей операции кодовому слову производят опознавание маркера кадровой синхронизации, при этом в случае равенства логических переменных в К разрядах и наличии в одном из (К+1) разрядах этого слова логической переменной противоположного значения формируется кадровый синхроимпульс, а в случае равенства значений логических переменных во всех (К+1) разрядах этого слова кадровый синхроимпульс не формируется.

Отличительной особенностью устройства-прототипа (3), реализованного в соответствии с указанным способом, является:

возможность его оперативной перенастройки на различные конфигурации маркера;

возможность оперативного изменения допустимого количества ошибок в сигнале кадровой синхронизации при его опознании;

постоянство быстродействия при увеличении элементного состава устройства, вызванного увеличением числа символов маркера кадровой синхронизации.

К недостаткам устройства-прототипа относится то, что решение предложено для случая, когда допустимое количество ошибок в сигнале кадровой синхронизации не превышает двух, что предполагает работу системы кадровой синхронизации при высоких отношениях сигнал/шум, однако в реальных системах отношение сигнал к шуму лежит в пределах 8-10 дБ и ниже, что указывает на низкую помехозащищенность устройства-прототипа выделения маркера системы кадровой синхронизации.

Целью настоящего изобретения является повышение помехозащищенности устройства выделения маркера системы кадровой синхронизации, устойчиво работающем при допустимом количестве ошибок, в два раза большем, чем в устройстве-прототипе.

Для достижения поставленной цели предлагается устройство выделения маркера для системы кадровой синхронизации, содержащее последовательно соединенные К ступеней анализа, в котором ступени анализа со второй по (К-1) выполнены идентично в виде блоков формирования трехразрядных результатов сравнения, при этом выходы двух предыдущих ступеней анализа подключены ко входам одного соответствующего элемента последующей ступени анализа, а к К ступени анализа, выполненной в виде блока конечного анализирующего элемента, подключены выходы блока формирования трехразрядных результатов сравнения (К-1) ступени анализа, при этом первая ступень анализа содержит регистр сдвига, выполненный в виде последовательно соединенных D-триггеров, вход первого и выход последнего из которых является информационным входом и информационным выходом устройства, а каждый D-триггер регистра сдвига имеет вход установки эталонной кодовой комбинации и вход настройки на длину маркера, при этом каждая смежная пара D-триггеров регистра сдвига входит в состав каждого из N блоков промежуточного анализа первой ступени анализа.

Согласно изобретению, в состав каждого из N блоков промежуточного анализа первой ступени анализа введены блоки формирования пятиразрядных результатов сравнения, ко входам каждой из которых подключены трехразрядные выходы каждой пары блоков промежуточного анализа, а в состав каждой из последовательно соединенных со второй по (К-1) ступеней анализа введены блоки формирования двухразрядных результатов сравнения, причем ко входам каждого блока формирования трехразрядных результатов сравнения и каждого блока формирования двухразрядных результатов сравнения второй ступени анализа подключены выходы соответствующей пары блоков формирования пятиразрядных результатов сравнения первой ступени анализа, ко входам каждого блока формирования трехразрядных результатов сравнения и каждого блока формирования двухразрядных результатов сравнения каждой с третьей по (К-1) последующих ступеней анализа подключены выходы соответствующей пары блоков формирования пятиразрядных результатов сравнения предыдущей ступени анализа, а выходы блока формирования пятиразрядных результатов сравнения (К-1) ступени анализа подключены к соответствующим дополнительным входам конечного анализирующего элемента К ступени анализа, вторые входы которого являются входами установки допустимого количества ошибок в сигнале кадровой синхронизации, а выход является выходом кадрового синхроимпульса.

Сочетание отличительных признаков и свойств предлагаемого устройства выделения маркера для системы кадровой синхронизации в литературе не описаны, поэтому оно соответствует критериям новизны и изобретательского уровня.

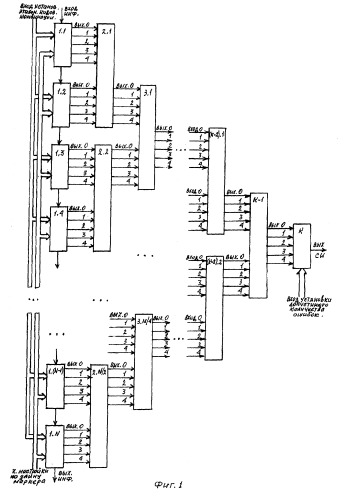

На фиг.1 приведена схема электрическая функциональная предлагаемого устройства выделения маркера кадровой синхронизации.

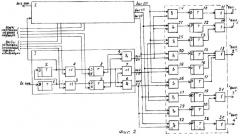

На фиг.2 приведена схема электрическая функциональная элемента первой ступени анализа предлагаемого устройства.

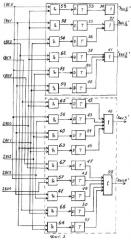

На фиг.3 приведена схема электрическая функциональная элемента второй ступени анализа предлагаемого устройства.

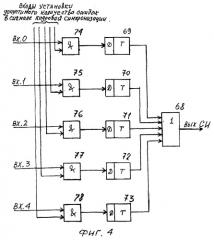

На фиг.4 приведена схема электрическая функциональная элемента конечной ступени анализа предлагаемого устройства.

Предлагаемое устройство выделения маркера кадровой синхронизации (фиг.1) содержит регистр сдвига, выполненный в виде последовательно соединенных четверок D-триггеров, входящих в N элементов первой ступени анализа 1.1, 1.2, 1.3, IN, причем вход регистровой четверки D-триггеров элемента 1.1 является информационным входом устройства, а ее выход является входом регистровой четверки D-триггеров элемента 1.2, выход же регистровой четверки D-триггеров N-го элемента является информационным выходом устройства, каждый из N-элементов первой ступени анализа имеет по четыре входа установки эталонной комбинации маркера, по четыре входа настройки на длину маркера и по пять одноразрядных выходов результатов сравнения символов фрагментов анализируемой входной информационной последовательности и соответствующих символов эталона маркера. Выходы элементов 1.1 и 1.2 первой ступени анализа подключены ко входам элемента 2.1 второй ступени анализа, а выходы элементов 1.3 и 1.4 первой ступени анализа подключены ко входам элемента 2.2 второй ступени анализа. Выходы же элементов 1.(N-1) и 1. N первой ступени анализа подключены ко входам элемента 2. N/2 второй ступени анализа. Каждый из элементов N/2 второй ступени анализа имеет по пять одноразрядных выходов. Выходы элементов 2.1 и 2.2 второй ступени анализа подключены ко входам элемента 3.1 третьей ступени анализа, а выходы элементов 2. N/2-1 и 2N/2 второй ступени анализа подключены к элементу 3 N/4 третьей ступени анализа. Каждый из двух элементов (К-2).1 и (К-2).2 (К-2)-й ступени анализа имеет по десять одноразрядных входов, подключенных к выходам (К-3)-й ступени анализа, и по пять одноразрядных выходов, подключенных ко входам единственного элемента (К-1)-й ступени анализа. Пять одноразрядных выходов элемента К-1 подключены к первым входам конечного анализирующего элемента К, вторые входы которого являются входами установки допустимого количества ошибок в сигнале кадровой синхронизации, а выход является выходом кадрового синхроимпульса.

Все элементы первой ступени анализа выполнены по одной и той же схеме электрической функциональной (фиг.2) и содержат две идентичные схемы I и II блока промежуточного анализа и блок формирования пяти одноразрядных выходов результатов сравнения,

Схема I блока промежуточного анализа содержит четыре D-триггера 1, 2, 5, 8, три элемента исключающее ИЛИ 3, 4, 7 и два элемента И 6 и 9, причем Д вход триггера 1 является информационным входом элемента первой ступени анализа. Выход D-триггера 1 соединен с D входом D-триггера 2 и первым входом элемента исключающее ИЛИ 3, при этом выход D-триггера 2 соединен с D входом D-триггера 1 схемы II блока промежуточного анализа и первым входом элемента исключающее ИЛИ 4. Вторые входы элементов исключающее ИЛИ 3 и 4 являются входами установки эталонной кодовой комбинации - фрагмента маркера кадровой синхронизации. Выход элемента исключающее ИЛИ 3 соединен с D входом D-триггера 5, прямой выход которого подсоединен к первым входам элемента И 6 и третьего элемента исключающее ИЛИ 7. Выход элемента исключающее ИЛИ 4 соединен с D входом D-триггера 8, прямой выход которого подсоединен ко вторым входам элемента И 6 и третьего элемента исключающее ИЛИ 7. R-входы D-триггеров 5 и 8 являются входами настройки на длину маркера. Инверсные выходы D-триггеров 5 и 8 присоединены ко входам второго элемента И 9, выход которого является промежуточным выходом регистрации совпадения двухбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. ОП". Выход первого элемента И 6 является промежуточным выходом регистрации несовпадения обоих бит двухбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 2П". Выход элемента исключающее ИЛИ 7 является промежуточным выходом регистрации несовпадения одного из двух бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 1П".

Блок формирования пяти одноразрядных выходов результатов сравнения содержит девятиканальную схему, каждый канал которой содержит последовательно соединенные элемент И и D-триггер и пять элементов ИЛИ. Выход D-триггера 10 первого канала соединен со входом элемента ИЛИ 11, выход которого является выходом регистрации совпадения четырехбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. О". Выходы D-триггеров 12 и 13 второго и третьего каналов соединены со входами элемента ИЛИ 14, выход которого является выходом регистрации несовпадения одного из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 1". Выходы D-триггеров 15, 16 и 17 четвертого, пятого и шестого каналов соединены со входами элемента ИЛИ 18, выход которого является выходом регистрации несовпадения двух из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 2". Выходы D-триггеров 19 и 20 седьмого и восьмого каналов соединены со входами элемента ИЛИ 21, выход которого является выходом регистрации несовпадения трех из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 3". Выход D-триггера 22 девятого канала соединен со входом элемента ИЛИ 23, выход которого является выходом регистрации несовпадения всех четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "ВЫХ. 4".

Первые входы элементов И 24, 25, и 26 первого, третьего и шестого каналов подключены к "ВЫХ. ОП" схемы II блока промежуточного анализа, а первые входы элементов И 27, 28 и 29 второго, пятого и восьмого каналов подключены к "ВЫХ. 1П" той же схемы II блока промежуточного анализа. Первые входы элементов И 30, 31 и 32 четвертого, седьмого и девятого каналов подключены к "ВЫХ. 2П" той же схемы II блока промежуточного анализа. Вторые входы элементов И 19, 21 и 25 первого, второго и четвертого каналов подключены к "ВЫХ. ОП" схемы I блока промежуточного анализа. Вторые входы элементов И 25, 28 и 31 третьего, пятого и седьмого каналов подключены к "ВЫХ. 1П" той же схемы I блока промежуточного анализа. Вторые входы элементов И 26, 29 и 32 шестого, восьмого и девятого каналов подключены к "ВЫХ. 2П" схемы I блока промежуточного анализа, выход второго D-триггера схемы II блока промежуточного анализа является информационным выходом элемента первой ступени анализа - "ВЫХ. ИНФ.".

Все элементы второй ступени анализа выполнены по одной и той же схеме электрической и функциональной (фиг.3), которая представляет собой блок формирования пяти одноразрядных выходов результатов сравнения.

Блок формирования трех одноразрядных выходов результатов сравнения состоит из шести каналов, каждый из которых содержит последовательно соединенные элемент И и D-триггер, и трех элементов ИЛИ. Выход D-триггера 33 первого канала соединен со входом элемента ИЛИ 34, выход которого является "ВЫХ. 0". Выходы D-триггеров 35, 36 второго и третьего каналов соединены со входами второго элемента ИЛИ 37, выход которого является "ВЫХ. 1". Выходы D-триггеров 38, 39 и 40 четвертого, пятого и шестого каналов соединены со входами третьего элемента ИЛИ 41, выход которого является - "ВЫХ. 2".

Блок формирования двух одноразрядных выходов результатов сравнения состоит из девяти каналов, каждый из которых содержит последовательно соединенные элемент И и Д-триггер, и двух элементов ИЛИ. Выходы Д-триггеров 42, 43, 44 и 45 седьмого, восьмого, девятого и десятого каналов соединены со входами четвертого элемента ИЛИ 46, выход которого является "ВЫХ. 3". Выходы Д-триггеров 47, 48, 49, 50 и 51 одиннадцатого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого каналов подсоединены ко входам пятого элемента ИЛИ 52, выход которого является "ВЫХ. 4".

Вход "1ВХ. 0" первой группы входов подключен к первому входу элементов И 53, 54, 55, 56 и 57 первого, третьего, пятого, восьмого и двенадцатого каналов. Вход "1ВХ. 1" первой группы входов подключен к первому входу элементов И 58, 59, 60 и 61 второго, шестого, девятого и тринадцатого каналов. Вход "1.ВХ. 2" первой группы входов подключен к первому входу элементов И 62, 63 и 64 четвертого, десятого и пятнадцатого каналов. Вход "1.ВХ. 3" первой группы входов подключен к первому входу элементов И 65 и 66 седьмого и четырнадцатого каналов. Вход "1.ВХ. 4" первой группы входов подключен к первому входу элемента И 67 одиннадцатого канала. Вход "2.ВХ. 0" второй группы входов подключен ко второму входу элементов И 53, 58, 62, 65 и 67 первого, второго, четвертого, седьмого и одиннадцатого каналов. Вход "2.ВХ.1" второй группы входов подключен ко второму входу элементов И 54, 59, 63 и 66 третьего, шестого, десятого и четырнадцатого каналов. Вход "2.ВХ. 2" второй группы входов подключен ко второму входу элементов И 55, 60 и 64 пятого, девятого и пятнадцатого каналов. Вход "2.ВХ. 3" второй группы входов подключен ко второму входу элементов И 56 и 61 восьмого и тринадцатого каналов. Вход "2.ВХ. 4" второй группы входов подключен ко второму входу элемента И 57 двенадцатого канала.

Элемент К-й ступени анализа (фиг.4) содержит блок конечного анализирующего элемента, состоящий из пяти каналов, каждый канал которой содержит последовательно соединенные элемент И и Д-триггер и элемент ИЛИ 68, при этом выходы Д-триггеров 69, 70, 71, 72 и 73 подключены ко входам элемента ИЛИ 68, выход которого является выходом регистрации маркера кадровой синхронизации "ВЫХ. СИ". Входы "ВХ. 0", "ВХ. 1", "BX. 2", "ВХ. 3" и "ВХ. 4" подключены к первым входам элементов И 74, 75, 76, 77 и 78 соответственно первого, второго, третьего, четвертого и пятого каналов, вторые входы которых являются входами установки допустимого количества ошибок в сигнале кадровой синхронизации.

Работа устройства рассматривается по схеме электрической функциональной, приведенной на фиг.1.

Рассмотрение работы устройства выделения маркера кадровой синхронизации проведем в следующей последовательности:

- работа элемента первой ступени анализа;

- работа элемента второй ступени анализа;

- работа элемента К-й ступени анализа;

- взаимодействие элементов анализа устройства выделения маркера кадровой синхронизации.

Для рассмотрения работы элемента первой ступени анализа воспользуемся фиг.2.

Элемент первой ступени анализа содержит две идентичные схемы I и II блока промежуточного анализа и блок формирования пяти одноразрядных выходов результатов сравнения.

Работу блока промежуточного анализа рассмотрим на примере схемы I блока промежуточного анализа. На D-вход триггера 1 схемы I блока промежуточного анализа подается информационная последовательность, в результате чего в течение первого такта на первых входах элементов исключающее ИЛИ 3, 4 обеих схем промежуточного анализа фиксируется очередной фрагмент входной последовательности из двух бит. На вторых входах элементов исключающее ИЛИ 3, 4 постоянно присутствуют потенциалы, соответствующие двухбитовому фрагменту эталонной четырехбитовой кодовой комбинации маркера. При одновременном совпадении потенциалов на первых и вторых входах обоих элементов исключающее ИЛИ 3, 4 на инверсных выходах триггеров 5 и 8 будут зафиксированы логические единицы и на выходе элементов И 9 - «Вых. ОП» в течение такта будет удерживаться логическая единица, одновременно с которой на выходах элементов 6, 7 («Вых. 1П», «Вых. 2П») будут логические нули.

При одновременном несовпадении потенциалов на первых и вторых входах элементов ИЛИ 3, 4 на прямых входах триггеров 5 и 8 будут зафиксированы логические единицы и на выходе элемента и на входе элемента И 6 - «Вых. 2П» в течение такта будет удерживаться логическая единица, одновременно с которой на выходах элементов 7, 9 («Вых. 0П», «Вых. 1П») будут логические нули.

При совпадении потенциалов на первых и вторых входах одного из элементов и несовпадении потенциалов на входах другого элемента ИЛИ 3, 4 на входе элемента исключающее ИЛИ 7 - «Вых 1П» в течение такта будет удерживаться логическая единица, одновременно с которой на выходах элементов И 6, 9 («Вых. 0П», «Вых. 2П») будут логические нули. Если на R-вход триггера 5 подан запирающий потенциал, то на выходе элемента И 6 - «Вых. 2П» будет зафиксирован логический ноль и рассматриваемый элемент первой ступени анализа окажется переведенным в режим анализа однобитового фрагмента входной информационной последовательности.

Схема II блока промежуточного анализа работает аналогичным образом.

Блок формирования пяти одноразрядных выходов результатов сравнения работает следующим образом.

При одновременном появлении на выходах обеих схем блока промежуточного анализа «Вых. 0П» логической единицы, на выходе элемента И 24 установится логическая единица, которая поступит на D-вход триггера 10. При этом на выходе элемента ИЛИ 11 («Вых. 0») в течение такта будет удерживаться логическая единица, что будет свидетельствовать о совпадении четырехбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера.

При одновременном появлении на выходах «Вых. 0П» схемы I блока промежуточного анализа и «Вых. 1П» схемы II блока промежуточного анализа логической единицы, на выходе элемента И 25 установится логическая единица, которая поступит на D-вход триггера 13. При этом на выходе элемента ИЛИ 14 («Вых. 1») в течение такта будет удерживаться логическая единица. Точно к тому же результату приведет одновременное появление логической единицы на выходах «Вых. 0П» схемы II блока промежуточного анализа и «Вых. 1П» схемы I блока промежуточного анализа. Это будет свидетельствовать о несовпадении одного из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера.

При одновременном появлении на выходах «Вых. 0П» схемы I блока промежуточного анализа и «Вых. 2П» схемы II блока промежуточного анализа логической единицы, на выходе элемента И 26 установится логическая единица, которая поступит на D-вход триггера 17. При этом на выходе элемента ИЛИ 18 («Вых. 2») в течение такта будет удерживаться логическая единица. Точно к тому же результату приведет одновременное появление логической единицы на выходах «Вых. 0П» схемы II блока промежуточного анализа и «Вых. 2П» схемы I блока промежуточного анализа или на выходах «Вых. 1П» обеих схем блока промежуточного анализа. Это будет свидетельствовать о несовпадении двух из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера.

При одновременном появлении на выходах «Вых. 1П» схемы I блока промежуточного анализа и «Вых. 2П» схемы II блока промежуточного анализа логической единицы, на выходе элемента И 29 установится логическая единица, которая поступит на D-вход триггера 20. При этом на выходе элемента ИЛИ 21 («Вых. 3») в течение такта будет удерживаться логическая единица. Точно к тому же результату приведет одновременное появление логической единицы на выходах «Вых. 1П» схемы II блока промежуточного анализа и «Вых. 2П» схемы I блока промежуточного анализа 1. Это будет свидетельствовать о несовпадении трех из четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера.

При одновременном появлении на выходах обеих схем блока промежуточного анализа «Вых. 2П» логической единицы на выходе элемента И 32 установится логическая единица, которая поступит на D-вход триггера 22. При этом на выходе элемента ИЛИ 23 («Вых. 4») в течение такта будет удерживаться логическая единица, что будет свидетельствовать о несовпадении всех четырех бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера.

Для рассмотрения работы элемента второй ступени анализа воспользуемся фиг.3.

На входы «1 Вх. 0», «1 Вх. 1», «1 Вх. 2», «1 Вх. 3», «1 Bx. 4» поступают сигналы от соответствующих выходов первого элемента первой ступени анализа, на входы «2 Вх. 0», «2 Вх. 1», «2 Вх. 2», «2 Вх. 3», «2 Вх. 4» поступают сигналы от соответствующих выходов второго элемента первой ступени анализа.

При одновременном появлении на входах «1 Вх. 0» и «2 Вх. 0» логической единицы на выходе элемента И 53 установится логическая единица, которая и поступит на D-вход триггера 33. При этом на выходе элемента ИЛИ 34 («Вых. 0») в течение такта будет удерживаться логическая единица, что будет свидетельствовать об отсутствии отличий двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера.

При одновременном появлении на входах «1 Вх. 0» и «2 Вх. 1» логической единицы на выходе элемента И 54 установится логическая единица, которая и поступит на D-вход триггера 36. При этом на выходе элемента ИЛИ 73 («Вых. 1») в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет появление логической единицы на входах «1 Вх. 1» и «2 Вх. 0». Последнее будет свидетельствовать об отличии в одном бите двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера.

При одновременном появлении на входах «1 Вх. 0» и «2 Вх. 2» логической единицы на выходе элемента И 55 установится логическая единица, которая и поступит на D-вход триггера 39. При этом на выходе элемента ИЛИ 41 («Вых. 2») в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет появление логической единицы на входах «1 Вх. 2» и «2 Вх. 0» или «1 Вх. 1» и «2 Вх. 1». Последнее будет свидетельствовать об отличии в двух битах двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера.

При одновременном появлении на входах «1 Вх. 1» и «2 Вх. 2» логической единицы на выходе элемента И 60 установится логическая единица, которая и поступит на D-вход триггера 44. При этом на выходе элемента ИЛИ 46 («Вых. 3») в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет появление логической единицы на входах «1 Вх. 3» и «2 Вх. 0», «1 Вх. 0» и «2 Вх. 3» или «1 Вх. 2» и «2 Вх. 1». Последнее будет свидетельствовать об отличии в двух битах двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера.

При одновременном появлении на входах «1 Вх. 0» и «2 Вх. 4» логической единицы на выходе элемента И 57 установится логическая единица, которая и поступит на D-вход триггера 48. При этом на выходе элемента ИЛИ 52 («Вых. 4») в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет появление логической единицы на входах «1 Вх. 4» и «2 Вх. 0», «1 Вх. 1» и «2 Вх. 3» «1 Вх. 3» «2 Вх. 1» или «1 Вх. 2» и «2 Вх. 2». Последнее будет свидетельствовать об отличии в трех битах двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера.

При одновременном появлении на входах «1 Вх. 1» и «2 Вх. 4» логической единицы, на выходе элемента ИЛИ 34, 37, 41, 46, 52 («Вых 0», «Вых. 1», «Вых 2», «Вых.3», «Вых. 4» в течение такта будут удерживаться логические нули. Точно к такому же результату приведет появление логической единицы на входах «1 Вх. 4» и «2 Вх. 1», «1 Вх. 4» и «2 Вх. 1», «1 Вх. 4» и «2 Вх. 2», «1 Вх. 4» и «2 Вх 3», «1 Вх 4» и «2 Вх. 4», «2 Вх. 4» и «1 Вх. 2».или «2 Вх. 4» и «1 Вх. 3». Последнее будет свидетельствовать о том, что отличия двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера превышают допустимые четыре бита. Если рассматриваемый элемент анализа используется на третьей, ..., К-й ступени анализа, то возможна ситуация, при которой одновременно на все пять входов «1 Вх. 0», «1 Вх. 1», «1 Вх. 2», «1 Вх. 3», «1 Вх. 4» или одновременно на другие пять входов «2 Вх. 0», «2 Вх. 1», «2 Вх. 2», «3 Вх. 3», «2 Вх. 4» поступит логический ноль, в этом случае на выходах элементов ИЛИ 34, 37, 41, 46, 52 ("Вых. 0», "Вых. 1", "Вых. 2", "Вых. 3", "Вых. 4") в течение такта будут удерживаться логические нули. Последнее будет свидетельствовать о том, что отличия двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера превышают допустимые четыре бита. То есть если отличия двух смежных фрагментов эталона маркера меньше или равны четырем битам, на одном из выходов рассматриваемого элемента («Вых. 0», «Вых. 1», «Вых. 2», «Вых. 3», «Вых. 4») будет присутствовать логический ноль.

Для рассмотрения работы элемента К-й ступени анализа воспользуемся фиг.4.

Предположим допустимое количество ошибок в сигнале кадровой синхронизации равно четырем, в этом случае на первые входы элементов И 74, 75, 76, 77, 78 («Вх. 0», «Вх. 1», «Вх. 2», «Вх. 3», «Вх. 4») поступают сигналы от соответствующих выходов элемента (К-1)-й ступени анализа, которые через триггеры 69, 70, 71, 72, 73 попадают на входы элемента ИЛИ 68. При этом если на одном из пяти входов («Вх. 0», «Вх. 1», «Вх. 2», «Вх. 3», «Вх. 4») появится единица, то на выходе элемента ИЛИ 68 в течение такта будет удерживаться логическая единица, которая и будет служить кадровым синхроимпульсом. Если же одновременно на всех пяти входах («Вх. 0», «Вх. 1», «Вх. 2», «Вх. 3», «Вх. 4») будут логические нули, то и на выходе элемента ИЛИ 68 будет логический ноль, что интерпретируется как отсутствие маркера кадровой синхронизации. Предположим допустимое количество ошибок в сигнале кадровой синхронизации равно единице, в этом случае на первые входы элементов И 74, 75, 76, 77 подаются потенциалы, соответствующие логической единице, а на первый вход элемента И 78 подается логический ноль. При этом «Вх. 4» оказывается заблокированным элементом И 78 и кадровый синхроимпульс на выходе элемента ИЛИ 68 появляется только в случае появления логической единицы на одном из входов «Вх. 0», «Вх. 1», «Вх. 2», «Вх. 3». Если мы хотим формировать кадровый синхроимпульс лишь в случае обнаружения безошибочной комбинации маркера кадровой синхронизации, то на первые входы элементов И 75, 76, 77, 78 необходимо подать потенциалы, соответствующие логическому нулю, а на первый вход элемента И 74 - логическую единицу. При этом элементы И 75, 76, 77, 78 заблокируют входы «Вх. 1», «Вх. 2», «Вх. 3», «Вх. 4» и кадровый синхроимпульс на выходе элемента ИЛИ 68 будет регистрироваться лишь при появлении логической единицы на входе «Вх. 0».

Для рассмотрения элементов анализа устройства выделения маркера кадровой синхронизации воспользуемся фиг.1.

Предположим, что анализируемый фрагмент информационного потока, находящийся в регистре, входящем в элементы первой ступени анализа 1.1, ..., 1.N, отличается от эталона маркера лишь в последнем и пятом от конца фрагмента битах. В этом случае у элементов 1.1 и 1.2 логическая единица будет присутствовать на выходах «Вых. 1», а у элементов 1.3, ..., 1.N логические единицы появятся на выходах «Вых. 0», все остальные выходы элементов первой ступени анализа содержат логические нули. Такому состоянию выходов элементов первой ступени анализа будет соответствовать появление логической единицы на выходе «Вых. 2» элемента 2.1 и логических единиц на выходах «Вых. 0» элементов 2.2, ..., 2.N/2, при логических нулях на всех остальных выходах элементов второй ступени анализа. При этом на выходе «Вых. 2» элемента 3.1 появится логическая единица, у элементов 3.2, ..., 3.N/4 логические единицы будут на выходах «Вых. 0», а на всех остальных выходах третьей ступени анализа будут присутствовать логические нули. Такое состояние выходов третьей ступени анализа приведет к тому, что у элемента (К-2).1 логическая единица появится на выходе «Вых. 2», а у элемента (К-2).2 логическая единица будет на выходе «Вых. 0» при логических нулях на всех остальных выходах (К-2)-й ступени анализа. При этом у элемента (К-1)-й ступени анализа логическая единица появится на выходе «Вых. 2» и логические нули на выходах «Вых. 0», «Вых. 1». Если задаваемое входами установки допустимое количество ошибок в сигнале кадровой синхронизации равно двум, то при описанном состоянии выходов устройства на выходе К-го элемента появится кадровый синхроимпульс, если же допустимое количество ошибок в сигнале кадровой синхронизации равно нулю или единице, то кадровый синхроимпульс на выходе К-го элемента не появится.

Предположим, что анализируемый фрагмент информационного потока, находящийся в регистре, входящем в элементы первой ступени анализа 1.1, ..., 1.N, отличается от эталона маркера лишь последними пятью от конца фрагментами битов. В этом случае у элемента 1.1 логическая единица будет присутствовать на выходе «Вых. 2», у элемента 1.2 логическая единица будет на выходе «Вых. 1», у элементов 1.3, ..., 1.N логические единицы появятся на выходах «Вых. 0», а все остальные выходы элементов первой ступени анализа содержат логические нули. Такому состоянию выходов элементов первой ступени анализа будет соответствовать отсутствие единиц на всех пяти выходах («Вых. 0», «Вых. 1», «Вых. 2», «Вых. 3», «Вых. 4») элемента 2.1, что приведет к появлению логических нулей на всех выходах элементов 3.1, ..., (K-2).1, (K-1), и как следствие этого к логическому нулю на выходе К-го элемента, т.е. кадровый синхроимпульс будет отсутствовать.

Для повышения быстродействия устройства в каждый элемент анализа включены Д-триггеры, которые осуществляют привязку к тактовой частоте сигнала. При таком построении устройства его совокупное быстродействие не зависит от количества входящих в него элементов анализа. Однако при этом следует иметь в виду, что момент фиксации анализируемого фрагмента информационной последовательности в регистре сдвига первой ступени анализа отделен от момента завершения анализа этого фрагмента К тактами.

Результаты испытания макета, реализованного на современной высокоинтегрированной и высокоскоростной базе с использованием перепрограммируемых логических интегральных схем (ПЛИС), подтвердили его высокую помехоустойчивость, обеспечивающую возможность выделения маркера кадровой синхронизации при отношении сигнал к шуму не менее 7 дБ в информационной последовательности, передаваемой со скоростью 120 Мбит/с.

Литература

1. Способ выделения маркера кадровой синхронизации и устройство для его осуществления. АС №1821931, Россия, МКИ Н04L 7/4, заявка №4754998/09, заявл. 30.10.1989; Н.Е.Патонов, А.Н.Дядюнов, А.Н.Дятлов, А.Н.Кантор, М.Л.Платонова.

2. Способ выделения маркера кадровой синхронизации и устройство для его осуществления. АС №1821932, Россия, МКИ H04L 7/4, заявка №4755121/09, заявл. 30.10.1989; Н.Е.Патонов, Ю.Р.Салихов, А.Н., А.Н.Дядюнов, А.Н.Дятлов, А.Н.Кантор.

3. Способ выделения маркера кадровой синхронизации и устройство для его осуществления. Патент №2158483, Россия.

Устройство выделения маркера для системы кадровой синхронизации, содержащее последовательно соединенные К ступеней анализа, в котором ступени анализа со второй по (К-1) выполнены идентично в виде блоков формирования трехразрядных результатов сравнения, при этом выходы двух предыдущих ступеней анализа подключены ко входам одного соответствующего элемента последующей ступени анализа, а к К ступени анализа, выполненной в виде блока конечного анализирующего элемента, подключены выходы блока формирования трехразрядных результатов сравнения (К-1) ступени анализа, при этом первая ступень анализа содержит регистр сдвига, выполненный в виде последовательно соединенных D-триггеров, вход первого D-триггера и выход последнего является информационным входом и информационным выходом устройства, а каждый D-триггер регистра сдвига имеет вход установки эталонной кодовой комбинации и вход настройки на длину маркера, при этом каждая смежная пара Д-триггеров регистра сдвига входит в состав каждого из N блоков промежуточного анализа первой ступени анализа, отличающееся тем, что в состав каждого из N блоков промежуточного анализа первой ступени анализа введены блоки формирования пятиразрядных результатов сравнения, ко входам каждой из которых подключены трехразрядные выходы каждой пары блоков промежуточного анализа, а в состав каждой из последо