Модуль генерации схем для декодирования сверточных кодов и схема декодирования

Иллюстрации

Показать всеИзобретение относится к модулю генерации интегральных схем декодирования для использования, в частности, в турбоустройствах и для генерации схем сверточного кодирования. Модуль является параметрическим и, благодаря этому, делает возможным генерировать схемы декодирования, имеющие различные рабочие характеристики, которые могут быть использованы в турбоустройствах, применяющих различные режимы декодирования и различные архитектуры. Кроме того, модуль обеспечивает генерацию схем декодирования, отличительным признаком которых является то, что они могут селективно управлять множеством генераторных полиномов и, таким образом, могут быть использованы в асимметричных турбоустройствах. Технический результат - обеспечение генерации схем декодирования с различными рабочими характеристиками с использованием различных режимов декодирования и различных технологий. 2 н. и 6 з.п. ф-лы, 7 ил, 1 табл.

Реферат

Изобретение относится к модулю генератора для схем связи, способных декодировать сверточные коды, способу генерации схем этого типа и связанной с ним схеме.

Более конкретно, настоящее изобретение относится к модулю генерации интегральных схем декодирования для использования в устройствах декодирования каскадных сверточных кодов (турбокодов), к способу определения характеристик схемы этого типа и к схеме декодирования, которая может быть получена с этим модулем.

Интегральные схемы могут быть спроектированы с использованием языков описания высокого уровня, такого как ЯОАСБИС (язык описания аппаратных средств сверхбыстродействующих ИС).

Посредством этого метода проектирования и использования соответствующих кремниевых компиляторов можно получить интегральный компонент, имеющий характеристики, определенные с использованием языка высокого уровня, например, описания ЯОАСБИС.

Известно, что описания ЯОАСБИС заранее определенных функций, таких как те, которые относятся к схеме декодирования, могут составлять библиотеки модулей, упоминаемые как интеллектуальная собственность (ИСб), или библиотеки интеллектуальной собственности, посредством чего могут быть сконструированы очень сложные электронные устройства, такие как системы на кристалле (СНК).

Отличительным признаком модулей, принадлежащих библиотеке интеллектуальной собственности, (модулей ИСб или модулей) является то, что они могут быть использованы при проектировании многочисленных электронных устройств, благодаря тому факту, что их параметры интерфейса с другими модулями или электронными схемами могут «специализироваться» перед кремниевой компиляцией, присвоением конкретных величин переменным или параметрам, определенным на стадии проектирования.

В соответствии с настоящим изобретением ссылка делается на модуль ИСб для связи и соответствующие схемы декодирования, которые могут быть использованы в устройствах декодирования каскадных сверточных кодов (турбодекодирование).

В отношении передачи цифровой информации (данных) известно, что ошибки, вводимые при передаче данных по каналу, делают необходимым кодирование упомянутых данных посредством добавления избыточных битов перед передачей и их декодирование после их приема посредством исключения избыточных битов. По существу, благодаря присутствию избыточных битов, кодирование и декодирование делают возможным восстановление исходных данных со степенью достоверности или вероятности, которая учитывает ошибки, вводимые рассматриваемым каналом передачи.

Многочисленные известные методы могут быть использованы для кодирования и декодирования данных.

В настоящем изобретении рассматривается метод сверточного кодирования и декодирования, и, в частности, каскадного типа, турбокодирование и турбодекодирование.

Как известно, устройство сверточного кодирования способно при кодировании данных использовать заранее определенные алгоритмы для учета информации, которая предшествует кодированию, т.е. априорной информации. Также известно, что степень, с которой кодирование надежно, или другими словами, степень, с которой оно гарантирует, что данные будут правильно восстановлены, прямо пропорциональна количеству априорной информации, которое учитывает алгоритм кодирования. Конечно, сложность алгоритма, используемого при кодировании и декодировании, повышается вместе с количеством априорной информации, которую оно рассматривает.

Для того чтобы улучшить результаты, которые могут быть достигнуты при декодировании, и уменьшить сложность схем и устройств кодирования и декодирования, необходимых для любого данного уровня рабочих характеристик, были введены так называемые устройства турбокодирования и турбодекодирования.

Турбоустройства, используемые для кодирования или декодирования, содержат множество сверточных схем, соединенных между собой каскадным образом при помощи одной или нескольких схем (известных как схемы перемежителя), способных задерживать или изменять порядок битов.

В общих чертах, архитектура устройств турбокодирования (турбокодеров), таким образом, включает в себя использование множества схем сверточного кодирования, соединенных между собой с использованием последовательного или параллельного расположения так, что кодирование выполняется параллельно или последовательно.

Например, схема 10 сверточного кодирования (схема кодирования) (фиг.1) для турбокодеров включает в себя вход (u) данных и два выхода, один для данных (u) входа, в этом случае схема упоминается как систематическая, и один для информации кодирования (кода) (с).

Кроме того, схема включает в себя регистр 12 сдвига, имеющий разрядность в несколько битов (ν-1), которая в этом примере составляет три бита, т.е. бит 21, бит 22 и бит 23 соответственно. Этот регистр сдвига способен принимать данные (u) на входе и выводть код (с) в соответствии с типом межсоединений, используемых в схеме 10 кодирования.

Основными параметрами, которые характеризуют схему 10 кодирования, являются следующие:

- k обозначает число битов, введенных в последовательность в единицу времени. В примере и как обычно используется кодирование с k=1,

- k·(ν-1) обозначает емкость регистра 12 сдвига, используемого для кодирования,

- n обозначает количество битов, выводимых кодером.

В общих чертах, кодер принимает k битов в момент времени, которые вводятся в регистр 12 сдвига, характеризующийся k*(ν-1) позициями; на выходе кодера будет n выходных битов для каждого k входного бита (n≥k). Каждый выходной бит вычисляется в результате двоичного сложения или сложения по модулю 2 некоторого количества битов в регистре 12 сдвига; как и следовало ожидать, эта сумма зависит от логики межсоединений кодера и устанавливает так называемые генераторные полиномы, которые подробно описываются ниже. Например, величина u входного бита добавляется к величине бита, полученного через соединение (путь) обратной связи. Полученная таким образом величина затем добавляется к величине первого бита 21 регистра 12 сдвига и результат добавляется к величине третьего бита 23 регистра 12 сдвига; на пути обратной связи, кроме того, третий бит 23 и второй бит 22 регистра 12 сдвига добавляются к входному биту.

Как известно, схемы 10 кодирования упоминаются как рекурсивные в тех случаях, когда присутствуют соединения обратной связи.

Таким образом, каждый кодированный бит (с) зависит не только от k битов, принимаемых в любой данный момент, но также от k* битов (ν-1), принятых ранее.

В соответствии с известным уровнем техники термин «кодовое слово» используется для обозначения множества n битов, подаваемых на выход кодера. В примере имеется два кодовых слова, т.е. данные, представленные на входе (u), и связанный с ними код (с). Величина k/n называется «скоростью кода».

В общих чертах рабочие характеристики схем кодирования определяются на основе указанных выше параметров. В частности, эти характеристики включают в себя:

ν - длина кодового ограничения схемы кодирования или кода, которая, конечно, зависит от длины регистра сдвига,

Nst - число состояний, соответствующее величине 2k(ν-1) и которое соответствует числу возможных двоичных комбинаций в регистре сдвига,

gc - генераторный полином для с, который определяет межсоединения для генерации кода с, и

gf - генераторный полином для fm, который определяет межсоединения для генерации информации f об обратной связи.

Как известно, генераторный полином однозначно идентифицируется двоичным словом, состоящим из ν битов. Каждый бит двоичного слова соответствует позиции входных данных или регистра сдвига, и по соглашению, если величина бита составляет 1 в генераторном полиноме, входные данные или данные, хранимые в регистре сдвига в соответствующей позиции, участвуют при вычислении кода обратной связи или выходного кода. Если величина бита составляет 0, то он не участвует.

В примере, показанном на фиг.1, ν равно 4 битам, полином gc, что очевидно для специалистов этой области техники, равен 1101 (13 в десятичной форме), тогда как полином gf равен 1011 (11 в десятичной форме).

Кодирование описывается, в основном, так называемой решетчатой диаграммой.

Для схемы кодирования на фиг.1, например, на фиг.2 представлена соответствующая решетчатая диаграмма 20, где все возможные изменения во времени в схеме кодирования для различных входных величин u и состояния схемы выражены графически с использованием линий, называемых ребрами. На ребрах решетчатой диаграммы 20 также показаны выходные данные, т.е. u и с, соответственно.

Вышеописанные соображения в отношении рабочих характеристик схем кодирования для турбоустройств также применимы к характеристикам схем декодирования для турбоустройств (турбодекодеров) в связи с тем, что, как очевидно для специалиста в этой области техники, схемы декодирования должны иметь характеристики, которые эквиваленты характеристикам схем кодирования, если они должны быть способны правильно декодировать кодированную информацию.

Конечно, входная информация для схем декодирования состоит из битов для оценки (u) систематической информации и битов для оценки (с) избыточной информации, получаемых в соответствии с известным уровнем техники на выходе канала передачи, следуя за операцией демодуляции.

Тип кодирования, используемый турбоустройствами, например параллельный или последовательный, является еще одним параметром, который необходимо учитывать при реализации как турбодекодеров, так и схем декодирования, которые их содержат.

Техническим недостатком систем известного уровня техники при проектировании турбодекодеров является то, что нет доступных модулей ИСб схем декодирования, которые могут быть использованы независимо от изменений в характеристиках.

В частности, известные модули ИСб для генерации схем декодирования сверточных кодов ограничены рабочими характеристиками, и поэтому существует, таким образом, однозначное соответствие между модулями ИСб и схемами декодирования, имеющими данное множество рабочих характеристик.

Другой недостаток систем известного уровня техники заключается в том, что нет доступных модулей ИСб схем декодирования, которые могут быть использованы независимо от изменений в режиме кодирования.

Как и следовало ожидать, это означает, что модули ИСб схем декодирования, которые могут быть использованы в турбодекодерах, различаются в соответствии с рассматриваемым режимом турбокодирования.

Кроме того, известные модули ИСб схем декодирования ограничены использованием определенных способов и технологий.

По существу, известные модули ИСб схем декодирования не являются параметрическими в отношении рабочих характеристик архитектуры и декодера и из-за этого ограничения делают необходимым производить выбор при проектировании на ранней стадии технологического процесса. Если, напротив, эти модули были бы параметрическими и гибкими, то эти выборы могли бы быть сделаны на более поздних стадиях. Это обеспечило бы явные преимущества, особенно в случаях, когда становится необходимым изменить характеристики используемых алгоритмов или архитектуру.

Еще одним техническим недостатком, который конкретно оказывает влияние на схемы декодирования, реализованные на кремнии или использующие программируемую логику, является то, что, если они реализованы, то эти схемы могут использовать только один генераторный полином, или, другими словами, только один тип функции декодирования для восстановления исходных данных.

Это очень важное ограничение систем известного уровня техники, особенно в случае турбоустройств, в которых используется последовательное декодирование.

При декодировании в последовательном режиме, как известно, вторая схема или каскад декодирования занят декодированием в другие моменты времени, чем первая схема или каскад, в связи с тем, что информация первого каскада должна использоваться для декодирования. Таким образом, в принципе можно использовать одну схему декодирования в турбодекодерах, в которой используются последовательные принципы декодирования.

В системах известного уровня техники, однако, использование одной схемы декодирования возможно только тогда, когда каскады декодирования турбодекодера используют одну пару генераторных полиномов.

В тех случаях, когда два или несколько каскадов декодирования используют различные генераторные полиномы, то это ограничение означает, что последовательные турбодекодеры должны включать в себя соответствующее число схем декодирования, что, безусловно, повышает сложность устройства и связанные с ними затраты на опытно-конструкторские работы в связи с тем, что каждая индивидуальная схема декодирования, в основном, содержит большое количество эквивалентных логических элементов, например около 150000.

Конечно, это ограничение было бы преодолено, если бы существовали схемы декодера для турбоустройств, которые могли бы управлять множеством генераторных полиномов.

Задачей настоящего изобретения является создание модуля ИСб генерации схем декодирования, который отличается различными рабочими характеристиками, которые могут быть применены в устройствах декодирования, использующих различные режимы декодирования и различные технологии.

Другой задачей настоящего изобретения является способ генерации модулей декодирования с указанными выше характеристиками.

Еще одной задачей настоящего изобретения является схема декодирования для турбоустройств, способная селективно управлять множеством генераторных полиномов.

В соответствии с этими задачами в настоящем изобретении предложены модуль генератора для схем декодирования, раскрытый в п.1 формулы изобретения, способ генерации таких схем, раскрытый в п.7 формулы изобретения, и схема сверточного декодирования, раскрытая в п.9 формулы изобретения, которые представлены ниже.

Вышеупомянутые и другие признаки настоящего изобретения будут более понятны из следующего описания предпочтительного варианта осуществления изобретения, которое приводится исключительно в качестве примера и не должно рассматриваться как ограничивающее, и сопровождающих чертежей, на которых:

на фиг.1 представлена логическая блок-схема систематической и рекурсивной схемы сверточного кодирования;

на фиг.2 представлена решетчатая диаграмма для схемы, изображенной на фиг.1;

на фиг.3 представлена схема последовательности операций для генерации модуля и схемы в соответствии с изобретением;

на фиг.4 представлена общая схема ввода и вывода для модуля в соответствии с изобретением;

на фиг.5 представлена общая архитектура модуля и схемы, которые могут быть получены при помощи схемы последовательности операций, показанной на фиг.3;

на фиг.6 представлена архитектура элемента памяти для модуля и схемы, показанных на фиг.5, и

на фиг.7 представлена архитектура характерного вычислительного элемента для модуля и схемы, показанных на фиг.5.

Предпочтительный вариант осуществления изобретения описывается со ссылкой на фиг.3, на которой представлена схема последовательности операций для проектирования модуля генератора для схем декодирования сверточного кода в соответствии с настоящим изобретением.

На первом этапе, обозначенном позицией 100, определяется общее техническое задание на схему декодирования. В частности, различные способы кодирования исследуются вместе с возможными архитектурами для соответствующих схем декодирования.

Принимая сверточное кодирование для турбокодеров в качестве эталона, одним из первых ограничений для турбодекодеров и схем, которые их содержат, является то, что операции декодирования сверточных кодов должны повторяться некоторое число раз, кратное числу схем сверточного кодирования, содержащихся в турбокодере.

Это означает, что выход одной схемы декодера является входом другой такой схемы. Это, в свою очередь, означает, что необходимо использовать схемы декодера с мягким входом и мягким выходом (МВМВ), которые, как известно, делают возможным продолжать повторение циклов декодирования до того момента, пока не будет достигнута степень надежности, требуемая по техническому заданию.

Следовательно, на основе характеристик кодирования первым требованием технического задания на модули генератора схем декодирования в соответствии с настоящим изобретением является то, что эти модули должны генерировать схемы МВМВ, в которых входная и выходная информация состоит из вероятностных оценок передаваемой информации.

Конечно, тот факт, что должны быть реализованы модули для генерации схем МВМВ, приводит ко второму ограничению, т.е. что декодирование должно использовать алгоритм типа МВМВ, такой как алгоритм, предложенный Бенедетто (Benedetto), Дивсларом (Divslar), Монторси (Montorsi) и Поллара (Pollara) в документе «Soft-Input Soft-Output modules for the construction and distributed iterative decoding of code networks», Department of Electronics, Politecnico di Torino, November 1996.

Алгоритм 1] и 2] известного типа ссылается на ребра решетчатой диаграммы, а не на пары состояний и, таким образом, является совершенно обычным. Следовательно, он может работать с кодами, которые необязательно являются двоичными, и с решетками с многочисленными переходами. Однако алгоритм 1] и 2] имеет главный недостаток в том, что он является предметом строгого ограничения реализации, которое требует его ожидания окончания передачи данных перед тем, как может начаться декодирование.

В соответствии с целями настоящего изобретения было предпочтительным использовать так называемый аддитивный алгоритм МВМВ (аддитивный алгоритм скользящего окна), аналогично, известного типа.

Этот алгоритм, который выводится из исходного алгоритма МВМВ 1] и 2], делает возможным работу с постоянным количеством хранимых данных (который, таким образом, не зависит от продолжительности передачи) и возврат распределений вероятности, уточненных фиксированной задержкой D, называемой временем ожидания, на выходе.

Аддитивный вариант алгоритма был выбран потому, что он выполняет операцию сложения, а не умножения при вычислении и, таким образом, на него не оказывают влияние известные трудности, вызываемые выполнением операций умножения на аппаратном уровне. Окончательная версия алгоритма выглядит следующим образом:

Дано:

где α и β, известные как метрика ветвей, представляют весовые коэффициенты предыдущих и последующих битов при определении вероятности данного бита в момент времени t.

Алгоритм вычисления вероятности выхода становится:

| [3] | |

| [4] |

где:

k=1,...,n

k=k,...,k-D,

где:

- буквы курсивом верхнего регистра (например U, C, S, E) обозначают случайные переменные;

- буквы курсивом нижнего регистра (например u, c, s, e) обозначают индивидуальное вхождение случайных переменных, указанных выше;

- буквы верхнего регистра P(A) обозначают вероятность события А;

- нижний индекс k обозначает дискретный момент времени, определенный во множестве моментов времени К;

- буква курсивом нижнего регистра с нижним индексом и верхним индексом (uk1k2) обозначает временную последовательность переменной от момента времени k1 до момента времени k2;

- буквы нижнего регистра, набранные жирным шрифтом, (u, c, s, e) обозначает полные последовательности связанных случайных переменных;

- круглые скобки «( )» обозначают временную последовательность; и

- фигурные скобки «{ }» обозначают конечное множество элементов.

Что касается решетчатой диаграммы, с другой стороны, используется следующая система обозначений:

- обобщенное ребро представлено переменной е;

- начальное состояние - SS(e);

- конечное состояние - SE(e);

- входной символ - u(e);

- выходной символ - c(e).

Ничего не изменяется в отношении инициализации вероятности или альфа-метрики; бета-метрики, с другой стороны, инициализируются как равные и постоянные для всех состояний, так как итерация должна начинаться с неизвестного состояния.

Проблема сложности обработки, таким образом, сместилась с проблемы необходимости выполнения операций умножения на проблему вычисления логарифма экспоненциальной суммы, которая может быть аппроксимирована зависимостью:

Как известно, это упрощение приводит к ухудшению характеристик, если имеется высокое отношение сигнал-шум. Следовательно, если необходимо достичь высоких характеристик, может быть применен следующий рекурсивный алгоритм, который обеспечивает точное решение в выражении 5] ниже:

a(1)=a1

[5]

l=2,...,L

a≡a(L),

где выполняются две операции для оценки (а) алгоритмом 5]: нахождение максимума двух чисел, которое очень простое для осуществления, и вычисление log[1+exp(-|Δ|)].

Конечно, выполнение этой второй операции в 5] может быть осуществлено при помощи таблицы преобразования.

Вариант алгоритма, который не содержит этот признак и где максимальная величина аппроксимирована, называется MAX_log_MAP, тогда как вариант, в котором применяется поправочный коэффициент, называется log_MAP. Во всех случаях общеизвестны как алгоритмы, так и аппроксимации реализации.

Таким образом, вторым требованием технического задания на модули генератора схем декодера в соответствии с настоящим изобретением является то, что должен быть определен алгоритм декодирования для реализации в связанной схеме.

Другое требование технического задания, подлежащее определению в начале генерации модуля в соответствии с настоящим изобретением, заключается в определении одной из возможных архитектур для модуля.

Анализ, выполняемый на этапе 100 определения технического задания, указывает, что возможные архитектуры, которые реализуют алгоритм МВМВ, могут быть разделены на два семейства: архитектуры с памятью и конвейерные архитектуры типа параллельного регистра.

Первые, как известно, безусловно являются наилучшим выбором, если нет ограничений на быстродействие, так как они требуют значительно меньших ресурсов.

Если наиболее строгими ограничениями являются ограничения на быстродействие, то единственным путем достижения высоких частот декодирования является использование архитектур типа параллельного регистра, использующих конвейерные методы. Очевидно, что выбор архитектуры, подлежащей реализации, зависит в значительной степени от применения, для которого предназначен модуль.

Для того чтобы учесть наиболее строгие ограничения, как было обнаружено, желательно применять решение с конвейерной архитектурой типа параллельного регистра в качестве третьего требования технического задания.

В любом случае, что очевидно из описания настоящего варианта осуществления изобретения, части модуля генерации схем декодирования сверточного кода в соответствии с настоящим изобретением также могут быть использованы для реализации модели, способной генерировать схемы декодирования, имеющие архитектуру с памятью.

После завершения этапа 100 в соответствии с настоящим изобретением определяется техническое задание, которое необходимо для определения типов схемы, подлежащей генерации (например МВМВ), алгоритма, подлежащего реализации (например аддитивного алгоритма скользящего окна), и общей архитектуры (например параллельной конвейерной архитектуры).

На втором этапе, который обозначен позицией 200, определяются степень программируемости и внутренняя архитектура модуля декодирования или модуля 50 ИСб и соответствующие схемы.

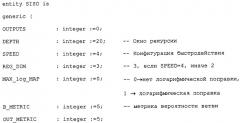

На фиг.4 показаны интерфейсные сигналы модуля 50 ИСб и их значение, подчеркивающее схемные характеристики, происходящие из их использования. Эти характеристики тесно связаны с параметрами модуля, которые являются эффективным инструментом для реализации схем, предназначенных для охвата широкого диапазона применений.

В соответствии с этим примером предпочтительного варианта выполнения входные данные МВМВ (INPUT0-3) представляют собой четыре вероятности слов, соответствующие возможным комбинациям двух битов, т.е. метрики ветви, которые составляют сигнал, принимаемый из канала.

Следовательно, предполагается, что существует модуль и соответствующая схема, внешняя для модуля 50 ИСб, которая способна определять вероятности слов, начинающиеся с отношения правдоподобия, принимаемого с выхода демодулятора.

Выход, с другой стороны, состоит из вычисленных вероятностей вместе с оценками информационного бита (u) и бита (с) избыточности.

Входные/выходные данные реализуются в модуле 50 ИСб в параметрической форме в том смысле, что они могут быть уточнены перед кремниевой компиляцией и обозначены как B_METRIC и OUT_METRIC, соответственно, для входа и выхода.

Благодаря этим параметрам можно установить ряд битов, используемых для представления величин входных и выходных данных, INPUT 0-3 и Output_u, Output_c соответственно.

Для проверки достоверности входных данных протокол характеризуется активным высоким сигналом DVALID_I.

Модуль 50 ИСб также предусмотрен с сигналами START_FRAME_I и END_FRAME_I, которые способны синхронизировать модуль посредством идентификации первого и последнего бита пакета данных. Этот метод гарантирует работу модуля без необходимости включения в параметры длины передаваемого пакета данных. Информация, касающаяся начала и окончания каждого пакета, в любом случае является важной, так как алгоритм скользящего окна включает в себя различную инициализацию для метрик на начальном этапе, этапе работы и этапе завершения.

На выходе имеется сигнал (DVALID_O) проверки достоверности данных и сигналы идентификации для первых и последних битов в пакете (START_FRAME_O и END_FRAME_O), которые необходимы для модуля 50 МВМВ при последующей итерации.

Сигнал, обозначенный EXP, делает возможным представить метрики экспоненциальной системой обозначения, где экспонента, однако, фиксированна для всех метрик в пакете. Этот метод, на самом деле, часто используется при проектировании турбодекодеров. Фактически критическим аспектом этих вопросов является то, как они обрабатывают метрики, которые имеют тенденцию к увеличению и приводят вычисленные величины к переполнению. Для того чтобы предотвратить это, часто используемым средством является деление всех метрик, с уменьшением их мантиссы и сохранением информации для работы, которая была выполнена в результате использования общей экспоненты. Эта информация нужна тогда, когда реализуется алгоритм с логарифмической поправкой, так как на поправочный коэффициент оказывает влияние величина экспоненты. Это позволяет исключить проблему переполнения метрик без перегрузки вычислений, которые необходимо было бы выполнить, если бы каждая единственная метрика была представлена экспонентой.

Модуль 50 также предусмотрен с управляющим сигналом GEN_CTRL, который позволяет выбрать из четырех различных конфигураций (которые могут быть установлены в параметрах) для генераторных полиномов кода, и, таким образом, генерировать схемы, способные управлять вплоть до четырех пар различных полиномов.

В частности, благодаря управляющему сигналу GEN_CTRL, можно создать схемы, которые могут управлять вплоть до четырех пар различных полиномов.

Так как схема декодирования очень сложная, способность применения ее в качестве совместно используемого ресурса является важным признаком дополнительных возможностей.

В противоположность известному уровню техники, где возможность реализации декодеров для каскадных сверточных кодов, использующих единственную схему МВМВ, ограничена случаем симметричных передач, при которых не изменяется генераторные полиномы блоков каскадного кода, модуль 50 в соответствии с настоящим изобретением делает возможным генерировать схемы МВМВ, которые оптимизируют использование ресурса и осуществляют два этапа декодирования, используя единственную схему, которая подробно описывается ниже.

Способность передавать данные с различными генераторными полиномами, на самом деле, позволяет снять ограничения систем известного уровня техники и гарантировать, что даже асимметричные передачи могут управляться одной схемой МВМВ.

Параметризация модуля 50 возникает в результате попыток, выполняемых с целью получения схем, которые способны работать в различных применениях.

Достижение этой рассматриваемой цели, не только определяющей параметры для входных/выходных данных, но также использующей параметры конфигурации, внутренние для модуля 50, которые, аналогично параметрам входа/выхода, также могут быть специализированы во время кремниевой компиляции и синтеза.

Как будет подробно описано ниже, эти параметры конфигурации внутреннего модуля оцениваются до синтеза и гарантируют, что различные схемы могут быть сгенерированы, начиная с одного описания.

Следующее описание делает ссылку на табл.1, в которой показаны все параметры модуля 50, который может быть специализирован, и который включает в себя:

1 - параметры кодирования,

2 - параметры декодирования,

3 - параметры интерфейса,

4 - параметры архитектуры.

Параметры кодирования характеризуют передаваемый код. Число состояний кодирования устанавливается параметром N_STATES, который соответствует величине 2k(ν-1).

Этот параметр имеет большое влияние на внутреннюю структуру, так как он играет лидирующую роль при определении фактических ресурсов, которые используются в модуле.

Если было установлено число состояний, и приняв k=1, единственными параметрами, посредством которых может быть однозначно определена решетчатая диаграмма 20 (фиг.2), представляющая выполняемое кодирование, являются генераторные полиномы gc и gf. Эти параметры отличаются от всех других параметров, поскольку они включают в себя состояние, предшествующее компиляции кода. Они, фактически, обрабатываются в результате процедуры, которая имеет место перед компиляцией и приводит к пакету, в котором хранятся векторы характеризации решетки. Так как можно управлять вплоть до четырех пар различных полиномов, используются восемь различных параметров.

Параметры декодирования характеризуют декодирование и, как таковые, включают в себя только декодер независимо от типа выполняемого кодирования.

Параметры, обозначенные как DEPTH и MAX_log_MAP, характеризуют выбранный алгоритм, тогда как на OUTPUTS оказывает влияние тип архитектуры, выбранной для декодера в целом, и подробно описаны ниже.

- Выбор DEPTH устанавливает ширину окна, в котором происходят итерации. Влияние, которое этот параметр имеет на структуру схемы МВМВ, главным образом видно в блоке хранения метрик; как следует ожидать, фактически, число элементов данных, подлежащих хранению, увеличивается вместе с шириной этого окна,

- MAX_log_MAP выбирает реализуемый блок, позволяя определить, пренебрегается ли поправочный коэффициент или нет, и

- OUTPUTS представляет собой параметр, который оптимизирует площадь, занимаемую схемой, согласно техническому заданию на модуль МВМВ, в связи с тем, что некоторым конфигурациям турбодекодера не требуется оба выхода, генерируемые схемой МВМВ. В таких случаях можно выбрать соответствующий выход и таким образом исключить использование логических ресурсов, которые генерируют величину, которая не представляет интереса.

Параметры интерфейса, которые уже были описаны в связи с входными/выходными сигналами, включены в представление входных и выходных параметров модуля МВМВ.

Их присутствие необходимо по двум причинам: первая связана с качеством декодирования, так как эти величины определяют внутреннюю арифметику и, следовательно, качество результатов. Вторая причина связана с необходимостью гарантирования того, что как модуль, так и его интерфейс необходимы и, таким образом, обеспечивают то, что модуль может быть без затруднения введен в сложные системы.

В частности, параметр B_METRIC (фиг.4) представляет количество битов, используемых при представлении входных вероятностей, тогда как OUT_METRIC представляет собой отсечку, выполняемую на выходе.

Параметры архитектуры имеют прямое влияние на внутреннюю структуру для любого данного типа декодирования, так как они изменяют свои характеристики в смысле быстродействия и занимаемой площади.

Важность, которую это имеет, связана с конкретным рассматриваемым применением.

Некоторые системы могут не накладывать определенные требования на скорость обработки потока данных. В таких системах важно иметь возможность снизить сложность посредством применения методов совместного использования ресурса.

Параметром, обозначенным как SPEED, таким образом, является параметр, который имеет наибольшее влияние при определении синтезированной архитектуры.

| Таблица 1 | ||

| Параметры кодирования | ||

| Параметр | Диапазон | Описание |

| N_STATES | 4-256 | Число состояний на решетчатой |

| (целое число) | диаграмме. | |

| GEN_OUTi | - | i-ый генераторный полином для выходов |

| (i=0,...,4) | ||

| (целое число) | ||

| GEN_FEEDBACKi | - | i-ый генераторный полином для ветви |

| (i=0,...,4) | обратной связи | |

| (целое число) | ||

| Параметры декодирования | ||

| Параметр | Диапазон | Описание |

| OUTPUTS | 0-2 | Делает возможным выбор выходов, |

| (целое число) | подлежащих генерации. | |

| В частности: | ||

| - 0=> генерирует u и с | ||

| - 1=> генерирует u | ||

| - 2=> генерирует с | ||

| DEPTH | - | Устанавливает ширину окна для итераций. |

| (целое число) | (Разрядность решений) | |

| MAX_log_MAP | 0-1 | Выбирает рабочий режим: |

| (целое число) | - 0=> без логарифмической поправки | |

| - 1=> с логарифмической поправкой | ||

| Параметры интерфейса | ||

| Параметр | Диапазон | Описание |

| B_METRIC | 3-16 | Число битов, используемых при |

| (целое число) | представлении метрики ветви (входная | |

| вероятность) | ||

| OUT_METRIC | 3-16 | Число битов, используемых при |

| (целое число) | представлении выходных вероятностей |

| Параметры архитектуры | ||

| Параметр | Диапазон | Описание |

| SPEED | 0-4 | Устанавливает уровень совместного |

| (целое число) | использования ресурса. По мере | |

| увеличения этого параметра используется | ||

| больше ресурсов, но снижается время | ||

| обработки: | ||

| - 1=>1 элемент данных каждые 8 | ||

| тактовых циклов | ||

| - 2=>1 элемент данных каждые 4 | ||

| тактовые цикла | ||

| - 3=>1 элемент данных каждые 2 | ||

| тактовые цикла | ||

| - 4=>1 элемент данных каждый тактовый | ||

| цикл |

Как очевидно специалисту в этой области техники, модуль 50 с определенными таким образом параметрами позволяет с высокой гибкостью генерировать схемы сверточного декодирования для турбоустройств. В частности, упомянутый модуль 50 превосходит, благодаря описанным выше параметрам, используемые до настоящего времени модули для генерации схем декодера.

Определение этих параметров и их реализация нетривиальны и представляет собой один из квалифи