Устройство поиска широкополосных сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации и управления, использующих широкополосные сигналы. Достигаемый технический результат - повышение помехоустойчивости при воздействии структурных помех. Устройство содержит линейную часть (1), перестраиваемый согласованный фильтр (2), детектор (3), блок сравнения с порогом (4,6), ключ (5,8), элемент "НЕ" (7,15), элемент "И" (9), решающий блок (10), блок таймеров (11), генератор тактовых импульсов (12), блок управления переключением каналов (13), триггер (14). 7 ил.

Реферат

Предлагаемое устройство относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы.

Известны устройства поиска широкополосных сигналов (см. а.с. №1003372, Н04L 7/02, 1981 г.; №809619, Н04L 7/02, 1979 г.), которым присущ общий недостаток, заключающийся в низкой помехоустойчивости поиска широкополосных сигналов (ШПС) по задержке, а именно в большой вероятности синхронизации устройств поиска на структурные помехи.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в книге "Шумоподобные сигналы в системах передачи информации" под редакцией Пестрякова В.Б. М.: "Сов. Радио", 1973, стр.66-70, 195-199, 234-240, принятое за прототип.

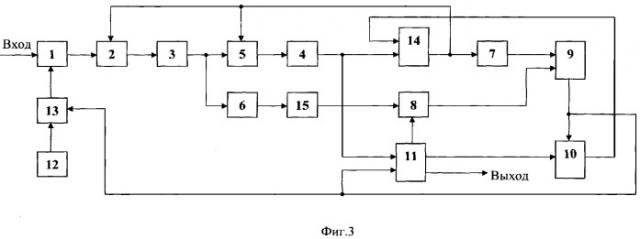

На фиг.1 изображена блок-схема прототипа, где приведены следующие обозначения:

1 - линейная часть;

2 - согласованный фильтр;

3 - детектор;

4 - блок сравнения с порогом;

21 - предварительный фильтр;

22 - линия задержки;

23.1-23.n - первый, ..., n-ый аттенюаторы;

24.1-24.n - первый, ..., n-ый фазовращатели;

25 - сумматор.

Устройство-прототип содержит последовательно соединенные линейную часть 1, вход которой является входом устройства, и согласованный фильтр 2, содержащий последовательно соединенные предварительный фильтр 21 и линию задержки 22, выходы которой соединены соответственно с входами со второго по n-ый аттенюатор 23.2-23.n, выходы которых соединены соответственно с входами со второго по n-ый фазовращатель 24.2-24.n, выходы которых соединены с (n-1) входами сумматора 25 соответственно; при этом вход линии задержки 22 через первый аттенюатор 23.1 и первый фазовращатель 24.1 соединен с первым входом сумматора 25, выход которого, являющийся также выходом согласованного фильтра 2, через детектор 3 подключен ко входу блока сравнения с порогом 4, выход которого является выходом устройства.

Устройство-прототип работает следующим образом.

Сигнал со входа устройства через блок 1 поступает на вход блока 2, где через блок 21 подается на вход блока 22. С входа блока 22 и с его выходов элементы сигнала через соответствующие последовательно соединенные блоки 23.1-23.n и блоки 24.1-24.n поступают на соответствующие n входы блока 25. При этом параметры блока 22, блоков 23.1-23.n и блоков 24.1-24.n выбираются таким образом, что на выходе блока 25 элементы сигнала складываются в фазе и дают значение автокорреляционной функции полезного сигнала, а на выходе блока 3 будет значение огибающей функции автокорреляции (АКФ) полезного сигнала.

В случае, когда на входе устройства присутствуют структурные помехи, то на выходе блока 3 в этом случае будет значение огибающей функции взаимной корреляции (ВКФ) сигнала и структурной помехи.

Таким образом, если на вход устройства приходит только полезный сигнал, то превышение порога в блоке 4 приводит к правильному решению о наличии полезного сигнала, и поиск прекращается. Если же на входе устройства присутствует мощная структурная помеха, то превышение порога в блоке 4 приведет к ошибочному решению о прекращении поиска сигнала.

Укрупненная схема устройства-прототипа представлена на фиг.2, где приведены следующие обозначения:

1 - линейная часть;

2 - согласованный фильтр;

3 - детектор;

4 - блок сравнения с порогом.

Укрупненный прототип содержит последовательно соединенные линейную часть 1, вход которой является входом устройства, согласованный фильтр 2, детектор 3 и блок сравнения с порогом 4, выход которого является выходом устройства.

Укрупненный прототип работает следующим образом.

Сигнал с входа устройства через блок 1 поступает на вход блока 2, где происходит его согласованная фильтрация. С выхода блока 2 сигнал поступает на вход блока 3, где он детектируется, а затем значение огибающей сравнивается с пороговым в блоке 4. Поскольку на вход устройства могут поступать и мощные структурные помехи, то на выходе блока 3 может быть сигнал, который будет принят блоком 4 как истинный.

Недостатком устройства-прототипа является низкая помехоустойчивость при воздействии структурных помех.

Для устранения указанного недостатка в устройство поиска широкополосных сигналов, содержащее первый блок сравнения с порогом и последовательно соединенные линейную часть, первый, сигнальный вход которой является входом устройства, согласованный фильтр и детектор, согласно изобретению введены первый ключ, блок таймеров и последовательно соединенные триггер, первый элемент "НЕ", элемент "И" и решающий блок; последовательно соединенные второй блок сравнения с порогом, второй элемент "НЕ" и второй ключ; последовательно соединенные генератор тактовых импульсов и блок управления переключением каналов; при этом согласованный фильтр выполнен перестраиваемым, и в нем дополнительно введен второй, управляющий вход, соединенный с выходом триггера и вторым, управляющим входом первого ключа, выход которого через первый блок сравнения с порогом соединен с первым, информационным входом триггера и первым входом блока таймеров, первый выход которого соединен со вторым, управляющим входом второго ключа, выход которого соединен со вторым входом элемента "И", выход которого соединен со вторым, управляющим входом блока управления переключением каналов, выход которого соединен с дополнительно введенным вторым, управляющим входом линейной части; выход детектора соединен с входом второго блока сравнения с порогом и первым входом первого ключа; кроме того, выход элемента "И" соединен со вторым входом блока таймеров, второй выход которого соединен с первым, сигнальным входом решающего блока, выход которого соединен со вторым, управляющим входом триггера; третий выход блока таймеров является выходом устройства.

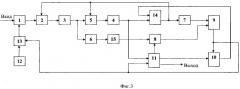

На фиг.3 изображена блок-схема предлагаемого устройства, где приведены следующие обозначения:

1 - линейная часть;

2 - перестраиваемый согласованный фильтр;

3 - детектор;

4 и 6 - первый и второй блоки сравнения с порогом;

5 и 8 - первый и второй ключи;

7 и 15 - первый и второй элементы "НЕ";

9 - элемент "И";

10 - решающий блок;

11 - блок таймеров;

12 - генератор тактовых импульсов;

13 - блок управления переключением каналов;

14 - триггер.

Предлагаемое устройство содержит последовательно соединенные линейную часть 1, перестраиваемый согласованный фильтр 2, детектор 3, первый ключ 5, первый блок сравнения с порогом 4, триггер 14, первый элемент "НЕ" 7, элемент "И" 9 и решающий блок 10, выход которого соединен со вторым, управляющим входом триггера 14, выход которого соединен со вторыми, управляющими входами перестраиваемого согласованного фильтра 2 и первого ключа 5; кроме того, выход детектора 3 через последовательно соединенные второй блок сравнения с порогом 6, второй элемент "НЕ" 15 и второй ключ 8 подключен ко второму входу элемента "И" 9, выход которого соединен со вторым, управляющим входом блока управления переключением каналов 13, первый вход которого соединен с выходом генератора тактовых импульсов 12, а выход - со вторым, управляющим входом линейной части 1, первый, сигнальный вход которой является входом устройства. Кроме того, выход первого блока сравнения с порогом 4 соединен с первым входом блока таймеров 11, выход элемента "И" 9 соединен со вторым входом блока таймеров 11, первый выход которого соединен со вторым, управляющим входом второго ключа 8, второй - с первым, сигнальным входом решающего блока 10, а третий выход блока таймеров 11 является выходом устройства.

Предлагаемое устройство работает следующим образом.

На вход устройства может поступать сигнал, структурная помеха или их смесь.

В исходном состоянии на выходе блока 14 находится логическая единица, которая поступает на второй, управляющий вход блока 5, в результате чего в исходном состоянии блок 5 открыт, что обеспечивает прохождение сигнала с выхода блока 3 на вход блока 4; при этом блок 8 закрыт.

Рассмотрим случай, когда с входа устройства на первый, сигнальный вход блока 1 поступает только полезный сигнал.

С выхода блока 1 сигнал поступает на первый, сигнальный вход блока 2, где происходит его согласованная фильтрация. Отфильтрованный сигнал с выхода блока 2 поступает на вход блока 3. С выхода блока 3 значение огибающей АКФ полезного сигнала через блок 5 подается на вход блока 4, где происходит сравнение с пороговым значением. Превышение порога в блоке 4, уровень которого определяется уровнем полезного сигнала, приводит к тому, что с выхода блока 4 на первый, информационный вход блока 14 поступает логическая единица, которая переведет его в другое состояние, в результате которого на его выходе будет логический ноль, который поступит на вход блока 7, где он проинвертируется, и на первый вход блока 9 придет логическая единица. В то же время логический ноль с выхода блока 14 поступит на второй, управляющий вход блока 2, что приведет к перестройке характеристик блока 2 на обработку другой формы сигнала, а также на второй, управляющий вход блока 5, и закроет его.

При этом с выхода блока 4 логическая единица поступает на первый вход блока 11, в результате чего на его первом выходе через время, равное периоду найденного сигнала, сформируется логический импульс, который поступит на второй, управляющий вход блока 8, и откроет его. К этому времени блок 2 закончит перестройку на прием ортогонального сигнала, огибающая АКФ которого с выхода блока 3 подается на вход блока 6, где происходит сравнение с пороговым значением. Так как поступивший сигнал полезный и не содержит помех, то порог в блоке 6, уровень которого определяется уровнем структурной помехи, не будет превышен, и на выходе блока 6 сформируется логический ноль, а на выходе блока 15 сформируется логическая единица, которая через блок 8 подается на второй вход блока 9.

Следовательно, на выходе блока 9 сформируется логическая единица, которая поступит на второй, управляющий вход блока 13, что приведет к фиксации данного канала, а также на второй вход блока 11, в результате чего с третьего выхода блока 11 с периодичностью, равной периоду полезного сигнала, в моменты, соответствующие превышению порога полезным сигналом, будет выходить импульс уровня логической единицы, что означает - сигнал найден, и поиск сигнала закончен.

Если на первый, сигнальный вход блока 1 поступит смесь полезного сигнала и мощной структурной помехи, то, как и в случае с полезным сигналом, превышение порога суммы огибающих АКФ и ВКФ в блоке 4 приведет к поступлению на первый вход блока 14 логической единицы, которая переведет его в другое состояние, и на его выходе будет логический ноль, который поступит на вход блока 7, где он проинвертируется, и на первый вход блока 9 придет логическая единица. В то же время логический ноль с выхода блока 14 поступит на второй, управляющий вход блока 2, что приведет к перестройке характеристик блока 2 на обработку другой формы сигнала, а также на второй, управляющий вход блока 5, и закроет его.

При этом с выхода блока 4 логическая единица поступает на первый вход блока 11, в результате чего на его первом выходе через время, равное периоду обнаруживаемого сигнала, сформируется логический импульс, который поступит на второй, управляющий вход блока 8, и откроет его. К этому времени блок 2 закончит перестройку на прием ортогонального сигнала, огибающая АКФ которого с выхода блока 3 подается на вход блока 6, где происходит сравнение с пороговым значением. Так как поступивший сигнал содержит мощную структурную помеху, то порог в блоке 6 будет превышен, и на его выходе блока 6 сформируется логическая единица, а на его выходе сформируется логический ноль, который через блок 8 подается на второй вход блока 9.

Следовательно, на выходе блока 9 сформируется логический ноль, который поступит на второй, управляющий вход блока 13, что приведет к прохождению в блок тактовых импульсов с выхода блока 12, в результате чего произойдет подготовка к работе на другом канале. Кроме того, логический ноль поступит также на второй вход блока 11, в результате чего по истечении времени, равного двум периодам обнаруживаемого сигнала, на втором выходе блока 11 сформируется импульс уровня логической единицы, который поступит на первый, сигнальный вход блока 10, что приведет к перестройке устройства поиска, которая произойдет следующим образом. С выхода блока 10 на второй, управляющий вход блока 14 поступит логическая единица, что приведет к формированию логической единицы на его выходе, которая поступит на вторые, управляющие входы блоков 2 и 5, в результате чего система вернется в первоначальное состояние, то есть будет готова к поиску полезного сигнала, и поиск полезного сигнала будет продолжен на других каналах.

Если на вход устройства поступит только мощная структурная помеха, то пороги в блоках 2 и 5 будут превышены, и работа устройства поиска будет такой же, как и в случае приема сигнала с мощной структурной помехой.

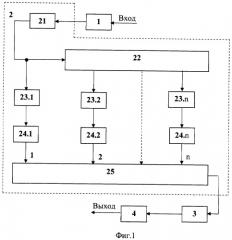

Функциональная схема перестраиваемого согласованного фильтра 2 приведена на фиг.4, где введены следующие обозначения:

21 - предварительный фильтр;

22 - линия задержки;

23.1-23.n - первый, ..., n-ый аттенюаторы;

24.11-24.n1 - первый, ..., n-ый фазовращатели первой группы;

24.12-24.n2 - первый, ..., n-ый фазовращатели второй группы;

25 - сумматор;

26.11-26.n1 - первый, ..., n-ый ключи первой группы;

26.12-26.n2 - первый, ..., n-ый ключи второй группы;

27 - триггер.

Перестраиваемый согласованный фильтр (ПСФ) 2 содержит последовательно соединенные предварительный фильтр 21, вход которого является первым, сигнальным входом ПСФ 2, и линию задержки 22, вход и (n-1) выходов которой соединены соответственно со входами n аттенюаторов 23.1-23.n, выходы которых соединены с объединенными между собой первыми, сигнальными входами соответствующей пары ключей первой 26.11-26.n1 и второй 26.12-26.n2. групп. Вторым, управляющим входом ПСФ 2 является вход триггера 27, первый, прямой выход которого соединен со вторыми, управляющими входами n ключей первой группы 26.11-26.n1, выходы которых через соответствующие фазовращатели первой группы 24.11-24.n1 соединены с n входами первой группы сумматора 25 соответственно. Второй, инверсный выход триггера 27 соединен со вторыми, управляющими входами n ключей второй группы 26.12-26.n2, выходы которых через соответствующие фазовращатели второй группы 24.12-24.n2 соединены соответственно с n входами второй группы сумматора 25, выход которого является выходом ПСФ 2.

ПСФ 2 работает следующим образом.

В исходном состоянии на входе блока 27 находится логическая единица, и, следовательно, на его первом, прямом выходе будет логическая единица, которая открывает блоки 26.11-26.n1, при этом блоки 26.12-26.n2 закрыты. В этом случае сигналы с блоков 23.1-23.n проходят на блоки 24.11-24.n1, параметры которых выбираются таким образом, что ПСФ 2 является согласованным (оптимальным) для обнаруживаемого сигнала. В блоке 25 происходит суммирование n составляющих ортогонального сигнала, результат которого подается на выход блока 2.

В случае, когда на вход устройства поступает только полезный сигнал, на вход блока 27 поступит логический ноль, в результате чего блок 27 срабатывает, и на его первом, прямом выходе сформируется логический ноль, а на втором, инверсном выходе - логическая единица. В итоге блоки 26.11-26.n1 закроются, а блоки 26.12-26.n2 откроются, и сигналы с блоков 23.1-23.n проходят на блоки 24.12-24.n2, параметры которых выбираются таким образом, что ПСФ 2 является согласованным для сигнала, являющегося ортогональным к обнаруживаемому. В блоке 25 происходит суммирование n составляющих полезного сигнала, результат которого подается на выход блока 2.

Методика выбора параметров фазовращателей для построения оптимальных фильтров широко известна и приведена в книге Варакина Л.Е. "Системы связи с шумоподобными сигналами". М.: "Радио и связь", 1985.

Функциональная схема решающего блока 10 приведена на фиг.5, где введены следующие обозначения:

101 - триггер;

102 - ключ;

103 - линия задержки.

Решающий блок 10 содержит последовательно соединенные триггер 101, ключ 102 и линию задержки 103, выход которой является выходом решающего блока 10. При этом вход триггера 101 является вторым, управляющим входом решающего блока 10, а первый вход ключа 102 - первым, сигнальным входом решающего блока 10.

Решающий блок 10 работает следующим образом.

В исходном состоянии с блока 9 сигнал уровня логического ноля поступает на вход блока 101, на выходе которого будет логическая единица, которая приходит на второй, управляющий вход блока 102, в результате чего блок 102 открыт, и сигнал логической единицы со второго выхода блока 11 через блоки 102 и 103 проходит на второй, управляющий вход блока 14, что приведет к перестройке устройства поиска.

В случае прихода с блока 9 логической единицы блок 102 закрывается, и на второй, управляющий вход блока 14 подается логический ноль, что приведет к прекращению поиска.

При наличии мощной структурной помехи с выхода блока 9 на вход блока 101 поступает сигнал уровня логического ноля, вследствие чего блок 102 открывается, и сигнал логической единицы со второго выхода блока 11 через блоки 102 и 103 проходит на второй, управляющий вход блока 14, что приведет к перестройке устройства поиска.

Структурная схема блока таймеров 11 приведена на фиг.6, где введены следующие обозначения:

111 - первый таймер;

112 - второй таймер;

113 - третий таймер;

114 - первый формирователь;

115 - второй формирователь;

116 - третий формирователь.

Блок таймеров 11 содержит последовательно соединенные первый таймер 111 и первый формирователь 114, выход которого является первым выходом блока таймеров 11; последовательно соединенные второй таймер 112 и второй формирователь 115, выход которого является вторым выходом блока таймеров 11; последовательно соединенные третий таймер 113 и третий формирователь 116, выход которого является третьим выходом блока таймеров. При этом вход первого таймера 111, объединенный с входом второго таймера 112, является первым входом блока таймеров 11, а вход третьего таймера является вторым входом блока таймеров 11.

Блок таймеров 11 работает следующим образом.

При превышении порога в блоке 4 сигнал уровня логической единицы подается на первый вход блока таймеров 11, откуда он подается на блоки 111 и 112. По истечении времени прохода периода найденного сигнала на выходе блока 111 генерируется импульс, который запускает блок 114, на выходе которого формируется логическая единица, которая с первого выхода блока 11 подается на второй, управляющий вход блока 8. По истечении времени прохода двойного периода найденного сигнала на выходе блока 112 генерируется импульс, который запускает блок 115, на выходе которого формируется логическая единица, которая со второго выхода блока 11 подается на первый, сигнальный вход блока 10.

Если устройство поиска обнаружило полезный сигнал, то с выхода блока 9 на вход блока 113 подается сигнал логической единицы. По истечении времени прохода периода найденного сигнала на выходе блока 113 генерируется импульс, который запускает блок 116, на выходе которого формируется логическая единица, которая с третьего выхода блока 11 подается на выход устройства.

Структурная схема блока управления переключением каналов 13 приведена на фиг.7, где введены следующие обозначения:

131 - триггер;

132 - счетчик фиксированных чисел;

133 - формирователь;

134 - канальный переключатель;

135 - ключ.

Блок управления переключением каналов (БУПК) 13 содержит последовательно соединенные ключ 135, счетчик фиксированных чисел 132, формирователь 133 и канальный переключатель 134, выход которого является выходом БУПК 13; а также содержит триггер 131, вход которого также является вторым, управляющим входом БУПК 13, а выход триггера 131 соединен с первым входом ключа 135, второй вход которого является также первым входом БУПК 13.

БУПК 13 работает следующим образом.

В исходном состоянии в блоке 132 записан логический ноль, при этом на выходе блока 131 находится логическая единица, которая держит открытым блок 135.

Если устройство поиска обнаружило полезный сигнал, то с выхода блока 9 на вход блока 131 поступит логическая единица и переведет его в другое состояние, и сигнал логического ноля с выхода блока 131 поступит на первый вход блока 135, что приведет к его закрытию. Следовательно, тактовые импульсы с блока 12 не будут поступать на вход блока 132, и каналы переключаться не будут, чем обеспечится фиксация данного канала.

Рассмотрим процессы, происходящие в блоке 13, при наличии на входе устройства смеси полезного сигнала и мощных структурных помех, а также при наличии одних структурных помех.

С выхода блока 9 на вход блока 131 подается логический ноль, и, следовательно, на его выходе будет логическая единица, которая держит открытым блок 135. При этом тактовые импульсы с выхода блока 12 через блок 135 поступают на вход блока 132. После отсчета заданного числа тактовых импульсов, которое определяется временем, в течение которого устройство поиска будет производить обнаружение полезного сигнала на данном канале, на выходе блока 132 появится логическая единица, при поступлении которой в блоке 133 сформируется логический импульс, который подается на вход блока 134, что приведет к переключению его на другую частоту.

В качестве блока 134 можно использовать перестраиваемый генератор, выполненный как цифровой синтезатор частот на микросхеме класса DDS AD 9858 (Analog Devices).

Остальные блоки имеют широкое применение и описаны в научно-технической литературе.

Описание принципа построения блока 14 можно найти, например, в книге Н.И.Димитрова, В.П.Пунджева "33 схемы на триггерах", пер. с болгарского, Л., "Энергоатомиздат", Ленинградское отд., 1990.

Блок 12 может быть выполнен на основе различных типов генераторов, например на основе кварцевого генератора (см. книгу М.Мэндла "200 избранных схем электроники", пер. с англ. под редакцией Я.С.Ицхоки, М., "Мир", 1980, стр.86-87, рис.4.5), либо на основе блокинг-генератора (там же, стр.94-96, рис.4.9). В этой же книге можно найти описание структуры и принципов построения блоков 4, 5, 6 и 8.

Таким образом, введение дополнительных блоков в заявленном устройстве обеспечивает снижение вероятности ложной синхронизации на мощные структурные помехи, в результате чего значительно улучшается помехоустойчивость устройства.

Устройство поиска широкополосных сигналов, содержащее первый блок сравнения с порогом и последовательно соединенные линейную часть, первый, сигнальный вход которой является входом устройства, согласованный фильтр и детектор, отличающееся тем, что введены первый ключ, блок таймеров и последовательно соединенные триггер, первый элемент "НЕ", элемент "И" и решающий блок; последовательно соединенные второй блок сравнения с порогом, второй элемент "НЕ" и второй ключ; последовательно соединенные генератор тактовых импульсов и блок управления переключением каналов; при этом согласованный фильтр выполнен перестраиваемым, и в нем дополнительно введен второй, управляющий вход, соединенный с выходом триггера и вторым, управляющим входом первого ключа, выход которого через первый блок сравнения с порогом соединен с первым, информационным входом триггера и первым входом блока таймеров, первый выход которого соединен со вторым, управляющим входом второго ключа, выход которого соединен со вторым входом элемента "И", выход которого соединен со вторым, управляющим входом блока управления переключением каналов, выход которого соединен с дополнительно введенным вторым, управляющим входом линейной части; выход детектора соединен с входом второго блока сравнения с порогом и первым входом первого ключа; кроме того, выход элемента "И" соединен со вторым входом блока таймеров, второй выход которого соединен с первым, сигнальным входом решающего блока, выход которого соединен со вторым, управляющим входом триггера; третий выход блока таймеров является выходом устройства.