Преобразователь время-код

Иллюстрации

Показать всеИзобретение относится к измерительной технике, а именно к технике цифрового измерения интервалов времени. В устройство, содержащее синхронизированную с опорным генератором цифровую линию задержки, дополнительно введены управляемый элемент задержки, блок фазовой интерполяции, второй блок регистров, первый и второй шифраторы, счетчик импульсов и блок вычитания. Входы блока вычитания, образующего результат преобразования, соединены с соответствующими выходами счетчика импульсов и обоих шифраторов, у которых входы подключены к соответствующим выходам первого и второго блоков регистров. Соответствующие информационные входы обоих блоков регистров объединены, а разделенные тактовые входы регистров обоих блоков регистров присоединены к соответствующим выходам блока фазовой интерполяции. Первый вход блока фазовой интерполяции вместе с входом управляемого элемента задержки и управляющим входом счетчика импульсов посредством буферного элемента присоединен к входному зажиму устройства, а его второй вход - к выходу управляемого элемента задержки. Управляющий вход управляемого элемента задержки объединен с управляющим входом цифровой линии задержки, основным выходом присоединенной к счетному входу счетчика импульсов. Технический результат - упрощение устройства при сохранении высокой точности измерения. 2 з.п. ф-лы, 6 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к технике прецизионного измерения интервалов времени.

Уровень техники

Для измерения интервалов времени широко применяются преобразователи время-код, действие которых основано на подсчете числа импульсов эталонного периода, укладывающихся в измеряемый интервал времени. Для повышения точности преобразования за счет уменьшения шага квантования времени используются различные способы интерполяции эталонного периода.

Известен цифровой измеритель интервалов времени [1], который содержит эталонный генератор импульсов, выход которого присоединен через первый элемент И к входу счетчика импульсов, при этом оставшийся вход первого элемента И подключен к выходу триггера, входы которого служат входами сигналов пуска и останова устройства. Кроме того, имеется подключенная к выходу эталонного генератора последовательная цепь множества элементов задержки, выход каждого из которых соединен с входом сброса соответствующего дополнительного триггера, число которых равно числу элементов задержки. Выходы всех дополнительных триггеров присоединены к входам шифратора. Процесс измерения начинается после сброса счетчика импульсов и триггеров импульсом пуска, а завершается импульсом останова. Старшие разряды результата измерения образуются на выходах счетчика импульсов и отображают целое число эталонных периодов, укладывающихся в измеряемый интервал, а младшие разряды результата образуются на выходах шифратора и отображают дробную часть эталонного периода - остаток от деления интервала на эталонный период в единицах времени задержки элемента задержки. Недостаток данного аналога - низкая точность измерения, погрешность которого не может быть меньше времени задержки одного элемента задержки.

Аналогами настоящего изобретения являются также схемы цифровых преобразователей время-код, в которых использован нониусный метод оценки дробной части измеряемого с помощью эталонного генератора интервала времени, например схема, описанная в [2]. Данное устройство включает основной и дополнительный генераторы импульсов, периоды которых различаются на малую величину, которая и составляет значение разрешения по времени. В известное устройство входят также два триггера и два элемента И, управляющие процессом нониусной развертки, а также два счетчика импульсов, отображающих результат измерения. При высокой точности измерения данного устройства оно имеет низкую производительность, так как процесс нониусной развертки занимает множество опорных периодов, тем большее, чем выше точность измерения.

Другим аналогом настоящего изобретения является временной интерполятор [3], содержащий счетчик импульсов и секционированную линию задержки, входы которых соединены с общим зажимом опорных сигналов. Устройство включает регистр в виде множества триггеров с общими информационными и сбросовыми входами, причем синхронизирующие входы триггеров соединены с соответствующими промежуточными отводами линии задержки. Кроме того, в схему входит постоянное запоминающее устройство (ПЗУ), которое служит преобразователем термометрического кода регистра в двоичный код. Общее время задержки секционированной линии задержки равно одному опорному периоду. Запуск устройства осуществляется синхронизированным с опорным сигналом стартовым импульсом, который разрешает работу счетчика импульсов. Одновременно опорные сигналы распространяются по линии задержки. В момент поступления стопового импульса счетчик импульсов фиксирует число полных опорных периодов, уложившихся в измеряемый интервал, а регистр - номер отвода секционированной линии задержки, до которого успел распространиться опорный сигнал. В итоге счетчик отражает старшие биты результата измерения, а ПЗУ - младшие биты. Погрешность измерения определяется в аналоге временем задержки одной секции линии задержки, что существенно меньше опорного периода. В то же время такая разрешающая способность преобразователя время-код во многих применениях оказывается недостаточной, кроме того, имеется дополнительный источник погрешности преобразования из-за возможной неравномерности задержки отдельных секций линии задержки.

Известно также устройство для измерения интервала времени [4] с опорным генератором в виде мультифазного генератора импульсов (МГИ), множество выходов которого образует субшкалу отсчета времени. Выходы МГИ связаны с соответствующими информационными входами двух регистров, тактовые входы которых соединены с входными зажимами сигналов начала и окончания интервала времени, а выходы через соответствующие шифраторы подключены к младшим входам соответствующих операндов блока вычитания. При этом старшие входы первого операнда блока вычитания присоединены посредством третьего регистра к выходам счетчика импульсов, определяющего целое число опорных периодов в измеряемом интервале времени. Имеется также четвертый регистр для записи результата измерения в момент окончания интервала времени. В данном аналоге нет необходимости в синхронизации начала отсчета интервала с опорным импульсом, а неравномерность квантов времени по выходам МГИ может быть получена произвольно малой. Это обеспечивает повышение точности измерения временного интервала. Однако точность измерения по-прежнему ограничена значением названного кванта времени МГИ.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является временной интерполятор [5]. Данное устройство содержит МГИ, выполненный в виде основной линии задержки на последовательно соединенных управляемых элементах задержки, вход основной линии задержки подключен к выходу опорного генератора. Каждый элемент задержки снабжен управляющим входом для электронного регулирования времени задержки, указанные входы элементов задержки объединены и используются как единый управляющий вход основной линии задержки. Этот управляющий вход используется для автоматической подстройки полного времени задержки линии задержки, которая осуществляется с помощью блока фазового сравнения, установленного в цепи обратной связи линии задержки. Блок фазового сравнения, регулируя полное время задержки линии задержки, поддерживает его точно равным опорному периоду. В устройстве имеются также множество регистров, одноименные информационные входы которых объединены и подключены к соответствующим выходам МГИ - промежуточным отводам основной линии задержки. Устройство содержит, кроме того, дополнительную прецизионную линию задержки с распределенной RC-структурой, к множеству промежуточных отводов которых присоединены тактовые входы соответствующих регистров. Полное время задержки дополнительной линии задержки равно времени задержки одного звена в основной линии задержки. В устройстве предусмотрены средства автоматической калибровки времени задержки каждого звена дополнительной линии задержки.

Импульс, момент поступления которого преобразуется устройством в цифровой код, приходит на вход дополнительной линии задержки и далее появляется на ее промежуточных отводах, последовательно задерживаясь каждым звеном. Время задержки импульса в каждой секции определяется выражением

где То - опорный период, N и М - число звеньев соответственно основной и дополнительной линий задержки.

Импульсы с отводов дополнительной линии задержки поступают на тактовые входы соответствующих М регистров, которые фиксируют состояния всех выходов МГИ в моменты, разделенные квантом Δt. В итоге на полной совокупности выходов всех N-разрядных регистров образуется цифровой термометрический код разрядностью N×M, который далее может быть преобразован в обычный двоичный код известными средствами.

Устройство-прототип отличается высокой разрешающей способностью по времени, так как квант времени Δt в N раз меньше времени задержки одного звена основной линии задержки. Например, если элементом задержки основной линии задержки служит спаренный инвертор КМОП типа, то в прототипе достигается разрешение 48,8 пикосекунд, что много меньше времени задержки распространения двух инверторов.

Устройство-прототип имеет недостатки. Во-первых, его основу, обеспечивающую прецизионное преобразование времени в код, составляет сложная в изготовлении дополнительная линия задержки с распределенной интегральной RC-структурой. Такая линия задержки требует индивидуальной подгонки звеньев в процессе изготовления и калибровки их времени задержки в процессе эксплуатации. Во-вторых, в устройстве-прототипе не предусмотрены технические средства для преобразования в код интервала времени как разности моментов спада и фронта входного импульса.

Сущность изобретения

Целью настоящего изобретения является упрощение преобразователя время-код и расширение его функциональных возможностей. Указанная цель достигается благодаря замене пассивной линии задержки RC типа не требующим регулировок активным фазовым интерполятором и введению блоков, фиксирующих моменты спада и фронта входного сигнала в виде цифровых кодов и вычисляющих их разность.

Преобразователь время-код содержит соединенный с входным зажимом буферный элемент, цифровую линию задержки, охваченную обратной связью через блок фазового сравнения с запускающим цифровую линию задержки опорным генератором, а также первый блок регистров, информационные входы регистров в которых подключены к соответствующим выходам цифровой линии задержки, а каждый регистр в первом блоке регистров имеет собственный тактовый вход. Для достижения поставленной цели в устройство дополнительно введены управляемый элемент задержки, блок фазовой интерполяции, второй блок регистров, первый и второй шифраторы, счетчик импульсов и блок вычитания. При этом выходы блока вычитания являются выходами преобразователя время-код, а его соответствующие входы подключены к выходам счетчика импульсов, второго и первого шифраторов. Входы первого и второго шифраторов соединены с соответствующими выходами первого и второго блока регистров соответственно, информационные входы второго блока регистров объединены с соответствующими информационными входами первого блока регистров, тактовые входы всех регистров в обоих блоках регистров присоединены к соответствующим выходам блока фазовой интерполяции. Первый вход блока фазовой интерполяции вместе с управляющим входом счетчика импульсов и входом управляемого элемента задержки подключен к выходу буферного элемента, а его второй вход - к выходу управляемого элемента задержки. Управляющий вход управляемого элемента задержки объединен с управляющим входом цифровой линии задержки, основным выходом присоединенной к счетному входу счетчика импульсов.

Цифровая линия задержки может быть выполнена в виде последовательной цепи управляемых элементов задержки, объединенные управляющие входы которых служат управляющим входом цифровой линии задержки, а их выходы - выходами цифровой линии задержки.

В предпочтительном варианте исполнения блок фазовой интерполяции содержит последовательно соединенные каскады интерполяции, каждый i-ый каскад интерполяции имеет (2i-1+1) входов и (2i+1) выходов, выходы оконечного каскада интерполяции служат выходами блока фазовой интерполяции. Каждый каскад интерполяции включает (2i-1+1) элементов интерполяции, имеющих первый и второй парафазные входы и парафазный выход, первый и второй входы элементов интерполяции с нечетными порядковыми номерами объединены и служат входами каскада интерполяции. Первый и второй входы элементов интерполяции с четными порядковыми номерами подключены к объединенным входам соответствующих элементов интерполяции с нечетными порядковыми номерами, отличающимися от порядкового номера данного элемента интерполяции на ±1, выходы всех элементов интерполяции составляют совокупность выходов каскада интерполяции.

Каждый из элементов фазовой интерполяции, соединенных между собой в блоке фазовой интерполяции описанным выше образом, представляет собой узел взвешенного суммирования двух входных сигналов и в биполярном варианте может быть выполнен в виде двойного балансного смесителя на трех дифференциальных транзисторных каскадах. В схеме двойного балансного смесителя первый и второй дифференциальные транзисторные каскады имеют общие коллекторные резисторы соответственно в правом и левом плечах, а источниками токов смещения являются коллекторные цепи соответствующих транзисторов третьего дифференциального транзисторного каскада, имеющего общий источник тока смещения в эмиттерной цепи. Дифференциальные входы первого и второго дифференциальных транзисторных каскадов служат первым и вторым парафазными входами элемента фазовой интерполяции. Для обеспечения нагрузочной способности и согласования входных/выходных цепей элементов фазовой интерполяции объединенные коллекторы первого и второго дифференциальных транзисторных каскадов подключены к парафазным выходам элемента фазовой интерполяции через эмиттерные повторители.

Принцип действия предлагаемого устройства основан на стробировании состояний цифровой линии задержки в моменты начала и окончания преобразуемого интервала времени импульсами, сдвинутыми относительно друг друга на время Δt в течение времени, равного времени задержки распространения одного звена цифровой линии задержки. Указанные состояния, соответствующие цифровому отсчету фронта и спада интервала времени запоминаются первым и вторым блоками регистров, регистры которых тактируются смещенными на Δt импульсами. Число полных периодов опорного генератора, укладывающихся в интервале, фиксируется счетчиком импульсов. Код, отражающий длительность интервала, образуется как разность отсчетов после преобразования термометрических кодов блоков регистров в двоичные коды в соответствии с выражением:

где dСЧ - двоичное состояние счетчика импульсов, dРГ1, dРГ2 - преобразованные первым и вторым шифраторами состояния первого и второго блоков регистров соответственно.

Таким образом, в предлагаемом преобразователе время-код достигается такая же разрешающая способность, как и в прототипе, но существенно более простыми средствами. Смещенные на Δt тактовые импульсы формируются активным блоком фазовой интерполяции, не требующим юстировки и регулирования. Принцип действия блока фазовой интерполяции рассматривается ниже при описании предпочтительного варианта осуществления изобретения.

Перечень чертежей

На фиг.1 представлена функциональная электрическая схема преобразователя время-код в соответствии с настоящим изобретением.

На фиг.2 показана принципиальная схема варианта секции цифровой линии задержки, входящей в преобразователь время-код.

На фиг.3 показан вариант принципиальной схемы биполярного элемента фазовой интерполяции, используемого в блоке фазовой интерполяции.

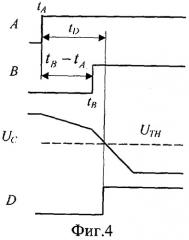

На фиг.4 изображена временная диаграмма сигналов, поясняющая принцип действия элемента фазовой интерполяции.

На фиг.5 представлена функциональная схема блока фазовой интерполяции, выполненного на элементах фазовой интерполяции.

На фиг.6 изображены временные диаграммы сигналов в характерных узлах преобразователя время-код, поясняющие принцип его действия.

Сведения, подтверждающие возможность осуществления изобретения

Представленная на фиг.1 схема преобразователя время-код содержит входной буферный элемент 1, соединяющий входной зажим 2 с управляющим входом счетчика 3 импульсов, входом управляемого элемента 4 задержки и первым входом блока 5 фазовой интерполяции, второй вход которого подключен к выходу управляемого элемента 4 задержки. Счетный вход счетчика 3 импульсов присоединен к основному выходу цифровой линии 6 задержки, имеющий множество промежуточных выходов, сигнальный вход и управляющий вход. Сигнальный вход цифровой линии 6 задержки соединен с выходом опорного генератора 7 и одним входом блока 8 фазового сравнения, у которого другой вход соединен с основным выходом цифровой линии 7 задержки, а выход - с ее управляющим входом. Промежуточные и основной выходы цифровой линии 6 задержки подключены к соответствующим информационным входам первого 9 и второго 10 блоков регистров, причем тактовые входы регистров первого блока 9 регистров подключены к соответствующим прямым выходам блока 5 фазовой интерполяции, а тактовые входы регистров второго блока 10 регистров - к соответствующим инверсным выходам блока 5 фазовой интерполяции. Выходы первого блока 9 регистров, представляющие собой упорядоченную совокупность всех выходов всех входящих в него регистров, подключены к соответствующим входам первого шифратора 11, а выходы второго блока 10 регистров - к входам второго шифратора 12. Выходы счетчика 3 импульсов и второго шифратора 12 присоединены к соответствующим входам уменьшаемого блока 13 вычитания, входы вычитаемого которого соединены с соответствующими выходами второго шифратора 12. Входы старших разрядов вычитаемого подключены к шине «0», поскольку разрядность уменьшаемого в общем случае меньше разрядности вычитаемого. Блок 13 вычитания на своих выходах 14 образует результат преобразования интервала времени в цифровой код.

Цифровая линия 6 задержки в предпочтительном варианте осуществления представляет собой последовательную цепь управляемых электронных элементов 15 задержки, объединенные управляющие входы которых служат управляющим входом цифровой линии задержки, а их выходы - выходами цифровой линии 6 задержки. Элементом задержки может служить любой неинвертирующий логический элемент, допускающий электронное регулирование времени задержки распространения. В биполярном варианте это может быть буферный элемент эмиттерно-связанной логики с регулируемым током смещения, схема которого показана на фиг.2. Схема состоит из дифференциального переключателя тока на транзисторах 16, 17 с раздельными коллекторными резисторами 18, 19 с общим источником эмиттерного тока на транзисторе 20 и резисторе 21. Диоды 22, 23 шунтируют коллекторные нагрузки транзисторов 16 и 17 для ограничения размаха выходного напряжения. Эмиттерные повторители на транзисторах 24, 25 с соответствующими нагрузочными резисторами 26, 27 служат для согласования уровней входных/выходных сигналов. Времязадающим конденсатором 28 может служить паразитная емкость схемы. Дифференциальным парафазным входом элемента 15 задержки служат базы 29 транзисторов 16 и 17, а дифференциальным парафазным выходом - выходы 30 эмиттерных повторителей 24 и 25. База 31 транзистора 20 в источнике тока смещения служит управляющим входом элемента 15 задержки. Изменение напряжения на управляющем входе 31 приводит к изменению тока смещения каскада и, следовательно, к изменению скорости перезаряда конденсатора 28. Это означает изменение времени задержки распространения, которое обычно отсчитывается по уровню половины размаха выходного напряжения.

Основу блока 5 фазовой интерполяции составляют элементы фазовой интерполяции, каждый из которых в биполярном варианте исполнения может быть построен как двойной балансный смеситель, упрощенная схема которого показана на фиг.3. Схема выполняет взвешенное суммирование входных сигналов. Схема включает три дифференциальных транзисторных каскада на транзисторах соответственно 32 и 33, 34 и 35, 36 и 37, два из которых переключаются входными парафазными сигналами А и В, а третий распределяет ток общего источника 38 между двумя первыми каскадами в соответствии с управляющим напряжением U. Пара дифференциальных каскадов на транзисторах 32 и 33, 34 и 35 имеют общую коллекторную нагрузку в виде резисторов 39 и 40, напряжения с которых выводятся на парафазный выход D, с помощью эмиттерных повторителей на транзисторах 41 и 42, служащих также для согласования уровней входных и выходных сигналов элементов фазовой интерполяции. Конденсатором 43, определяющим задержку распространения элемента фазовой интерполяции, может быть паразитная емкость схемы, приведенная к точкам подключения. На фиг.3 приведено также используемое ниже упрощенное графическое обозначение элемента фазовой интерполяции.

Фиг.4 иллюстрирует принцип действия элемента фазовой интерполяции, схема

где

a R - сопротивление выравнивающего резистора в эмиттерной цепи управляющего дифференциального каскада. Если моменты поступления tA и tB фронтов (или спадов) сигналов различаются на tB-tA, то в процессе двухэтапного перезаряда емкости сначала током IA, а затем полным током I0 задержка выходного сигнала D относительно входного сигнала А, отсчитанная по уровню половины перепада, составит

где - время задержки при совпадающих фронтах сигналов А и В. При изменении управляющего напряжения U в пределах от -RI0 до +RI0 значение k(U) изменяется от 1 до 0. Коэффициент k(U), следовательно, определяет влияние входа В на задержку распространения сигнала от входа А до выхода D. В описываемом устройстве элемент фазовой интерполяции используется в режиме U=0, при этом k(U)=1/2 и фронт выходного сигнала D располагается по центру между фронтами задержанных на входных сигналов А и В.

Блок 5 фазовой интерполяции содержит последовательно соединенные каскады интерполяции. В приведенном на фиг.5 примере схемы этого блока первый каскад интерполяции, состоящий из элементов 43, 44, 45 фазовой интерполяции, имеет два входа и три выхода, второй каскад интерполяции включает элементы 46...50 и имеет три входа, соединенных с тремя выходами первого каскада, и пять выходов. Третий каскад фазовой интерполяции состоит из элементов 51...59 фазовой интерполяции и имеет пять входов и девять выходов. Парафазный выходной сигнал каждого из элементов 43...59 фазовой интерполяции располагается по центру между задержанными входными сигналами этих элементов, то есть задержка распространения выходного сигнала относительно сигнала на первом входе составляет где tB, tA - моменты поступления сигналов на входы В и А соответственно. Поскольку входы элементов 42, 44 46, 48, 50, 51, 53, 55, 57 и 59 объединены tB=tA, то они выполняют функции простых элементов задержки на время . Остальные элементы фазовой интерполяции в схеме выполняют основную функцию фазовой интерполяции. Выход элемента 59 фазовой интерполяции не используется, данный элемент служит для выравнивания нагрузок элементов в блоке. С каждым каскадом фазовой интерполяции квант времени уменьшается в два раза, если входные сигналы блока 5 фазовой интерполяции разделены интервалом времени , то в трехкаскадном примере осуществления этого блока парафазные сигналы на смежных выходах оказываются разделенными интервалами Δt=/8.

Порядок функционирования устройства (фиг.1) иллюстрируется временными диаграммами, показанными на фиг.6. До поступления преобразуемого сигнала 60 опорный генератор 7 непрерывно снабжает цифровую линию 6 задержки опорными импульсами, которые по мере распространения появляются на ее промежуточных отводах (61, 62, 63, ...), пока не достигают основного выхода 64. Импульсы 64 основного выхода цифровой линии 6 задержки сравниваются по фазе с ее входными импульсами с выхода опорного генератора 7 в блоке 8 фазового сравнения, выходное напряжение которого подстраивает время задержки распространения каждого входящего в цифровую линию 6 задержки управляемого элемента 15 задержки так, что время задержки всей цифровой линии 6 задержки постоянно равно периоду То импульсов опорного генератора 7. Поскольку управляемый элемент 4 задержки идентичен управляемым элементам 15 задержки в составе цифровой линии 6 задержки, то их времена задержки распространения одинаковы и равны , где N - число секций цифровой линии 6 задержки.

В момент поступления фронта входного сигнала 60 на входной зажим 2 блок 5 фазовой интерполяции начинает формирование тактовых импульсов 65...69 (в данном примере осуществления восемь парафазных сигналов), которые появляются последовательно на выходах блока 5 фазовой интерполяции в порядке возрастания их номеров. По фронтам этих импульсов, задержанных относительно друг друга на (М - число парафазных выходов блока 5 фазовой интерполяции, в данном примере равное 8), тактируются соответствующие регистры в первом блоке 9 регистров и в них записываются состояния выходов цифровой линии 6 задержки. Таким образом производится отсчет состояний выходов цифровой линии 6 задержки, соответствующих началу преобразуемого интервала времени Тx. Также с момента поступления входного сигнала разрешается работа счетчика 3 импульсов, который в течение интервала Tx заполняется импульсами с основного выхода 64 цифровой линии 6 задержки.

По окончании интервала Тx начинается процесс отсчета состояний выходов цифровой линии 6 задержки. При этом на инверсных выходах блока 5 фазовой интерполяции в порядке нарастания их номеров с последовательно нарастающей на Δt задержкой появляются фронты импульсов, которые тактируют соответствующие регистры во втором блоке 10 регистров. В результате во втором блоке 10 регистров оказываются записанными отсчеты состояний выходов цифровой линии 6 задержки, соответствующие окончанию преобразуемого интервала времени Тx.

Записанные в блоки 9 и 10 регистров коды в порядке: регистр 1 - выход 1, регистр 2 - выход 1, регистр 3 - выход 1, ..., регистр 1 - выход 2, регистр 2 - выход 2, ... регистр (М-1) - выход N, регистр М - выход N являются термометрическими N×М - разрядными кодами вида 000...111 либо 111...000. Эти коды преобразуются в прямые двоичные коды разрядностью log2(N×М) соответствующими первым 11 и вторым 12 шифраторами. Накопленное за время Тх содержимое Sсч счетчика 3 импульсов и двоичное число Sш2 выхода второго шифратора 12 составляют соответственно старшие и младшие разряды полного отсчета состояния цифровой линии 6 задержки при окончании интервала времени Тх: S2=SсчSш2. Аналогичный отсчет Sш1 состояния цифровой линии 6 задержки, соответствующий началу интервала времени Тх, образуется на выходе первого шифратора 11.

Число S2=SсчSш2 и число S1=0Sш1 с приписанными в старших разрядах нулями поступают на соответствующие входы комбинационного блока 13 вычитания, который на своих выходах образует результат преобразования интервала времени Тх как разность двух отсчетов:

где - коэффициент пропорциональности (ед/сек). Результат преобразования получается в единицах Δt.

Во избежание необходимости дополнительных преобразований произведение N×M следует выбирать равным целой степени двух. Перед следующим циклом преобразования счетчик 3 импульсов должен быть сброшен (цепь сброса на фиг.1 не показана).

Таким образом, предлагаемое устройство осуществляет преобразование время-код с субвентильным разрешением по времени, но обладает упрощенной по сравнению с прототипом реализацией.

Литература

1. Шляндин В.М. Цифровые измерительные устройства: Учебник для вузов. - М.: Высшая школа, 1981, с.166, рис.3.27.

2. Там же, с.163, рис.3.25.

3. Патент США 4439046, МПК G048/00, 27.03.1984 г.

4. Устройство для измерения интервала времени. Заявка на изобретение №2004108575/28 (009039), МПК G04F 10/04, решение о выдаче патента от 22.03.2005 г.

5. Mota M., Christiansen J. A High-Resolution Time Interpolator Based on a Delay Locked Loop and an RC Delay Line. - IEEE Jornal of Solid-State Circuits, Vol.34, № 10, October 1999, pp.1360-1366 (Fig.2, p.1361) - прототип.

1. Преобразователь время-код, содержащий соединенный с входным зажимом буферный элемент, цифровую линию задержки, которая имеет множество выходов, соединенный с опорным генератором сигнальный вход и управляющий вход, подключенный к выходу блока фазового сравнения, пара входов которого присоединена к входу и основному выходу цифровой линии задержки, а также первый блок регистров, информационные входы регистров которого подключены к соответствующим выходам цифровой линии задержки, причем каждый регистр в первом блоке регистров имеет собственный тактовый вход, отличающийся тем, что в него введены управляемый элемент задержки, блок фазовой интерполяции, второй блок регистров, первый и второй шифраторы, счетчик импульсов и блок вычитания, выходы которого являются выходами преобразователя время-код, а соответствующие входы подключены к выходам счетчика импульсов, второго и первого шифраторов, при этом входы первого и второго шифраторов соединены с соответствующими выходами первого и второго блока регистров соответственно, информационные входы второго блока регистров объединены с соответствующими информационными входами первого блока регистров, тактовые входы всех регистров в обоих блоках регистров присоединены к соответствующим выходам блока фазовой интерполяции, первый вход которого вместе с управляющим входом счетчика импульсов и входом управляемого элемента задержки подключен к выходу буферного элемента, а второй вход - к выходу управляемого элемента задержки, управляющий вход управляемого элемента задержки объединен с управляющим входом цифровой линии задержки, основным выходом присоединенной к счетному входу счетчика импульсов.

2. Преобразователь время-код по п.1, отличающийся тем, что цифровая линия задержки выполнена в виде последовательной цепи управляемых элементов задержки, объединенные управляющие входы которых служат управляющим входом цифровой линии задержки, а их выходы - выходами цифровой линии задержки.

3. Преобразователь время-код по п.1, отличающийся тем, что блок фазовой интерполяции содержит последовательно соединенные каскады интерполяции, каждый i-й каскад интерполяции имеет (2i-1+1) входов и (2i+1) выходов, выходы оконечного каскада интерполяции служат выходами блока фазовой интерполяции, при этом каждый каскад интерполяции включает (2i-1+1) элементов интерполяции, имеющих первый и второй парафазные входы и парафазный выход, первый и второй входы элементов интерполяции с нечетными порядковыми номерами в каждом упомянутом каскаде объединены и служат входами каскада интерполяции, первый и второй входы элементов интерполяции с четными порядковыми номерами в каждом упомянутом каскаде подключены к объединенным входам соответствующих элементов интерполяции с нечетными порядковыми номерами, отличающимися от порядкового номера данного элемента интерполяции на ±1, выходы всех элементов интерполяции данного каскада составляют совокупность выходов каскада интерполяции.