Имитатор джиттера

Иллюстрации

Показать всеИзобретение относится к области генерирования импульсов с нормированным фазовым дрожанием и может быть использовано в устройствах для испытаний систем синхронизации и декодирования цифровых данных. Достигаемый технический результат - повышение точности моделирования джиттера за счет достижения равномерного энергетического спектра в заданной полосе частот. Устройство содержит опорный генератор, генератор псевдослучайных чисел, мультиплексор, блок цифрового суммирования, параллельный регистр и делитель частоты. 1 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к технике генерирования импульсов с нормированным фазовым дрожанием для испытаний систем синхронизации и декодирования цифровых данных.

Уровень техники

Для моделирования фазового дрожания (джиттера) цифровых сигналов данных широко применяются цифровые фазовые модуляторы, управляемые генераторами псевдослучайных чисел (ГПСЧ).

Известен генератор пульсаций для испытаний битового синхронизатора [1], включающий последовательно соединенные ГПСЧ, аналоговый сумматор и управляемый напряжением генератор. Поскольку двоичная сумма смежных разрядов ГПСЧ обладает нормальным распределением, то и мгновенная частота на выходе управляемого генератора также случайна и имеет нормальное распределение. Точность моделирования джиттера в данном аналоге невысока, поскольку джиттер задается косвенно через частоту импульсов, а его среднеквадратическое отклонение зависит от нестабильных аналоговых блоков - сумматора и управляемого генератора.

Известен также генератор джиттера [2], включающий питаемый тактовыми импульсами ГПСЧ, выходы нескольких смежных разрядов которого подключены к адресным входам мультиплексора, у которого информационные входы соединены с соответствующими выходами блока последовательной задержки в виде сдвигающего регистра, тактовым входом связанного с тактовым входом ГПСЧ. Вход последовательной записи информации сдвигающего регистра является сигнальным входом генератора. Недостаток данного аналога - низкая точность имитации джиттера, поскольку для управления мультиплексором используется не сумма смежных разрядов ГПСЧ, а значения этих разрядов, взятые по отдельности. Другим недостатком аналога является то, что входные сигналы устройства (сигналы опорного генератора) и его тактовые импульсы не синхронизированы, что затрудняет наблюдение реакции испытуемых устройств.

Аналогом предлагаемого устройства является также генератор импульсов с нормированным фазовым шумом [3], который состоит из последовательно включенных тактового генератора и цепи управляемых элементов задержки. Каждый управляемый элемент задержки снабжен управляющим входом, присоединенным к соответствующему выходу ГПСЧ, тактовый вход которого присоединен к выходу названной цепи управляемых элементов задержки. В данном аналоге осуществляется непосредственное сложение квантов времени, благодаря чему отпадает необходимость в блоке цифрового сложения. Недостаток этого аналога состоит в неравномерном энергетическом спектре генерируемого джиттера. Известно [4], что огибающая дискретного спектра сигналов ГПСЧ описывается выражением [4]

где ƒ0 - опорная тактовая частота ГПСЧ. При ƒ=ƒ0W(ƒ)=0, следовательно, распределение процесса по частоте в аналоге далеко от равномерного распределения белого шума.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является устройство для моделирования фазового дрожания импульсов кодовой последовательности [5]. Данное устройство-прототип содержит опорный генератор, нагруженный на ГПСЧ, а также мультиплексор, адресные входы которого присоединены к соответствующим выходам блока цифрового суммирования, а информационные входы - к соответствующим выходам блока последовательной задержки, причем выход мультиплексора служит выходом устройства. В прототипе блок последовательной задержки выполнен в виде секционированной линии задержки, а блок цифрового суммирования - в виде реверсивного счетчика импульсов с управляющими направлением счета элементом ИСКЛЮЧАЮЩЕЕ ИЛИ и элементом И.

Устройство-прототип обеспечивает нормальное распределение случайных временных сдвигов импульсов относительно их номинальных позиций. Энергетический спектр джиттера простирается от ƒ0/(2n-1) до ƒ0, где n - разрядность ГПСЧ. Частотный спектр случайного процесса определяется ГПСЧ и описывается формулой (1). Следовательно, энергетический спектр воспроизводимого джиттера в устройстве-прототипе не соответствует универсальной модели белого шума, что является его недостатком.

Сущность изобретения

Целью настоящего изобретения является повышение точности моделирования джиттера за счет достижения равномерного энергетического спектра в заданной полосе частот.

Указанная цель достигается тем, что в устройство, содержащее опорный генератор, нагруженный на ГПСЧ, и мультиплексор, адресные входы которого присоединены к соответствующим выходам блока цифрового суммирования, информационные входы - к соответствующим выходам блока последовательной задержки, а выход служит выходом устройства, введены параллельный регистр и делитель частоты. При этом делитель частоты включен между выходом опорного генератора и объединенными входом блока последовательной задержки и тактовым входом параллельного регистра, информационные входы параллельного регистра подключены к соответствующим выходам ГПСЧ, а его выходы - к входам блока цифрового суммирования.

Частота ƒ0 опорного генератора выбирается в N раз выше заданной

частоты выходных импульсов имитатора джиттера, этому же числу N выбирается равным модуль делителя частоты. За счет включения между выходами ГПСЧ и блока цифрового суммирования регистра, который тактируется выходными импульсами делителя частоты, энергетический спектр цифрового кода, управляющего мультиплексором, ограничивается частотой ƒДЧ=ƒ0/N. Таким образом, из полного частотного диапазона ƒ0/(2n-1)...ƒ0 процесса на выходе ГПСЧ путем его стробирования с помощью регистра сохраняется лишь практически плоский участок ƒ0/(2n-1)...ƒ0/N энергетического спектра. Например, при N=8 из (1) следует

что означает спад огибающей энергетического спектра всего на 0,45 дБ.

Перечень фигур чертежей

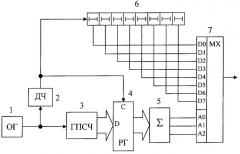

На чертеже представлена функциональная электрическая схема имитатора джиттера в соответствии с настоящим изобретением.

Сведения, подтверждающие возможность осуществления изобретения

Показанная на чертеже схема имитатора джиттера содержит опорный генератор 1, подключенный к входам делителя 2 частоты и генератора 3 псевдослучайных чисел, а также параллельный регистр 4, у которого информационные входы присоединены к выходам группы смежных разрядов ГПСЧ 3, а выходы - к соответствующим входам блока 5 цифрового суммирования. Кроме того, в схеме имеются блок 6 последовательной задержки, входом подключенный к выходу делителя 2 частоты и одновременно к тактовому входу параллельного регистра 4, а выходами - к соответствующим информационным входам мультиплексора 7. Выход мультиплексора 7 служит выходом имитатора джиттера.

Блок 6 последовательной задержки представляет собой секционированную линию задержки, которую целесообразно выполнить в виде цепи электронных элементов задержки с общим числом m выходов (секций), равным числу информационных входов мультиплексора 7.

Разрядность n ГПСЧ 3 выбирается с учетом заданной нижней границы ƒ0/(2n-1) энергетического спектра джиттера, к входам блока 5 цифрового суммирования подключаются (m-1) выходов смежных разрядов ГПСЧ. В любом случае должно выполняться условие n≥m-1.

Блок 5 цифрового суммирования представляет собой комбинационный сумматор (m-1) одноразрядных чисел, который можно выполнить как на нескольких одноразрядных сумматорах, так и в виде постоянного запоминающего устройства [6]. Число разрядов параллельного регистра 4 также равно (m-1).

Имитатор джиттера работает в следующем порядке. Опорный генератор 1 снабжает тактовыми импульсами с частотой ƒ0 ГПСЧ 3 и делитель 2 частоты. ГПСЧ 3 образует на своих (m-1) смежных выходах сдвинутые во времени псевдослучайные последовательности двоичных состояний, которые поступают на информационные входы параллельного регистра 4. Делитель 2 частоты делит тактовую частоту ƒ0 в N раз, его выходные импульсы поступают на вход блока 6 последовательной задержки и одновременно на тактовый вход параллельного регистра 4. Упомянутые импульсы начинают распространяться по блоку 6 задержки, последовательно появляясь на соответствующих информационных входах мультиплексора 7 с интервалом Δt, который равен времени задержки одной секции блока 6 задержки. По фронтам тех же импульсов делителя 2 частоты производится запись состояний ГПСЧ 3 в параллельный регистр 4. Блок 5 цифрового суммирования преобразует количество единиц, имеющихся на выходах регистра 4, в двоичное число - адрес мультиплексора 7. В соответствии с адресом мультиплексор 7 передает на свой выход импульсы с того или иного информационного входа и выполняет, таким образом, функции фазового модулятора.

Поскольку сумма содержимого смежных разрядов ГПСЧ 3, записанная в регистр 4 и преобразованная в адрес мультиплексора 7, имеет нормальное распределение, то и момент появления импульса на выходе мультиплексора 7 также случаен и подчиняется нормальному закону. Энергетический спектр джиттера выходного импульса ограничен сверху частотой ƒ0/N и при надлежащем выборе значения N равномерен.

Источники информации

1. Харикумар, Наир. Генератор пульсаций для испытаний битового синхронизатора. - Электроника, 1975, №11, с.65-67.

2. Tom Seim. Embed A Generator To Do Comm Test. - Electronic Design, March 20, 2000. (см. также Internet Online http://www.elecdesign.com/Articles/ArticleID/l 316/1316.html).

3. Генератор импульсов с нормированным фазовым шумом. - Патент РФ №2133552, кл. Н03K 5/159.

4. Хоровиц П., Хилл У. Искусство схемотехники: В 2-х т. Т.2 - М.: Мир, 1986, с.99, рис.9.71.

5. Устройство для моделирования фазового дрожания импульсов кодовой последовательности. - Авт. свид. СССР №1198533, кл. G06F 15/20 (прототип).

6. Чулков В.А. Генератор импульсов с фазовым дрожанием. - Приборы и техника эксперимента, 1996, №2, с.73-74.

Имитатор джиттера, содержащий опорный генератор, нагруженный на генератор псевдослучайных чисел, а также мультиплексор, адресные входы которого присоединены к соответствующим выходам блока цифрового суммирования, а информационные входы - к соответствующим выходам блока последовательной задержки, причем выход мультиплексора служит выходом имитатора джиттера, отличающийся тем, что в него дополнительно введены параллельный регистр и делитель частоты, при этом делитель частоты включен между выходом опорного генератора и объединенными входом блока последовательной задержки и тактовым входом параллельного регистра, информационные входы параллельного регистра подключены к соответствующим выходам генератора псевдослучайных чисел, а его выходы - к входам блока цифрового суммирования.